**Zeitschrift:** bulletin.ch / Electrosuisse

Herausgeber: Electrosuisse

**Band:** 104 (2013)

Heft: 4

**Artikel:** Energieeffiziente Nanodraht-Transistoren

Autor: Riel, Heike

**DOI:** https://doi.org/10.5169/seals-856472

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 02.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Energieeffiziente Nanodraht-Transistoren

### Der Tunnel-Transistor als Kandidat für künftige Schaltelemente

Die konventionelle Miniaturisierung in der Halbleitertechnik stösst heute an physikalische Grenzen. Die Reduzierung des Energieverbrauchs eines Schaltkreises ist eine der grössten Herausforderungen der Nanoelektronik. Will man bei gleichzeitiger Verminderung des Energieverbrauchs die Leistung steigern, sind radikal neue Konzepte gefordert. Halbleitende Nanodrähte, bei denen nicht nur die dreidimensionale Form, sondern auch quantenmechanisches Tunneln genutzt werden, bieten sich als Schaltelemente für künftige Prozessoren an.

Heike Riel

Durch die kontinuierlich steigende Rechenleistung der Prozessoren werden elektronische Geräte bei gleicher Leistung stets kleiner, während Hochleistungsrechner immer mehr leisten können und sich somit neue Anwendungsmöglichkeiten erschliessen lassen. Gleichzeitig wächst der Energieverbrauch der Informationstechnologie. Im Jahr 2010 verbrauchten die Rechenzentren rund 1,3% der gesamten weltweit erzeugten elektrischen Energie - und dieser Trend steigt [1]. Sequoia, der grösste IBM-Supercomputer, leistet 16,3 PFLOPS (Peta-FLOPS = 1015 Fliesskomma-Rechenoperationen pro Sekunde) und verbraucht dabei 7,9 MW. Da sich bei Hochleistungsrechnern die Rechenleistung im Durchschnitt alle vier Jahre verzehnfacht, erwartet man, 2020 einen EFLOPS-Rechner (Exa = 1018) zur Verfügung zu haben. Dies erfordert jedoch eine enorme Steigerung der Energieeffizienz, da sonst bei gleicher Technologie fast 1 GW an Leistung nötig wäre - ein Energieverbrauch in dieser Grössenordnung ist unrealistisch. Deshalb müssen neue, energieeffiziente Technologien erforscht und entwickelt werden. Diese Effizienzsteigerung betrifft auch den Feldeffekttransistor (FET), das kleinste aktive Bauelement eines Computerprozessors.

# Herausforderungen der Skalierung

In einem Metalloxid-Halbleiter-FET (MOSFET) wird der elektrische Stromfluss im Kanal zwischen zwei Kontakten,

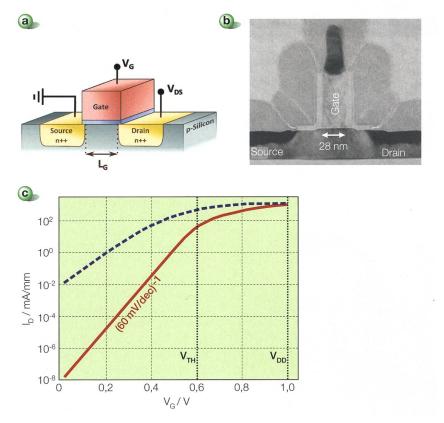

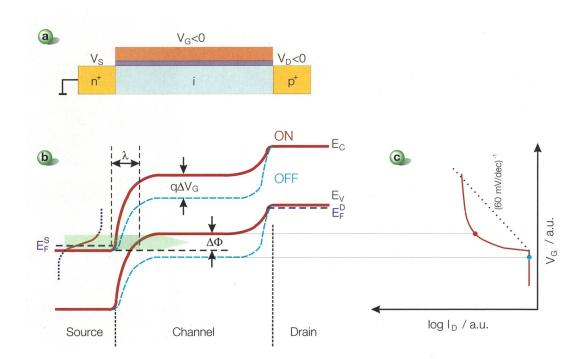

den sogenannten Source- und Drain-Kontakten, über einen dritten Kontakt, dem Gate, mittels elektrischem Feldeffekt gesteuert (Bild 1a). Der Source-Drain-Strom steigt bei gegebener Source-Drain-Spannung mit zunehmender Gate-Spannung exponentiell an und sättigt oberhalb der Schwellenspannung (Bild 1b). In einem idealen MOSFET beträgt dieser Anstieg bei Raumtemperatur 1/(60 mV/dec). Es werden also 60 mV benötigt, damit der Strom um eine Grössenordnung zunimmt. Dieser Anstieg ist bestimmt durch die thermische Injektion von Elektronen über die Energiebarriere in den Transistorkanal und stellt eine fundamentale physikalische Grenze dieses Bauelements dar.

Der Leistungsverbrauch eines Schaltkreises setzt sich aus zwei Komponenten zusammen: dem dynamischen Teil, der durch das Laden und Entladen während des Schaltens entsteht, und dem statischen Teil, der von Leckströmen dominiert ist, die auch im nicht schaltenden Zustand auftreten. Die Schaltfrequenz hängt für viele Schaltkreise nahezu linear von der Spannung ab, sodass sich insge-

**Bild 1** Der konventionelle MOSFET. a) Schematischer Aufbau eines MOSFETs. b) MOSFET-Transfercharakteristik mit (blaue Kurve) und ohne Kurzkanaleffekte (rote Kurve). c) MOSFET in heutigen Schaltkreisen mit 28 nm Gate-Länge.

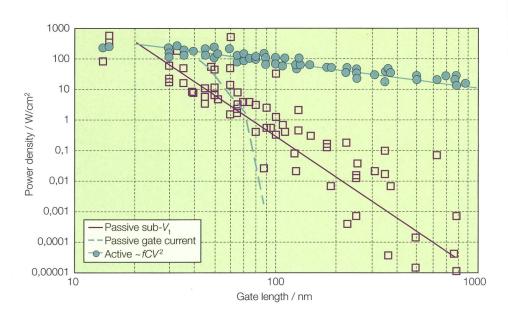

**Bild 2** Herausforderungen der Skalierung. Aktive und passive Leistungsdichte als Funktion der Gate-Länge; reproduziert aus [3].

samt eine kubische Spannungsabhängigkeit des dynamischen Leistungsverbrauchs ( $P \sim V^3$ ) ergibt [2]. Deshalb lässt sich der Leistungsverbrauch am einfachsten durch eine Reduktion der Spannung erreichen.

Durch die kontinuierliche Miniaturisierung der Transistoren über die letzten Jahrzehnte wurde die Gate-Länge stark reduziert und beträgt heute nur noch 25–30 nm (Bild 1c). Damit einhergehend konnte auch die Betriebsspannung verringert werden. Jedoch wurden hier bereits physikalische Grenzen erreicht, sodass die Betriebsspannung in den letzten

Chipgenerationen nicht entsprechend der zunehmenden Transistordichte gesenkt werden konnte und nun im Bereich von etwa 0,8 V verharrt. Dadurch ist die aktive Leistungsdichte im Schaltkreis mit der reduzierten Gate-Länge angestiegen (Bild 2) [3]. Zudem hat die passive Leistungsdichte noch stärker zugenommen. Sie ist durch die Skalierung um mehr als sieben Dekaden angestiegen und liegt heute in der gleichen Grössenordnung wie die aktive Leistung. Ein Grund für diese Entwicklung ist die Tatsache, dass sich der Transistor bei fortschreitender Skalierung nicht mehr ideal

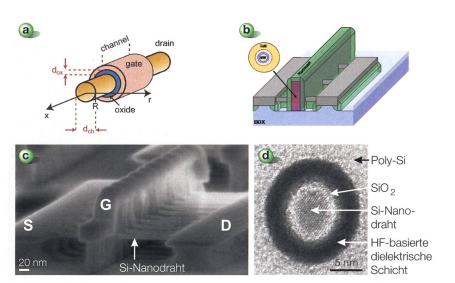

**Bild 3** Si-Nanodraht-MOSFET. a) Schematisches Bild eines Nanodrahts mit Gate-Elektrode und Gate-Oxidschicht, welche den Nanodraht voll umschliessen. b) Schema eines MOSFETs auf der Basis lateraler Nanodrähte. c) Rasterelektronenmikroskopieaufnahme eines Si-Nanodraht-MOSFETs. d) Transmissionselektronenmikroskopaufnahme des Querschnitts eines Nanodrahts. (Reproduziert aus [5].)

verhält, sondern durch sogenannte Kurzkanaleffekte dominiert ist. In diesem Fall können die Ladungsträger im Kanal nicht mehr ausreichend gut durch das elektrische Feld der Gate-Elektrode gesteuert werden. Leckströme nehmen zu, die Steigung in der Transfercharakteristik wird flach [<(60 mV/dec)-1], und der Transistor lässt sich nicht mehr vollständig ausschalten (Bild 1b). Die starke Zunahme des Stroms bei einer Gate-Spannung von 0 V erhöht somit den Leistungsverbrauch des Transistors. Hinzu kommen noch Verluste aufgrund von Leckströmen durch die Oxidschicht, die die Gate-Elektrode und den Kanal voneinander trennt. Diese Schicht beträgt nur noch wenige Atomlagen und ist deshalb nicht mehr vollkommen elektrisch isolierend.

Dies verunmöglicht heute die Fortsetzung der klassischen Skalierung der Bauelemente. Nur mit fundamental neuen Konzepten lässt sich die Miniaturisierung fortführen und gleichzeitig bei jeder neuen, kleineren Generation von Transistoren eine Verbesserung der Leistungsfähigkeit und eine höhere Energieeffizienz erzielen.

## Der Nanodraht als idealer Transistor

Einer dieser fundamental neuen Ansätze, an dem am IBM-Forschungszentrum in Rüschlikon geforscht wird, sind halbleitende Nanodrähte. Dies sind Halbleitermaterialien in Form eines Zylinders, dessen Durchmesser nur wenige Nanometer klein ist. Im Gegensatz zum

planaren FET umschliesst im Nanodrahttransistor das Gate den zylindrischen Kanal vollständig (Bild 3a). Dadurch können eine optimale Elektrostatik und die bestmögliche Steuerung der Ladungsträger im Transistorkanal erreicht werden. Deshalb wird auch bei sehr kleinen Gate-Längen ein nahezu ideales Verhalten der Einschaltcharakteristik des Transistors mit einer inversen Steigung von 60 mV/ dec erreicht, und Leckströme können reduziert werden. Im Vergleich zum konventionellen planaren Transistor erlaubt deshalb der Nanodraht-MOSFET mehr als eine Halbierung der Gate-Länge bei gleicher Siliziumdicke ohne das Auftreten von Kurzkanaleffekten [4].

Heute können kristalline und defektfreie Si-Nanodrähte hergestellt werden, die nur wenige Nanometer Durchmesser besitzen - die kleinsten Durchmesser liegen unter 3 nm. Mittels ausgefeilter Herstellungsverfahren werden aus diesen winzigen Drähten Transistoren mit Gate-Längen von deutlich unter 15 nm gefertigt. Das schematische Bild 3b und die Rasterelektronenmikroskopaufnahme 3c zeigen einen Transistor bestehend aus mehreren parallelen, lateralen Nanodrähten mit gemeinsamen Source-, Gateund Drain-Elektroden. Der Querschnitt in Bild 3d, aufgenommen mittels Transmissionselektronenmikroskopie, deutlicht die den kristallinen Siliziumdraht umschliessende Schichtfolge von SiO<sub>2</sub> und Hf-basiertem Gate-Oxid und Tantalnitrid als Gate-Metall [5]. Äusserst vorteilhaft ist, dass sich dieser Nanodraht-Transistor weitgehend mit herkömmlichen Fabrikationsmethoden herstellen und direkt implementieren lässt. Der Nanodraht-MOSFET mit vollständig umfassender Gate-Elektrode wird somit der ultimativ skalierte Siliziumtransistor sein. Weitere Verbesserungen, insbesondere der Energieeffizienz, erfordern nicht nur neue Geometrien, sondern auch die Ausnutzung neuer physikalischer Mechanismen.

#### **Neues Schaltelement gesucht**

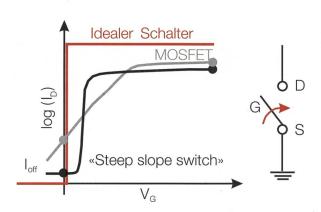

Bei einem idealen Schalter würde im Aus-Zustand kein Strom fliessen, im Ein-Zustand wäre der Schalter ein sehr guter Leiter. Zudem würde der Schalter fürs Schalten von Aus nach Ein nur eine infinitesimal kleine Spannung benötigen. Das Ziel, die Operationsspannung und damit den Leistungsverbrauch signifikant zu reduzieren, kann jedoch allein mit einer Änderung der Geometrie nicht erreicht werden. Ursache dafür ist die

Bild 4 Einschaltcharakteristik eines MOSFETs, eines idealen Schalters und eines Schaltelements mit steiler Einschaltcharakteristik.

physikalische Grenze von 60 mV/dec der inversen Steigung der Einschaltcharakteristik des MOSFETs. Diese führt zu einer Limitierung der Betriebsspannung (Bild 4). Wie erwähnt, beträgt diese minimale Spannung beim Silizium-MOSFET etwa 0,8 V.

Die IT-Industrie sucht nun nach einem neuen, technisch umsetzbaren Schaltelement, das eine deutliche Reduzierung der Spannung ermöglicht und somit den Energieverbrauch drastisch verringert und gleichzeitig eine weitere Miniaturisierung ermöglicht. Das Ziel weltweiter Forschungsaktivitäten ist die Entwicklung eines Transistors mit steiler Einschaltcharakteristik, auch «steep slope switch» genannt, dessen inverse Steigung deutlich unter 60 mV/dec liegt (Bild 4). Anstatt wie beim MOSFET die thermische Injektion der Ladungsträger zu nutzen, wird ein anderer physikalischer Effekt ausgenutzt, um die Ladungsträger in den Kanal zu leiten und somit die natürliche Grenze zu umgehen. Ein Bauelementkonzept, das eine vierfache Verringerung der Spannung erlaubt (z.B. von 0,8 V auf 0,2 V) bei gleichzeitig vernachlässigbaren Leckströmen würde aufgrund der kubischen Abhängigkeit (P~V3) zu einem 64-fach geringerem Leistungsverbrauch führen.

Es gibt einige Vorschläge für zukünftige Schalter, die eine steile Einschaltcharakteristik versprechen [6]. Beispielsweise zeichnet sich ein nanoelektromechanischer Schalter (NEMS), ähnlich einem mechanischen Relais in Nanometer-Grösse, durch sehr abruptes Schaltverhalten aus und zeigt einen nahezu idealen Anstieg. Jedoch ist die Betriebsspannung noch zu hoch, und auch die Verlässlichkeit dieser Technologie ist bisher nicht gross genug, um die im Chip notwendigen Schaltfrequenzen und Schaltzyklen zu liefern. Auch Stossioni-

sation aufgrund hoher elektrischer Felder im Transistor kann ausgenutzt werden, um aus einem einzigen Elektron eine Lawine von Elektronen zu erzeugen und damit ein Schalten mit abrupter Charakteristik zu erreichen. Beim jetzigen Status der Forschung ist der Tunnel-FET (TFET) jedoch der vielversprechendste Kandidat aller «steep slope switches» [7].

#### **Energieeffizienter Schalter**

In einem TFET werden die Ladungsträger mittels quantenmechanischem Tunneln in den Transistorkanal injiziert und nicht wie beim MOSFET mittels thermischer Aktivierung über die Barriere an der Grenzfläche zwischen Source und Kanal [8]. Die Struktur eines TFETs besteht deshalb aus einer p-i-n-Schicht mit hoch dotiertem n- und p-Bereich als Source- und Drain-Kontakt und dem mit einem Gate-Kontakt versehenen intrinsischen Kanal (Bild 5a). Im ausgeschalteten Zustand (blaue Kurve im Energiebanddiagramm, Bild 5b) liegt die Valenzbandkante des Kanals unterhalb der Leitungsbandkante der Source. In diesem Fall kann kein Tunnelstrom fliessen, da es keine freien Zustände im Kanal gibt, in welche die Elektronen aus der Source tunneln könnten. Dies ergibt einen sehr niedrigen Strom im ausgeschalteten Zustand des Transistors, wie man es sich für einen idealen Schalter wünscht. Durch Anlegen einer negativen Gate-Spannung verändert sich die energetische Lage der Zustände im Kanal (rote Linie im Energiebanddiagramm, Bild 5b), und es entstehen freie Plätze im Valenzband des Kanals, in welche die Elektronen aus dem Leitungsband der Source tunneln können. Der Stromfluss im TFET nimmt zu. Es können jedoch nur Ladungsträger mit einer ganz bestimmten Energie (siehe grün einge-

Bild 5 Funktionsprinzip eines Tunnel-FETs. a) Schematischer Ouerschnitt eines TFETs. b) Energiebandkantendiagramm des TFETs im ausgeschalteten (gestrichelte blaue Linie) und im eingeschalteten (rote Linie) Zustand. c) Schematische Zeichnung der Einschaltcharakteristik eines TFETs im Vergleich zum MOSFET. (Reproduziert aus [8].)

zeichneter Pfeil) in den Kanal fliessen, Elektronen mit höherer Energie werden herausgefiltert. Dieser Effekt ermöglicht eine inverse Steigung unter 60 mV/dec und damit eine steile Einschaltcharakteristik als Voraussetzung für niedrigere Betriebsspannungen (Bild 5c).

Eine Herausforderung beim TFET ist es jedoch, einen hohen Betriebsstrom zu erzielen, da dieser hauptsächlich durch die Tunnelwahrscheinlichkeit bestimmt ist. Die Wahrscheinlichkeit, dass Ladungsträger durch eine Barriere hindurch tunneln, wird umso grösser, je kleiner deren effektive Masse und je kleiner die Energiebarriere bzw. der Bandabstand des verwendeten Halbleiters ist. Deshalb bieten sich vor allem III-V-Halb-

leiter mit einer Bandlücke kleiner als die von Silizium an. Noch besser eignen sich Heterostrukturen – eine Kombination von z.B. zwei aufeinander abgestimmten Materialien. Damit kann die Bandstruktur gezielt optimiert werden. Sehr kleine effektive Bandabstände können so erreicht werden, die hohe Stromflüsse und ein steiles Einschalten des Transistors ermöglichen.

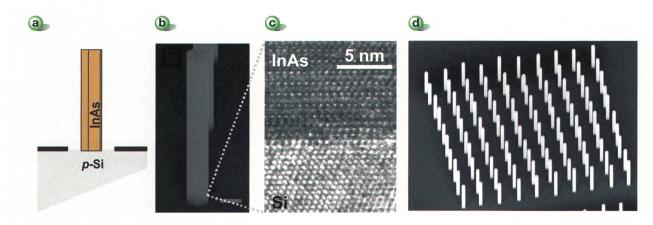

Eine vielversprechende Materialkombination ist Indiumarsenid (InAs) als Source und Silizium als Kanal und Drain. Da jedoch InAs und Si unterschiedlich grosse Atomabstände im Kristall besitzen, ist es sehr schwierig, beide Materialien zu verbinden. Nur mittels einer neuen Technologie, dem Wachstum von

Nanodrähten, ist es möglich, InAs-Si-Heterostrukturen als Ausgangsmaterial für TFETs herzustellen. Aufgrund der sehr kleinen Querschnittsfläche des Nanodrahts kann man InAs direkt kristallin auf Si wachsen lassen (Bild 6). In einem speziellen Verfahren (metal-organic chemical vapour deposition, MOCVD) wird InAs aus der Gasphase auf einem aufgeheizten Si-Substrat (T = 520 °C) abgeschieden. Das Si-Substrat ist mit einer dünnen Siliziumoxidschicht (~30 nm) beschichtet, in die an vordefinierten Stellen kleine Löcher geätzt wurden. Nur in diesen Öffnungen kann InAs auf Si wachsen, sodass diese hauptsächlich den Ort und den Durchmesser des Nanodrahts bestimmen (Bild 6a, 6b, 6d). Vor-

**Bild 6** Indiumarsenid-Nanodrähte. a) Schema des InAs-Nanodrahtwachstums auf einer strukturierten Si-Oberfläche. b) InAs-Nanodraht mit hexagonalem Querschnitt, gewachsen auf Si. c) Transmissionselektronenmikroskopieaufnahme der InAs-Si-Grenzfläche. d) Feld von vertikalen InAs-Nanodrähten, gewachsen auf Si.

#### TECHNOLOGIE NANOTECHNOLOGIE

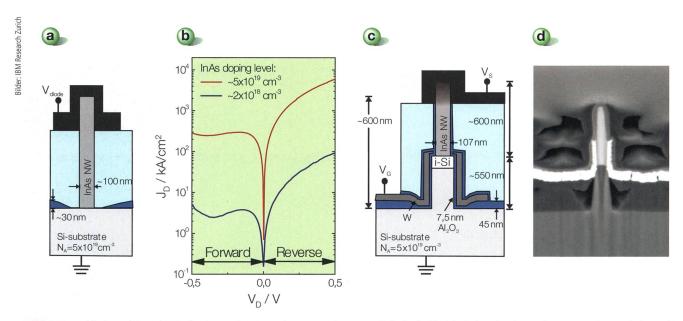

**Bild 7** Tunneldiode und Tunnel-FET. a) Schema einer InAs-Si-Heterostruktur-Nanodrahtdiode. b) Elektrische Charakteristik von InAs-Si-Nanodraht-Esaki-Tunneldioden. c) Schematischer Aufbau eines InAs-Si-Nanodraht-Tunnel-FETs. d) Rasterelektronenmikroskopaufnahme des Querschnitts eines InAs-Si-Nanodraht-Tunnel-FETs.

aussetzung für einen gut funktionierenden TFET mit hohem Stromfluss und steiler Steigung ist die Qualität der Grenzfläche zwischen InAs und Si, da hier das quantenmechanische Tunneln stattfindet. Dies bedingt unter anderem eine scharfe Grenzfläche zwischen InAs und Si (Bild 6c). Die elektrische Qualität der InAs-Si-Heterostruktur kann man mittels hoch dotierten p-n-Dioden, sogenannten Esaki-Tunneldioden, untersuchen. Diese geben Aufschluss über den maximalen Tunnelstrom, der mit der gewählten Materialkombination erreicht werden kann. Bild 7a zeigt den schematischen Querschnitt einer InAs-Si-Diode basierend auf einem einzigen Nanodraht. Im Vergleich zu normalen Dioden, die in Rückwärtsrichtung sperren, fliesst bei diesen hoch dotierten Esaki-Tunneldioden in Sperrrichtung ein Tunnelstrom. In Vorwärtsrichtung beobachtet man darüber hinaus einen negativen differenziellen Widerstand (NDR), d.h. einen Bereich, in dem der Stromfluss mit zunehmender Spannung abnimmt (Bild 7b). Detaillierte Studien haben ergeben, dass bei sehr hohen Dotierkonzentrationen von 1020 Atomen/cm3 für Si (p-dotiert) und 5·10<sup>19</sup> Atomen/cm<sup>3</sup> für InAs (n-dotiert) Tunnelströme von 6 MA/cm² bei -0,5 V in Sperrrichtung (Betriebspunkt des TFETs) erreicht werden - die höchsten Werte, die bisher in Esaki-Tunneldioden erreicht wurden [9]. Dies belegt die hohe Qualität der InAs-Si-Nanodraht-Heterostruktur und ist eine wesentliche

Voraussetzung, einen TFET mit steiler Einschaltcharakteristik (S < 60 mV/dec) und hohem Strom ( $I_D > 100 \,\mu\text{A/cm}^2$ ) zu erzielen. Erste auf vertikalen Nanodrähten basierende InAs-Si-TFETs wurden bereits realisiert. Bild 7c zeigt den schematischen Aufbau eines vertikalen InAs-Si-Nanodraht-TFETs im Querschnitt. Hierbei dient das Si-Substrat als Drain-Elektrode, der intrinsische Si-Kanal ist von der Gate-Elektrode voll umschlossen. Von der von oben kontaktierten

InAs-Source-Seite werden die Ladungsträger injiziert. Dieses Konzept konnte erst vor Kurzem technisch umgesetzt werden (Bild 7d) [10]. Erste vielversprechende elektrische Messungen wurden bereits durchgeführt. Die weiteren Forschungsaktivitäten zielen darauf, ein noch detaillierteres Verständnis der physikalischen Mechanismen zu erlangen – auch mittels Simulation – und eine weitere Optimierung der einzelnen Komponenten zu erreichen.

### Résumé Les transistors à nanofil à faible consommation d'énergie

Le transistor à effet tunnel, un candidat aux futurs éléments de commutation

La miniaturisation conventionnelle dans le domaine de l'informatique se heurte aujourd'hui

aux limites physiques fondamentales. C'est la raison pour laquelle la recherche de nouvelles

technologies à faible consommation d'énergie se révèle indispensable. Chaque nouvelle

génération de transistors de taille inférieure nécessite de nouveaux concepts (nouveaux

matériaux, nouvelles architectures et l'application d'autres mécanismes de commutation), car

un simple changement d'échelle ne suffit plus à augmenter la puissance de calcul et à réduire

la consommation d'énergie.

La forme tridimensionnelle du nanofil complètement entouré d'une isolation et de la grille offre la géométrie idéale pour obtenir une caractéristique MOSFET optimale, même avec de très faibles longueurs de grille (< 15 nm). Les transistors planaires présentant des longueurs de grille au moins deux fois plus importantes, le transistor MOSFET à nanofil deviendra donc l'ultime réduction du transistor au silicium.

Afin d'économiser de l'énergie supplémentaire, il est généralement nécessaire d'appliquer d'autres mécanismes physiques pour éviter la pente inverse de 60 mV/dec de la caractéristique de mise en marche d'un transistor MOSFET. Parmi tous les candidats éventuels à un nouvel interrupteur présentant des tensions de service inférieures à 0,3 V, le transistor à effet de champ à effet tunnel (TFET) est celui qui possède le plus grand potentiel. Dans ce cas, le nanofil permet d'associer de nouveaux matériaux et propose une géométrie optimale. Les TFET promettent ainsi une réduction importante de la consommation d'énergie par rapport aux transistors MOSFET conventionnels.

#### TECHNOLOGIE NANOTECHNOLOGIE

#### Zusammenfassung

Die konventionelle Miniaturisierung in der Informationstechnologie stösst heute an fundamentale physikalische Grenzen. Deshalb ist insbesondere die Erforschung neuer energieeffizienter Technologien notwendig. Bei jeder neuen, kleineren Generation von Transistoren müssen neue Konzepte angewendet werden, denn eine reine Skalierung reicht nicht mehr aus, um die Rechenleistung zu steigern und den Energieverbrauch zu senken. Neue Materialien, neue Architekturen und das Anwenden anderer Schaltmechanismen sind der Schlüssel zum Erfolg.

Die dreidimensionale Form des Nanodrahts mit vollständig umfassender Gate-Elektrode bietet die ideale Geometrie, um die optimale MOSFET-Charakteristik auch bei sehr kleinen Gate-Längen (<15 nm) zu erzielen. Bei planaren Transistoren sind die Gate-Längen mindestens doppelt so lang. Somit wird der Nanodraht-MOSFET der ultimativ skalierte Siliziumtransistor sein.

Um zusätzlich Energie zu sparen, muss man aber noch einen Schritt weiter gehen. Grundsätzlich andere physikalische Mechanismen müssen angewendet werden, um die physikalisch begrenzte inverse Steigung von 60 mV/dec der Einschaltcharakteristik eines MOSFETs zu umgehen. Der Tunnel-FET ist unter allen möglichen Kandidaten für einen neuen Schalter mit Betriebsspannungen unter 0,3 V derjenige mit dem höchsten Potenzial. Hierbei ermöglicht der Nanodraht die Kombination neuer Materialien und bietet die optimale Geometrie, um zukünftige energieeffiziente Tunnel-FETs zu realisieren. Tunnel-FETs versprechen damit im Vergleich zu konventionellen MOSFETs eine signifikante Reduktion des Energieverbrauchs.

#### Referenzen

- [1] Koomey, J. G., Growth in Data Center Eletricity Use 2005 to 2010, Analytics Press, (2011).

- [2] Chang, L., Frank, D. J., Montoye, R. K., Koester, S. J., Ji, B. L., Coteus, P. W., Dennard, R. H., Haensch, W., Practical Strategies for Power-Efficient Computing Technologies, Proc. IEEE, Vol. 98, S. 215 (2010).

- [3] Haensch, W., Nowak, E.J., Dennard, R.H., Solomon, P.M., Bryant, A., Dokumaci, O.H., Kumar, A., Wang, X., Johnson, J.B., Fischetti, M.V., Silicon CMOS devices beyond scaling, IBM J. Res. & Dev., Vol. 50, S. 339 (2006).

- [4] Bangsaruntip, S., Cohen, G. M., Majumdar, A., Sleight, J. W., Universality of Short-Channel Effects in Undoped-Body Silicon Nanowire MOSFETS, IEEE Elec. Dev. Lett., Vol. 31, S. 903 (2010).

- [5] Sleight, J. W., et al., Gate-All-Around Silicon Nanowire MOSFETs and Circuits, IEEE DRC, Vol. 68, S. 269 (2010).

- [6] Bernstein, K., Cavin, R. K., Porod, W., Seabaugh A. C., Welser, J., Device and Architectures Outlook for beyond CMOS Switches. Proc. IEEE, Vol. 98, S. 2169 (2010).

- [7] ITRS International Technology Working Groups. International Technology Roadmap for Semiconductors, http://www.itrs.net (2010).

- [8] Ionescu, A. M., Riel, H., Tunnel Field-effect Transistors as Energy-efficient Electronic Switches, Nature, Vol. 479, S. 329 (2011).

- [9] Riel, H., Moselund, K. E., Bessire, C., Björk, M. T., Schenk, A., Ghoneim, H., Schmid, H., InAs-Si Heterojunction Nanowire Tunnel Diodes and Tunnel FETs, IEEE IEDM (2012).

- [10] Schmid, H., Moselund, K. E., Björk, M. T., Richter, M., Ghoneim, H., Bessire, C. D., Riel, H., Fabrication of Vertical InAs-Si Heterojunction Tunnel Field Effect Transistors, IEEE DRC, Vol. 69 (2011).

#### Angaben zur Autorin

Dr. **Heike Riel** leitet die Nanoscale-Electronics-Gruppe bei IBM Research – Zurich. Ihre Forschungsinteressen liegen auf dem Gebiet der Nanotechnologie, insbesondere der halbleitenden Nanodrähte für verschiedenste Anwendungen und der molekularen Elektronik.

IBM Research – Zurich, 8803 Rüschlikon hei@zurich.ibm.com

Ein spezieller Dank geht an alle Mitarbeiter der Nanoscale-Electronics-Gruppe, IBM Research – Zurich. Die Arbeiten wurden finanziell teilweise vom EU FP7 Projekt Steeper unterstützt.

Wir sind der Komplettanbieter für Energieverteil- und Kabelverbindungstechnik im Bereich Mittel- und Niederspannung. Von Beratung bis Unterhalt profitieren Sie vom breiten Know-how unserer Spezialisten und unser Rund-um-die-Uhr-Service sorgt für grenzenlose Power. Heute und morgen.

Cellpack Power Systems AG Schützenhausstrasse 2 5612 Villmergen Tel. 056 618 18 18 power.systems@cellpack.com