**Zeitschrift:** bulletin.ch / Electrosuisse

**Herausgeber:** Electrosuisse

**Band:** 96 (2005)

**Heft:** 1

**Artikel:** High Density Packaging oder ASIC?

**Autor:** Scheffler, Michael / Gillen, Thomas

**DOI:** <https://doi.org/10.5169/seals-857764>

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 18.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# High Density Packaging oder ASIC?

## Was eignet sich besser, um eine Schaltung zu miniaturisieren?

Elektronikprodukte werden immer kleiner, ganze Schaltungen werden auf wenigen Quadratzentimetern miniaturisiert.

Während beim ASIC die ganze Schaltung in einem Chip untergebracht wird, lötet oder klebt man beim High Density Packaging den nackten Chip auf einen Print – allenfalls gestapelt in mehreren Schichten. Beide Technologien haben Vor- und Nachteile.

Heutzutage besteht ein beständiger Zwang zur Produktinnovation: mehr Funktionalität, erhöhte Portabilität, Volumen- und Gewichtsreduktion sowie eine reduzierte Leistungsaufnahme. Dies erfordert eine stetige Weiterentwicklung der Produkte: Sie werden höher integriert, und gleichzeitig dürfen die Stückkosten nicht ansteigen – oder sollten noch

*Michael Scheffler, Thomas Gillen*

lieber fallen. Um dies zu erreichen müssen die Schaltungen kontinuierlich überarbeitet werden. Es bietet sich an, die Schaltungen in ASICs<sup>1)</sup> zu integrieren oder High Density Packaging (HDP) zu nutzen.

Ein ASIC bezeichnet die Integration von unterschiedlichen Schaltungsteilen auf einem Chip. Dies können analoge, digitale oder optische Komponenten sein oder auch Speicher. Sie werden mit einem festgelegten Prozess, zum Beispiel CMOS, CMOS/Flash oder BiCMOS, und einer bestimmten Strukturbreite (0.8 µm, 0.35 µm, ...) auf den Chip integriert.

HDP hingegen umfasst Aufbau- und Verbindungstechniken, die auf der Basis von meist ungehäusten ICs und hochdichten Leitungsträgern eine Miniaturisierung von Schaltungsgruppen ermöglichen. Die Technologie ist verwandt mit der Standard-SMD-Technik.

Je nach Schaltungstyp, Komplexität und Stückzahlen eignet sich eine Schaltung eher für einen ASIC oder für HDP. Beide Technologien haben Vor- und

Nachteile, mit unterschiedlichen Kosten, Risiken und Durchlaufzeiten.

### Schaltungstyp und Komplexität

Vom Prinzip her am besten geeignet zur ASIC-Integration sind rein digitale Schaltungen. Hier gab es in der Vergangenheit die grössten Fortschritte, und im Nachzug sind analoge Schaltungen mehr und mehr digitalisiert worden, um von diesem Integrationspotenzial zu profitieren. In der Folge steigen die Gatterzahlen von rein digitalen ASICs weiter an. Entsprechend steht eine Vielzahl von Tools und Werkzeugen (IP-Cores, ...) zur Verfügung, die alle Phasen vom Entwurf über

Prototyping bis hin zur Realisierung unterstützen. Die Fortschritte bei den FPGAs und leistungsfähigere Prozessoren mit flexibler Peripherie machen aber dem reinen Digital-ASIC das Feld streitig. Parallel sinkt das Angebot an vorstrukturierten Gate-Arrays mit bis zu 100 000 Gattern, bei gleichzeitig steigenden NRE-Kosten<sup>2)</sup> und Mindeststückzahlen. Deshalb sollte bei niedrigeren Gatterzahlen stets ein voll kundenspezifischer ASIC geprüft werden.

Der Vorteil eines rein digitalen ASICs liegt in der Größenreduktion, der Kapselung der Schaltungskomplexität und den niedrigeren Stückkosten verglichen mit zugekauften Bauteilen, bei relativ geringem Integrationsrisiko.

Bereits bei der Integration von nicht-flüchtigem Speicher muss abgewogen werden: Ein gemischter CMOS/Flash-Prozess liegt in seinen Fertigungskosten etwa 30% höher als ein reiner CMOS-Prozess. Hier bietet HDP die Möglichkeit, durch geschickte Partitionierung des Systems die Integrationslast zu verteilen und die Kosten zu optimieren, indem für Standardaufgaben (Speicher, Prozessor) dedizierte Chips eingesetzt werden, und nur der Rest in einem kundenspezifischen ASIC realisiert wird.

Rein analoge Schaltungen sind ebenfalls gut geeignet für eine ASIC-Integration, da sie durch eine Vielzahl von diskreten Bauteilen implementiert werden können, sie erfordern aber eine sehr gute

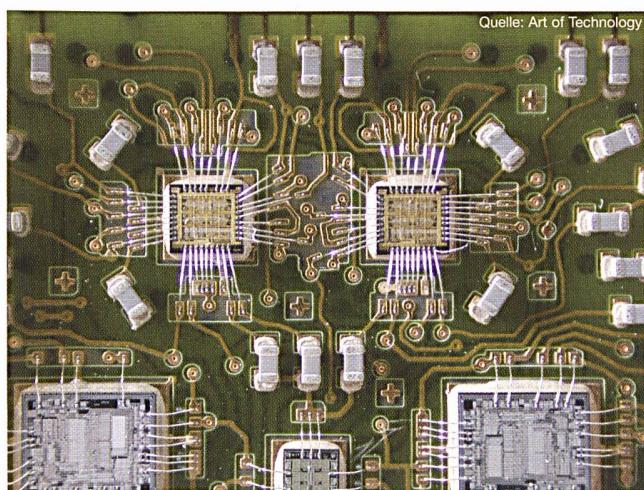

**High Density Packaging und ASIC kombiniert**

Teilansicht eines HDP-9:4-Satellitenswitch-Moduls (vor Verguss), bestehend aus zwei 5:4-HF-Switch-ASICs (oben) und zwei Standard-Controllern mit einem Spannungsinverter (unten). Das ASIC/HDP-Modul ermöglichte eine deutliche Zeit- und Kostenersparnis gegenüber einer ASIC-Neuentwicklung im Mixed-Signal-Bereich.

Spezifikation des zu integrierenden Systemteils.

Mixed-Signal-Anwendungen hingegen sind komplex im Design und aufwändig in der Prozessrealisierung: So müssen zum Beispiel analoge Elemente in CMOS realisiert oder (eher seltener) Logikkomponenten in einen BiCMOS-Prozess transferiert werden. Auf Grund der widersprüchlichen Anforderungen müssen dann oft wichtige Systemfeatures geopfert werden, was letztlich zur Unzufriedenheit mit dem Ergebnis führt. Kommt zum Beispiel noch der Wunsch nach der Integration von optischen Komponenten hinzu, steigen das Risiko und die Kosten deutlich an.

Diese Risiken werden von ASIC-Entwicklern oft auch als Herausforderung verstanden und möglicherweise nicht ausreichend kommuniziert. Leidvolle Erfahrungen gerade bei Mittelständlern im Mixed-Signal-Bereich sind allseits bekannt, und nicht selten musste ein ambitioniertes Projekt unverrichtet abgebrochen oder mit sehr niedriger Prozessausbeute beendet werden.

HDP bietet bei Mixed Signal den Vorteil, Standardkomponenten und ASICs miteinander kombinieren zu können, wobei jede Teilschaltung im jeweils optimalen Prozess realisiert werden kann. Die Kapselung wird dann auf Gehäuse- oder Modulseite vorgenommen, wobei das Resultat nicht zwingend grösser oder teurer sein muss als die angestrebte 1-Chip-Lösung.

## Wie gross muss die Stückzahl sein?

Eine ASIC-Entwicklung bedeutet immer einen beträchtlichen Aufwand hinsichtlich Entwicklungszeit und -aufwand, Einmalkosten, Prototypendurchlaufzeit und -kosten. Der Baustein muss dann noch gehäust und qualifiziert werden. Ein gewisses Mindestvolumen ist also erforderlich, über die 3M-Daumenregel (1 Mio. Gatter, 1 Mio. Stück oder 1 Mio. Bauteilwert) mag man streiten.

Der Lohn dieser Mühen besteht in der späteren Reduktion der Stückkosten durch die «Economics of Scale» und der Tatsache, dass nur das integriert ist, was wirklich benötigt wird. Jedoch muss der Aufwand stets über die projektierte Stückzahl abgeschrieben werden, etwaige Prozessänderungen und -migrationen laufen mindestens auf eine Neuqualifikation, eventuell auf ein Redesign hinzu.

Im Bereich der Einmalkosten muss man von knapp unter 100000 Euro für einen Siliziumrun inklusive Masken aus-

gehen, beispielsweise für einen Semi-Custom-Mixed-Signal-ASIC. Bei komplexen digitalen Designs sind schnell mehrere 100000 Euro erforderlich, die pro benötigtem Run anfallen, zum Beispiel für die Beseitigung von Fehlern. Die Designkosten sind dabei noch nicht berücksichtigt, liegen aber mindestens im gleichen Rahmen.

Hinsichtlich Prototypen- und Einmal-kosten bieten MPW-Runs<sup>3)</sup> eine gute Alternative zur Kostenreduktion. Hier werden mehrere ASICs verschiedener Kunden auf demselben Wafer produziert, dadurch verliert man natürlich eine gewisse Flexibilität, denn für bestimmte Prozesse gibt es nur sehr wenige Runs pro Jahr – zu fixen Terminen. Danach muss der ASIC noch zu einem Volumenhersteller transferiert werden. Bei Losen von bis zu 20 Wafern auf 6"- bis 8"-Lini en und kleinen Siliziumflächen werden in einem Los schnell einige 10000 Stück und mehr produziert. Unter Umständen entspricht dies dem Bedarf mehrerer Jahre, was eine hohe Kapitalbindung und eine geringe Flexibilität nach sich zieht. Dafür besteht Schutz vor Bauteilabkündigungen.

log Gate Array), gestattet eine kostengünstige Realisierung bei geringeren Stückzahlen, allerdings mit reduzierter Flexibilität.

HDP ist prinzipiell von kleinsten bis zu mittleren Stückzahlen geeignet, bei ganz grossen Stückzahlen wird es in Kombination mit ASICs eingesetzt, zum Beispiel mit Chip-on-Board in Uhren oder Spielzeugen aus Fernost. Die erforderlichen «bare dies» sind meistens entweder als Samples oder in Kleinstmengen von einigen 100 Stück erhältlich (entspricht einem Wafer). Anfangs skeptische Lieferanten lassen sich – je nach Produkt – manchmal schon ab einem Volumen von mehreren 1000 Stk/p.a. umstimmen, Volumen, die für die meisten ASIC-Hersteller uninteressant sind.

Die HDP-Entwicklungszeiten hängen von der Komponentenverfügbarkeit ab und liegen (inkl. Prototypenlieferung) in etwa bei 4 bis 6 Monaten. Die Entwicklungskosten für den Transfer eines Designs auf eine HDP-Lösung liegen je nach Komplexität zwischen 25000 und 50000 Euro, Prototypen schlagen meistens mit 10000 bis 20000 Euro zu Buche.

## HDP für kleine, ASIC für grosse Volumen

HDP und ASIC sind zwei unterschiedliche Integrationstechnologien mit spezifischen Vor- und Nachteilen, die sich nicht gegenseitig ausschliessen, sondern vielmehr ergänzen. Ein HDP-System kann später als ASIC realisiert werden, und ein ASIC wiederum kann in einem HDP-Design eingesetzt werden, um den nächsten Integrationsschritt zu machen.

Grundsätzlich kann man aber HDP als die «kleine» Lösung ansehen, bei der schneller Ergebnisse verfügbar sind, mit

|                                                 | ASIC                                                        | HDP Technologien                                                  |

|-------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------|

| <b>Systemgrösse</b>                             | Am kleinsten                                                | Sehr klein                                                        |

| <b>Stückkosten</b>                              | Am kleinsten (für eingefahrenen Prozess mit hoher Ausbeute) | Klein                                                             |

| <b>Initiale Entwicklungskosten</b>              | Hoch bis sehr hoch (einige 100k bis über 1 Million Euro)    | Moderat (wenige 10k bis 100k Euro)                                |

| <b>Erforderliche Stückzahlen/Jahr</b>           | >> 100 000 Stück                                            | Schon ab 100 Stk                                                  |

| <b>Design-Risiko</b>                            | Oft sehr hoch, v.a. bei mixed-signal Anwendungen            | Relativ niedrig                                                   |

| <b>Verfügbarkeit Prototypen ab Projektstart</b> | ~ 12–24 Monate                                              | ~ 4–6 Monate                                                      |

| <b>Typische Anwendungsfelder</b>                | Konsumentenelektronik, Mobiltelefone, Automobil, ...        | Medizin, Industrie, Sensoren, Automobil, Luft- und Raumfahrt, ... |

Tabelle Vergleich HDP-Technologien mit ASIC-Design

einem kleineren Risiko und für kleinere Volumen. ASICs sind durch die Komplexität des Designs und der Tools eher für Mittelfriststrategien und hohe Volumen einzusetzen, wobei die niedrigen Stück-

kosten und der reduzierte Montageaufwand auf Boardebene die treibenden Kräfte sind.

Die Beantwortung der Eingangsfrage lautet also: HDP und ASIC sind synerge-

tische Partner, die in einer optimalen Kombination geeignete Integrationslösungen für jeden Schaltungstyp, hohe und niedrige Komplexität und beliebige Stückzahlen darstellen.

## High Density Packaging ou bien ASIC?

### Quelle est la technique la mieux appropriée pour miniaturiser un circuit?

Les produits électroniques deviennent de plus en plus petits, des circuits entiers sont miniaturisés sur quelques centimètres carrés. Tandis qu'en ASIC tout le circuit est disposé sur une puce, en High Density Packaging, on soude ou on colle les puces sur un circuit imprimé – éventuellement sur plusieurs couches. Ces deux technologies ont des avantages et des inconvénients.

### Angaben zu den Autoren

Dr. Michael Scheffler ist Mitglied der Geschäftsleitung bei Art of Technology und verantwortlich für Produktionsbegleitung und Qualitätssicherung. Er ist seit mehr als 8 Jahren in Bereichen der Aufbau- und Verbindungstechnologien tätig.

Dr. Thomas Giller ist verantwortlich für die Hardwareentwicklung bei Art of Technology. Seit über 10 Jahren befasst er sich mit Elektronikminiaturisierung und ASIC-Entwicklung aus Kundensicht.

*Art of Technology AG, 8048 Zürich,*

*www.art-of-technology.com*

<sup>1</sup> ASIC: Application Specific Integrated Circuits

<sup>2</sup> NRE-Kosten: Non Recurring Engineering Costs, Ein-

malige Kosten für die Entwicklung

<sup>3</sup> MPW: Multiprojectwafer-Service

## Willkommen in der Welt von Complete Automation

Integrated Architecture

Superior Value-Added Services & Expertise

World Products

Global Supply & Local Capabilities

*Complete Automation*

[www.rockwellautomation.ch](http://www.rockwellautomation.ch)

### Beratung und Support, die Ihnen einen Mehrwert sichern

Willkommen in einer Welt, in der Daten und Informationen nahtlos zwischen den Anlagen und Unternehmen fließen, Kosten niedrig gehalten werden können und Unterstützung jederzeit und überall auf sechs Kontinenten bereitsteht.

Ob ein einziger Bauteil, eine integrierte Steuerung für die ganze Anlage oder ein Ausbildungsprogramm für das

Bedienungspersonal: es ist unser Ziel, immer die beste Lösung anzubieten.

Mit unseren System Integratoren, Distributoren und Encompass Partnern kooperieren wir weltweit. So stellen wir den umfangreichen Support sicher, der unsere Complete Automation-Lösungen auszeichnet.

### Rockwell Automation AG

Gewerbepark, 5506 Mägenwil

Telefon 062 889 77 77

Fax 062 889 77 66