**Zeitschrift:** bulletin.ch / Electrosuisse

Herausgeber: Electrosuisse

**Band:** 96 (2005)

Heft: 1

Artikel: La conception des circuits intégrés analogiques

Autor: Stefanovic, Danica / Kayal, Maher / Pastre, Marc

**DOI:** https://doi.org/10.5169/seals-857762

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 01.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# La conception des circuits intégrés analogiques

PAD: Un outil didactique

Aujourd'hui on peut intégrer de plus en plus de circuits analogiques et numériques sur une même puce de silicium. La majorité des outils de CAO sont destinés à la conception des circuits numériques. PAD est un outil didactique pour la conception des circuits intégrés analogiques, basé sur un modèle du transistor MOS spécialement optimisé pour cette catégorie de circuits.

Les systèmes électroniques intégrés sur silicium sont de plus en plus performants. Ils rassemblent un grand nombre de transistors sur une surface restreinte et réalisent des fonctions les plus diverses.

Danica Stefanovic, Maher Kayal, Marc Pastre

Aujourd'hui, l'évolution technologique a permis une baisse drastique de la tension d'alimentation et en même temps une augmentation de la densité de fonctions électroniques. Cependant, les contraintes de conception deviennent de plus en plus sévères en termes de vitesse, de consommation, de surface occupée sur silicium, etc. Comme dans tous les domaines de l'ingénieur, des compromis sont donc à trouver afin d'optimiser ces systèmes intégrés.

Beaucoup d'outils de CAO (Conception Assistée par Ordinateur) ont été développés pour aider les concepteurs à identifier et choisir les meilleurs compromis lors de la conception de systèmes électroniques. Ces outils leur permettent de contrôler la démarche de réalisation de circuits, d'accomplir automatiquement certaines tâches et d'optimiser le temps global de conception.

La majorité des systèmes électroniques se réalisent de nos jours en combinant des fonctions numériques et analogiques. La pratique montre que la plus grande partie de la surface occupée sur le silicium dans un système typique l'est par les circuits numériques. Cependant, l'interface avec notre monde physique, qui a une nature analogique, se fait en utilisant des circuits analogiques.

La méthodologie de conception de circuits numériques est de nature algorithmique et peut donc être décrite et automatisée sur ordinateur. La synthèse des fonctions numériques et l'implémentation sur silicium peuvent se faire à l'aide de programmes informatiques de plus en plus performants. Il existe ainsi une grande variété d'outils CAO pour circuits numériques.

Contrairement aux circuits numériques, la méthodologie de conception de circuits analogiques est fortement liée au type de fonction à implémenter. En effet, le choix de la topologie d'un circuit et le dimensionnement de ses transistors demandent une bonne maîtrise des lois physiques de chaque transistor utilisé et du modèle physique du composant qui est relativement complexe. D'autre part, l'optimisation des paramètres électriques, ainsi que la migration d'une technologie de fabrication vers une autre, sont presque impossibles sans l'intervention d'un expert en conception de circuits analogiques. Les outils de synthèse automatique de circuits intégrés analogiques sont très limités, voire quasi inexistants.

Le Laboratoire d'Electronique Générale (LEG) de l'EPFL a une longue expérience dans la conception de circuits analogiques et dans la modélisation des composants électroniques. Il a réalisé un outil d'aide à la conception de circuits intégrés analogiques. Ce dernier s'appelle PAD

(Procedural Analog Design) [1-3]. En plus de son rôle d'aide à la conception, PAD fait partie intégrante de la formation des étudiants de la section de Génie Electrique et Electronique de l'EPFL dans le domaine de la conception de circuits. Ses travaux sont financés par le Fond d'Innovation pour la FOrmation (FIFO) de l'EPFL

## PAD (Procedural Analog Design)

Basé sur une approche interactive d'aide à la conception de circuits analogiques, PAD propose une nouvelle méthodologie claire et didactique dédiée au dimensionnement de cellules analogiques et à la génération de leur plan de masque (layout). Une démarche systématique qui relie l'expérience d'un concepteur «expert» basée sur la théorie de circuits analogiques est implémentée afin de fournir une assistance à l'utilisateur. De plus, les éléments d'interface graphique permettent la visualisation instantanée des dépendances entre les paramètres ainsi que la possibilité de découvrir de façon interactive les compromis entre les paramètres importants. Le concepteur obtient donc une compréhension intuitive du comportement de son circuit. PAD est un outil qui guide l'utilisateur pour choisir les paramètres optimaux pour des spécifications données et permet de diminuer les efforts nécessaires pour découvrir des compromis. Ceci aide à la compréhension de phénomène physique, optimise le temps de développement des cellules analogiques et favorise l'apprentissage. PAD peut également être utilisé en interaction avec un simulateur de circuits, il permet alors de d'optimiser le nombre de simulations.

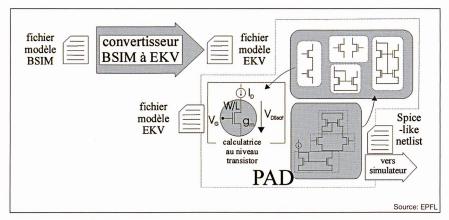

En se basant sur une approche de conception au niveau du transistor, PAD intègre une calculatrice qui utilise l'ensemble des équations du modèle EKV du MOS [4, 5]. Cette calculatrice est capable d'explorer les relations physiques complexes et de fournir des solutions pour des ensembles des paramètres électriques (Figure 1).

Le modèle EKV, développé à l'EPFL, est un modèle particulièrement puissant

Figure 1 Structure de PAD

et adapté à la conception de circuits analogiques. Il permet une bonne précision, tout en possédant un petit nombre de paramètres. Ce modèle, fondé sur le comportement physique du transistor MOS, facilite la compréhension intuitive du comportement de chaque cellule analogique. De plus, il permet de trouver facilement des solutions pour des ensembles de paramètres d'entrée sans utiliser des méthodes numériques complexes. Finalement, tous les paramètres importants pour la conception, tels que: facteur d'inversion, tension de saturation, tension de pincement, tension d'Early, paramètres petits signaux, capacités parasites, rapport  $g_m/I_D$  et TEF (rapport  $g_m/I_D$  normalisé) peuvent être calculés sans difficulté.

PAD contient une bibliothèque de structures analogiques: miroir de courant, miroir de courant cascodé, paire différentielle, étage cascode, étage cascode re-

plié. Grâce au modèle EKV, pour chaque structure, un ensemble de paramètres (par exemple: paramètres petits signaux, paramètres de polarisation, capacités parasites, vitesse, etc.) est instantanément évalué et affiché. De même, des paramètres spécifiques, tels que: un offset d'entrée pour une paire différentielle, un appariement des courants pour le miroir de courant, une résistance de sortie, une capacité d'entrée, la somme des capacités parasites de certains nœuds, sont aussi calculés et affichés. Après chaque intervention de l'utilisateur, l'ensemble de ces paramètres est remis à jour. Ceci permet au concepteur d'analyser le comportement de ses structures dans un environnement imposé par le circuit et de découvrir rapidement les dépendances et les compromis à effectuer. La génération automatique de plan de masque (layout) est aussi disponible pour les structures appariées,

gain, bruit, offset, stabilité, dynamique à la sortie

miroir de courant - bias 1

A Voc.

SR,

CMR\*,

PSRR\*

GBW,

Bain,

Bruit,

Offset,

stabilité

miroir de courant - bias 2

Source: EPFL

Source: EPFL

Figure 2 OTA à cascode replié

par exemple: miroir de courrant, paire différentielle, etc. Les layouts générés sont exportées dans un format standard (CIF).

En plus de la bibliothèque de structures analogiques, PAD propose une démarche pour la conception procédurale de cellules analogiques plus complexes, basée sur la subdivision de cellules complexes en un ensemble de structures de base. Un scénario pas à pas, sans règle de conception imposée et qui contient les conseils et les directives basés sur l'expérience et la théorie, est proposé pour diverses topologies d'amplificateurs opérationnels. Ceci permet de découvrir les meilleurs compromis et d'évaluer les performances. Une visualisation de tous les paramètres, en utilisant des éléments d'interface graphique appropriés, rend l'utilisation de PAD très simple et intuitive. L'utilisateur suit une procédure de conception guidée avec beaucoup de liberté d'action et découvre d'une façon interactive quels sont les meilleurs paramètres de son circuit.

### Convertisseur BSIM à EKV (BSIM2EKV)

Malheureusement, les paramètres du modèle EKV ne sont disponibles que pour un nombre restreint de concepteurs, étant donné que le modèle BSIM est considéré aujourd'hui comme un standard industriel [6, 7] (les versions 3.2 et 3.3). Malheureusement, BSIM a besoin d'un grand nombre de paramètres et sa complexité limite fortement une compréhension intuitive des phénomènes électriques dans un circuit.

Afin d'élargir l'utilisation de PAD aux concepteurs de circuits analogiques qui utilisent le modèle BSIM, un outil d'extraction et conversion des paramètres EKV à partir de BSIM a été développé [8] (Figure 1).

La version actuelle du convertisseur consiste en un programme autonome (Figure 1), qui reçoit en entrée le fichier de paramètres du modèle BSIM (version 3.3) et génère un fichier pour le modèle EKV (version 2.6). Ce dernier contient les paramètres suivants: les paramètres intrinsèques de modèle, les paramètres de température, les paramètres du bruit, les capacités de recouvrement de grille, les capacités de jonction. Le fichier ainsi généré peut être aussi bien utilisé par un simulateur classique de type SPICE ou directement par PAD.

Le concept de base de BSIM2EKV consiste à simuler à l'aide d'un simulateur de type SPICE, utilisant le modèle BSIM, certaines courbes caractéristiques.

Ces courbes sont indispensables à la procédure d'extraction. Les résultats ainsi obtenus sont traités par l'algorithme d'extraction qui se base sur la méthodologie décrite dans [9]. Dans ce travail, une nouvelle démarche est proposée. Elle se distingue par l'utilisation d'une séquence précise d'opérations consistant à comparer certains points caractéristiques des deux modèles BSIM et EKV. Cette démarche évite une comparaison exhaustive entre l'ensemble des courbes simulées. De plus, les paramètres du modèle sont déterminés avec un minimum de propagation d'erreur et un respect du fondement des deux modèles. Pour chaque conversion des paramètres, l'ensemble des simulations effectuées est mis à la disposition de l'utilisateur. Les courbes caractéristiques d'inversion du transistor MOS (inversion forte, modérée, faible) et les régimes différents (linéaire, saturé) sont présentés afin d'évaluer la qualité des résultats et de donner une compréhension visuelle des différences possibles. Un fichier qui décrit la démarche et le déroulement de la conversion, ainsi que les erreurs moyennes calculées pour l'ensemble des courbes est aussi généré.

## Exemple de conception d'un amplificateur à l'aide PAD

Pour mieux comprendre PAD et son environnement, un exemple concret est illustré dans ce paragraphe. Il s'agit d'un amplificateur à transconductance (OTA) utilisant un étage à cascode replié, présenté sur la figure 2. Pour chaque transistor de cette topologie, PAD permet de trouver les meilleurs combinaisons des paramètres (dimensions géométriques, courant de polarisation, transconductances, tension de saturation, bruit équivalent, fréquence de transition, etc.) afin d'obtenir les valeurs demandées dans le cahier des charges de cet amplificateur (gain, linéarité, dynamique d'entrée, dynamique de sortie, bruit, vitesse, consommation, etc.).

Ce genre de circuit est généralement abordé par les experts de conception en le subdivisant en un ensemble de cellules de base (miroir de courant, paire différentielle, etc.). Ensuite commence la tâche de dimensionnement proprement dit de chacune des structures selon des critères qui trouvent leurs racines aussi bien dans les lois physiques du transistor MOS que dans la théorie de circuits.

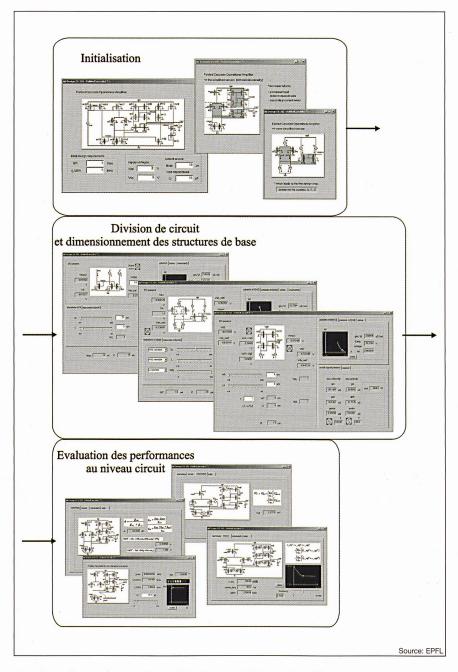

Cette même démarche est intégrée dans PAD et détaillée ci-dessous sur l'exemple de la conception de l'OTA (Figure 3). L'ordre des opérations effectuées par PAD est le suivant:

Figure 3 La séquence de conception procédurale pour un OTA à cascode replié

- Initialisation des paramètres du modèle EKV et spécification du cahier des charges: slew rate, produit gain x bande passante, tension d'alimentations courant de polarisation I<sub>BIAS</sub> et capacité de charge C<sub>L</sub>.

- 2. Subdivision de la topologie en structures analogiques de base:

- miroir de courant p (bias 1)

- miroir de courant n (bias 2)

- étage à cascode replié

- miroir de courant cascodé

- cellule de polarisation pour miroir de courant cascodé (bias 3)

- cellule de polarisation pour étage à cascode replié (bias 4)

3. Ensuite, une procédure de conception individuelle de chaque structure est proposée à l'utilisateur. Cette procédure s'articule sur un ensemble d'équations décrivant le comportement du circuit.

La procédure de conception est prédéfinie et basée sur une expérience de conception acquise au Laboratoire d'Electronique Générale. Elle permet de comprendre l'influence de chaque structure de base sur l'ensemble de circuit. Les effets des modifications des paramètres sont calculés et affichés instantanément.

Durant toute la procédure de conception, l'utilisateur peut observer les perfor-

#### Systèmes intégrés

mances acquises et les comparer avec les spécifications initiales. A la fin, un résumé de tous les paramètres importants est affiché avec la possibilité de faire différentes analyses complexes, comme par exemple: tracer la fonction de transfert du circuit, évaluer son bruit équivalent, observer son offset, etc. Le résultat final est un circuit optimisé, prêt pour la simulation. La procédure décrite peut être répétée plusieurs fois en interaction avec le simulateur afin d'effectuer un ajustement final.

#### Conclusion

PAD intègre une méthodologie de conception basée sur une approche systématique et un modèle de transistor adapté pour la conception de circuits analogiques. Il permet aux utilisateurs de contrôler la démarche de réalisation de leurs circuits et d'optimiser le temps de conception. Il est à la fois un outil de CAO capable d'assister le concepteur et un didacticiel pour l'apprentissage de la microélectronique analogique (une version d'évaluation de PAD est accessible sur le site: http://legwww.epfl.ch/CSL/).

#### Références

- D. Stefanovic, M. Kayal, M. Pastre, V. Litovski: Procedural Analog design (PAD) Tool. Fourth International Symposium on Quality Electronic Design, ISOED 2003, pp. 313–318.

- ISQED 2003, pp: 313–318

M. Kayal, D. Stefanovic, M. Pastre: CMOS Analog Design Educational Tool. 5th European Workshop on Microelectronics Education, Lausanne, Switzerland, 15–16 April 2004, Kluwer Academic Publishers, pp: 133–138.

- [3] D. Stefanovic, M. Kayal, M. Pastre: PAD: un outil de CAO pour la conception procédurale de cellules intégrées analogiques. TAISA'03 4ème colloque sur le Traitement Analogique de l'Information, du Signal et ses Applications, Louvain-la Neuve, Belgique, 25–26 septembre 2003.

- [4] C. Enz F. Krummenacher and E. A. Vittoz: An Analytical MOS Transistor Model Valid in All Regions of Operation and Dedicated to Low-Voltage and Low-Current Applications. J. Analog Integrated Circuits and Signal Processing, Vol. 8, July 1995, pp: 83–114.

- [5] M. Bucher, C. Lallement, C. Enz, F. Théodoloz and F. Krummenacher: The EPFL-EKV MOSFET Model Equations for simulation. Version 2.6, Technical Report, EPFL, July 1998, available on-line: http:\\ legwww.epfl.ch/EKV

- [6] Y. Cheng, C. Hu: MOSFET modeling & BSIM3 user's guide, 1999, Kluwer Academic Publishers Group

- [7] http://www-device.eecs.berkeley.edu/~bsim

- [8] D. Stefanovic, F. Krummenacher, M. Pastre, M. Kayal: BSIM2EKV: un outil pour la conversion automatique des paramètres du modèle BSIM aux paramètres du modèle EKV. TAISA'04 5ème colloque sur le Traitement Analogique de l'Information, du Signal et ses Applications. Lausanne, Suisse, 30 septembre et 1 octobre 2004, pp. 85–88

- [9] M. Bucher, C. Lallement, C.C. Enz: An efficient parameter extraction methodology for the EKV MOST model. International Conference on Microelectronic Test Structures, ICMTS 1996, 25–28 March 1996, pp. 145–150

#### Informations sur les auteurs

Danica Stefanovic, diplôme et master en électricité de la Faculté d'Electronique, Université de Nis (Serbie et Monténégro) en 2000 et 2003, est actuellement assistante doctorante au Laboratoire d'Electronique Générale (LEG). Les thèmes de sa recherche sont: les méthodologies et les outils de conception de circuits analogiques.

EPFL, STIJIMM /LEG1, 1015 Lausanne, danica.stefanovic@epfl.ch

Prof. Dr. *Maher Kayal* a effectué ses études et sa thèse de doctorat à l'Ecole Polytechnique Fédérale de Lausanne dans la section d'électricité où il est professeur depuis l'an 2000. Il dirige un groupe de chercheurs dans le domaine de la conception de circuits intégrés. Il est auteur de plus de 50 publications scientifiques et de plusieurs brevets.

EPFL, STIJIMM ILEG1, 1015 Lausanne, maher.kayal@epfl.ch

Marc Pastre a terminé ses études d'ingénieur en informatique à l'EPFL, en 2000. Depuis, il est assistant doctorant au Laboratoire d'Electronique Générale (LEG). Son travail de recherche s'articule autour d'interfaces analogiques pour capteurs, de circuits numériques de compensation automatiques et d'outils CAO pour circuits mixtes analogiques-numériques. EPFL, STIIIMM ILEG1, 1015 Lausanne,

EPFL, STIIIMM ILEG1, 1015 marc.pastre@epfl.ch

## Das Design analoger integrierter Schaltungen

#### PAD: ein didaktisches Design-Tool

Heute werden immer mehr analoge und digitale Schaltungen auf demselben Stück Silizium integriert. Die meisten CAE-Tools sind allerdings auf die digitalen Schaltungen optimiert. PAD ist ein didaktisches Design-Tool für analoge integrierte Schaltungen, das mit einem für diesen Zweck optimierten Modell des MOS-Transistors arbeitet.