**Zeitschrift:** bulletin.ch / Electrosuisse

Herausgeber: Electrosuisse

**Band:** 94 (2003)

Heft: 7

**Artikel:** Mémoire dynamique à 1 transistor

Autor: Fazan, Pierre / Nagoga, Mikhail / Okhonin, Serguei

**DOI:** https://doi.org/10.5169/seals-857540

## Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 09.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Mémoire dynamique à 1 transistor

# Un nouveau concept de mémoire à semi-conducteur de type DRAM

La surface est une des majeures restrictions quant à la production des mémoires dynamiques de plus en plus performantes. Dans cet article un nouveau concept de mémoire à semi-conducteur de type Dynamic Random Access Memory (DRAM) pour des applications de stockage de masse ou pour des applications de type mémoire embarquées (embedded DRAM ou eDRAM) sera introduit. En exploitant les effets de substrat flottant de transistors MOS (Metal Oxyde Semiconductor) partiellement désertés intégrés sur substrat de type silicium sur isolant (SOI), une cellule DRAM sans condensateur peut être réalisée. Un seul transistor permet de stocker et d'amplifier l'information. Une telle cellule mémoire a une surface deux fois plus petite que la surface d'une cellule DRAM courante et peut être fabriquée avec des procédés de fabrication traditionnels.

Les fabricants de mémoires dynamiques DRAM et eDRAM font face à des difficultés majeures pour réduire la surface des cellules élémentaires nécessaires pour les applications futures où les dimensions minimales définies sur les

Pierre Fazan, Mikhail Nagoga, Serguei Okhonin

circuits ne cessent de décroître. A l'heure actuelle, toutes les mémoires DRAM et eDRAM incorporent des cellules constituées d'un transistor à effet de champ et d'un condensateur (cellule dite 1T/1C, introduite par R. Dennard en 1967 [1]).

Si l'on définit d comme étant la dimension minimale d'une géométrie gravée sur un circuit, avec la cellule 1T/1C, une cellule DRAM occupe une surface minimale de 8 à 12  $d^2$  [2] alors qu'une cellule eDRAM recouvre 18 à 26  $d^2$  [3, 4]. Le problème majeur pour miniaturiser les cellules 1T/1C réside dans l'intégration du condensateur, qui doit fournir une capacité de 30 fF<sup>1</sup>) quelle que

soit la taille de la cellule. Une telle contrainte a forcé les fabricants à intégrer des condensateurs à trois dimensions, et pour des technologies ayant *d* inférieur à 100 nm, fabriquer de telles structures devient pratiquement impossible.

Les transistors à effet de champ de type partiellement déserté, intégrés sur substrats de type SOI<sup>2)</sup> présentent ce que l'on appelle des «effets de substrat flottant». En effet, la région du transistor située sous le canal peut se charger lors de l'opération du dispositif. Ces effets ont plutôt été considérés comme parasites jusqu'à présent [5].

Pour réaliser une cellule mémoire de type DRAM simple et dense, le laboratoire d'Electronique Générale de l'EPFL à Lausanne (LEG) et l'entreprise lausannoise Innovative Silicon S.A. (ISi) ont proposé récemment d'utiliser un transistor MOS SOI unique et d'exploiter ces effets de substrat flottant [6,7]. Cette cellule – appelée cellule 1T-DRAM – intègre un seul dispositif. Cet article décrit d'abord ce concept et présente ensuite certains résultats obtenus lors du

test de ce concept, les principes de fonctionnement de la cellule ainsi que les applications possibles seront présentés.

### **Description du concept**

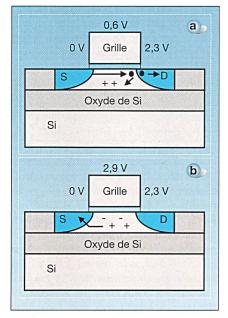

La cellule 1T-DRAM proposée est donc un simple transistor NMOS3) ou PMOS<sup>4)</sup>, intégré sur un substrat de type SOI. En exploitant la charge électrique créée sous le canal de tels transistors, il est possible de réaliser une mémoire binaire, un excès de charge positive ou négative étant utilisé pour définir les états «1» ou «0» de la mémoire. Dans le cas d'un transistor NMOS, en appliquant une tension positive sur le drain du dispositif, un excès de charge positive peut être créé sous le canal par le mécanisme d'ionisation par impact. La présence de cette charge augmente le courant  $I_{ds}^{5)}$  du transistor, définissant l'état «1». L'application d'une tension négative sur le drain est utilisée pour créer une charge nette négative sous le canal. Cette charge a pour effet de réduire le courant  $I_{ds}$  du transistor, définissant l'état «0». Les deux états «1» et «0» sont illustrés à la fi-

L'information est lue en comparant les courants  $I_{ds}$  de la cellule sélectionnée au

Figure 1 Programmation de la mémoire a: création d'une charge positive sous le canal; b: création d'une charge négative sous le canal; D: drain; S: source

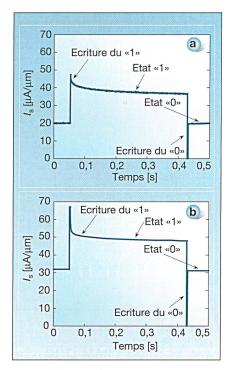

Figure 2 Courant en fonction du temps Illustration des 2 niveaux de courant obtenus par programmation de la cellule; a: mesure: b: simulation

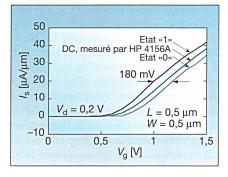

Figure 3 Caractéristique courant-tension d'un transistor NMOS utilisé comme cellule mémoire

L = Length; W =Width

courant d'une cellule de référence à l'aide d'un amplificateur travaillant en mode courant [8].

La lecture se fait à faible tension de drain afin de ne pas affecter l'état de la cellule. Pendant un temps correspondant au temps de rafraîchissement de la cellule, lire la cellule ne perturbe pas l'information stockée. Cet effet, qui n'existe pas pour les cellules DRAM classiques, permet de réduire considérablement la taille des circuits de lecture de l'information. Les mesures de courant sont aussi facilement vérifiées par simulations numériques.

#### Présentation des mesures

Pour démontrer le concept, des transistors MOS SOI partiellement désertés fabriqués avec des dimensions minimales<sup>6)</sup> d de 250 nm et 130 nm ont été utilisés<sup>7)</sup>. Les procédés de fabrication utilisent une technologie de type logique et les substrats sont de type «Bonded SOI». Le silicium a une épaisseur de 100 nm, et l'oxyde de silicium enterré est de 400 nm.

Lors des tests faits par le LEG et ISi, la source du transistor est connectée à la masse à travers une résistance de  $50~\Omega$  et un oscilloscope digital est utilisé pour mesurer le courant. Un analyseur de paramètres<sup>8)</sup> et un générateur d'impulsions sont utilisés pour caractériser la rétention de l'information.

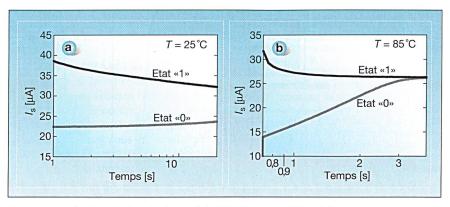

La figure 2 illustre l'évolution du courant du transistor  $I_s$  dans le cas d'un dispositif de type N, fabriqué avec une technologie de 250 nm. L'état «1» est écrit avec les conditions suivantes:  $V_d = 1,5 \,\mathrm{V}$ ,  $V_g^{(9)} = 1.0 \text{ V}$ , pulses de 1 ms. L'état «0» est écrit à  $V_d = -2.8 \text{ V}$  pendant 1 ms. La cellule est lue à  $V_d = 0.5$  V et  $V_g = 1.0$  V. La figure 3 montre la caractéristique  $I_s$  vs.  $V_g$ correspondant aux deux états. Il faut noter que même une quantité infime de charge influence le courant du transistor à cause de son effet d'amplificateur. Cette cellule 1T-DRAM est en effet une cellule que l'on nomme «cellule à gain». La figure 3 donne une fenêtre de programmation typique de 180 mV.

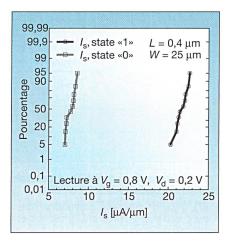

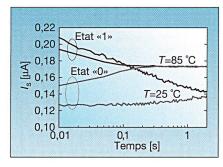

La distribution des courants mesurés en lecture est importante pour s'assurer que l'information puisse être lue et que les deux états restent différenciables. La figure 4 illustre des distributions de courant typiques. Comme on peut le voir, deux états clairement distincts sont obtenus. Dans une matrice mémoire, on peut s'attendre à ce que la distribution soit meilleure du fait de la proximité des dispositifs.

Une des caractéristiques les plus importantes à considérer pour une mémoire DRAM est la rétention de l'information. Dans un circuit de type DRAM classique,

Figure 4 Distribution des courants correspondant aux états «1» et «0»

L = Length; W =Width

chaque cellule doit être rafraîchie périodiquement pour restaurer la charge qui fuit à cause des fuites du transistor, du condensateur ou des jonctions. L'opération de rafraîchissement est effectuée ligne par ligne. Un temps de rétention suffisamment long est nécessaire pour pouvoir adresser toutes les lignes de la mémoire. Pour des applications de stockage de masse, un temps de rétention de quelques centaines de ms à 85°C est exigé. Pour des applications de type eDRAM, des valeurs bien plus faibles de l'ordre de la ms peuvent être tolérées [9] car la bande passante du circuit est nettement supérieure.

Pour son concept, le LEG et ISi ont défini le temps de rétention de l'information,  $T_c^{10}$ , comme le temps nécessaire pour que la moitié de la charge stockée dans le substrat flottant disparaisse. Les figures 5 et 6 montrent que la cellule 1T-DRAM a des valeurs de  $T_c$  de quelques secondes à 25 °C et supérieures à 1 sec à 85 °C pour de grands dispositifs. Ces valeurs sont réduites à 15–30 ms à 85 °C

Figure 5 Caractéristiques de rétention d'une cellule 1T-DRAM sous conditions de lecture constante a: à 25 °C; b: à 85 °C pour des dispositifs SOI de type N, ayant des dimensions W/L = 25/10  $\mu$ m et intégrés en technologie 250 nm

Figure 6 Caractéristiques de rétention d'une cellule 1T-DRAM sous conditions de lecture constante

a: à 25 °C; b: à 85 °C pour des dispositifs SOI de type N, ayant des dimensions W/L =  $10/0,2~\mu m$  et intégrés en technologie 130 nm

pour de petits dispositifs. Ces valeurs, trop faibles pour des applications de stockage de masse, sont par contre compatibles avec les contraintes posées par les mémoires de type eDRAM.

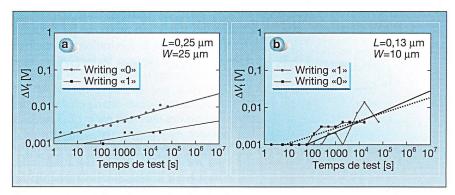

Comme on utilise la méthode de l'ionisation par impact et des tensions relativement élevées pour programmer la cellule 1T-DRAM, il faut également s'assurer que le dispositif reste fiable. En utilisant les tensions nécessaires à programmer en 3 ns, et en supposant un temps de cycle de 100 ns ou moins, une durée de vie du circuit de 10 ans correspond à plus de 3·10<sup>15</sup> cycles d'écriture ou de lecture, ou plus de 1·107 secondes d'écriture en continu. Des tests de fiabilité en continu sont utilisés pour caractériser la fenêtre de programmation. Dans ces tests, la tension de seuil  $V_{\rm th}^{11}$  de la cellule est enregistrée en fonction du temps. Des extrapolations permettent de prédire le comportement au voisinage de 1·107 secondes. La figure 7 montre que l'on s'attend à des variations de tension de seuil inférieures à 20 mV, pour des tech-

Figure 7 Variation de la tension de seuil en fonction du temps

a: pour des dispositifs de 250 nm; b: pour des dispositifs de 130 nm, lors de tests continus simulant la programmation de «1» et de «0». L = Length; W =Width

nologies de 250 nm ou 130 nm de dimensions minimales. Cela correspond à moins de 10% de la largeur de la fenêtre de programmation du point mémoire, offrant une marge suffisante pour une fiabilité de 10 ans.

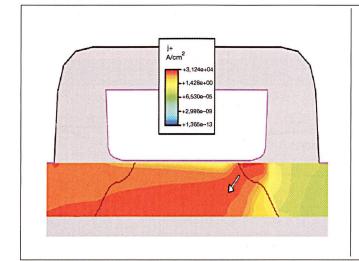

# Résultats des simulations numériques

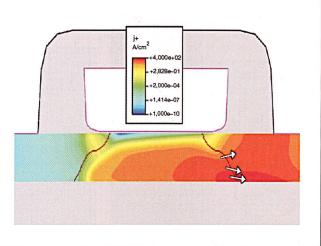

Le comportement de la cellule présenté ci-dessus se simule aisément en utilisant des outils de simulation TCAD12) disponibles dans le commerce. L'état «1» est écrit par ionisation par impact quand le transistor est enclenché, alors que l'état «0» est écrit par extraction de trous en polarisant la jonction drain/substrat en direct. Les figures 8 et 9 montrent, par simulation, le courant de trous chargeant ou déchargeant le substrat flottant lors de la programmation d'un «1» ou d'un «0». Pouvoir simuler le comportement de la cellule 1T-DRAM facilite ensuite son optimisation ou l'extension du concept à d'autres architectures (transistors SOI à double grille, transistors complètement désertés, etc.).

## **Applications**

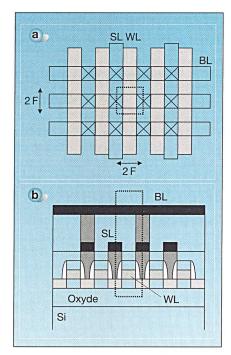

Dans les mémoires de stockage de masse, les cellules DRAM 1T/1C occupent une surface de 8 à  $12\,d^2$ . Maintenir ce concept pour les technologies futures est de plus en plus difficile car le condensateur ne se miniaturise pas. Pour aller à des dimensions d inférieures à 100 nm, l'industrie a besoin de nouveaux concepts. Avec un dessin approprié la cellule 1T-DRAM du LEG/ISi devrait permettre d'atteindre une surface de  $4\,d^2$ . Cette amélioration de surface d'un facteur 2 peut être obtenue en partageant les contacts de source et drain de cellules voisines, comme illustré à la figure 10.

Un point mémoire est donc obtenu par l'intersection de 2 lignes perpendiculaires: une ligne de mot (Word Line, WL) connectant les grilles des transistors et une ligne de bit (Bit Line, BL) qui connecte leurs drains. Dans le dessin de

Figure 8 Courant de trous lors de l'écriture de l'état «1» Ce cas est simulé avec  $V_d$  = 2 V,  $V_g$  = 0,6 V et  $V_s$  = 0 V

Figure 9 Courant de trous lors de l'écriture de l'état «0» Ce cas est simulé avec  $V_d = -1$  V,  $V_q = 0,6$  V et  $V_s = 0$  V

Figure 10 Dessin et coupe d'une cellule 1T-DRAM de 4  $d^2$

a: dessin; b: coupe; BL: Bit Line (ligne de bit); SL: Source Line (ligne de source); WL: Word Line (ligne de mot)

la figure 11, des lignes de source (Source Line, SL) parallèles aux WL servent à connecter entre elles toutes les sources qui seront mises à la masse en périphérie de la matrice. Avec un tel concept, aucun condensateur n'est nécessaire. La cellule 1T-DRAM peut donc être miniaturisée aussi longtemps que le transistor l'est. Ce concept devrait donc permettre aux mémoires DRAM de s'étendre bien en dessous de 100 nm, probablement jusqu'à

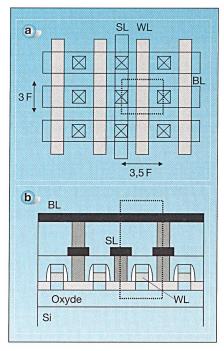

La demande de mémoires de type eDRAM est en pleine croissance car les avantages de telles puces au niveau des performances sont nombreux [9, 10, 11]. En effet, une puce eDRAM permet de réaliser un système complet sur un seul circuit, réalisant ainsi des gains considérables en surface, volume, coût et performances (bande passante). En général de telles puces sont réalisées avec des technologies utilisées pour fabriquer des microprocesseurs. On parle dans ce cas de technologie de type logique. Avec une cellule 1T/1C, intégrer un condensateur ajoute jusqu'à 7 niveaux de masques et jusqu'à 25% de coût supplémentaire lors de la fabrication du circuit [10]. Les technologies de type logique vont sous peu migrer vers des substrats de type SOI pour des considérations de consommation d'énergie et de performance [12].

Figure 11 Dessin et coupe d'une cellule 1T-DRAM de 10,5 d<sup>2</sup> de type eDRAM

a: dessin; b: coupe; BL: Bit Line (ligne de bit); SL: Source Line (ligne de source); WL: Word Line (ligne de mot)

La cellule 1T-DRAM offre donc dans ce domaine d'application une solution élégante car elle se situe au point de convergence de l'évolution des technologies tant DRAM que logique. Des cellules eDRAM 1T/1C occupent typiquement une surface de 18 à 26  $d^2$ . Avec le concept 1T-DRAM une surface de 9 à  $13 d^2$  peut être obtenue. Cela correspond à un gain d'un facteur 2 sur la taille du point mémoire. Un dessin de cellule eDRAM est présenté à la figure 11. Il faut noter qu'un gain de surface du circuit supérieur à 2 peut être atteint car les circuits de décodage et d'amplification peuvent être réduits si l'on exploite le fait que la lecture de l'information est non destructive.

#### Conclusion

Une cellule DRAM à un seul transistor est proposée. Elle est réalisée en exploitant les effets de substrat flottant de transistors SOI et ne nécessite aucun matériau nouveau. Un excès de charges positives ou négatives sous le canal sert à écrire les états «1» ou «0». Ce concept est idéal pour miniaturiser les mémoires DRAM de stockage de masse ou les mémoires eDRAM. La surface de la cellule de base est deux fois plus petite que la surface d'une cellule classique. La caractérisation par le LEG et par ISi, ef-

fectuée pour des dimensions de 250 nm et 130 nm, montre qu'un tel concept satisfait la plupart des critères de performance nécessaires pour de telles applications.

#### Références

- R. H. Dennard: Field effect transistor memory. US Patent 3.387.286, 4 juin, 1968.

- [2] H. S. Jeong, W. S. Yang, Y. S. Hwang et al.: Highly manufacturable 4Gb DRAM using 0,11 µm DRAM technology. IEDM Tech. Digest, pp. 353-356, 2000.

- [3] M. Takeuchi, K. Inoue, M. Sakao et al.: A 0,15 μm logic based embedded DRAM technology featuring 0,425 μm<sup>2</sup> stacked cell using MIM capacitor. Symp. on VLSI Tech. Tech. Digest, p. 33, 2001.

- [4] IBM Embedded DRAM web site: http://www.chips.ibm.com.

- [5] M. Yoshimi, M. Terauchi, A. Nishiyama et al.: Suppression of the floating body effect in SOI MOSFET's by the band gap engineering method using a Si<sub>1-x</sub> Ge<sub>x</sub> source structure. IEEE Trans. Electron Devices, Vol. 44, pp. 423–430, 1997.

- [6] S. Okhonin, M. Nagoga, J. M. Sallese, P. Fazan: A SOI capacitor-less 1T-DRAM concept. Proceedings of the IEEE International SOI Conf., pp. 153–154, 2001.

- [7] S. Okhonin, M. Nagoga, J. M. Sallese, P. Fazan: A capacitor-less 1T-DRAM cell. IEEE Electron Device Letters, Vol. 23, pp. 85–87, 2002.

[8] T. N. Blalock, R. C. Jaeger: A high speed clamped

- [8] T. N. Blalock, R. C. Jaeger: A high speed clamped bit line current mode sense amplifier. IEEE J. Solid State Circuits, Vol. 26, pp. 542–547, 1991.

- [9] M. Hamada, K. Inoue, R. Kubota et al.: A high performance 0,18 μm merged DRAM/logic technology featuring 0,45 μm² stacked capacitor cell. IEDM Tech. Digest, pp. 45–48, 1999.

- [10] S. S. Iyer, H. L. Kalter: Embedded DRAM technology: opportunities and challenges. IEEE Spectrum, pp 56–64, April 1999.

- [11] M. Yoshida, K. Asaka, Y. Hoshino et al.: An embedded 0,405 μm<sup>2</sup> stacked DRAM technology integrated with high performance 0,2 μm CMOS logic and 6 level metallization. IEDM Tech. Digest, pp. 41–44, 1999.

- [12] M. Pella, W. Maszara, S. Sundararajan et al.: Advantages and challenges of high performance logic on SOI. Proceedings of the IEEE International SOI Conf., pp. 1–4, 2001.

## Informations sur les auteurs

Prof. *Pierre Fazan* est professeur titulaire du Laboratoire d'Electronique Générale de l'Ecole polytechnique fédérale de Lausanne (EPFL), CH-1015 Lausanne, depuis 1997. Il est co-fondateur de l'entreprise Innovative Silicon S.A., mise sur pied afin de promouvoir le concept de mémoire 1T-DRAM. Pierre Fazan a plus de 20 ans d'expérience dans le domaine de la technologie des semiconducteurs et est co-inventeur du concept 1T-DRAM.

Contact: pierre.fazan@epfl.ch

D' Serguei Okhonín est chef de projet au Laboratoire d'Electronique Générale de l'Ecole polytechnique fédérale de Lausanne (EPFL), CH-1015 Lausanne, depuis 1994. Il est co-fondateur de l'entreprise Innovative Silicon S.A., mise sur pied afin de promouvoir le concept de mémoire 1T-DRAM. Serguei Okhonin a plus de 20 ans d'expérience dans le domaine de la physique des semiconducteurs et est co-inventeur du concept 1T-DRAM.

Contact: serguei.okhonin@epfl.ch

**Mikhail Nagoga** est chercheur au Laboratoire d'Electronique Générale de l'Ecole polytechnique fédérale de Lausanne (EPFL), CH-1015 Lausanne, depuis 1994. Il a plus de 20 ans d'expérience dans le do-

maine de la caractérisation de dispositifs semiconducteurs et l'automatisation de mesures complexes. Contact: mikhail.nagoga@epfl.ch

- <sup>1</sup> fF: f 10<sup>-15</sup> F (signifie femto Farad)

- <sup>2</sup> SOI: Silicon on Insulator

- <sup>3</sup> NMOS: negative-channel metal-oxide semiconductor

- <sup>4</sup> PMOS: positive-channel metal-oxide semiconductor

- <sup>5</sup> Index d: Drain; index s: Source

- <sup>6</sup> Distances minimales de gravure sur le circuit

- <sup>7</sup> Les dispositifs ont été fournis par le Laboratoire d'Electronique et de Technologies de l'Information (LETI, http://www-leti.cea.fr) de Grenoble et par l'institut Interuniversity Microelectronic Center (IMEC, http://www.imec.be) de Leuven en Belgique.

- <sup>8</sup> Analyseur de paramètres utilisé: HP4156A

- 9 Index g: Grille

- $^{10}$  Index c: c signifie «critique»;  $T_{\rm c}$  est le temps de rétention critique

- 11 Index th: threshold

- 12 TCAD: Technology Computer Aided Design

# **Dynamischer Speicher mit 1 Transistor**

# Neues Konzept für DRAM-Halbleiterspeicher

Der Herstellung immer leistungsfähigerer dynamischer Speichermodule werden vor allem durch die benötigte Fläche enge Grenzen gesetzt. Der vorliegende Bericht zeigt ein neues Konzept für dynamische Halbleiterspeicher vom Typ Dynamic Random Access Memory (DRAM) für Massenspeicheranwendungen bzw. integrierte Speicher (embedded DRAM bzw. eDRAM). Die «Floating Substrate»-Eigenschaften von MOS-Transistoren (Metal Oxyde Semiconductor, partically depleted) auf SOI-Substraten (Silicon on Insulation) erlauben es, eine kondensatorlose DRAM-Zelle herzustellen. Ein einziger Transistor ist dabei in der Lage, die Information zu speichern und zu verstärken. Eine solche Speicherzelle weist gegenüber einer herkömmlichen DRAM-Zelle nur die halbe Fläche auf und lässt sich mit traditionellen Fertigungsverfahren herstellen.

# Buchbinde-Angebot Bulletin SEV/VSE

Mit einem Sammelband des Bulletins SEV/VSE können Sie Ihre Bulletins SEV/VSE übersichtlich und kompakt aufbewahren.

Gerne übernehmen wir das Einbinden Ihrer Fachzeitschrift.

#### Bestellung

| Anzahl Ja |                            | Jahrgang | Pre | Preis  |  |

|-----------|----------------------------|----------|-----|--------|--|

|           | Einband inkl. Einbanddecke | 2002     | Fr. | 109.20 |  |

|           | Einband inkl. Einbanddecke |          | Fr. | 109.20 |  |

|           | Einbanddecken/Jahrgang     | 2002     | Fr. | 43.20  |  |

|           | Einbanddecken/Jahrgang     |          | Fr. | 43.20  |  |

|           |                            |          | Fr. |        |  |

Exkl. Porto, Verpackung +MwSt.

Die Bulletins des Jahrgangs 2002 werden zusammen mit einer gedruckten Version des Jahresinhaltsverzeichnisses gebunden.

Bei Bestellung von Einbanddecken des Jahrgangs 2002 wird ein gedrucktes Exemplar des Jahresinhaltsverzeichnisses gratis mitgeliefert.

Bitte senden Sie Ihre Bulletins mit dem Vermerk «Bulletin SEV/VSE» an:

Buchbinderei Burkhardt AG Isenrietstrasse 21, 8617 Mönchaltorf Tel. 01 949 44.59, www.bubu.ch