|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 91 (2000)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 19                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | High Density Packaging                                                                                                                                                                                                    |

| <b>Autor:</b>       | Hirt, Etienne / Schmid, Rolf                                                                                                                                                                                              |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-855599">https://doi.org/10.5169/seals-855599</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 14.12.2025

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# High Density Packaging

## Der schnelle Weg zur Miniaturisierung von Elektronik

High Density Packaging (HDP) ermöglicht eine massive Verbesserung der Eigenschaften von Elektroniksystemen. Es erlaubt nicht nur die Abmessungen zu verkleinern, sondern auch die Leistung zu steigern und die Zuverlässigkeit zu erhöhen. Da High Density Packaging nicht eine spezifische Technologie, sondern eine Sammlung verschiedenster Technologien ist, setzt ihr Einsatz ein breites Know-how voraus. Der Anwender muss nicht nur die Vorteile und Nachteile der zur Verfügung stehenden Basistechnologien kennen, er muss auch Zugang zu einem umfangreichen Netzwerk von Herstellern dieser Technologien haben. Art of Technology ist eine jener Firmen, welche die Möglichkeiten von HDP einem möglichst breiten Anwenderkreis zur Verfügung stellen wollen.

In der Mikroelektronik tätige Unternehmen führen einen Wettlauf mit der Zeit, im Bestreben, ständig kleinere, leichtere und kostengünstigere Produkte auf den Markt zu bringen. High Density Packaging(HDP)-Technologien und Multi-Chip-Module (MCM) bieten ihnen neue Möglichkeiten zur Verbesserung der Produkteigenschaften und somit zur Steigerung ihrer Wettbewerbsfähigkeit. HDP- und MCM-Technologien ermöglichen

- Reduktion der Kosten auf Systemebene

- Erhöhung der Funktionalität bei reduzierter Größe und verringertem Gewicht

- Ausnutzung der vollen Leistungsfähigkeit der eingesetzten ICs

- Reduktion der Leistungsaufnahme

- Erhöhte Zuverlässigkeit

- Einfacherer EMV- und ESD-Schutz

- Erhöhte Modularität und Wiederverwendbarkeit der Baugruppen

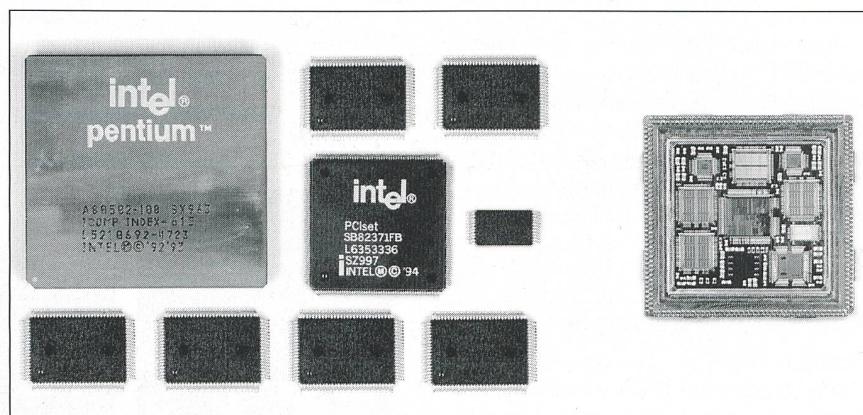

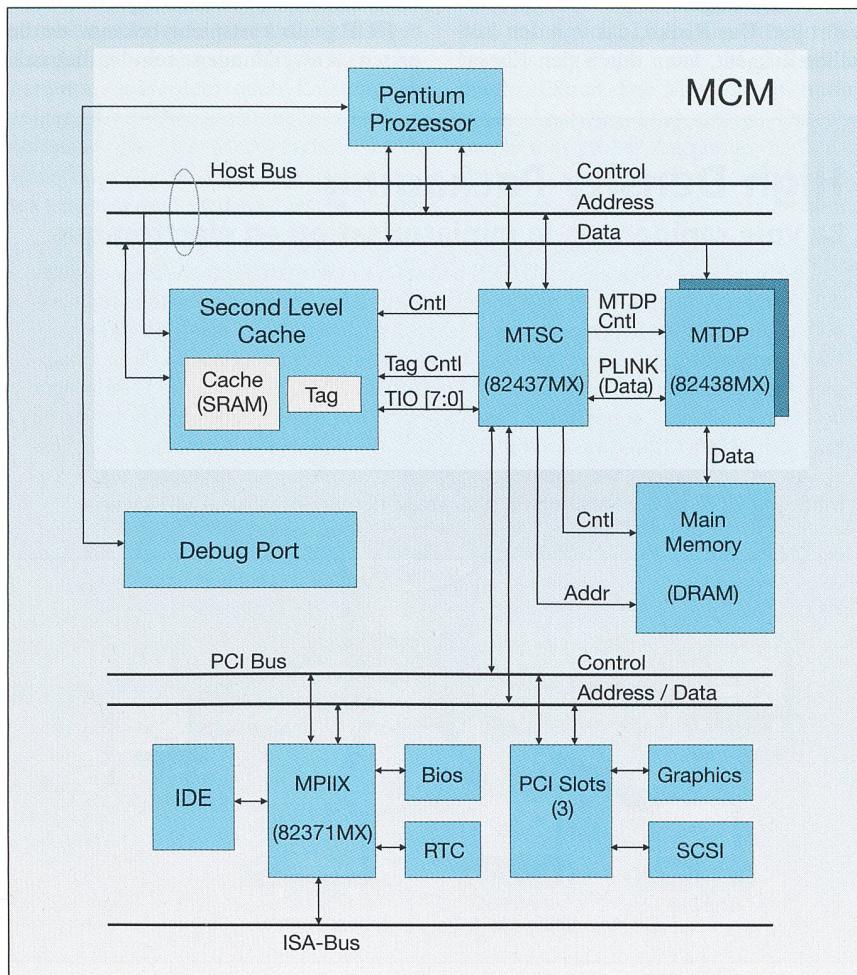

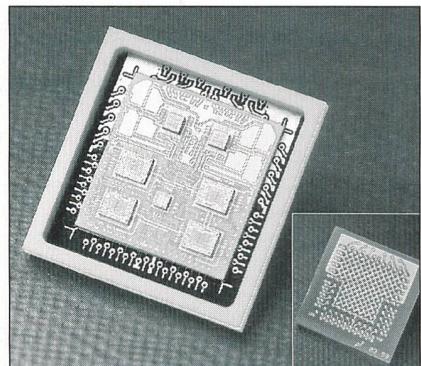

Das Potential der Größenreduktion zeigt sich am Beispiel des an der ETH Zürich entwickelten Pentium-Moduls in Bild 1. Die dabei verwendeten Technologien und

ihre Anwendungen werden in diesem Artikel beschrieben.

### High Density Packaging

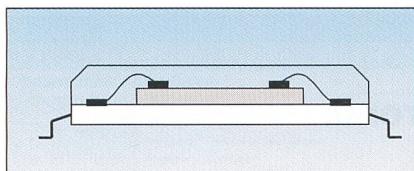

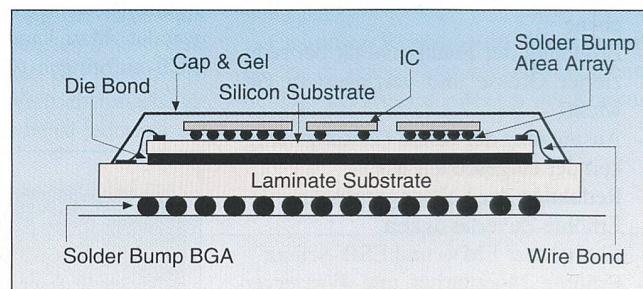

Bisher wurden die Chips einzeln in ein Gehäuse (Single Chip Package, SCP) verpackt und auf einer Leiterplatte (Printed Circuit Board, PCB) als durchkontaktiertes oder SMD-Bauteil (Surface Mounted Device, SMD) montiert (Bild 2).

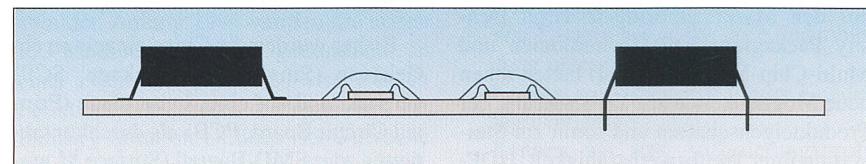

Für HDP werden die unverpackten Silizium-IC, sogenannte Bare Dies, verwendet. Man kann diese direkt auf ein PCB aufbringen (Chip on Board, COB)

(Bild 3) oder mehrere IC in ein Gehäuse verpacken (Multi Chip Package, MCP) (Bild 4) und dann auf eine Leiterplatte montieren.

Ein HDP-Modul ist entweder ein komplettes System oder ein Subsystem in einem Gehäuse, das in mehreren Geräten Verwendung findet.

Die Module werden aus Bare Dies aufgebaut, die mittels verschiedener Montagetechnologien auf hochdichten Leiterplatten, sogenannten Substraten, kontaktiert werden. Diese Technologien werden im folgenden Abschnitt beschrieben.

### HDP-Technologien

HDP steht für eine ganze Vielfalt von Technologien. Nackte IC werden auf unterschiedliche Weise miteinander verbunden.

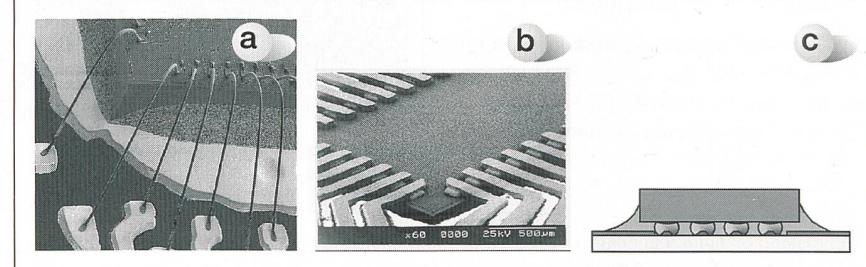

#### Drahtbonden

Dabei wird die Kontaktierung der IC mittels einzeln gezogener Drähte (Gold oder Aluminium mit Durchmessern von 12–33 µm) hergestellt (Bild 5a).

#### Tape Automated Bonding

Eine vorgefertigte einlagige Folie ermöglicht die Kontaktierung des IC in einem Arbeitsschritt (Bild 5b).

#### Flip Chip

Lotkugeln werden direkt auf die Anschlüsse des Chips aufgebracht. Der Chip

Bild 1 Pentium-Modul als Beispiel für eine Größenreduktion um den Faktor 4

Im Zentrum ist der Prozessor umrahmt vom Chipsatz und dem 2<sup>nd</sup> Level Cache. Als Schnittstelle gegen außen stehen der PCI- und der DRAM-Bus zur Verfügung.

**Adresse der Autoren**

Dr. Etienne Hirt und Rolf Schmid, Dipl.

El.-Ing. ETH, Art of Technology AG

8092 Zürich

<http://www.art-of-technology.ch>

Bild 2 Single Chip Package

wird anschliessend – Kopf nach unten – auf das Substrat gelötet (Bild 5c).

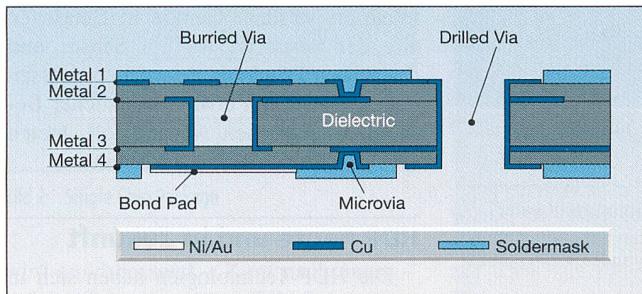

#### Substrate

Es gibt drei Arten von Substraten, deren Eigenschaften in Tabelle I zusammengefasst sind:

- Laminat-Substrate: Auf herkömmlichen Leiterplatten werden Aufbaulagen (Sequential Build Up, SBU) aufgebracht, welche mittels sogenannter Microvias (mittels Laser gebohrter oder geätzter Durchkontaktierungen) jeweils (nur) zwei übereinander liegende Leiterebenen zu verbinden erlauben

- Keramik-Substrate: Substrate auf Keramikbasis werden möglich, die vor allem für Applikationen in Umgebungen mit hohen Temperaturen oder mit grossen Wärmeverlusten interessant sind

- Dünnfilm-Substrate: Mit Technologien, welche aus der Chip- und LCD-Fertigung bekannt sind, können sehr dichte und genaue Substrate realisiert werden.

#### Designhinweise

Neben der Wahl der Technologie ist dem Design Beachtung zu schenken. Systeme müssen beim Design in Subsysteme aufgeteilt (partitioniert) werden. Dabei wird unter anderem speziell darauf geachtet, dass innerhalb eines Subsystems die gleichen oder kompatiblen Technologien verwendet werden und dass diese Subsysteme sinnvolle Baugruppen darstellen.

Aus den Möglichkeiten der unterschiedlichen Partitionierungen und der verschiedenen Technologien erwachsen damit viele Freiheitsgrade. Wenn man diese richtig nutzt, bringen die HDP-Technologien viele Vorteile. Einige werden in den nächsten Abschnitten vorgestellt.

## Applikations-Beispiele

### Pentium MCM

Bild 6 zeigt das Blockschaltbild eines Pentium-Systems. Der Kern besteht aus dem Prozessor, dem Systemkontroller (MTSC), dem DRAM-Kontroller (MTDP) und 512 kBytes 2<sup>nd</sup> Level Cache. Diese Bausteine sind über den Hostbus miteinander verbunden. MTDP und MTSC steuern den Hauptspeicher und den PCI-Bus. Über den Letzteren ist die Computer-Peripherie angeschlossen.

Der Kern des Systems (Kernmodul) wurde in HDP-Technologie aufgebaut, was eine Reduktion des Flächenbedarfs auf 25% zur Folge hatte (Bild 1). Das Kernmodul beinhaltet die Bausteine mit den meisten und schnellsten Verbindungen. Es reduziert nicht nur die Fläche eines Systems, sondern ermöglicht den Aufbau eines Pentium-Motherboards mit 4 anstatt wie bisher mit 6 bis 8 Lagen. Die Komponenten wurden als Bare Dies durch Drahtboden auf ein Dünnfilmsubstrat montiert. Dank den Designregeln von 20 µm Leiterbreite, 30 µm Abstand und 50 µm Via-Land (Kontaktierungsflächen) konnte das Modul mit nur 4 Lagen implementiert werden. Verpackt wurde das Subsystem in ein neu entwickeltes Plastic-Stud-Grid-Array-Gehäuse von 43×43 mm<sup>2</sup> mit 320 Anschlüssen, von denen 60 ausschliesslich Testzwecken dienen und auf dem Motherboard nicht verdrahtet werden müssen. Das Modul wird damit kleiner als der reine Pentiumprozessor im PGA-Gehäuse von 50×50 mm<sup>2</sup> mit fast 400 Anschlüssen.

## Art of Technology

Die Art of Technology AG wurde im Oktober 1999 als Spin-off-Firma des Institutes für Elektronik der ETH Zürich gegründet. Die Gründer beschäftigten sich am Institut seit 1995 mit den HDP-Technologien im Rahmen des EU-Forschungsprojektes Europractice und wollen nun ihr Wissen der Industrie zur Verfügung stellen. Art of Technology bietet Beratung, Machbarkeitsanalysen, Design und Layout. Zudem sorgt die Firma für die reibungslose Produktion bei Partnerfirmen.

Grössenreduktion ist aber nur ein Argument für den Einsatz von HDP. Ein weiteres Argument ist, dass mit dieser Technik, wie im folgenden Abschnitt beschrieben, die Leistungsfähigkeit der ICs voll ausgenutzt werden kann.

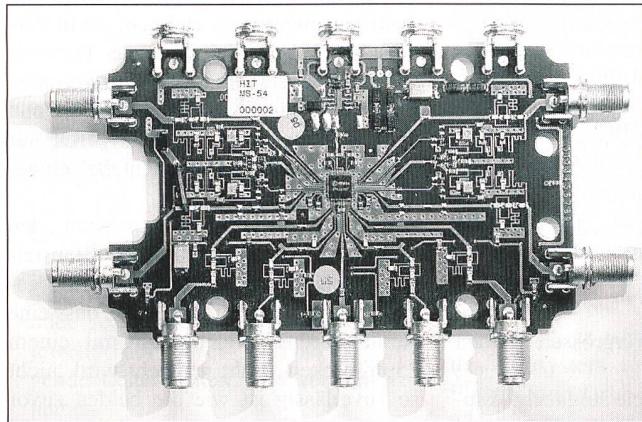

### Schalter für Satellitenempfänger

Richard Hirschmann GmbH & Co., Stuttgart, baut Schaltsysteme für Satellitenempfänger. Das Bild 8 zeigt eine Implementation mit fünf Eingängen auf der Unterseite (vier Satellitensignale und ein terrestrisches Signal) und vier Ausgängen an den vertikalen Seiten (Benutzersig-

Bild 3 Chip on Board

### Bild 4 Multi Chip Package

Bild 5 Montagetechnologien

a: Drahtboden, b: Tape-Automated-Bonden, c: Flip Chip

|                       | SBU-Laminat-Substrat         | Keramik-Substrat                          | Dünnschicht-Substrat |                                  |

|-----------------------|------------------------------|-------------------------------------------|----------------------|----------------------------------|

|                       | Hybrid                       | Cofired                                   |                      |                                  |

| Trägermaterial        | 2- oder mehrlagiger PCB-Kern | Keramik (Al <sub>2</sub> O <sub>3</sub> ) | Ungebrannte Keramik  | Silizium, Keramik, Glas, Laminat |

| Leitermaterial        | Kupfer                       | Leitpaste                                 | Leitpaste            | Aluminium, Kupfer                |

| Dielektrikumsmaterial | FR4, FR5                     | Glas                                      | Keramik              | Polymid, BCB                     |

| Leiterbreiten         | > 50 µm                      | > 125 µm                                  | > 125 µm             | > 10 µm                          |

| Leiterabstände        | > 50 µm                      | > 125 µm                                  | > 125 µm             | > 20 µm                          |

| Via-Landeflächen Ø    | > 250 µm                     | > 200 µm                                  | > 200 µm             | > 30 µm                          |

| Anzahl Lagen          | 2×3 (symmetrisch)            | 2–5                                       | bis 30               | 2–5                              |

Tabelle I Verwendete Substrate in der HDP-Technologie

nale). Das Schalten der 2,5-GHz-Eingänge wird vom Asic im Zentrum übernommen.

Bei der gewünschten Erweiterung dieses Systems auf 9 Eingänge stellte Hirschmann fest, dass es auf Grund der kurzen Signallaufzeiten und der notwendigen starken Abschirmung der hochfrequenten Signale unmöglich ist, zwei gehäusete Asics ohne Leistungseinbusse miteinander zu verschalten. Hirschmann beauftragte aus diesem Grund Art of Technology mit der Entwicklung einer HDP-Lösung. Diese soll die 9 Eingänge auf 4 Benutzer verteilen und die analoge Benutzerkommunikation mit dem digitalen DISEQ-Protokoll ergänzen. Eine Machbarkeitsanalyse zeigte, dass eine Integration der Schalter-Asics, ein Prozessor pro Benutzer und ein Inverter die beste Lösung darstellen. Die restlichen Bauteile inklusive der Stecker verbleiben auf einer zweilagigen Leiterplatte.

Bild 9 zeigt einen Prototyp in Dünnschichttechnologie. Auf zwei Lagen wurden die HF-Leitungen impedanzkontrolliert geführt, die digitalen Anschlüsse verdrahtet und die Spannungsversorgung realisiert. Auf die Montage von passiven Elementen konnte verzichtet werden, da Widerstände und Kapazitäten direkt in das Substrat integriert wurden.

Das Dünnschichtsubstrat wurde auf einen Ball-Grid-Array-Träger montiert (Bild 9, kleines Bild), um ein kapazitäts- und induktivitätsarmes Gehäuse zu erhalten. Für die Serienproduktion werden das Substrat und der Träger zu einem Substrat miteinander kombiniert. Das Design ist im Vergleich mit der reinen PCB-Lösung kosteneutral, da der grosse Träger zweilagig bleibt und das Metallgehäuse

um das System nicht vergrössert werden muss.

Diese beiden Beispiele sind recht komplexe Anwendungen. Die verwendeten Technologien können jedoch auch kosteneffizient in Low-Cost-Applikationen

integriert werden. Gerade in Bereichen wie der Sensorik, wo ein Sensor und etwas Logik kombiniert werden müssen oder ein Asic mit etwas zusätzlicher Beleuchtung versehen werden soll, bieten diese Technologien viele Vorteile.

## HDP heute und in Zukunft

Die HDP-Technologien haben sich in den letzten Jahren in der europäischen Industrie weniger stark etabliert, als in Voraussagen prognostiziert wurde. Dies hat vor allem mit einem fehlenden Vertrauen in die Zuverlässigkeit dieser Technik und mit der Behauptung zu tun, dass HDP nur bei grossen Stückzahlen rentabel eingesetzt werden kann.

Viele Betriebe haben soeben den Schritt von durchkontaktierten Bausteinen zu oberflächenmontierten (SMD) gemacht. Nun wird vorausgesetzt, dass eine Kontaktierung, welche nur mit einem 25µm dicken Draht gemacht wird, nicht so zuverlässig ist wie die beiden zuvor genannten Technologien. Dabei wird außer Acht gelassen, dass das Drahtbonden eine Technologie ist, die seit mehre-

Bild 6 Blockschematicum Pentium-System

Bild 7 Substrat am Beispiel Laminat-Substrat mit Aufbaulagen (SBU)

Bild 8 5:4-Satelliten-schalter

Bild 9 Satellitenempfänger-Modul

ren Jahrzehnten in jedem einzelnen Chip (unabhängig davon, ob durchkontaktiert oder SMD) eingesetzt wird und sich bewährt hat. Das Risiko, das von den Lötstellen ausgeht, kann durch den Einsatz

von HDP drastisch reduziert werden (Beispiel Pentium MCM: Reduktion der Lötstellen von 1004 auf 320).

HDP ist als kostspielig bekannt, da die ersten Anwendungen rein militärisch

oder für die Luft- und Raumfahrt waren. Der Preis und die benötigten Stückzahlen für ein in HDP-Technologien gefertigtes Modul hängen jedoch sehr stark von den verwendeten Technologien ab. Dazu kommen die Vorteile für das ganze System, welche nicht ausser Acht gelassen werden dürfen. Oft ist das HDP-Modul etwas teurer als eine reine PCB/SMD-Lösung, doch meistens können die Kosten des Gesamtsystems reduziert werden. Möglichkeiten für diese Kosteneinsparung sind:

- kleineres und einfacheres Gehäuse

- kleinere Platine

- weniger Bauteile

- Kernmodule, die in verschiedenen Systemen verwendet werden können

Dies führt dazu, dass auch bei Serien unter 1000 Stück/Jahr der Einsatz von HDP-Technologien durchaus rentabel sein kann und geprüft werden muss.

Die Erfahrung der letzten Jahre mit dem Einsatz dieser Technologien zeigen trotz allem eine steigende Akzeptanz in der Industrie. In Zukunft werden HDP-Technologien vermehrt auch in Low-Cost-Anwendungen eingesetzt werden. Anstrengungen in diese Richtung werden auch durch die immer grösser werdende Zahl von Chipherstellern unterstützt, die ihre ICs auch als Bare Die anbieten.

## High Density Packaging

### La voie rapide vers la miniaturisation en électronique

Le High Density Packaging (HDP) permet d'améliorer largement les propriétés des systèmes électroniques, non seulement en réduisant les dimensions mais encore en augmentant la performance et la fiabilité. Etant donné que le High Density Packaging n'est pas une technologie spécifique mais une collection de technologies très diverses, son application exige un savoir-faire très vaste. L'utilisateur doit non seulement connaître les avantages et inconvénients des technologies de base à disposition mais aussi avoir accès à un vaste réseau de fabricants de celles-ci. Art of Technology est une des sociétés qui se proposent de mettre les possibilités du HDP à la disposition du plus grand nombre possible d'utilisateurs.