**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 91 (2000)

Heft: 1

Artikel: Ein Chip entsteht

Autor: Troxler, Thomas

**DOI:** https://doi.org/10.5169/seals-855503

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 30.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# **Ein Chip entsteht**

Mikroelektronik zieht auch im Textilmaschinenbereich ein. Die dauernde Weiterentwicklung der mechanischen Funktionen verlangt entsprechend anpassungsfähige Steuer- und Regelungsmodule in der Antriebstechnik. Anwendungsspezifische Chips (Asic, Application Specific Integrated Circuit) können zeitkritische Aufgaben in hochdynamischen Antrieben übernehmen, gesteuert und koordiniert von einem übergeordneten Mikrokontroller.

Im Rahmen des Impuls-Programms *Microswiss* wird an der Hochschule Rapperswil ein Nachdiplomstudium (NDS) in Mikroelektronik angeboten. Nicht selten wird dabei eine Diplomarbeit zum Grundstein einer neuen Firma, wie im Falle der PowerTrack GmbH von Andreas Leuthold mit Sitz in Menzingen, die hochdynamische Motorantriebe entwickelt. Auftraggeber des Projektes war der Textilmaschinenhersteller SSM aus Horgen.

Wer Mikroelektronik sagt, denkt auch an Asic (Application Specific Integrated Circuit) und der Leser fragt sich, wozu denn eine so stark miniaturisierte Schal-

#### Adresse des Autors

Thomas Troxler, Geschäftsleiter Microswiss-Zentrum Rapperswil Oberseestrasse 10, 8640 Rapperswil SG

tung in einer grossen Maschine überhaupt notwendig ist. In Textilmaschinen sind heute oft hochdynamische Antriebe eingesetzt, zu deren Steuerung viele teilweise zeitkritische Aufgaben gleichzeitig gelöst werden müssen. Dafür wäre ein sehr leistungsfähiger und teurer Mikroprozessor notwendig, der oft gar nicht ohne spezifische Elektronik auskommen könnte.

#### Konzept

Aus dieser Aufgabenstellung entstand das Konzept, wonach ein verhältnismässig einfacher Mikrokontroller zusammen mit einem Asic den Regel- und Steuerteil des Antriebs bilden. Der Mikrokontroller nimmt dabei die übergeordnete Regelung sowie Überwachungs- und Schutzfunktionen wahr, während der Asic für die zeitkritischen Aufgaben zuständig ist. Dieser Lösungsansatz sah nicht nur von der technischen, sondern auch von der ökonomischen Seite her sehr erfolgversprechend aus.

Im Rahmen seiner Diplomarbeit erarbeitete Andreas Leuthold die Spezifikation für den Asic und entwickelte diesen gemeinsam mit Mitarbeitern des Microswiss-Zentrums Rapperswil. In der Spezifikationsphase wurden die Detailfunktionen des Asic festgelegt. Diese gliederten sich schliesslich wie folgt:

- Adressdecodierung des Mikrokontrollers

- Interface zum Daten- bzw. Adressbus des Mikrokontrollers

- Zwei voneinander unabhängige asynchrone Schnittstellen vom Typ RS 232/485 zur Kommunikation mit weiteren Steuerungssystemen

- Erfassung, Filterung und Decodierung der Signale mehrkanaliger optischer Inkrementalgeber

- Dreiphasen-PWM-Generator zur Ansteuerung eines Asynchronmotors

- Ansteuerung der Leistungsendstufe eines Servomotors

Damit war die Grundlage für eine Asic-Entwicklung geschaffen und der Umsetzung stand nichts mehr im Wege.

### **Entwicklung**

Am Microswiss-Zentrum Rapperswil wird bei der Entwicklung digitaler Asic und von FPGA (feldprogrammierbare Logikbausteine, Field Programmable Gate Array) sowie bei den Digitalteilen von Mixed-Signal-Asic (Chip mit analogen und digitalen Funktionen) ein technologieunabhängiger Ansatz gewählt. Dabei kommen die genormten Hardwarebeschreibungssprachen Verilog HDL (Hardware Description Language) oder VHDL (VHSIC HDL bzw. Very High Speed Integrated Circuit HDL) zum Einsatz. Diese erlauben es, die Funktion eines digitalen Blockes ähnlich einem Software-Programm zu beschreiben, sein Verhalten zu simulieren und anschliessend daraus automatisch ein Schaltschema zu erzeugen.

Allerdings ist es schon bei kleineren Projekten oft schwierig, sich schnell einen Überblick über ein textlich beschriebenes System zu verschaffen. Seit einigen Jahren gibt es Computerprogramme, mit denen man grafisch die Funktion erfassen und anschliessend aus der grafischen Beschreibung den HDL-Code generieren kann. Um in einem möglichst frühen Stadium eine Aussage über das korrekte Verhalten der Schaltung zu erhalten, wird die Beschreibung simuliert. Dabei handelt es sich allerdings nur um eine rein funktionale Simulation, das heisst es wird nur das logische Verhalten der Beschreibung überprüft. Erst wenn dabei das gewünschte Resultat erreicht ist, folgen die weiteren Schritte.

# **Technologie**

Die HDL-Beschreibung wird nun einem Syntheseprogramm übergeben, das in einem ersten Schritt die Beschreibung in boolesche Gleichungen umwandelt und diese nach den Regeln der booleschen Algebra minimiert (Synthese und Optimierung). Erst jetzt muss man sich entscheiden, mit welcher Technologie man seinen Entwurf ausführen will, weil das Syntheseprogramm für den folgenden Schritt die Angaben über die Zieltechnologie benötigt. Es bildet die minimierten Gleichungen auf Elemente (AND, OR, Flip-Flop usw.) dieser Zieltechnologie ab (Technologiemapping) und setzt so das gewünschte Schaltschema zusammen. Die in der Technologiebibliothek modellierten Elemente enthalten aber nicht nur eine logische Funktion, sondern auch physikalische Eigenschaften wie Signallaufzeiten oder Eingangslastfaktoren. Das Syntheseprogramm stellt in der Folge nicht nur sicher, dass die logische Funktion des Schaltschemas jener der HDL-Beschreibung entspricht, sondern auch dass weitere Anforderungen erfüllt werden. So wird automatisch sichergestellt, dass kein Ausgang eines Elements durch zu viele Eingänge weiterer Elemente belastet wird, oder dass die Schaltung in der geforderten Geschwindigkeit betrieben werden kann. Und ganz nebenbei versucht es auch noch, den Schaltungsaufwand möglichst gering zu halten.

Wenn ein Asic später in grossen Massen produziert wird, können bedingt durch die Komplexität der Arbeitsschritte auf einzelnen Chips Fehler entstehen. Um fehlerhafte Bausteine zu erkennen,

werden die Chips während des Produktionsablaufes getestet. Zur Optimierung dieser Tests wird das Schaltschema um besondere Teststrukturen erweitert. Bei digitalen Schaltungen kann zusätzlich ein Testsynthesizer eingesetzt werden, der auch gleich das für das Testgerät benötigte Programm erzeugt. Dieser Schritt ist bei programmierbaren Bauelementen allerdings nicht nötig, da sie schon in der Fabrikation und teilweise beim Programmieren überprüft werden.

### **Simulation**

Das endgültige Schaltschema ist damit fertiggestellt und wird mit der Prelayoutsimulation überprüft. Dabei entspricht sein Verhalten schon relativ genau der Hardware, denn es werden jetzt auch die physikalischen Eigenschaften der einzel-

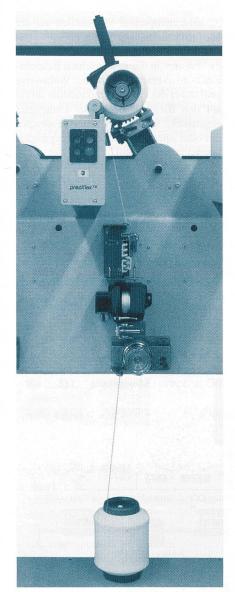

**Bild 1** Antriebskonzept mit Spindelmotor

Die platzsparende Bauweise verlangt neue Lösungen im Regel- und Steuerteil.

nen Schemaelemente berücksichtigt. Was zum jetzigen Zeitpunkt noch nicht feststeht, ist der genaue Einfluss der Verbindungsleitungen. Dieser kann bei Technologien mit Strukturen von unter einem Mikrometer erheblich sein und wird deshalb anhand eines «Wireload»-Modells berücksichtigt. Sobald auch diese Simulation erfolgreich verlaufen ist, kann mit dem letzten Schritt, dem Layout begonnen werden. Dabei werden die Elemente physisch plaziert und anschliessend die Verbindungsleitungen gezogen. Erst jetzt ist der genaue Einfluss der Verbindungsleitungen bekannt, und mit der Postlayoutsimulation kann das endgültige Verhalten der Hardware überprüft wer-

Je nach Technologie wird der Baustein nun sofort programmiert (z.B. FPGA), oder im Falle des Gatearrays die Layoutdaten via Internet zur «Foundry» (Werk für die Chipfabrikation, ursprünglich Giesserei) geschickt. Dort werden die zur Herstellung des Chips benötigten Produktionsmasken hergestellt und sechs bis acht Wochen später können die ersten Muster ausgeliefert werden. Das Herstellen dieser Produktionsmasken ist ein sehr aufwendiges und damit teures Verfahren. Vorgängig muss also unbedingt sichergestellt sein, dass der Chip genau so funktioniert, wie man es sich eigentlich vorgestellt hat.

In der Praxis ist es leider ab und zu der Fall, dass sich der Chip zwar genau den Spezifikationen entsprechend verhält, sobald er aber in das ihn umgebende System eingesetzt wird, treten überraschende Reaktionen auf, weil irgend ein Einfluss oder eine Besonderheit beim Erstellen der Asic-Spezifikation übersehen wurde. Deshalb entschied man sich im vorliegenden Projekt, die HDL-Beschreibung vorerst auf einem programmierbaren Baustein von Quicklogic umzusetzen und diesen im Gesamtsystem auszutesten. Und siehe da, der kleine Umweg lohnte sich sehr wohl. Es konnten einige kleine Unzulänglichkeiten festgestellt werden, die zwar nicht die benötigte Funktion beeinträchtigt hätten, deren Beseitigung aber die Performance des Systems nochmals steigern konnte. Erst nach Verifikation der entsprechenden Änderungen wurde die Beschreibung auf eine Gatearray-Technologie von NEC umgesetzt.

# **Produktion**

Im letzten November trafen die Musterchips bei der PowerTrack GmbH ein und wurden vor der eigentlichen Seriefreigabe nochmals eingehend getestet. Erst danach wurde die Serienfertigung für die ersten 10000 Stück des etwa 32000 Transistoren umfassenden Asic gestartet. Auf diesem Weg kam die PowerTrack GmbH also zu ihrem ersten Asic.

Natürlich sieht der Verlauf bei jedem Projekt wieder etwas anders aus. Auch ist das Angebot des Microswiss-Zentrum, Rapperswil, viel breiter als man anhand dieses Fallbeispiels vielleicht annehmen könnte. So bietet es mit seinen Spezialisten nebst der Beratung in Fragen rund um die Mikroelektronik auch Hilfestellung bei konzeptionellen und systemtechnischen Problemen oder beim Erstellen einer Asic-Spezifikation an. Das Hauptbetätigungsfeld liegt jedoch in der Entwicklung von kundenspezifischen integrierten Schaltungen, dies sowohl im Analog-, Mixed-Signal- und Digitalbereich. Auch wird das dabei aufgebaute und akkumulierte Wissen an Weiterbildungsveranstaltungen in die Industrie transferiert. Das Mittel dazu ist die Weiterbildungsinitiative Elektronik (WiE), die von der Hochschule Rapperswil (HSR) gemeinsam mit der Interstaatlichen Fachhochschule für Technik Buchs (NTB) und der Hochschule für Technik und Architektur Luzern aufgebaut wurde.

Geplant ist eine nationale Ausdehnung des Angebotes durch den am 24. August 1999 in Horw gegründeten Verein *Microswiss Network*, in dem landesweit die Mikroelektronikfachstellen sämtlicher Fachhochschulen zusammengefasst sind.

# Naissance d'une puce

La micro-électronique conquiert également le domaine des machines textiles. Le perfectionnement constant des fonctions mécaniques exige, dans la technique d'entraînement, des modules de commande et de réglage adaptés en conséquence. Des puces spécifiques en fonction des applications, ou Asic (Application Specific Integrated Circuits), peuvent assumer des tâches critiques dans le temps dans les entraînements à haute dynamique, sous la commande et la coordination d'un microcontrôleur. Le projet est issu d'un travail de diplôme effectué dans le cadre du programme d'impulsion «Microswiss».