**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 91 (2000)

Heft: 1

**Artikel:** Energiekostenmessung mit "intelligentem" Chip

Autor: Schenk, Karl U.

**DOI:** https://doi.org/10.5169/seals-855502

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 30.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

## **Energiekostenmessung mit «intelligentem» Chip**

Der Wunsch nach zentraler und damit kostengünstiger und umweltfreundlicher Energieerzeugung ruft nach der Möglichkeit, die Energiekosten verbrauchsabhängig messen und verrechnen zu können. Die vorgestellte Lösung beruht auf einem intelligenten Chip, der an der Fachhochschule Aargau als anwendungsspezifische integrierte Schaltung (Asic) entwickelt wurde.

Die Firma Bernina Electronic AG in Steckborn stellt Geräte für die Erfassung und Abrechnung von Energiekosten her. In der neuen Produktereihe «Metrix» werden Heizkostenverteiler, Wassersowie Wärmezähler entwickelt. Dabei kommt der exakten Bestimmung der Durchflussmenge eine zentrale Rolle zu.

Die für Wasser- und Wärmezähler benötigte Durchflussmessfunktion beruht auf dem Prinzip eines Wasserrades, dessen Umdrehungen im Gegensatz zum

#### Adresse des Autors

Prof. Karl U. Schenk, Geschäftsleiter Zentrum für Mikroelektronik Aargau 5210 Windisch

früheren mechanischen Zählwerk magnetisch übertragen und von Hallsensoren aufgenommen werden. Die Hallsensoren und die gesamte Auswerteelektronik sollen in einem anwendungsspezifischen IC (Application Specific Integrated Circuit Asic) realisiert werden. Damit soll neben minimalem Stromverbrauch, Miniaturisierung und Kostenreduktion auch ein technologischer Vorsprung gegenüber den Mitbewerbern erreicht werden.

#### Lösungsansatz

Auf Grund einer ausführlichen Systemanalyse und dem Studium der Grobspezifikation wird der Entscheid getroffen, eine Asic-Lösung zu realisieren. Dabei erscheint vor allem interessant, in einem einzigen Bauelement sowohl den Messaufnehmer (Hallsensoren), die analoge Signalaufbereitung (Filterung, Verstärkung, Signalanpassung, Selbsttest) als auch die digitale Verarbeitung (Zähler, Auswertung) vereinigen zu können.

Vom Gerät wird gefordert, dass es während langer Zeit autonom funktionie-

ren muss, eine geringe Grösse aufweist und kostengünstig produziert werden kann. Daher liegt der Einbezug der Hauptfunktionen in eine integrierte Schaltung nahe. Daraus entstand der Kontakt zum Zentrum für Mikroelektronik der Fachhochschule Aargau (ZMA), das dann mit dem Kunden zusammen die Entwicklung durchführte.

Im Projekt, das im Rahmen des Microswiss-Bundesprogramms abgewickelt wurde, arbeiteten ein Entwickler der Kundenfirma und das Entwicklungsteam des ZMA in einem Projektteam zusammen.

Auch der Asic-Hersteller, in diesem Fall die Firma AMS Austria Mikro Systeme International in Unterpremstätten (Österreich) sowie deren Vertretung in der Schweiz, die Firma Dätwyler-Electronics AG in Zürich, waren am Entwick-

lungsprojekt beteiligt. Sie kümmerten sich einerseits um die technische Unterstützung für alle technologiespezifischen Fragen der Fertigung, andererseits um die kommerziellen Aspekte der Produktionsabwicklung und der Lieferungen.

Schliesslich gehören – wenn auch meist nicht direkt in das Projekt involviert – auch die Hersteller der CAD-Werkzeuge zum Projektablauf. Das ZMA verwendet seit Jahren erfolgreich die Werkzeuge der Firma Mentor Graphics und verlässt sich auf deren Unterstützung, sobald Fragen auftauchen.

Das Projekt umfasst die in Tabelle I aufgeführten Schritte.

#### Lösungsmethodik

Zuerst ist unbedingt eine vollständige Analyse des gewünschten Systems erforderlich. Dies wird am ZMA nach der SA/SD-Methode (Structured Analysis/Structured Design) nach Tom DeMarco mit Papier und Bleistift durchgeführt. Sobald alle Grundfunktionen klar und eindeutig definiert sind, werden Lösungsvarianten für die Ausführung gesucht, die Varianten studiert und die Aufteilung des Systems auf Systemkomponenten definiert (Partitionierung). Im Fall einer Schaltung mit digitalen und analogen Komponenten (Mixed Analog/Digital Asic) muss insbesondere geprüft werden,

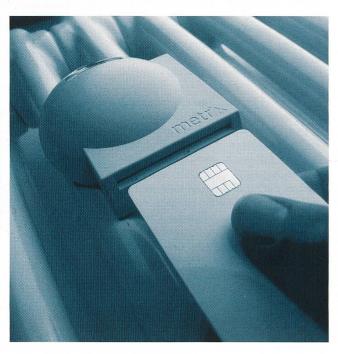

Bild 1 Einfaches Auslesen der Messgeräte mit Chipkarte (Foto: Bernina Flectronic)

#### Vorteile von Asic Grösse: Asic-Lösungen sind dank der geringeren Grösse und der geringeren Anzahl externer Bauelemente kleiner als konventionell aufgebaute Lösungen. Energieverbrauch: Asic-Lösungen können auf geringen Energieverbrauch optimiert werden und sind deshalb für batteriebetriebene Produkte optimal. Der niedrige Energieverbrauch ermöglicht auch abgeschlossene Produkte ohne Lüftung und damit ohne bewegte Bauteile. Zuverlässigkeit: Dank der geringen Anzahl Bauelemente kann die Zuverlässigkeit wesentlich erhöht werden, vor allem für Produkte, die während längerer Zeit unbeaufsichtigt betrieben werden sollen. Vertraulichkeit: Ein Asic ist wesentlich schwieriger zu kopieren als ein Aufbau auf einer Leiterplatte.

wieweit eine Signalverarbeitung analog erfolgt und wann digitalisiert werden soll. Ausserdem muss festgelegt werden, welche Funktionen überhaupt innerhalb des Asic und welche zum Beispiel durch einen Mikrokontroller ausserhalb des Asic ausgeführt werden sollen.

Nachdem alle diese Fragen geklärt sind, kann erstmals die CAD-Umgebung zum Einsatz kommen. Das Design wird grafisch eingegeben. Dabei werden analoge Funktionen direkt als technologieabhängige Schemas gezeichnet, während die digitalen Funktionen grafisch strukturiert und mit einer Hardware-Beschreibungssprache (analog einer Programmiersprache für Software) spezifiziert werden.

Die analogen Funktionen werden mit Spice-basierenden (Simulation Program with Integrated Circuit Emphasis) leistungsfähigen Simulatoren überprüft, während für die digitalen Funktionen eine VHDL-Testbank (Very High Speed Integrated Circuit Hardware Description Language) entwickelt wird, die sowohl die Stimuli für die Überprüfung erzeugt als auch direkt die zu erwartenden Ergebnisse mit den tatsächlichen Simulationsresultaten vergleicht. Damit besteht die Möglichkeit einer weitgehend automatisierten Verifikation, was vor allem bei den unumgänglichen «letzten Änderungen» äusserst hilfreich ist.

Dank der Analog-Erweiterung von VHDL (VHDL-AMS, IEEE-Norm 1076.1) und entsprechender Werkzeuge wird es schon bald möglich sein, die VHDL-Testbank auch für die analogen Funktionen und damit für das Gesamtsystem einzusetzen.

Nach der Abnahme der funktionalen Simulation durch den Kunden wird das System implementiert, was bedeutet, dass die VHDL-Beschreibung mit einem Synthesewerkzeug auf eine technologiespezifische Netzliste umgesetzt wird. Dabei wird auf geringen Flächenbedarf unter Erfüllung der Laufzeit-Anforderungen optimiert.

Die Zellen der analogen und digitalen Funktionsteile werden auf der IC-Grund-

fläche plaziert und verdrahtet. Diese Arbeit wird vor allem für die analogen Schaltungsteile von Hand durchgeführt. Ausserdem werden die Ein-/Ausgangs-Anschlussflächen (Pads) und spezielle Elemente wie der «Clock-Tree» sowie Teststrukturen eingebaut. Es werden layoutabhängige Laufzeitdaten extrahiert und nochmals in einer Simulation verifiziert.

Nun kann eine erste Lieferung von etwa zehn Prototypen hergestellt werden. In der Regel wird dazu eine besondere Dienstleistung der Asic-Anbieter genutzt: der «Multi-Project-Wafer»-Service (MPW). Dabei werden auf einem Wafer (einer Siliziumscheibe) Chips für verschiedene Projekte vereinigt, was bei den Initialkosten (Maskenkosten) für jedes einzelne Projekt eine wesentliche Kosteneinsparung bedeutet.

Nach dem Test dieser Prototypen und allfälliger letzter Anpassungen wird der Serie-Maskensatz zu einem Preis von mehreren zehntausend Franken in Auftrag gegeben, werden die Engineering-Muster überprüft, das Testprogramm

| Aufgabe                                                                                                                                        | Partner                                                      | Tools                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Analyse des Gesamtsystems<br>und des Asic-Subsystems                                                                                           | ZMA,<br>Kunde                                                | Papier und Bleistift                                                                   |

| Partitionierung der Funktionen in Analog-<br>und Digitalteil, Spezifikation der Funk-<br>tionen des Gesamt-Asic sowie dessen Teile             | ZMA<br>Kunde                                                 | Papier und Bleistift                                                                   |

| Beschreibung und Verfikation (Simulation)<br>der analogen Funktionen des Asic<br>in Schema                                                     | ZMA, z.T. Kunde,<br>z.T. Asic-Hersteller<br>(Standardzellen) |                                                                                        |

| Beschreibung der digitalen Funktionen des<br>Asic in einer Hardware-Beschreibungs-<br>sprache (VHDL), Verifikation mit einem<br>VHDL-Testbench | ZMA,<br>Kunde                                                | Renoir, Modelsim<br>(Mentor Graphics)<br>Bestbench (Diagonal<br>Systems                |

| Verifikation des Gesamt-Asic                                                                                                                   | ZMA,<br>Kunde                                                | Continuum (Mentor<br>Graphics)                                                         |

| Synthese der VHDL-Beschreibung in Netzliste                                                                                                    | ZMA                                                          | Design Compiler (Synopsys)                                                             |

| Plazierung und Verdrahtung der Schaltung auf dem Asic                                                                                          | ZMA, z.T. Asic-<br>Hersteller (AMS)                          | IC-Station (Mentor Graphics)                                                           |

| Überprüfung der korrekten Umsetzung (DRC, LVS)                                                                                                 | ZMA                                                          | IC-Station (Mentor<br>Graphics)                                                        |

| Verifikation der Funktionen mit «Post-<br>Layout-Timing»                                                                                       | ZMA                                                          | AccuSim, ModelSim,<br>Continuum (Mentor<br>Graphics)                                   |

| Spezifikation und Entwicklung des Test-<br>programms                                                                                           | ZMA,<br>Asic-Hersteller                                      | DFT Advisor (Mentor<br>Graphics für digitale<br>Tests), Papier und<br>Bleistift (Rest) |

Tabelle I Projektschritte und verwendete Hilfsmittel

#### Innovations-Forum

beim Hersteller entwickelt und verifiziert und schliesslich die Serieproduktion freigegeben.

#### **Projektablauf**

26

Das ZMA führt alle Projekte wie auch das beschriebene nach einem festen Ablauf durch. Dieser besteht aus den verschiedenen Projektphasen und Berichten. Bei letzteren wird zwischen «Design Reviews» bei den Meilensteinen (z.B. Freigabe der Spezifikation, des Designs, der Prototypen sowie allfälliger Zwischen-

schritte) und «Project Reviews» in regelmässigen Abständen (z.B. zweiwöchentlich, Steuerung des Projektablaufs und der Projektkosten, Korrektur bei Problemen) unterschieden.

Die Projektleitung liegt letztlich beim Kunden. Trotzdem übernimmt das ZMA in der Regel die technische Projektleitung, da hier das Know-how und die Erfahrung liegt, die für einen störungsfreien Projektablauf unerlässlich sind. Selbstverständlich müssen alle Projektpartner (Kunde, Hersteller, Designer, allenfalls auch die Lieferanten der eingesetzten

Softwarewerkzeuge und weitere Partner) jederzeit über den Projektstand orientiert sein.

#### **Beurteilung**

Voraussetzung für ein erfolgreiches Asic-Projekt sind:

- Genaue Spezifikation des Systems und des Asics. Bereitschaft, diese Spezifikation nach gründlicher Systemanalyse einzufrieren und nicht mehr zu verändern bzw. Anpassungen nur vorzunehmen, wenn deren Auswirkungen auf Funktionalität, Projektkosten und Projekttermine abgeklärt und genehmigt sind.

- Exakte, systematische, methodische Bearbeitung des Projekts unter Beizug von ausgebildeten, erfahrenen Fachleuten und leistungsfähigen Werkzeugen

- Zusammenarbeit mit renommierten Partnern, die Einsteiger wirkungsvoll unterstützen und damit die Erfolgschancen steigern können.

Das Beispiel zeigt, dass es auch einem Einsteiger möglich ist, ein Asic-Projekt bis zur erfolgreichen Vermarktung durchzuführen.

## Une puce «intelligente» pour mesurer les coûts d'énergie

Tandis qu'on vise à centraliser la production d'énergie pour la rendre plus économique et plus écologique, il faut également chercher à en mesurer et facturer le coût en fonction de la consommation. En vue de permettre la mesure de débit nécessaire, il a été développé un circuit intégré réunissant sur la même puce le palpeur ainsi que l'évaluation analogique et numérique des signaux. La solution présentée est basée sur un circuit intégré spécifique à l'application (Asic) développé à l'Ecole d'ingénieurs d'Argovie.

Der SEV auf dem Internet / L'ASE sur l'Internet: http://www.sev.ch

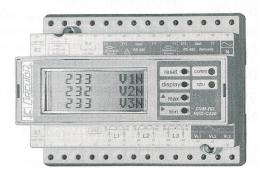

### «Der Perfekte» CVM-BD-Powermeter

True RMS-4-Quadrantmessung – isolierte Messeingänge; mit/ohne Messdatenspeicher – mit/ohne THD-Anzeige; für Messungen in Niederund Mittelspannungsnetzen; Strom-/Spannungswandlerverhältnis ohne Einschränkung wählbar

$\begin{array}{l} \textbf{U} \cdot \textbf{I} \cdot \textbf{kW} \cdot \textbf{kWh} \cdot \textbf{kVarL} \cdot \textbf{kVarC} \cdot \textbf{kVarhC} \cdot \\ \textbf{kVarhL} \cdot \textbf{kVA} \cdot \textbf{cos-phi} \cdot \textbf{Hz} \cdot \textbf{THDV} \cdot \textbf{THDI} \end{array}$

Messgeräte • Systeme • Anlagen zur Kontrolle und Optimierung des Verbrauches elektrischer Energie Postfach 151 CH-4310 Rheinfelden 1 Elefon 061-831 59 81 Telefax 061-831 59 83

#### Ihre Sicherheit – Unsere Kernkompetenz – LANZ Stromschienen 25 A – 8'000 A

lanz oensingen ist der marktführende Stromschienenanbieter mit langjähriger Erfahrung und mit einem leistungsstarken kompletten Lieferprogramm:

- Modernste, nach internationalen EN/IEC-Normen typengeprüfte Stromschienen 25 – 6'000 A/1'000 V bzw.

630 – 8'000 A/245 kV

- Schutzarten bis IP 68 korrosionsfest giessharzvergossen

- Rationelle "Just-in-time"-Produktion ISO 9001-zertifiziert

Profitieren Sie von unserer Kernkompetenz. Verlangen Sie Beratung, Offerte, rasche und preisgünstige Lieferung und Montage von

lanz oensingen ag Tel. 062 388 21 21, Fax 062 388 24 24

- LANZ Stromschienen interessieren mich! Bitte senden Sie Unterlagen.

- ☐ Könnten Sie mich besuchen? Bitte tel. Voranmeldung! Name/Adresse/Tel.

lanz oensingen ag CH-4702 Oensingen • Telefon ++41/62 388 21 21

SS

C ( // // // ENERGIE UND DIENSTLEISTUNGEN

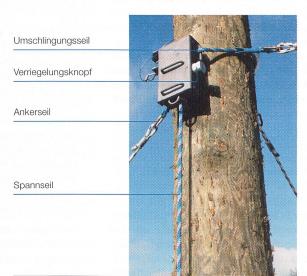

# Kleiner Aufwand, grosse Wirkung: Das Mastsicherungsgerät

Die Tests sind abgeschlossen, die Prüfung ist glänzend bestanden: Das neue Mastsicherungsgerät CKW98 wurde im täglichen Einsatz von Fachleuten entwickelt und von der SUVA zertifiziert.

Das System ist verblüffend einfach: Die Montage erfolgt am Boden. Das Gerät wird mit einer Teleskopstange bis unmittelbar unter das Mastbild geschoben und der Mast dreipunktig gesichert. Kein gefährliches Klettern, keine unberechenbaren Risiken.

Im Zusammenspiel zwischen

3-Punkt-Sicherung und dem zum

Patent angemeldeten Blockiermechanismus wird ein Höchstmass an Sicherheit erreicht.

Lassen Sie sich eine kostenlose

Demonstration vor Ort nicht entgehen. Rufen Sie uns an.

Herr Beat Fehlmann erteilt Ihnen

gerne weitere Auskünfte.

Centralschweizerische Kraftwerke Hirschengraben 33, Postfach, 6002 Luzern Telefon 041-249 51 11, Telefax 041-249 52 22 b.fehlmann@ckw.ch, www.ckw.ch