**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 90 (1999)

Heft: 1

**Artikel:** Chancen einer neuen Halbleitertechnologie

**Autor:** Pindl, Stephan / Risch, Lothar

**DOI:** https://doi.org/10.5169/seals-901891

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF: 28.11.2025**

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

## Chancen einer neuen Halbleitertechnologie

Die physikalische Grenze der Miniaturisierung von Halbleiterchips rückt näher. Ab einer Strukturgrösse von etwa 130 nm werden der sogenannten Silicon-on-Insulator-Technologie Chancen eingeräumt, die konventionelle Siliziumtechnik abzulösen. Sie zeichnet sich durch kleine Betriebsspannungen und einen geringen Leistungsbedarf aus.

Silicon-on-Insulator(SOI)-Substrate erleben in den letzten Jahren einen neuen Aufschwung im Bereich der CMOS-Anwendungen (Complementary Metal Oxide Semiconductor). Aufgrund der sehr guten Bauelementeigenschaften, wie der besseren elektrischen Kopplung zwischen Gate-Elektrode und Transistorkanal, der geringen parasitären Kapazitäten und der ausgezeichneten Isolation der Bauelemente, erscheint eine SOI-CMOS-Technologie besonders vielversprechend für Anwendungen mit kleinen Betriebsspannungen. Weitere Vorteile bietet SOI aufgrund einer Reduzierung der Prozessschritte, seiner Strahlungsfestigkeit und der möglichen hohen Betriebstemperaturen. Sehr wichtig ist allerdings, bei der Prozessierung von SOI-CMOS-Transistoren einige Besonderheiten zu berücksichtigen. Abweichungen zeigen sich dabei aufgrund des veränderten Schichtaufbaus zum Beispiel bei Rapid-Thermal-Prozessen, das heisst sehr schnellen optisch geheizten Prozessen, und im Temperaturverhalten von Dotierstoffen. Weitere Unterschiede finden sich bei der Prozessierung der Isolationsgebiete. Insgesamt ist die SOI-Technologie heute als die vielversprechendste CMOS-Technologie für Anwendungen mit Betriebsspannungen kleiner 0,9 V anzusehen.

#### **Elektrische Eigenschaften**

Die ständige Erhöhung der Packungsdichte von Schaltungen auf einem Silizium-Chip in der CMOS-Technologie mit kleinsten auftretenden Strukturgrössen von 0,18 μm und darunter stellt kontinuierlich wachsende Anforderungen an die Prozess- und Device-Technologie. Deshalb wird die Frage nach einer Technologie, mit der es möglich ist, den Lei-

#### Adresse der Autoren

Dr. Stephan Pindl, Dipl. Phys., und Dr. Lothar Risch, Dipl. Phys., Siemens AG Otto-Hahn-Ring 6, D-81730 München stungs- und Wärmeverbrauch einer Schaltung in prinzipieller Weise zu senken, immer drängender. Die Leistungsaufnahme P einer CMOS-Schaltung ist

$$P = \sigma C_L V_{dd}^2 f + \sigma Q V_{dd} f + I_{leak} V_{dd}$$

(1)

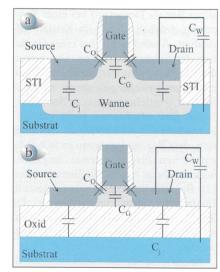

$\sigma$  ist die Schalthäufigkeit,  $C_L$  die Lastkapazität,  $V_{dd}$  die Versorgungsspannung, fdie Taktfrequenz, Q die Ladung, die beim Schalten fliesst, und Ileak der Leckstrom der Schaltung. Die Parameter, die am besten geeignet sind, die Leistungsaufnahme einer CMOS-Schaltung zu verringern, stellen somit die Versorgungsspannung und die Lastkapazitäten dar. Beim Vergleich eines schematischen Querschnitts eines SOI-CMOS-Transistors mit dem eines üblichen Silizium-CMOS-Transistors erkennt man, dass die Junction-Substrat-Kapazitäten C; durch unterschiedliche Materialien bestimmt werden (Bild 1). Bei Silizium-CMOS-Transistoren ist diese Kapazität näherungsweise durch einen einseitig abrupten pn-Übergang definiert, bei SOI ist sie durch eine Oxidschicht festgelegt. Abschätzungen zeigen dabei typischerweise eine Reduktion der Junction-Substrat-Kapazität Ci bei SOI-Substraten um einen Faktor 5. Auch die Kapazitäten der Verdrahtungen zum Substrat (Cw) verringern sich dadurch um etwa 40% [1]. Die Gate- und Overlap-Kapazitäten ( $C_G$ ,  $C_O$ ) bleiben hingegen unverändert. Somit kann die gesamte Lastkapazität C<sub>L</sub> einer CMOS-Schaltung gegenüber reinen Siliziumsubstraten insgesamt um ungefähr 40% verringert werden  $(C_L = C_G + C_i + C_O +$

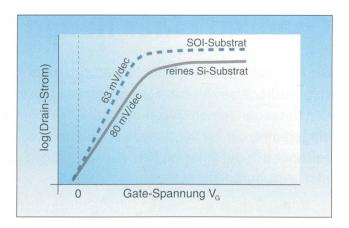

Verwendet man SOI-Substrate mit extrem dünner oberer Siliziumschicht (typ. 40 nm), so kann man durch geeignete Wahl der Kanaldotierung des Transistors eine vollkommene elektrische Verarmung des Kanals während des Betriebes erreichen [1]. Dies hat zur Folge, dass jede Spannungsänderung am Gate vollständig umgesetzt wird in eine Änderung des Oberflächenpotentials des Kanals. Dies

verbessert die inverse Unterschwellsteilheit S der Eingangskennlinie (Drainstrom vs. Gatespannung) bis nahe dem theoretisch erreichbaren Wert von

$$S = \frac{kT}{e} \ln(10) = 60 \, mV/dec \tag{2}$$

wobei k die Boltzmann-Konstante, T die Temperatur (hier Raumtemperatur) und e die Elementarladung bezeichnen [1]. Die Abkürzung dec bezieht sich dabei auf eine Dekade im Drainstrom. Ein Wert der Unterschwellsteilheit von S=60 mV/decbesagt somit, dass bei Gatespannungen kleiner der Einsatzspannung durch Erhöhung der Gatespannung um 60 mV der Drainstrom um einen Faktor 10 ansteigt. Erreicht werden für SOI-Substrate typisch Werte um 63 mV/dec im Vergleich zu 80-85 mV/dec bei reinen Siliziumsubstraten (Bild 2). Dadurch lassen sich bei SOI deutlich geringere Einsatzspannungen des Transistors realisieren (etwa 100 mV). Diese Senkung ermöglicht kleinere Versorgungsspannungen, was die Leistungsaufnahme deutlich reduziert (vgl. Formel 1).

Ein weiterer Vorteil von SOI-Substraten ist die mögliche Erhöhung der Packungsdichte einer CMOS-Schaltung. Betrachtet man den Querschnitt eines SOI-Transistors (Bild 1b), so erkennt man, dass ausserhalb des Transistorbereichs dieser sowohl vertikal als auch horizontal durch das vergrabene Oxid vom Substrat isoliert ist. Somit ist die Isolationsfähigkeit durch das Oxid defi-

Bild 1 Schematischer Querschnitt eines Mosfets auf reinem Siliziumsubstrat (a) und auf einem SOI-Substrat (b) mit eingezeichneten Kapazitäten

Die gesamte Lastkapazität ist bei SOI gegenüber reinen Siliziumsubstraten um ca. 40% reduziert.

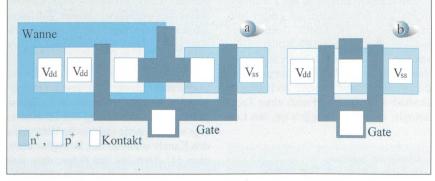

niert, während bei reinen Siliziumsubstraten Leckströme über das Substrat zu einem Kurzschluss zwischen zwei Transistoren («Latch up») führen können. Bei Verwendung reiner Siliziumsubstrate muss deshalb ein deutlich grösserer Abstand zwischen NMOS- und PMOS-Transistoren eingehalten werden als bei SOI-Substraten. Bei Inverter-Schaltungen (siehe Bild 3) lässt sich die Pakkungsdichte auf SOI-Substraten deutlich erhöhen. Bei komplexen Anwendungen reduziert sich die Fläche dabei um typischerweise 30%.

#### Bild 2 Unterschwellverhalten eines Transistors auf reinem Si-Substrat und auf SOI-Substrat

#### **SOI-Prozessierung**

Wie die Ausführungen des letzten Abschnitts zeigen, sind beim Prozess einer SOI-CMOS-Technologie gegenüber reinen Siliziumsubstraten einige Besonderheiten zu beachten. Durch die vergrabene Oxidschicht weist das SOI-Substrat deutlich andere optische Eigenschaften auf als reines Siliziumsubstrat. Verwendet man nun RTP-Prozesse (Rapid Thermal Processing), bei denen eine Lampenheizung eingesetzt wird, so stellt sich aufgrund eines veränderten Emissions- und Absorptionsverhaltens des Substrats eine andere Gleichgewichtstemperatur des Substrats ein. Ein Pyrometer, das auf die Substratoberfläche gerichtet ist, misst eine vollkommen falsche Temperatur (Abweichungen um teilweise mehrere 100 °C). RTP-Prozesse werden vor allem bei Epitaxieschritten, bei dünnen Oxiden und bei Ausheilschritten verwendet.

Bei der Ionenimplantation des Kanalund Junction-Dotierstoffs eines MOS-Transistors werden viele Zwischengitterplätze erzeugt. Dies führt dazu, dass vor allem Bor als Dotierstoff bei einer Temperung deutlich stärker im Kristall diffundiert. Ähnliches gilt bei einer Oxidation der Substratoberfläche. Das besondere an SOI-Substraten ist nun, dass die erzeugten Zwischengitteratome nicht ins Substrat wandern, sondern an der Grenzfläche zum vergrabenen Oxid mit Siliziumleerstellen rekombinieren. So zeigt sich, dass Bor bei Oxidation in SOI-Substraten um bis zu viermal langsamer wandert als in reinen Siliziumsubstraten [2]. Bei SOI-Substraten müssen deshalb Implantationsdosis und -energie für Kanal und Source/Drain-Gebiete und alle Hochtemperaturschritte angepasst werden.

Bei SOI-Substraten bietet sich zudem eine neue Methode der elektrischen Isolation der Transistoren an. Bei CMOS-Transistoren auf reinen Siliziumsubstraten wurde bisher meist die Locos-Technologie (Local Oxidation of Silicon) angewandt [3]. Dazu wird lokal das Siliziumsubstrat oxidiert. Gegenwärtig wird aufgrund der besseren Skalierbarkeit immer mehr die STI-Technologie (Shallow Trench Isolation) favorisiert. Dabei werden zur Isolation Gräben ins Silizium geätzt und mit Oxid gefüllt [3]. Für SOI-Substrate bietet sich nun ein neues Konzept an, welches technologisch einfach zu realisieren ist, die Mesa-Isolation. Dazu wird in den Isolationsgebieten die obere Siliziumschicht des SOI-Substrats bis zum vergrabenen Oxid weggeätzt. Somit sind die Transistoren bereits voneinander isoliert [1], siehe Bild 1b.

#### **Probleme und Perspektiven**

Bei den vielen bisher genannten Vorteilen stellt sich die Frage, warum nicht alle CMOS-Technologien sofort auf SOI-Substrate umgestellt werden. Die Antwort liegt darin, dass die Verwendung von SOI-Substraten auch Nachteile mit sich bringt. Hier ist zum Beispiel die Erwärmung des Transistors bzw. der Schaltung während des Betriebs zu nennen. Dieser Effekt tritt bei reinen Siliziumsubstraten nur bei Schaltungen mit grosser Leistungsaufnahme auf. Da sich jedoch die Wärmeabfuhr bei SOI-Substraten aufgrund der kleinen Wärmeleitzahl des vergrabenen Oxids verschlechtert, ist

dieser Effekt hier bereits bei kleineren Versorgungsspannungen zu beobachten. Durch die Erwärmung wird der Drainstrom wegen der erhöhten Temperatur reduziert und ist dadurch abhängig von der Schaltfrequenz der verwendeten Schaltung.

Ein weiterer, meist unerwünschter Effekt ist der «Floating-Body-Effekt». Dabei werden bei hohen Spannungen im Bereich der Drain eines NMOS-Transistors Elektron-Loch-Paare erzeugt. Die Löcher sammeln sich im Bereich unterhalb des Kanals und erhöhen dort das Potential. Dadurch wiederum wird die Einsatzspannung des Transistors abgesenkt und der Leckstrom erhöht. Umgekehrt lässt sich dieser Effekt auch ausnutzen. Wird der Bereich unterhalb des Kanals mit der Gateelektrode kurzgeschlossen, so ergibt sich für ein niedriges Gatepotential eine grosse Einsatzspannung mit kleinem Leckstrom, für ein hohes Gatepotential eine kleine Einsatzspannung mit grossem «On»-Strom. Um Bipolareffekte bei dieser Beschaltung möglichst klein zu halten, bietet sich insbesondere die «Solarzellenspannung» von 0,5 V an.

Die Wafer-Preise für SOI-Substrate liegen bisher noch um ein Vielfaches über den Preisen von reinen Silizium-Wafern (Faktor 3–5). Somit müssen die genann-

Bild 3 Schematisches Layout eines Inverters auf reinem Si-Substrat (a) und auf SOI-Substrat (b)

Aufgrund der fehlenden Wannen kann die Fläche des Inverters auf SOI-Substraten deutlich reduziert werden.

ten Vorteile der SOI-Technologie die erhöhten Kosten übertreffen. Ein zusätzliches Problem stellt bisher noch die hohe Defektdichte in der oberen Siliziumschicht von SOI-Substraten dar. Diese verringert deutlich die Ausbeute der Schaltungen, die sich dann im Preis des

Produkts niederschlägt. Die Entwicklung im Bereich der SOI-Wafer-Herstellung schreitet hier jedoch kontinuierlich fort.

Anhand einiger Beispiele wurden Vorund Nachteile der Verwendung von SOI-Substraten gemeinsam mit einigen Prozessbesonderheiten aufgezeigt. Nach

Einschätzung der Semiconductor Industry Association [4] erscheint die Verwendung von SOI-Substraten sehr aussichtsreich ab der 130-nm-Generation. Die wichtigsten Vorteile von SOI liegen in der höheren Geschwindigkeit, der niedrigeren Betriebsspannung und der Reduzierung der Prozessschritte. Hinzu kommen die erhöhte Strahlungsfestigkeit und die Möglichkeit des Einsatzes bei höheren Betriebstemperaturen.

### Une nouvelle technologie à semi-conducteurs

La miniaturisation des puces à semi-conducteurs approche de sa limite physique. Actuellement, la grandeur de structure des puces mémoires modernes n'est plus que de 180 nm. Dès une structure d'environ 130 nm, la technologie dénommée Silicon on Insulator revendique des chances de remplacer la technique traditionnelle au silicium. La géométrie particulière SOI - dans laquelle les circuits à transistors sont isolés du substrat de silicium par une mince couche d'oxyde incrustée (fig. 1b) - présente un certain nombre d'avantages importants. Outre une plus grande densité de montage, les transistors se démarquent par une courbe caractéristique d'entrée plus raide et des capacités diminuées. Cela réduit la consommation de puissance des circuits et permet d'utiliser des tensions de service plus basses.

#### Literatur

[1] J. P. Colinge: Silicon-on-Insulator Technology. Dordrecht: Kluwer Academic Publishers Verlag 1991.

[2] S. Pindl, M. Biebl, H. Schäfer, H. von Philips-

born: J. Electrochem. Soc. 144(1997), 4022

[3] D. Widmann, H. Mader, H. Friedrich: Technologie hochintegrierter Schaltungen. Berlin: Springer-

[4] The National Technology Roadmap for Semiconductors. Semiconductor Industry Association

Nachdruck mit freundlicher Genehmigung der Physikalischen Blätter, Weinheim (D).

| RUI | LETIN  | VS |

|-----|--------|----|

| DUL | LLIIIV | UC |

Publikationsorgan des Schweizerischen Elektrotechnischen Vereins SEV und des Verbandes Schweizerischer Elektrizitätswerke VSE

| Ich wünsche Unterlagen | über | folgende | Tätigkeiten | und |

|------------------------|------|----------|-------------|-----|

| Angebote des SEV:      |      |          |             |     |

|                        |      |          |             |     |

| Total | Security | Management | TSM® |

|-------|----------|------------|------|

|       |          |            |      |

|   | Qualitätsmanagement | Umweltmanagemer |

|---|---------------------|-----------------|

| _ | Qualitatsmanagement | Umweltmanagemei |

|        | Risikomanagement    | Normung, Bildung    |

|--------|---------------------|---------------------|

| $\neg$ | Sicherheitsberatung | Innovationsherature |

|   | 0.0        |                |                      |

|---|------------|----------------|----------------------|

| 1 | Prüfungen, | Qualifizierung | Starkstrominspektora |

| Abteilung    |       |  |

|--------------|-------|--|

|              |       |  |

| Fax          | <br>- |  |

| Unterschrift |       |  |

Ausfüllen, ausschneiden (oder kopieren) und einsenden an:

Schweiz. Elektrotechnischer Verein (SEV), IBN MD, Postfach, 8320 Fehraltorf, Fax 01 956 11 22 Bestellungen auch über http://www.sev.ch

Bulletin SEV/VSE 1/99

Telefon

im Verteilnetz lässt TOPAS 1000 keine Wünsche offen.

fabelhaft,

Ihr Vorteil:

mit dem

• Ein Messgerät mit dem Sie alle Parameter gleichzeitig erfassen. Das heisst, Spannungseinbrüche, schnelle Transienten, Oberschwingungen, EN 50160, Kurvenformen, Rundsteuertelegramme, Leistungsspitzen, Energieverbrauch etc. können mit TOPAS 1000 präzise erfasst werden.

besten

Mess-

gerät

ausgerüstet

zu sein?

Damit analysieren Sie Störungen schnell und umfassend und kommen auch dem Verursacher auf die Spur.

Störungen schneller analysieren? Fordern Sie ausführliche Unterlagen an.

#### LEM Instruments

ELMES • GOERZ • HEME • NORMA

Bahnhofstrasse 15 • CH-8808 Pfäffikon SZ Tel. 055-415 75 75 • Fax 055-415 75 55 e-mail: lel@lem.com • www.lem.com

# **POWERMETER**

Der Einbau-Netzanalysator von CIRCUTOR misst und berechnet alle wichtigen Parameter im elektrischen Netz. Auf dem gut ablesbaren Display werden neun, frei wählbare, Messwerte angezeigt. Die Programmierung ist äusserst einfach und menügeführt. Steckbare Erweiterungsmodule bieten - jederzeit nachrüstbar -Netzwerkfähigkeit, Relais- und Analogausgänge. Die Ausgänge können den Messwerten frei zugeteilt, die Funktionen programmiert werden.

Messgeräte · Systeme · Anlagen zur Kontrolle und Optimierung des Verbrauches elektrischer Energie Haldenweg 12 CH-4310 Rheinfelden Tel. 061-831 59 81 Fax 061-831 59 83

#### Ihre Sicherheit -Unsere Kernkompetenz -LANZ Stromschienen 25 A - 8'000 A

lanz oensingen ist der marktführende Stromschienenanbieter mit langjähriger Erfahrung und mit einem leistungsstarken kompletten Lieferprogramm:

- Modernste, nach internationalen EN/IEC-Normen typengeprüfte Stromschienen 25 – 6'000 A/1'000 V bzw. 630 – 8'000 A/245 kV

- Schutzarten bis IP 68 korrosionsfest giessharzvergossen

- Rationelle "Just-in-time"-Produktion ISO 9001-zertifiziert

Profitieren Sie von unserer Kernkompetenz. Verlangen Sie Beratung, Offerte, rasche und preisgünstige Lieferung und Montage von

lanz oensingen ag Tel. 062 388 21 21, Fax 062 388 24 24

- LANZ Stromschienen interessieren mich! Bitte senden Sie

- ☐ Könnten Sie mich besuchen? Bitte tel. Voranmeldung! Name/Adresse/Tel.

lanz oensingen ag

CH-4702 Oensingen · Telefon ++41/62 388 21 21