**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

Herausgeber: Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 88 (1997)

Heft: 9

**Artikel:** Moderne integrierte Schaltungen fordern neue

Verbindungstechnologien

**Autor:** Vetter, Martin

**DOI:** https://doi.org/10.5169/seals-902194

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 09.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

Chips mit Taktfrequenzen von über 200 MHz und über 500 Anschlusspins stehen im Rampenlicht der Elektronik. Die Herausforderung der nächsten zehn Jahre wird aber nicht nur darin bestehen, noch leistungsfähigere Chips mit noch mehr Anschlusspins zu entwickeln, sondern diese Megachips auch in Massen und zu vernünftigen Kosten in ein System zu integrieren: mit neuen Gehäusen, mit neuen Leiterplattentechnologien und mit wesentlich verbesserten Bestückungswerkzeugen. Dazu sind neue Konzepte bei den Entwicklungswerkzeugen und bei der Entwicklungsmethodik gefragt. Jede Elektronikfirma und jeder Elektronikentwickler, ob in der Entwicklung, in der Produktion oder beim Test tätig, wird über kurz oder lang mit diesen Fragen konfrontiert sein. Der vorliegende Artikel hat zum Ziel, die Technologietrends und deren Bedeutung für die Elektronikfirmen aufzuzeigen.

## Moderne integrierte Schaltungen fordern neue Verbindungstechnologien

#### ■ Martin Vetter

Der Begriff Verbindungstechnik lässt für die Elektronik mehrere Deutungen zu. Diesem Artikel liegen folgende Überlegungen zugrunde: Elektronikhardware besteht aus aktiven und passiven Komponenten. Dabei werden die eigentlichen Funktionen (Widerstand, Kondensator, Transistor, Diode usw.) auf einem Träger (Isolator) aufgebracht (Montagetechnik) und miteinander (Leiter) verbunden. Diese Definition gilt unabhängig vom Integrationsgrad und ist sowohl für eine Leiterplatte wie auch für eine integrierte Schaltung gültig, das heisst, ein elektronisches Modul ist aus mehreren Hierarchieebenen von miteinander verbundenen Submodulen aufgebaut.

Die einzelnen Hierarchiestufen unterscheiden sich nur durch die geometrische Grösse des Grundrasters, der Integrationsdichte. Auf der tiefsten Ebene, der integrierten Schaltung (IC), werden die Komponenten aus Silizium (Abmessung einer einzelnen Transistorzelle: einige

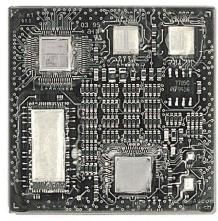

Bild 1 Kompletter 16-Bit-Mikroprozessor mit Flash EPROM, RAM und Interface-Logik auf einem Multichip-Modul von 40×40 mm mit 300 Anschlüssen<sup>1</sup>

Mikrometer) mit Leiterbahnen aus Aluminium und Polysilizium miteinander verbunden. Diese Funktionseinheit wird entweder in ein Gehäuse eingepackt oder direkt auf die nächste Submodulebene (Bild 2) montiert und mit den Verbindungsleitungen dieser Ebene verbunden, und so weiter, bis das gewünschte Modul

Adresse des Autors

Martin Vetter, Dipl. El.-Ing. HTL

Dozent ATIS, Fachstelle Mikroelektronik

Ingenieurschulen Zentralschweiz, 6048 Horw

Email mjvetter@atis.ch

<sup>1</sup> Quelle: Ascom Tech, 3018 Bern

#### **Elektronik**

|                           |         | 1992 | 1995 | 1998    | 2001    | 2004    | 2007    |

|---------------------------|---------|------|------|---------|---------|---------|---------|

| Gatterfunktionen pro Chip | in 1000 | 300  | 800  | 2000    | 5000    | 10 000  | 20 000  |

| Wafer-Durchmesser         | mm      | 200  | 200  | 200-400 | 200-400 | 200-400 | 200-400 |

| Speisung                  | V       | 5,0  | 3,3  | 2,2     | 2,2     | 1,5     | 1,5     |

| Anzahl Anschlüsse         |         | 500  | 750  | 1500    | 2000    | 3500    | 5000    |

| Frequenz (System)         | MHz     | 60   | 100  | 175     | 250     | 350     | 500     |

| Frequenz (Chip intern)    | MHz     | 120  | 200  | 350     | 500     | 700     | 1000    |

Tabelle I Entwicklungstrends bei integrierten Schaltungen

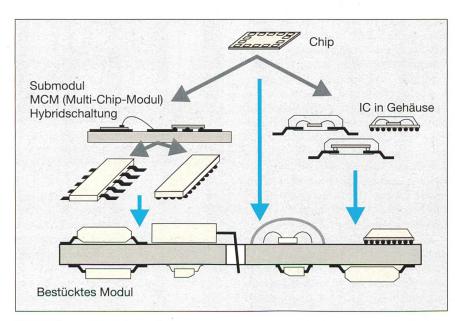

in Form einer bestückten Leiterplatte aufgebaut ist. Wie im Bild dargestellt ist, wird pro Hierarchieebene eine Trägertechnologie mit einer für diese Ebene optimierten Leitertechnologie eingesetzt. Die darauf montierten Submodule können sowohl in bezug auf die Montagetechnik als auch auf den Integrationsgrad stark differieren.

Wenn also Betrachtungen zu Trends in der Verbindungstechnik angestellt werden, so müssen diese zwangsläufig bei der Entwicklung auf der tiefsten Hierarchieebene, der Stufe mit der grössten Integrationsdichte beginnen, auf der Stufe der integrierten Schaltungen.

#### Trends in der IC-Technik

Die Integrationsdichte von ICs wird bei gleichzeitiger Steigerung der Arbeitsfrequenzen stetig vergrössert. Als Beispiele seien – ohne Wertung über deren Nutzen für die Menschheit – das Mobiltelefon, der PC, die Medizintechnik sowie die Unterhaltungselektronik mit Videokameras usw. erwähnt. Bei all diesen Geräten wird, für uns alle schon selbstverständlich, die Leistungsfähigkeit ständig vergrössert; dies bei immer kleineren Abmessungen und tieferem Ener-

gieverbrauch. Die Telekommunikations-, PC-, Medizin- und Consumer-Elektronik hat damit die traditionellen High-Tech-Bereiche Luft- und Raumfahrt sowie die Militärelektronik als Innovationsmotoren abgelöst.

Damit verbunden ist ein Wechsel der Anforderungen an Komponenten und Systeme; anstelle der relativ bescheidenen Stückzahlen von handverlesenen und hochzuverlässigen Komponenten mit exorbitanten Herstellkosten treten heute Massenprodukte (Beispiel: einige Millionen GSM-Mobiltelefone pro Jahr). Dabei stehen nebst dem Miniaturisierungsgrad vor allem hohe Ansprüche an die Produzier- und Testbarkeit, also letztlich an die Herstellkosten, im Vordergrund.

#### **Trends**

Dass die Entwicklung bei den integrierten Schaltungen noch lange nicht abgeschlossen ist, zeigen die gigantischen Investitionen, die jährlich in die Entwicklung neuer Chips sowie in neue Halbleiterwerke investiert werden. In der Tabelle I ist ein Ausschnitt aus der prognostizierten<sup>2</sup> Technologieentwicklung der integrierten Schaltungen von 1992 bis 2007 dargestellt. Für die ganze Aufbauund Verbindungstechnik sind die Trends im Bereich der Anzahl Anschlusspins, der über die Anschlusspins zu übertragenden Frequenzen sowie der Versorgungsspannungen und Verlustleistungen von besonderer Bedeutung.

Ein Beispiel soll dies verdeutlichen: Wird die Anzahl Anschlusspins pro Chip von 250 auf 500 erhöht und wird der Rasterabstand der Landeflächen auf dem Chip konstant auf 100 µm gehalten, so verdoppelt sich die für die Unterbringung der Anschlüsse notwendige Kantenlänge von 4×6,25 mm auf 4×12,5 mm. Die Chipfläche erhöht sich somit um den Faktor vier. Die Rasterabstände auf dem Chip werden nicht durch die Siliziumtechnologie, sondern durch die Möglichkeiten der Bonder limitiert.

So sind die Bonder-Hersteller auf der ständigen Suche nach Lösungen, um auch Chips mit kleineren Rasterabständen verarbeiten zu können. Der Stand der Technik liegt für Produktionsgeräte bei etwa 80  $\mu$ m. Bei einer zweireihigen Verarbeitung sind heute Rasterabstände von 60  $\mu$ m möglich.

### Auswirkungen auf die Gehäusetechnik

Da die meisten Chips in ein Gehäuse montiert werden, nehmen deren Anschlusszahlen im gleichen Masse wie bei den Chips zu. Spricht man bei integrierten Schaltungen von Rasterabständen der Anschlussflächen von 100 µm und weniger, so ist der Stand der Technik auf der Gehäuseseite bei 200 µm angelangt. Es stellt sich damit das Problem, alle Anschlüsse des Chips (Raster < 100 µm) mit den Leiterbahnen im Gehäuse (Raster 200 µm) zu verbinden. Die Länge der Bonddrähte ist aus Stabilitäts- und Produktionsgründen auf ungefähr 2 mm beschränkt. An der Gehäuseperipherie, dem Interface zur Leiterplatte, sind heute Rastermasse von 0,3 mm möglich; 0,5 mm werden aber im Normalfall wegen der zu erwartenden Fertigungsprobleme nicht unterschritten. Die Gehäusegrösse wird somit nicht von der Chipgrösse, sondern von der Anzahl Anschlüsse und dem Rastermass an der Gehäuseperipherie bestimmt.

Bild 2 Aufbau- und Verbindungstechnik

<sup>&</sup>lt;sup>2</sup> Quelle: R. Reynolds, BPA, 1994

Mit der Reduktion des Peripherierasters kann die Gehäusefläche reduziert werden. Aber wer kann heute SMD-Gehäuse mit einer Pinrasterung von 0,3 mm zuverlässig verarbeiten?

Wie der Tabelle I entnommen werden kann, sind Arbeitsfrequenzen auf den Zuleitungen von einigen 100 MHz keine Utopie mehr. Beispielsweise arbeitet ein Pentium-Prozessor schon heute mit einer Frequenz von über 200 MHz. Mit den höheren Frequenzen steigen die Flankensteilheiten der Digitalsignale an. Probleme mit Reflexionen auf Zuleitungen und Übersprechen zwischen den Gehäuseleiterbahnen sowie EMV-Probleme sind die Folge. Zudem steigen die Verlustleistungen auf einige 10 W pro Chip an. Dies trotz einer Reduktion der Versorgungsspannungen von heute 5 V respektive 3 V auf zukünftig 1,5 V. Massnahmen zur Verbesserung der thermischen Eigenschaften der Gehäuse sind damit zusätzlich zu den elektrischen Verbesserungen gefordert.

#### Trends in der Gehäusetechnik

Aus den zum Thema Chip-Trends gemachten Aussagen ist unschwer abzuleiten, dass in der Folge wesentliche Entwicklungen auf der Gehäuseebene zu erwarten sind.

#### **Trends**

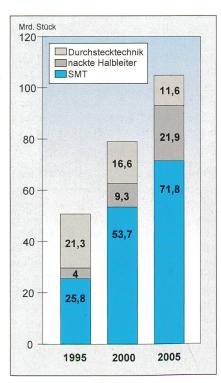

Die Technologieprognosen auf dem Gehäusesektor (Bild 3) bestätigen, dass

Bild 3 Weltweiter Gehäuseeinsatz

| Abkürzung             | Ausdruck                          | Erklärung                                                                                                                                                                                           |  |  |  |

|-----------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| μ-BGA<br>μ-Via<br>BGA | μ-Ball Grid Array Ball Grid Array | Ähnlich BGA, aber auf die Fläche des Chips reduziert<br>Plasmageätztes Via in einer Polyimid-Folie (Dyconex)<br>SMT-Gehäuseart. Verbindung über einen Array von                                     |  |  |  |

|                       |                                   | Lötkugeln auf der Gehäuseunterseite                                                                                                                                                                 |  |  |  |

| Blind Via             |                                   | Via in SMT-Pads in Sackloch-Technik                                                                                                                                                                 |  |  |  |

| Bonddraht             |                                   | Verbindungsdraht von 17 bis 32 µm Durchmesser zwischen<br>Chip und den Anschlüssen im Gehäuse oder auf dem<br>Trägermaterial                                                                        |  |  |  |

| Bonder                |                                   | Verarbeitungsmaschine zum Herstellen der Drahtverbindung (Bonddraht) Chip-Gehäuse mittels Ultraschall                                                                                               |  |  |  |

| Bondpad               |                                   | Kontaktfläche auf dem Chip resp. auf dem Gehäuseträger für den Bonddraht                                                                                                                            |  |  |  |

| Burried Via           |                                   | Via zwischen zwei Leitern bei Multilayer-Leiterplatten ohne durchgehende Bohrung                                                                                                                    |  |  |  |

| COB                   | Chip On Board                     | Montage nackter Chips direkt auf eine Leiterplatte mittels de<br>Bondtechnik                                                                                                                        |  |  |  |

| CSP                   | Chip Size Package                 | Ähnlich BGA, aber auf die Fläche des Chips reduziert                                                                                                                                                |  |  |  |

| DIL-Gehäuse           | Dual-In-Line-Gehäuse              | Gehäuse für die Montage in Durchstecktechnik mit einem<br>Rastermass von normalerweise 2,54 mm                                                                                                      |  |  |  |

| HAL                   | Hot Air Levelling                 | Verzinnungsverfahren bei Leiterplatten                                                                                                                                                              |  |  |  |

| Landless Via          |                                   | Technik zur Reduktion der Via-Restringe                                                                                                                                                             |  |  |  |

| Photo-Via             |                                   | Via, das anstelle einer Bohrung durch Entwickeln einer photoempfindlichen Schicht erstellt wird                                                                                                     |  |  |  |

| PLCC                  | Plastic Leadless Chip Carrier     | Ein SMT-Gehäuse mit Anschlüssen an allen vier Seiten mit<br>einem Pinraster von 1,27 mm                                                                                                             |  |  |  |

| PQFP                  | Plastic Quad Flat Pack            | Ein SMT-Gehäuse mit einem Pinraster von 0,65 mm, 0,5 mm, 0,4 mm oder 0,3 mm                                                                                                                         |  |  |  |

| SBU                   | Sequential Build Up               | Leiterplattentechnologie, die Photo-Vias ermöglicht                                                                                                                                                 |  |  |  |

| SLC                   | Surface Laminated Circuits        | Eine Leiterplattentechnologie, die sehr kleine Vias ermöglicht. Ähnlich wie SBU                                                                                                                     |  |  |  |

| SMD                   | Surface Mount Device              | Oberflächenmontierbare Gehäuse (auch SMT)                                                                                                                                                           |  |  |  |

| SMT                   | Surface-Mount-Technologie         | Oberflächenmontierbare Gehäuse (auch SMD)                                                                                                                                                           |  |  |  |

| SO                    | Small-Outline-Gehäuse             | Ein SMT-Gehäuse mit Anschlüssen an zwei gegenüber-<br>liegenden Seiten mit einem Pinraster von 1,27 oder 1,0 mm                                                                                     |  |  |  |

| Staggered Via         |                                   | Die Sackloch-Technik, bei der direkte Leiterverbindungen<br>nur zwischen zwei benachbarten Leiterebenen möglich sind.<br>Dies erfordert geometrisch versetzte Vias zur nächstunteren<br>Leiterebene |  |  |  |

| TAB                   | Tape Automated Bonding            | Ein Verfahren zur Verdrahtung von IC im Parallelverfahren                                                                                                                                           |  |  |  |

| THT                   | Through-Hole-Technologie          | Komponenten für die Durchstecktechnik                                                                                                                                                               |  |  |  |

Tabelle II Glossar Verbindungstechnik

die konventionellen DIL-Gehäuse sowohl im Anteil als auch bei den Stückzahlen massiv abnehmen werden. Dies bei einer prognostizierten Verdoppelung des weltweiten Gehäuseverbrauchs innerhalb von zehn Jahren.

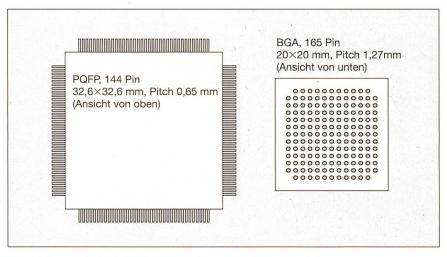

SMT-Gehäuse stellen die Standardtechnik der nächsten zehn Jahre dar. Dabei fällt auf, dass die PLCC-Form mit einem Anschlussraster von 1,27 mm vom Markt verschwinden wird. Nebst den SO-Gehäusen wird sich für Pinzahlen ab ungefähr 30 Pins bis über 250 Pins das PQFP (Bild 4) durchsetzen. Dazu kommen neue Gehäusearten wie das Ball Grid Array (BGA) sowie Chip Size Packages (CSP).

Der Grund für die neuen Formen liegt in der Schwierigkeit, Gehäuse mit einem Pinraster von unter 0,5 mm mit einer hohen Bestückungsausbeute zu verarbeiten. Als Alternative bieten sich Gehäuse mit einem Array aus Zinnkugeln auf der Gehäuseunterseite statt der heute üblichen peripheren Anschlüsse an. In Bild 4 und Bild 5 werden die Grössenverhältnisse klar ersichtlich. Dazu kommt, dass beim BGA-Gehäuse der Abstand zwischen den Lötkugeln 1,27 bis 1,5 mm beträgt und dass damit beim Bestücken ein wesentlich grösserer Versatz toleriert werden kann. Komponenten in BGA-Gehäusen sind heute schon von verschiedenen Herstellern erhältlich. Der Aufbau dieses Gehäuses ist in Bild 5 dargestellt.

#### **Ball Grid Arrays**

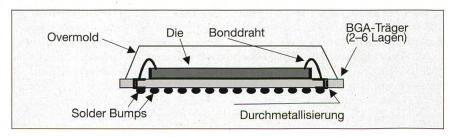

Ein BGA-Gehäuse basiert auf einer Leiterplatte mit 2 bis 6 Leiterebenen. Darauf wird mit konventioneller Bondtechnik oder einem anderen Chipmontageverfahren die integrierte Schaltung montiert und mit den Anschlusspads auf der Oberseite der Leiterplatte verbunden. Auf der Unterseite sind Lötkugeln aufgebracht. Das Gehäuse wird auf einem SMD-Bestückungsautomaten verarbeitet und im Reflow-Verfahren gelötet. Nach-

Bild 4 Grössenvergleich eines 144-Pin-QFP mit einem 165-Pin-BGA

teilig wirkt sich aus, dass die Lötstellen nicht visuell kontrolliert werden können. Wegen der grossen Pinabstände werden aber in der Praxis wesentlich bessere Bestückungsausbeuten als mit PQFP mit einem 0,65-mm-Raster (Bestückungsgenauigkeit, Lötbrücken) erreicht. Dieser Gehäusetyp könnte mittelfristig die Gehäuse mit peripheren Anschlüssen und engem Pinraster ablösen.

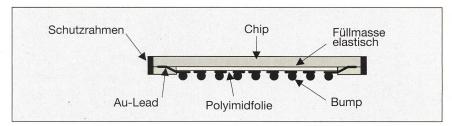

#### Chip Size Package (CSP oder µ-BGA)

Noch in der Entwicklungsphase ist ein neuer Gehäusetyp, der mit modernen SMT-Anlagen verarbeitet werden kann. Ein CSP, auch als μ-BGA bezeichnet, ist flächenmässig nur unwesentlich grösser als ein IC-Chip (Bild 7).

Beim CSP werden die Chipanschlüsse analog dem BGA über ein Array von Lötkugeln mit der Leiterplatte verbunden. Die Lötkugeln sind auf der Chipvorderseite auf einem flexiblen Kunststoffträger aufgebracht, auf dem auch dessen Anschlusspads liegen. Die Verbindungsleitungen führen vom Anschlusspad an der Peripherie des Chips zum Löt-Array, der über die restliche Chipfläche verteilt ist.

Die Chiprückseite ist gleichzeitig die Gehäuseoberseite, an den Kanten wird zum Schutz lediglich ein Kunststoffrahmen aufgebracht. Der Raster der Lötanschlüsse ist gegenüber den BGA-Gehäusen stark reduziert. Zurzeit werden

Raster von 0,75 mm und 0,5 mm diskutiert. Diese kleinen Pinraster werden aber die Anforderungen an die Bestückungssysteme erneut erhöhen.

Da mit CSP bei gleicher Chipgrösse weniger Fläche auf der Leiterplatte als mit COB belegt wird, ist anzunehmen, dass sich auch diese Gehäuseform rasch verbreiten wird.

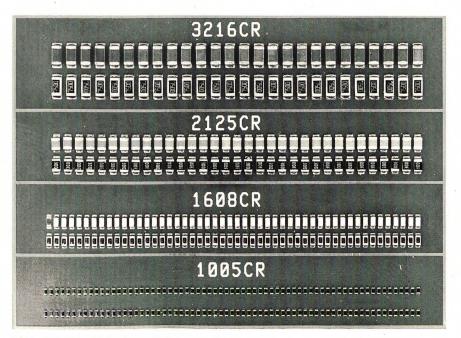

#### **Passive Komponenten**

Widerstände sind heute in der kleinsten Bauform als 1005 (Länge=1 mm, Breite = 0,5 mm), auch als 402 bezeichnet, verfügbar. Bild 8 zeigt einen Ausschnitt aus einer Versuchsleiterplatte mit den heute gängigen Widerstandsgeometrien.

#### Auswirkungen auf die Montagetechnik

Die neuen Gehäuseformen, aber auch sogenannte Fine-Pitch PQFP mit Pinraster bis 0,3 mm, erfordern hochpräzise SMD-Automaten. Array-Gehäuse müssen zudem auf dem SMD-Bestücker, bevor sie auf der Leiterplatte abgesetzt werden, mit einem optischen Inspektionssystem auf fehlende oder deformierte Lötkugeln hin überprüft werden. Da eine optische Kontrolle nach dem Löten wirtschaftlich nicht mehr möglich ist, werden auch neue Anforderungen an die elektrischen Tests gestellt. Eine effi-

ziente Methode stellt der Boundary-Scan-Test dar, wobei die entsprechenden Strukturen schon bei der Entwicklung der Schaltung in den verwendeten IC verfügbar sein müssen.

Die neuen Gehäuse stellen sowohl an die Bestückungstechnik (Präzision, visuelle Inspektion) als auch an die Löttechnik, angefangen vom Zinnauftrag auf die Leiterplatte bis zum Temperaturprofil im Lötofen, sehr hohe Anforderungen an die Prozessbeherrschung. Eine wirtschaftliche und qualitativ hochstehende SMD-Bestückung ist daher mit einem Handbestückungsplatz und einem einfachen Lötofen nicht mehr möglich.

#### Auswirkungen auf die Leiterplatte

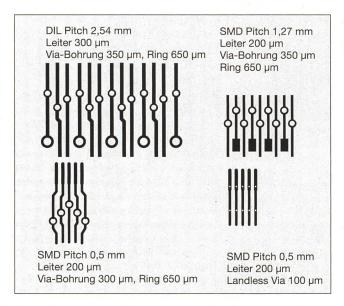

Die neuen Array-Gehäuse erfordern eine grössere Verbindungsdichte unter dem Gehäuse. Da bei kleineren Rastermassen keine Leiterführung zwischen den Anschlüssen möglich ist, werden alle Anschlüsse über Vias (Leiterplattendurchführungen) auf Innenlagen geführt und von dort verteilt. Zudem erfordern die grossen Anschlusszahlen auf kleinstem Raum eine Erhöhung der Verbindungsdichte zwischen den einzelnen Gehäusen. Kleinere Vias ohne Restring (Landless Via) ermöglichen diese hohe Verbindungsdichte.

Für die Bestückung mit modernen SMD-Gehäusen sind plane Lötober-flächen unabdingbar. HAL-Verzinnungen können somit nicht mehr eingesetzt werden. Als Alternativen sind Oberflächen mit chemisch aufgebrachten Nickel- und Goldschichten sowie Palladiumschichten in Betracht zu ziehen.

Die hohen Arbeitsfrequenzen können zu EMV-Problemen auf der Leiterplatte führen. Kontrollierte Leitungsimpedanzen und neue Konzepte der Abschirmung und der Speisungsverdrahtung müssen bei der Leiterplattenentflechtung berücksichtigt werden.

#### Trends bei der Leiterplattentechnik

Leiterplatten werden heute standardmässig mit Leiterbreiten und Leiterabständen von 150 bis 200 µm gefertigt. Die Via-Bohrungen liegen für eine wirtschaftliche Fertigung über 350 µm. Um das Via muss wegen des Fertigungsprozesses und der Fertigungstoleranzen ein Kupferring von rund 500 µm gelegt werden. Somit sind nicht die Leiterbreiten und Leiterabstände die Begrenzung der Verbindungsdichte. In einem viel grösseren Masse wirken sich die Durchmesser der Vias aus. Die Grenze für eine mechanische Bohrung liegt zudem bei einem Bohrdurchmesser von 250 µm. Eine Re-

Bild 5 Aufbau eines BGA(Ball Grid Array)-Gehäuses

Bild 6 Grössenvergleich von SMD-Gehäusen<sup>3</sup>

Bild 7 Chip Size Package

duktion des Bohrdurchmessers auf dieses Mass verteuert aber die Leiterplattenkosten überproportional. Bild 9 zeigt einen Vergleich zwischen verschiedenen Geometrien auf.

Die Entwicklungstrends bei IC und Gehäusen sowie die neuen Anforderungen an die Verbindungsdichte erfordern eine neue Generation von Leiterplatten mit feineren Leitern und wesentlich kleineren Vias beziehungsweise reduzierten Kupferringen um die Vias.

#### **Trends**

Mit der Reduktion des Via-Durchmessers und des Kupferringes kann bei gleichbleibenden Standardleiterbreiten von 200 bis 150 µm eine wesentlich höhere Leiterdichte erreicht werden. In Bild 9 sind verschiedene Leiterplattengeometrien im gleichen Massstab abgebildet. Im Vergleich zu der heute üblichen Geometrie (SMD, Pitch 0,5 mm, Leiterbreite 200 µm, Vias mit Restring) wird der mit einer Via-Technik ohne Restring (Landless Via) erzielbare Gewinn an Leiterdichte augenfällig. Werden zudem noch Sacklöcher (Blind Via) eingesetzt, so können die Lötflächen der SMT-Komponenten gleichzeitig als Via zur nächsttieferen Leiterebene verwendet werden.

Da für das mechanische Bohren bei ungefähr 250 µm Bohrdurchmesser die Grenze der wirtschaftlichen Machbarkeit erreicht ist, drängen sich andere Bohrtechnologien auf. Im Einsatz stehen heute Laserbohren, Plasmaätzen und die Photoviatechnik. Plasmaätzen und die Photoviatechnik sind Parallelverfahren, das heisst, alle Löcher werden gleichzeitig

können nur sinnvoll eingesetzt werden, wenn die isolierende Schicht relativ dünn ist. Beim Laserbohren werden die Löcher analog dem mechanischen Bohren sequentiell erzeugt. Dieses Verfahren wird erst von wenigen Leiterplattenherstellern eingesetzt. Es ist in der Anwendung noch sehr teuer.

gefertigt. Die neuen Parallelverfahren

#### Ausgewählte Technologien

Schweizerische Firmen sind massgeblich an der Entwicklung neuer Verfahren beteiligt und geniessen eine weltweite Reputation. Insbesondere wurden das Dycostrate-Verfahren und die SBU(Sequential Build Up)-Technik zum Teil von Schweizer Firmen entwickelt.

Landless-Via-Technik

Ein wesentlicher Schritt zur Erhöhung der Verbindungsdichte ist die Reduktion des Restrings um ein Via. Mit der Landless-Technik kann dieser auf ein Minimum reduziert oder gänzlich weggelassen werden. Bei Landless-Verfahren wird anstelle des normalen Negativphotoprozesses mit einem Positivprozess gearbeitet. Der Ätzresist wird nach dem Entwickeln des Photolacks in einer Schichtdicke von einigen Mikrometern galvanisch aufgebracht (Elektrophorese-Verfahren). Dabei werden, im Gegensatz zum Negativprozess, die Kupferflächen in den Via-Löchern direkt geschützt. Kritisch bei diesem Verfahren ist der alkalische Ätzprozess. Sind nebst den metallisierten Löchern auch reine Befestigungslöcher notwendig, so müssen diese in einem zweiten Bohrprozess gefertigt werden.

#### SBU/SLC-Technologie

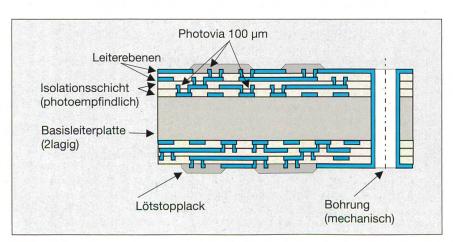

Die Technologie basiert auf einem normalen, mit Kupfer laminierten Leiterplatten-Basismaterial. Im Gegensatz zur normalen Multilayer-Technik werden bei diesem Verfahren die Isolationsschichten als Flüssigresist aufgebracht und die Via-Löcher im Photoprozess gefertigt. Die Kupferleiter werden analog der Metallisierung der Bohrlöcher beim Multilayer-Print gefertigt. Der Aufbau ist in Bild 10 dargestellt.

Der Herstellungsablauf lässt sich wie folgt beschreiben:

Auf normalem Basismaterial werden die Leiterbahnen auf der Vorder- (Leiter 1) und Rückseite hergestellt.

Bild 8 SMD-Widerstände mit verschiedenen Baugrössen

<sup>&</sup>lt;sup>3</sup> Quelle: Testleiterplatte der Firma Hilpert AG, Baden-Dättwil

#### **Elektronik**

Bild 9 Grössenvergleich verschiedener Leiterplattentechnologien

- Die Leiterplatte wird im Flüssigprozess mit einer Isolationsschicht (Verfahren analog dem Aufbringen von Flüssig-Lötstopplack) überzogen (ca. 35 μm) und die Löcher für die Sackloch-Via mittels Photoprozess gefertigt (Photo-Via-Technik). Das Verfahren ist das gleiche wie für das Aufbringen des Flüssig-Lötstopplackes bei Multilayer-Prints.

- 3. Die zweite Kupferlage wird chemisch auf die Isolationsschicht aufgebracht und anschliessend galvanisch auf die endgültige Schichtdicke verstärkt. Auch dieses Verfahren entspricht der normalen Multilayer-Technik. Die Leiterbilder der zweiten Leiterebene werden mit dem normalen Photoprozess gefertigt. Die Via-Verbindungen zur ersten Leiterebene entstehen automatisch mit dem Aufbringen des Kupfers der zweiten Lage.

- 4. Eine weitere Isolationsschicht wird über der Leiterebene 2 aufgebracht und die Via-Löcher für die Verbindung

- der Leiterebenen 2 und 3 gefertigt. Die Leiterebene 3 wird analog der Ebene 2 gefertigt.

- 5. Die Leiterebene 4 wird analog dem vorher beschriebenen Verfahren aufgebracht. Allfällige Löcher für die Durchmetallisierung auf die Rückseite und für mechanische Aufgaben werden gebohrt. Die Durchmetallisierung der gebohrten Löcher wird gefertigt.

- 6. Der Lötstopplack wird aufgebracht.

Bei diesem Verfahren können nur benachbarte Leiterebenen miteinander verbunden werden (Sackloch-Technik). Sollen beispielsweise Leitungen der Leiterebene 1 mit der Ebene 3 verbunden werden, so ist zuerst mit einem Via die Ebene 1 auf Ebene 2 zu verbinden. Die Ebene 2 wird mit der Ebene 3 mit einem zweiten, zum ersten Via versetzten Via verbunden. Man spricht hier von einem Staggered Via. Der Leiterplattenaufbau sollte analog den Multilayer-Prints symmetrisch erfolgen.

Bild 10 SBU-Technik<sup>4</sup>

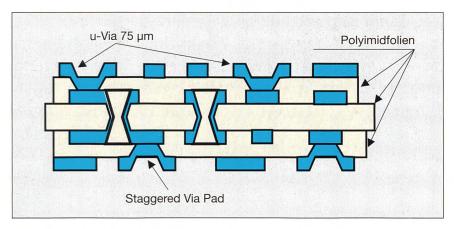

Dycostrate-Technologie

Die Dycostrate-Technologie wurde von der Firma Dyconex in Zürich entwickelt. Sie basiert auf sehr dünnen Polyimidfolien, deren Via-Löcher ( $\mu$ -Via) mittels Plasma geätzt werden.

Der Herstellungsablauf<sup>5</sup> sieht wie folgt aus:

- 1. Auf einen mit Kupferfolie beschichteten Polyimidträger werden die Vias in das Kupfer geätzt.

- 2. Mittels Plasma werden die Via-Bohrungen im Polyimid ausgeätzt. (Beim Plasmaätzen werden nur organische Stoffe angegriffen.)

- 3. Die Bohrungen werden metallisiert.

- 4. Das Leiterbild wird auf beiden Seiten eingebracht.

- Mit einem Kleber wird auf jeder Seite ein einseitig mit einer Kupferfolie beschichteter Polyimidträger auflaminiert.

- Die Sackloch-Vias werden in die Kupferfolie eingeätzt.

- Die freigelegten Polyimidflächen werden mittels Plasma bis auf die darunterliegende Kupferschicht ausgeätzt.

- 8. Die beiden Oberflächen werden metallisiert und so die inneren mit den äusseren Ebenen verbunden.

- 9. Das Leiterbild wird auf die beiden äussersten Ebenen aufgebracht.

- Die nächsten beiden Polyimidfolien werden auflaminiert, die Vias und die Leiterebenen gefertigt usw.

Analog dem SBU-Verfahren werden auch beim Dycostrate-Verfahren keine durchgehenden Via-Löcher gefertigt. Sind Signale über mehr als zwei Leiterebenen zu führen, so sind auch bei diesem Verfahren Staggered Vias notwendig. Ein möglicher Aufbau mit vier Leiterlagen ist in Bild 11 dargestellt. Die Folien können zudem auf normale Leiterplatten mit mehreren Multilayer-Ebenen aufgebracht werden.

#### Auswirkungen auf die Entwicklungswerkzeuge

Der Kostenanteil für das mechanische Bohren der Vias an den Herstellkosten liegt für komplexe Prints bei über 20%. Aus diesem Grund sind die heute erhältlichen Autorouter auf eine Minimierung der Anzahl Vias ausgelegt. Bei den Parallelprozessen zur Via-Herstellung (Plasmaätzen und Photo-Via-Technik) wird deren Herstellung billig. Mit dem Landless-Verfahren wird zudem die Verbin-

<sup>&</sup>lt;sup>4</sup> Quelle: Unterlagen der Firmen Multiboard-Electronics, 9473 Gams, und Ascom-Tech, 3018 Bern

<sup>&</sup>lt;sup>5</sup> Quelle: Unterlagen der Firma Dyconex AG, 8052 Zürich, und GS Präzisions AG, 6403 Küssnacht am Rigi

Bild 11 Dycostrate mit vier Leiterebenen

dungsdichte durch die Anzahl der Vias nicht beeinflusst. Eine Anpassung der Werkzeuge an die neuen Gegebenheiten wird daher notwendig. So ist beispielsweise das Plazieren von Vias im SMD-Pad heute noch nicht mit allen Systemen möglich.

Durch die feineren Geometrien und die zunehmende Anzahl Leiterebenen werden Layoutwerkzeuge mit integrierter Design-Rules-Überwachung unumgänglich. Durch die Mischung von verschiedenen Technologien (Beispiel: Dycostrate auf normalen Leiterplatten) müssen zudem die Designregeln für jede Leiterebene separat definiert werden. Und die CAD-Systeme müssen diese Regeln auch verarbeiten können. Hier sind allerdings auch die Leiterplattenhersteller gefordert, ist es doch in dieser Branche heute noch unüblich, verbindliche Layoutregeln zu definieren und für ein Leiterplattenlayout vorzuschreiben.

Unter dem Begriff Layoutregeln sind nicht mehr nur die geometrischen Vorgaben wie Leiterabstände, Leiterbreiten, Abstand Via zu Leiterbahn usw. zu verstehen. Auch die elektrischen Eigenschaften wie Leiterwiderstand, Leiterimpedanz, Verzögerungszeiten, Laufzeitdifferenz zwischen zwei Signalen, elektrisches Übersprechen zwischen zwei Leitungen, Reflexionsverhalten usw. bilden bei modernen Systemen einen festen Bestandteil des Regelsets. So erfordern digitale Taktsignale andere Impedanz-, Laufzeit- und Übersprechregeln als beispielsweise ein 230-V-Netz auf dem gleichen Print. Moderne Autorouter müssen deshalb in der Lage sein, Netze mit verschiedenen Layoutregeln richtig zu verdrahten.

#### Der Paradigmenwechsel bei der Hardware-Entwicklung

Die heute allgemein übliche Arbeitsteilung bei der Entwicklung elektronischer Module sieht so aus, dass das Elektronikerteam die Schaltung entwirft und dem Konstrukteur – oder bei kleineren Firmen dem externen Dienstleister – die Leiterplattenentflechtung überlässt. Diese Stelle entwirft die Leiterplatte nach

konstruktiven und - hoffentlich auch produktionstechnischen Grundsätzen. Die elektrischen Gegebenheiten treten dabei eher in den Hintergrund. Mit den neuen Anforderungen an elektronische Module - hohe Frequenzen, grosse Leistungen, hohe Packungsdichte, EMV-Normen - muss eine derartige Arbeitsteilung zwangsläufig scheitern. Mehrere Redesign-Zyklen sind die Folge. Hier muss zwingend ein Paradigmenwechsel in der Arbeitsteilung erfolgen: Der Schaltungsentwickler oder das Entwicklerteam ist auch für das Leiterplattenlayout sowie die Produzier- und Testbarkeit verantwortlich. Diese entflechten den Print selbst oder bezeichnen zumindest im Schema die verschiedenen Netze und die dafür geltenden Regeln. Die neue Arbeitsweise verlangt also verbindliche Layoutregeln der Leiterplattenhersteller, durchgängige Entwicklungssysteme mit regelgetriebenen Werkzeugen und den Willen der Entwickler, sich an diese Regeln auch zu halten. Im Gegensatz zur Entwicklung von Leiterplatten erfolgt die Entwicklung von integrierten Schaltungen schon lange nach diesen Grundsätzen. Schaltungen mit mehreren Millionen von Transistoren sind ohne klare Designregeln und die entsprechenden Entwurfswerkzeuge nicht denkbar.

#### **Ausblick**

Die aufgezeigten Trends sind keine futuristischen Träume, sondern eine Realität, die zur Kenntnis genommen werden muss. Das Ende der Entwicklung ist nicht abzusehen. Die Entwicklungsmethodik, die Entwicklungswerkzeuge und die Produktionstechnologien werden in den nächsten Jahren grundlegende Veränderungen erfahren: vom Schema zum High Level System Design, vom einfachen Entflechtungssystem zum komplexen, regelgetriebenen Entwicklungswerkzeug, von der SMD-Handbestückung zum hochpräzisen Bestückungsautomaten mit visueller Kontrolle aller Komponenten vor der Montage. Damit werden massive Veränderungen in der Arbeitsteilung, im Arbeitsbild und in der Projektorganisation einhergehen. Jede Firma muss die Frage für sich beantworten, ob und wie weit sie sich für die Entwicklung von Leiterplatten und die Produktion von Elektronikmodulen ausrüsten will. Dabei ist zu beachten, dass nebst den Investitionen auch das Halten einer kritischen Masse von qualifizierten Mitarbeitern eine unabdingbare Voraussetzung für den Erfolg ist. Neue Formen der Zusammenarbeit von Firmen, insbesondere der KMU, müssen gefunden werden.

# Des circuits intégrés modernes exigent de nouvelles technologies de connexion

Des puces cadencées à plus de 200 MHz et comprenant plus de 500 broches de raccordement sont sous les feux de la rampe de l'électronique. Mais le vrai défi des dix prochaines années ne sera pas seulement le développement de puces encore plus performantes et comprenant encore plus de broches, mais l'intégration de masse et pour un coût raisonnable de ces mégapuces dans un système: Grâce à des boîtiers nouveaux, des cartes imprimées issues de nouvelles technologies et à des outils à équiper considérablement améliorés. On devra pour cela faire appel à de nouveaux concepts pour les outils et la méthodologie de développement. Un jour ou l'autre, tous ceux qui sont actifs dans l'électronique – firmes, développeurs, producteurs ou testeurs – devront faire face à ces questions. Le présent article veut présenter les tendances dans ce secteur et leur importance pour les firmes concernées.