|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 86 (1995)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 3                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | 64-MBit-DRAM : Mikroelektronik für das 21. Jahrhundert                                                                                                                                                                    |

| <b>Autor:</b>       | Göltner, Christoph / Horninger, Karlheinz                                                                                                                                                                                 |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-902422">https://doi.org/10.5169/seals-902422</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

In der Mikroelektronik verstärkt sich der Trend zu Standardprodukten, die in hohen Stückzahlen kostengünstig gefertigt werden. Die Fähigkeit, Standardprodukte wettbewerbsfähig zu produzieren, stellt nicht nur den Zugang zu den etablierten Elektronikmärkten sicher, sondern eröffnet auch die Teilnahme in den wichtigsten neuen Zukunftsmärkten. Der DRAM-Speicher nimmt aufgrund seines Marktanteils und der technologischen Vorreiterrolle heute schon eine Schlüsselrolle in der Mikroelektronik ein und wird sie weiter ausbauen. Siemens und IBM gehören zu den ersten Herstellern, die in einem Kooperationsprojekt den 64-MBit-DRAM zur Serienreife entwickelt haben. Siemens wird 1996 die Serienproduktion in Dresden starten.

# 64-MBit-DRAM – Mikroelektronik für das 21. Jahrhundert

■ Christoph Göltner

und Karlheinz Horninger

Die Mikroelektronik zählt umstritten zu den dynamischsten Branchen der Wirtschaft. Ihr Einfluss auf fast alle anderen Industriezweige wächst beständig. Neben der Elektro- und Elektronikindustrie sind auch Telekommunikations- und Automobilindustrie Beispiele, bei denen die Anwendung der modernsten Mikroelektronikkomponenten der entscheidende Faktor für erfolgreiche Produkte geworden ist.

Innerhalb der Mikroelektronik spielt der DRAM (Dynamic Random Access Memory) eine zentrale Rolle, die sich an seinem Marktanteil innerhalb der Branche und dem harten Wettbewerb widerspiegelt. Gemessen am Marktvolumen dieser Industrie von rund 95 Milliarden US-\$ im Jahr 1994, stellen DRAM bereits einen Anteil von etwa 22% dar. Die Tendenz ist steigend und wird auf über 30% im Jahr 2000 geschätzt.

Nach anfänglicher Dominanz amerikanischer Unternehmen (in den 70ern) übernahmen nach kurzer Zeit die Japaner die führende Rolle in der DRAM-Produktion und konnten diese in den 80er Jahren stetig

ausbauen. Zur Überraschung der etablierten Industrie betraten Ende der 80er Jahre die Koreaner das Spielfeld und drangen stetig in die japanisch-amerikanische Domäne ein. Innerhalb von nur fünf Jahren konnte sich die koreanische Firma Samsung zum Marktführer bei DRAM (14% Marktanteil im Jahre 1993) etablieren. Andere koreanische Firmen verfolgen die gleiche Strategie, um mit dem Brückenkopf DRAM in andere Segmente profitabler Mikroelektronikprodukte vorzudringen.

Die europäische Elektronikindustrie konnte in der Anfangsphase in diesem Markt keine prägende Rolle spielen. Nach anfänglichem Engagement mehrerer europäischer Hersteller ist es im internationalen Wettbewerb nur Siemens gelungen, in diesem Segment zu bleiben. Nach einer technologischen Aufholjagd, beginnend mit dem 1-MBit- und 4-MBit-Speicher, hat Siemens Anfang der 90er Jahre wieder den Anschluss an die Weltspitze erreicht. Aufbauend auf diesem Erfolg wurde die Entwicklung und Produktion in der 16-MBit-Generation kontinuierlich fortgeführt. Mit diesem Engagement wurde das Know-how aufgebaut, um als gleichberechtigter Partner in Kooperationen mit an der internationalen Spitze aufzutreten.

Um ihre Position weiter auszubauen, hat sich Siemens als eine der ersten Firmen in

## Adresse der Autoren:

Dr. Christoph Göltner und Dr. Karlheinz Horninger,

Siemens AG, Bereich Halbleiter, Postfach 80 17 09,

D-81617 München.

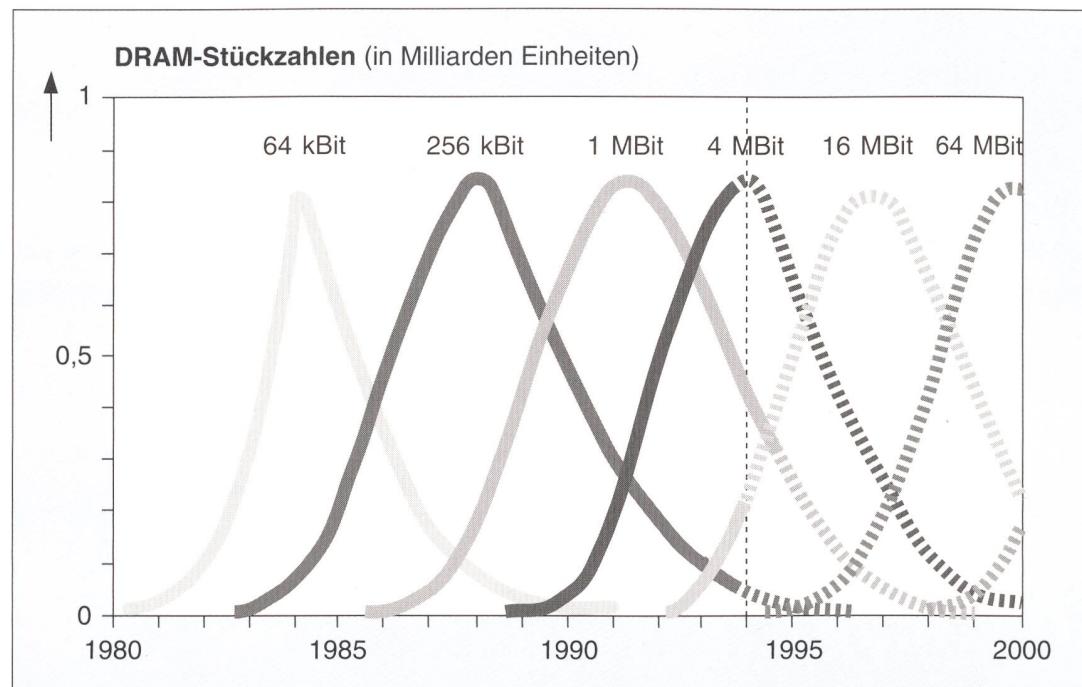

Bild 1 Entwicklung der DRAM-Stückzahlen

dieser Industrie entschieden, eine Produktionsstätte für den 64-MBit-Chip in Dresden zu errichten. Damit hat jetzt wieder ein europäischer Hersteller den Anspruch auf einen Platz in der Spitzengruppe in diesem vielleicht härtesten Technologierennen unterstrichen.

## DRAM - Kernprodukte heute und morgen

Die drei folgenden Themen stehen häufig im Mittelpunkt der Diskussion um den DRAM und geben Einblick in die geschäftsbestimmenden Faktoren:

- Koppelung des DRAM an den PC-Markt;

- neue Anwendungsfelder und Wachstumspotentiale für DRAM;

- technologische Möglichkeiten und Grenzen der DRAM-Speicher.

## Koppelung des DRAM an den PC-Markt

Die bisher dominierende und wichtigste Anwendung von DRAM-Speichern ist der PC, wo sie dem Zentralprozessor als schnelle Datenpuffer dienen. Nachdem sich der PC erst beim kommerziellen und zunehmend auch beim privaten Nutzer als Standardprodukt etabliert hatte, zeichnete sich rasch ab, dass für die PC-Hersteller der Preis zum entscheidenden Erfolgsfaktor wurde. Zwangsläufig wurde der immense Kostendruck auf die Zulieferer weitergeleitet. Während der Markt für das Kernstück des PC, den Prozessor, im wesentlichen monopolistisch war und sich erst jetzt in einer Umbruchsphase befindet, wurde das

zweite Kernstück des PC, der DRAM, als Standardkomponente schon immer von zahlreichen Herstellern angeboten.

Die Erklärung ist einfach: Beim Mikroprozessor ist der logische Aufbau des Chips die bestimmende Größe. Dieser ist hochkomplex, eng mit dem Betriebssystem verknüpft und lässt sich in seiner Gesamtheit patentrechtlich schützen. Beim DRAM hingegen ist die Logik von vergleichsweise untergeordneter Bedeutung und kann daher nicht als Differenzierungskriterium für das Produkt dienen. Bei einem homogenen Zellenfeld des DRAM (über 80 % der Fläche) liegt das Erfolgskriterium für den Hersteller in der Beherrschung des Produktionsprozesses, das heißt das Erreichen einer hohen Ausbeute (funktionsfähige Chips pro Wafer) in kurzer Zeit bei geringsten Kosten.

Unter diesen Randbedingungen entstand ein vom Kunden gefordertes Standardprodukt mit sogenannter Plug-in-Kompatibilität (DRAM-Bausteine aller Hersteller sind im PC austauschbar), bei dem nur noch der Preis zum erfolgsentscheidenden Kriterium der Hersteller wurde. Aufgrund der enormen Stückzahlen (z. B. etwa 1 Mrd. Stück für 4 MByte im Jahre 1994) entstand ein Markt, der – einzigartig in der Mikroelektronik – völlig frei von Systemorientierung den typischen Gesetzen eines Commodity-Produktes gehorcht.

## Neue Anwendungsfelder und Wachstumspotentiale für DRAM

Die Produktionszahlen der wichtigsten DRAM-Anwendungen – in PC, Notebook und Workstation – wachsen stetig mit zwei-

stelligen Zuwachsraten. Der Markt fordert immer leistungsfähigere Produkte, die bei der rasanten technologischen Entwicklung auch realisierbar sind. Neue Kundensegmente lassen sich durch komfortablere Software in kleineren, leichteren und mobilen Produkten erschließen, die dem rasanten Wachstum der Computerindustrie weiter Vorschub leisten. Der Nukleus dieser Entwicklung ist der Zentralprozessor, der immer leistungsfähiger wird. Um diesen Fortschritt dem Gesamtsystem zugute kommen zu lassen, sind entsprechend immer größere DRAM-Speicher gefordert. Dieser Trend wird mit zwei Daumenregeln der Computerindustrie beschrieben:

- Die Prozessorleistung verdoppelt sich seit 1984 alle zwei Jahre (Joy-Law).

- Die DRAM-Speicherdichte vervierfacht sich alle drei Jahre.

Das unbegrenzte Fortschreiben dieser Vorhersagen lässt sich zwar nicht plausibel ableiten, dennoch sind bisher alle Skeptiker dieser Leitsätze von der Realität dementiert worden. Von einer Fortsetzung dieses Trends bis zum Beginn des 21. Jahrhunderts kann ausgegangen werden, denn die Entwicklung der Nachfolgegenerationen für diesen Zeitraum sind schon in vollem Gange.

Bei den DRAM lässt sich diese Generationenfolge in Bild 1 gut erläutern. Als Faustregel hat sich seit Anfang der 80er Jahre bestätigt, dass sich die Speicherdichte pro Jahr um 60 % vergrößert, was zu einer Verdopplung in drei Jahren führt. Was für die laufende Produktion von derzeit 1-MBit-, 4-MBit- und 16-MBit-Chips gilt, wird vom Abschluss der Entwicklung beim 64-MBit-

Chip und der bereits fortgeschrittenen Entwicklung beim 256-MBit-Chip bestätigt. So wird diese Vorhersage bis zum Anfang des nächsten Jahrtausends Gültigkeit haben.

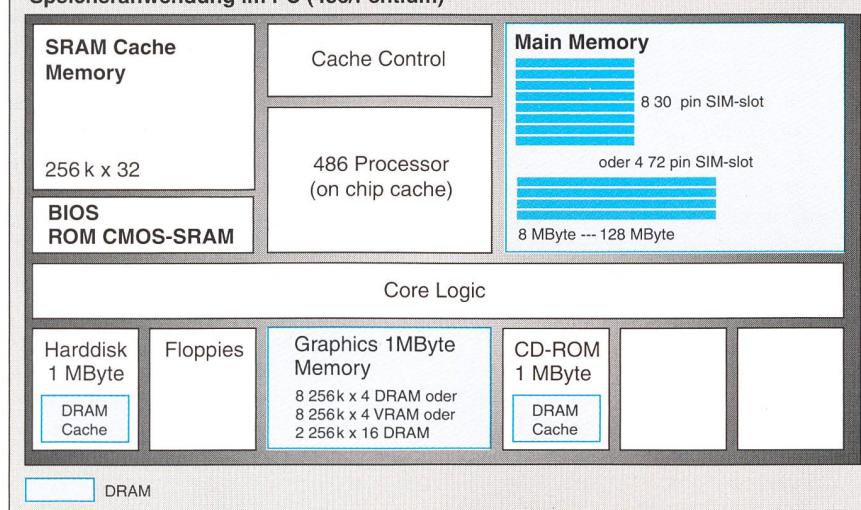

Bild 2 zeigt den Einsatz von DRAM in einem heute typischen PC (Sommer 1994). Neben der ursprünglichen Nutzung von DRAM im PC als Zwischenablage für den Prozessor entstehen zahlreiche neue Anwendungen, welche die verschiedenen Speichermedien eines PC-Systems optimal verknüpfen. DRAM werden als Puffer zwischen langsameren Massenspeichern wie Floppy disk und CD-ROM und dem Prozessor benötigt, um zu akzeptablen Reaktionsgeschwindigkeiten für den Bediener zu kommen. Die steigenden Anforderungen an die Grafikmöglichkeiten eines PC, besonders für den Multimediaeinsatz, erfordern neben spezialisierten Grafik-Koprozessoren auch die entsprechende DRAM-Kapazität, die in einer dezentralen Anordnung zahlreiche Vorteile bietet.

Zusätzlich zum Einsatz im PC wachsen neue Marktsegmente in der Peripherie des PC, wie zum Beispiel Drucker, Scanner usw. Die Telekommunikation verlangt in Infrastruktur und Endgeräten zunehmend grosse Mengen an schnellen und preisgünstigen Speichern, deren Anforderungen am besten mit DRAM abgedeckt werden. Diese Segmente haben heute einen Marktanteil von ungefähr 15% der DRAM-Produktion, werden aber relativ an Bedeutung gewinnen.

Ein weiteres Marktsegment mit grossen Zuwachsraten ist die Consumer- bzw. Entertainment-Elektronik. Als charakteristisches Beispiel für neue DRAM-Anwendungen seien hier Electronic Games genannt. Einer jährlichen PC-Produktion von etwa 40 Millionen Stück weltweit im Jahr

1994 steht eine etwa gleich grosse Zahl von Spielkonsolen gegenüber. Wenn auch der DRAM-Bedarf in der heutigen Generation für diese Konsolen noch kleiner ist als jener für PC (kleiner 1 MByte gegenüber mehr als 4 MByte), so wird bereits die nächste Gerätengeneration ab 1995 die Leistungsfähigkeit von Low-End-Workstations besitzen. Man wird dreidimensionale Grafik in Echtzeit interaktiv handhaben, was enorme Mengen von schnellen DRAM-Speichern verlangt.

Weitere neue Multimediaanwendungen für den DRAM-Speicher finden sich im interaktiven Fernsehen, in Video on Demand, Virtual-Reality-Maschinen, Data-Superhighways usw., Aktivitäten, deren Durchsetzung am Markt vielfach noch schlecht oder missverstanden wird. Unabhängig von der Richtigkeit solcher Prognosen im Einzelfall ist umstritten, dass die neuen Medien grosse Mengen an schnellen Speichern erfordern, die kostengünstig nur von DRAM abgedeckt werden können. Solche Multimediacomponenten werden bereits von kleinen Spezialanbietern angeboten und werden im zunehmenden Masse für die grossen Elektronik- und Computerkonzerne die erfolgsentscheidenden Wachstumsmärkte von morgen sein.

## Technologische Möglichkeiten und Grenzen der DRAM-Speicher

Die regelmässige Struktur der Speicherzellenfelder eines DRAM (im Gegensatz zu Logik-IC wie z.B. Mikroprozessoren) bietet ein enormes Potential zur Produktivitätssteigerung durch Integration. Die Generationen der DRAM-Speicher werden in Sprüngen von einem Faktor vier ihrer Kapazität gemessen.

Es muss allerdings unterstrichen werden, dass die Hersteller den Chip auch in-

nerhalb jeder Generation «shrinken»; durch einen ständigen Optimierungsprozess über Design und bessere Nutzung des Fertigungsequipments wird die Chipfläche systematisch ohne grundsätzliche Änderung der Technologie verkleinert. Das Ziel, das mit dem Shrink verfolgt wird, ist offensichtlich: je kleiner die Chipfläche, um so mehr Chips können pro Wafer erzielt werden.

Generationenwechsel sind allerdings nur durch die Einführung neuer technologischer Verfahren möglich. Dabei gerät jede neue DRAM-Generation immer dichter an die physikalischen Grenzen. Als charakteristisches Merkmal jeder Generation wird gerne die kleinste Linienbreite auf dem Chip benutzt, die beim 1-MBit-Chip noch bei 1 µm, beim 64-MBit-Chip nur noch bei 0,4 µm liegt.

Grenzen werden aus heutiger Sicht bei 0,05 µm gesehen. Damit liesse sich noch ein 16-GBit-DRAM produzieren. Man rechnet, dass ab dem Jahr 2015 solche Speicher als Massenprodukt verfügbar sind.

Die Investitionen für die Entwicklung und Produktion wachsen dabei in Dimensionen, die schon bei der 16-MBit-Generation bei mehreren Milliarden US-Dollar liegen, bei künftigen Generationen wird der finanzielle Aufwand weiter steigen; quantitative Prognosen abzugeben ist heute allerdings Spekulation. Die Beherrschbarkeit dieser neuen Technologien an den physikalischen Grenzen führt zu zahllosen schwer einschätzbares Risiken. Konsequenterweise versucht jeder Hersteller, diese Risiken zu verteilen. Dabei haben sich zahlreiche Allianzen zwischen den Halbleiterherstellern etabliert. Dies trifft vor allem auf die Entwicklung der neuen DRAM-Generation zu, Allianzen für die spätere Produktion werden oft separat gehandhabt.

Bei der 64-MBit-Generation, die bis über die Jahrhundertwende die dominierende DRAM-Generation sein wird, haben IBM und Siemens ihre Entwicklungsressourcen vereinigt und als eines der ersten Entwicklungsteams weltweit die technische Machbarkeit des 64-MBit-DRAM demonstriert. Im folgenden wird Einblick über den Ablauf eines konkreten Entwicklungsprojektes an der technologischen Front gegeben, der nicht nur die technischen Details, sondern auch Abläufe einer internationalen Zusammenarbeit beschreibt.

## Das 64-MBit-Projekt

### Geschichte

Anfang 1989 begannen erste Gespräche zwischen Siemens und IBM über eine Entwicklungskooperation auf dem Gebiet des

Speicheranwendung im PC (486/Pentium)

Bild 2 DRAM-Einsatz im PC

|                              |                                                                                  |

|------------------------------|----------------------------------------------------------------------------------|

| ► Strukturgrösse             | 0,4 µm                                                                           |

| ► Substrat                   | p- (0,01 bis 0,03 Ω · m)                                                         |

| ► Speicherzelle              | Buried-plate trench cell (Grabenzelle)                                           |

| ► Kapazität der Zelle        | 0,044 pF ±10%                                                                    |

| ► Isolierung                 | Shallow trench                                                                   |

| ► Wortleitung                | TiSi/Polysilizium                                                                |

| ► Kontakte                   | Wolfram                                                                          |

| ► Zahl der Metallebenen      | 3 – mit zwei Kontaktebenen                                                       |

| ► Planarisierung             | CMG (Chemical Mechanical Polish)                                                 |

| ► Zellen je Bitleitung       | 128                                                                              |

| ► Zellgrösse                 | 0,875 µm x 1,775 µm (1,5 µm <sup>2</sup> )                                       |

| ► Chipgrösse                 | 18,07 mm x 10,71 mm (193 mm <sup>2</sup> )                                       |

| ► Betriebsspannung           | 3,3 ±0,3 V                                                                       |

| ► Organisation               | 64 Mbit x 1; 16 Mbit x 4; 8 Mbit x 8; 4 Mbit x 16                                |

| ► Funktionsmodi              | Fast-page, Static Column, Self Refresh, Write-per-bit                            |

| ► Zugriffszeit ( $T_{RAC}$ ) | 40 ns, 50 ns, 60 ns                                                              |

| ► Stromaufnahme              | 200 µA (in Ruhe)<br>125 mA (Betrieb mit $T_{RAC} = 50$ ns; 4000 Auffrischzyklen) |

Bild 3 Technische Daten des 64-MBit-DRAM

64-MBit-Speichers. In mehreren Gesprächen und Workshops wurden die in den Forschungslaboreien der beiden Firmen bisher erarbeiteten Ergebnisse vorgestellt und verglichen. Es zeigte sich bald, dass man zwar unterschiedliche Konzepte verfolgte, dass der Stand der Entwicklung jedoch durchaus vergleichbar war. Um die Zusammenarbeit so wirtschaftlich wie möglich zu machen, musste ein gemeinsames Konzept gefunden werden. Auf weiteren Treffen einige man sich auf ein technisches Entwicklungskonzept sowie auf die Struktur und die Kosten der gemeinsamen Entwicklung. Im Frühjahr 1990 wurde schliesslich der Vertrag zwischen IBM und Siemens unterschrieben. Im Herbst 1994 wurde die Entwicklung mit dem Erreichen der gesetzten Ziele abgeschlossen.

Die Standortfrage für die Technologieentwicklung wurde zunächst durch die IBM-Pilotlinie ASTC (Advanced Semiconductor Technology Center) festgelegt. Diese Pilotlinie wurde damals gerade neu gebaut. Ihr Reinraum entspricht der Klasse 1 (d.h. weniger als ein Staubteilchen mit einem Durchmesser von 0,25 µm in etwa 30 l Luft). Die Entwicklung erfolgt auf Siliziumscheiben mit 200 mm (8 Zoll) Durchmesser. Die Pilotlinie liegt auf dem IBM-Gelände von East Fishkill (Staat New York) im malerischen Hudson Valley, 120 km nördlich von New York. Parallel zum 64-MBit-Entwicklungsprojekt arbeiten auf der gleichen Pilotlinie Siemens, IBM und seit 1992 auch Toshiba gemeinsam an der nächsten Technologiegeneration, dem 256-MBit-Speicher.

Während damit klar war, dass die Technologieentwicklung des 64-MBit-Projektes in East Fishkill erfolgt, musste man über den Standort für die Entwicklung des Designs und der Testverfahren verschiedene Vor- und Nachteile abwägen. Einerseits sollten Technologie- und Designentwicklung so nahe wie möglich beisammen sein, andererseits liegt der DRAM-Entwicklungsstandort von IBM, Burlington im Staat Vermont, 400 km nördlich von East Fishkill. Unter Abwägung der verschiedenen Randbedingungen entschloss man sich, die Design- und Testentwicklung in Burlington durchzuführen. Als dritter Entwicklungsstandort des Projekts kam 1992 der IBM-Standort in Yasu, Japan, dazu. Dort hin wurde die Gehäuseentwicklung des 64-MBit-Chips verlagert.

Das 64-MBit-Projekt wird als eigenständige Organisation geführt und umfasst die Bereiche Technologie, Design, Testen, Gehäusetechnik und Zuverlässigkeit. Die einzelnen Entwicklungsmannschaften bestehen aus gleich vielen Ingenieuren von Siemens und IBM. Managerpositionen sind nicht doppelt besetzt, sondern auf Manager der beiden Firmen aufgeteilt. Siemens-Ingenieure können IBM-Managern unterstellt sein und umgekehrt. Die Personalverantwortung für die einzelnen Mitarbeiter liegt jedoch immer bei den Vorgesetzten der eigenen Firma. Diese Projektstruktur hat sich in den letzten drei Jahren ausserordentlich gut bewährt und war mit ein Grund dafür, dass über Firmengrenzen hinweg ein gemeinsamer Teamgeist entstanden ist.

Ziel der gemeinsamen Entwicklung ist, eine Technologie für den 64-MBit-Spei-

cher sowie das dazugehörige Produkt zu entwickeln. Mit dieser Technologie können dann mit entsprechenden Änderungen auch Logikschaltungen realisiert werden. Die technischen Daten des 64-MBit-Speichers sind in Bild 3 zusammengefasst.

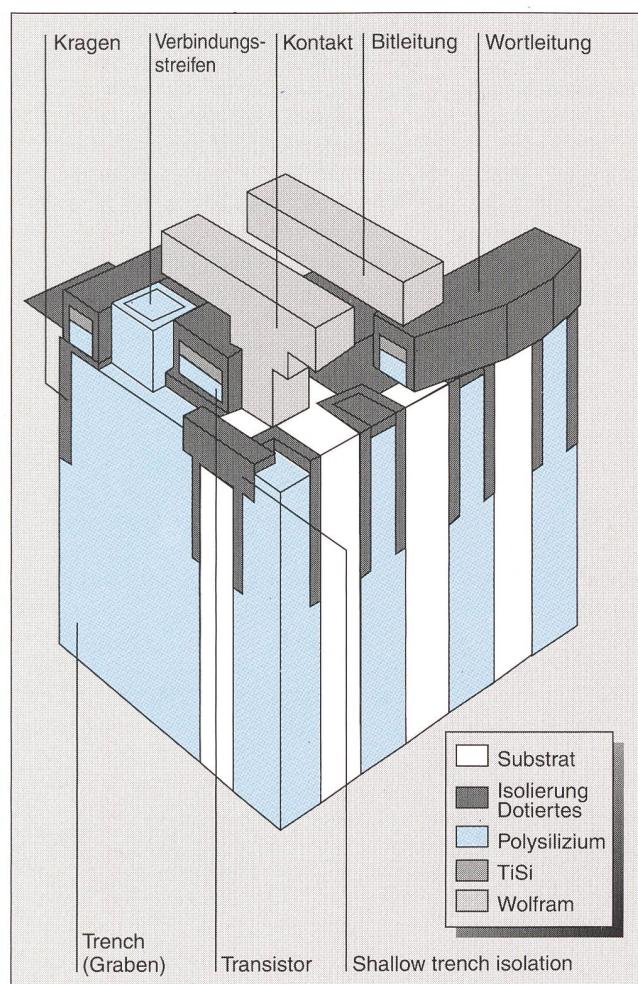

## Der Fertigungsprozess

Der Fertigungsprozess ist ein CMOS-Prozess mit einer minimalen Strukturbreite von 0,4 µm und einer nominellen Betriebsspannung von 3,3 V. Als Speicherzelle wird eine spezielle Form der Grabenzelle (buried-plate trench cell) verwendet. Bei dieser Grabenzelle (etwa 7 µm tiefe Gräben) entsteht die gemeinsame, vergrabene Zellplatte durch Ausdiffusion an der Grenzschicht zwischen Grabenzelle und Substrat (zwischen blauem/weissem Gebiet). Diese Zellplatte ist durch das Substrat (weiss) von den Auswahltransistoren getrennt. Durch einen Kontakt in der Zelle (surface trap) wird die individuelle Elektrode des Speicher kondensators mit dem Auswahltransistor verbunden. Bild 4 zeigt einen dreidimensionalen Querschnitt der Speicherzelle mit Speicher kondensator und Auswahltransistor.

Die Isolation der einzelnen aktiven Elemente (p-Kanal- und n-Kanal-Transistoren) erfolgt ebenfalls mit Hilfe von Gräben, allerdings mit deutlich geringerer Tiefe (shallow trench isolation). Mit diesem Verfahren kann neben hoher Packungsdichte auch eine hohe Leckstromfestigkeit von eng benachbarten Transistoren erreicht werden. Die Kanallänge der n-Kanal-Transistoren beträgt 0,35 µm, die der p-Kanal-Transistoren 0,5 µm. Als Verdrahtungsebenen hat der Prozess eine Polyzid (Polysilizium/TiSi-Schicht), eine Wolfram- und zwei Aluminium-Lagen (hier nicht eingezeichnet). Die Kontakte zwischen den Metallebenen werden mit Wolfram aufgefüllt. Zwischen den verschiedenen Abscheideprozessen wird zur Planarisierung der Chipoberfläche das sogenannte CMP-Verfahren (Chemical Mechanical Polishing) eingesetzt. Dieses Verfahren stellt sicher, dass vor der Belichtung jeder kritischen Ebene die Chipoberfläche möglichst planar ist. Dies ergibt eine bessere Auflösung für Belichtung und Ätzung in diesem mehrlagigen Prozess. Der Anspruch an die Tiefenschärfe der Belichtungsgeräte wird entspannt. Man kann daher Geräte mit grosser numerischer Apertur und dadurch verbesselter Auflösung verwenden. Es werden zwei Generationen von Lithographiegeräten verwendet: für die unkritischen Ebenen (etwa 75% der Maskenebenen) wird die bereits in der Fertigung des 16-MBit-Speichers erprobte i-line-Lithographie eingesetzt, für die kritischen Ebenen die neuere DUV-Lithographie (deep UV). Hervor-

zuheben ist die Skalierbarkeit der Technologie, die durch die Verwendung von Prozessneuerungen bereits jetzt einen evolutionären Pfad zur weiteren Strukturverkleinerung (Shrink-Pfad) abgesichert hat. Zukünftige Shrinks sollten daher – ausser weiterer Ebenen mit DUV – keine kostspieligen Innovationen mehr benötigen.

### Produktdesign und Gehäusetechnik

Sämtliche Schaltungen sind für den Betrieb mit der für den 64-MBit-Chip spezifizierten Spannung von  $3,3 \pm 0,3$  V ausgelegt. Entscheidend für einen schnellen Lesezugriff ist sowohl eine kleine RC-Zeitkonstante der Wortleitung als auch der Betrieb dieser Wortleitung mit einer überhöhten Spannung (boosted voltage). Das Problem der geringen RC-Zeitkonstante wurde im 64-MBit-DRAM durch die Verwendung einer Architektur mit globalen und lokalen Wortleitungen (master and local wordlines) gelöst.

Obwohl die Chipgröße von dynamischen Speichern mit jeder Generation etwa um den Faktor 1,4 wächst, nimmt die Geschwindigkeit dieser Bausteine ebenfalls zu. Der 64-MBit-Speicher von Siemens

und IBM wurde für eine Lesezugriffszeit (TRAC) von 40 bis 60 ns entwickelt, mit dem ein breiter Bereich von Systemanwendungen abgedeckt werden kann.

Die dazugehörigen Zykluszeiten betragen 80 bis 110 ns. Die Datenbreite des Bausteins von  $\times 4$ ,  $\times 8$  oder  $\times 16$  wird durch Bondoptionen bei der Montage des Chips festgelegt. Der Speicher kann im Fast-Page- oder im Write-per-Bit-Mode betrieben werden. Ein integrierter Zähler auf dem Chip ermöglicht den stromsparenden Betrieb bei Low-Power-Versionen. Um mit Speichern der Vorgängergeneration kompatibel zu sein, kann während der Montage zwischen 4000 und 8000 Auffrischzyklen durch Bondoptionen gewählt werden.

Die Stromaufnahme des 64-MBit-Speicher ist stark von der Zykluszeit sowie der Anzahl der Auffrischzyklen abhängig. Für eine Zugriffszeit von 50 ns und 4000 Auffrischzyklen beträgt die spezifizierte Stromaufnahme 130 mA. Im Ruhemodus ist die Stromaufnahme weniger als 0,2 mA. Die Ein- und Ausgangspegel sind mit den im LVCMOS- und LVTTL-Standard festgelegten Werten kompatibel.

Derzeit sind zwei Gehäusetypen für den 64-MBit-Speicher genormt: SOJ- und dünn-

ere TSOP-II-Gehäuse. Die Organisationsformen  $\times 4$  und  $\times 8$  werden in SOJ- oder TSOP-II-Gehäuse mit 34 Anschlässen, die  $\times 16$ -Konfiguration nur in TSOP-II-Gehäuse mit 54 Anschlässen montiert. Unabhängig von der Zahl der Anschlüsse haben alle Gehäuse eine Grösse von  $12,7 \times 22,2$  mm<sup>2</sup>. Das Standard-Anschlussraster von 1,27 mm wurde für die  $\times 16$ -Bauform auf 0,8 mm reduziert, um bei derselben Gehäuselänge 54 Anschlüsse unterzubringen.

### Elektrische Ergebnisse

Der 64-MBit-Chip (Bild 5) hat eine Fläche von 193,6 mm<sup>2</sup> ( $18,07 \times 10,71$  mm<sup>2</sup>). Messungen am aktuellen Designstand des Siemens-IBM-Speichers zeigen, dass die beschriebenen Geschwindigkeitsziele sowie der Funktionsumfang vollständig erreicht werden. Die verschiedenen Betriebsarten, Organisationen und Auffrischmodi arbeiten zuverlässig über den gesamten Spezifikationsbereich. Kennzeichen eines robusten Produktdesigns ist ein weiter Arbeitsbereich bezüglich Betriebsspannung, Temperatur und Variation der Prozessparameter.

Bild 4 Querschnitt einer Speicherzelle des 64-MBit-DRAM

### Zusammenarbeit

Beide Firmen haben sich das erste Mal auf eine solche partnerschaftliche Zusammenarbeit eingelassen. Dementsprechend aufmerksam wurden daher in der Anfangsphase alle Aktivitäten des Teams von der Leitung beider Firmen beobachtet. Nach fast fünf Jahren Zusammenarbeit kann man dieses Modell der Kooperation als ausserordentlich erfolgreich bezeichnen. Sicher gab es am Anfang Schwierigkeiten, Unstimmigkeiten und Probleme, die besonders in den Mentalitätsunterschieden zwischen den USA und Deutschland, aber auch in den unterschiedlichen Firmenkulturen begründet lagen. Diese und ähnliche Probleme konnten jedoch immer mit gutem Willen von beiden Seiten gelöst werden (auch wenn die Lösung manchmal etwas lange dauerte). Es trifft sicher zu, dass die Entwickler beider Unternehmen zu einem Team zusammengewachsen sind und sich auch als solches verstehen. Das hohe fachliche Niveau der Mitarbeiter, die von beiden Firmen in das Projekt entsandt worden sind, sowie die gegenseitige Wertschätzung haben sicher auch zu diesem Teamgeist beigetragen. Es ist auch gelungen, das Wissen und die Erfahrungen auf dem DRAM-Gebiet, das Siemens- und IBM-Mitarbeiter mitgebracht haben, in das Projekt einzubringen.

Im Sommer 1994 gaben IBM, Siemens und Toshiba die gemeinsame Entwicklung

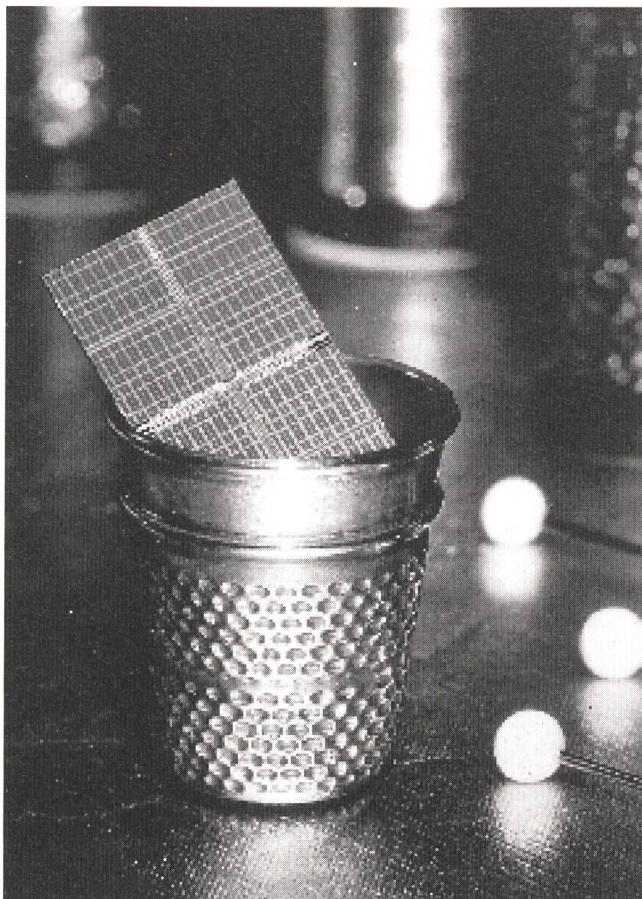

**Bild 5 Der 64-MBit-DRAM im Fingerhut**

Der Speicherinhalt entspricht 4000 Schreibmaschinenseiten (unkomprimiert).

und Prozess zu gewährleisten. Voruntersuchungen und Tests zur Qualität werden bereits im frühen Stadium der Entwicklung durchgeführt. Das abschliessende Testprogramm am letzten Designstand stellt sicher, dass das Produkt seine Marktreife erreicht hat.

### Serienproduktion in Dresden

Im Dezember 1993 fiel bei Siemens die Entscheidung, in Dresden ein neues Mikroelektronikzentrum mit einem Investitionsvolumen von ungefähr 2,7 Milliarden DM zu errichten. Es zählt zu den weltweit modernsten Standorten und ist das erste seiner Art in Europa. Neben einer Pilotlinie für den 256-MBit-DRAM sowie weiterer Forschungseinrichtungen für die Mikroelektronik ist der Schwerpunkt dieser Fabrik die Serienproduktion des 64-MBit-DRAM. Die ersten Wafer werden bereits ein Jahr nach dem ersten Spatenstich (Frühjahr 1994) in der «Fab» prozessiert.

Das Einfahren der Linie wird mit der Produktion von 16-MBit-DRAM erfolgen. Diese werden heute von IBM und Siemens in Essonne bei Paris in Serie gefertigt. Sukzessive wird nach der Stabilisierung des bereits beherrschten 16-MBit-Prozesses der neue Produktionsprozess für 64 MBit «hochgerampt», wie es im Fachjargon heißt.

Nachdem die Diskussion in wirtschaftspolitischen Kreisen lange genug die Wettbewerbsfähigkeit der europäischen Mikroelektronikindustrie in Frage gestellt hat, ist nun ein konstruktiver Ansatzpunkt gelungen, der diesem wichtigen Wirtschaftssektor auch in Europa einen entscheidenden Impuls geben wird.

der zweiten Generation des 64-MBit-Chips bekannt. Dieser geschränkte Baustein wird die Packungsdichte weiter erhöhen und erlaubt, den Chip in einem schmaleren Gehäuse zu montieren. Die Erfahrungen aus der erfolgreichen trilateralen Zusammenarbeit beim 256-MBit-Chip werden sich nicht nur aus technologischer Sicht vorteilhaft auf die Shrinkversion des 64-MBit-Chips auswirken, sondern auch diesem multikulturellen Entwicklungsteam zugute kommen.

tige Kennenlernen einer neuen Schlüsselkomponente ausschlaggebend für den Erfolg des Endproduktes ist. Die Erfahrungen, welche die Kunden beider Firmen in den nächsten Monaten einbringen werden, werden in den nächsten Designstand einfließen. Dieser wird dann einer Reihe von Zuverlässigkeitstests unterworfen, um Qualität und Langzeitstabilität von Produkt

### Kundenbemusterung

Die Ergebnisse, die man mit den voll funktionsfähigen Mustern des 64-MBit-Chip-Speichers gesammelt hat, legen es nahe, solche Muster an ausgewählte Kunden zu verteilen. Ziel einer solchen Kundenbemusterung ist, das Produkt möglichst frühzeitig beim Kunden zu testen und von ihm zu erfahren, an welchen Stellen Änderungen oder Anpassungen wünschenswert sind. Gleichzeitig hilft dies dem Kunden, sich frühzeitig mit der neuen Speichergeneration zu beschäftigen und Erfahrungen zu sammeln. Bei diesen ersten Mustern liegen oft noch einige Parameter ausserhalb der Spezifikation. Für die meisten Kunden ist dies jedoch kein Nachteil, da das frühzei-

## 64-MBit-DRAM – microélectronique pour le 21<sup>e</sup> siècle

En microélectronique, la tendance va toujours plus vers les produits standard fabriqués en grande quantité et à moindres frais. La capacité de fabriquer des produits standard de manière compétitive assure non seulement l'accès aux marchés électriques déjà établis, mais elle permet de tailler des parts sur les nouveaux marchés importants de l'avenir. La mémoire DRAM occupe déjà aujourd'hui en raison de sa situation sur le marché et de son rôle de précurseur sur le plan technologique une position clé en microélectronique, position qu'elle va certainement encore renforcer. Siemens et IBM font partie des premiers fabricants qui dans un projet de coopération ont développé le 64-MBit-DRAM jusqu'à sa maturité de produit de série. Siemens lancera en 1996 la production en série à Dresde.