|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 83 (1992)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 9                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Angst vor Asic-Entwicklung? : Migration : ein Mittel zur Risikoreduktion                                                                                                                                                  |

| <b>Autor:</b>       | Giovannini, Clive                                                                                                                                                                                                         |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-902820">https://doi.org/10.5169/seals-902820</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 07.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# **Angst vor Asic-Entwicklung?**

## **Migration – ein Mittel zur Risikoreduktion**

Clive Giovannini

**Obwohl der Einsatz von applikationsspezifischen ICs (Asics) technische und finanzielle Vorteile bietet, scheuen kleine und mittlere Betriebe oft davor zurück, diese auch einzusetzen. Der vorliegende Beitrag beschreibt, was unter Asics heute zu verstehen ist, wo diese sinnvoll eingesetzt werden können, mit welchen Kosten und Risiken dabei etwa zu rechnen ist, und welche Entwicklungswerkzeuge dazu benötigt werden. Eine Möglichkeit, das Entwicklungsrisiko, d.h. die Folgen des Redesign-Risikos, zu senken, ist die Wahl von möglichst hersteller- und technologieunabhängiger Design-Software.**

**Bien que l'utilisation d'ICs spécifiques de l'application (Asics) offre des avantages techniques et financiers, les petites et moyennes entreprises redoutent souvent encore de les utiliser. Le présent article décrit ce qu'il faut aujourd'hui entendre par Asics, où on peut les utiliser de manière judicieuse, les coûts et les risques auxquels il faut s'attendre et les outils nécessaires à leur développement. Une possibilité d'abaisser le risque inhérent au développement, c'est-à-dire le risque de redesign est de choisir un logiciel de design ouvert.**

### **Adresse des Autors**

Clive Giovannini, Dipl.-Ing. HTL, Migration Technology GmbH, Industriestrasse 42, 8117 Fällanden.

Immer kürzere Entwicklungszeiten, höhere Integrationsdichte, höhere Qualität und geringere Gestehungskosten, das sind die Forderungen, die an den heutigen Elektronik-Entwickler gestellt werden. Eine Antwort auf diese Forderungen stellen die applikationsspezifischen ICs mit ihren feldprogrammierbaren (PAL, PLD, FPGA usw.) und maskenprogrammierbaren (Gate Arrays, Sea of Gates, Standard-Zellen usw.) Varianten dar.

Wieso aber werden diese neuen Techniken nicht mit Begeisterung aufgenommen? Ein wichtiger Grund dafür dürfte sein, dass das ständig wachsende Angebot der Asic-Technologien sowie die Vielfalt der CAE-Entwicklungssysteme ein Planungsteam schon in der Phase der Produktspezifikation vor die Aufgabe stellen, den optimalen Lösungsweg für die spezifische Applikation zu finden.

Im vorliegenden Beitrag werden deshalb nach einer ersten kostenorientierten Betrachtung zum Asic-Einsatz die heute verbreiteten Asic-Technologien mit ihren bevorzugten Einsatzgebieten sowie mögliche Auswahlkriterien für die Technologiewahl sowie die gängigen Entwurfswege (nach Schnittstellen und Designmethodik) vorgestellt. Eine Betrachtung der Anforderungen, die an unterstützende Entwurfswerkzeuge (CAE-System) gestellt werden, ist wegen der engen Kopplung mit der Technologie unerlässlich. Es werden die wesentlichen Punkte genannt, die bei einer Entscheidung berücksichtigt werden sollten. Abschliessend wird ein Weg vorgestellt, der bei Asic Designs geringes Entwicklungsrisiko mit Investitionssicherheit bei der CAE-Software verbindet.

### **Wirtschaftlichkeit**

Der Einsatz von Asics erfordert von traditionellen Hardware-Entwicklern, die ihre Schaltungen mit Standard-Bausteinen auf Platinen aufbauen, ein Umdenken. Lötkolben, Papier und Logikanalysator werden durch Maus, Bildschirm und Logiksimulator ersetzt. Während beim Breadboarding Schaltungsanalyse und Modifikation direkt vom Entwickler am Prototypen durchgeführt werden, findet bei der Asic-Entwicklung der Hauptteil der Arbeit auf dem Computer statt. (CAE-Unterstützung). Nicht nur die Schaltungsentwicklung, sondern auch die Schaltungsverifikation findet auf dem Computer statt; das physikalische Verhalten der Schaltung wird durch Softwaremodelle nachgebildet. Somit kann erst beim Einsatz des Hardware-Prototyps auf der Platine nachgewiesen werden, dass der Entwurf auch wirklich funktioniert. Diese späte Verifikation ist eine emotionale Barriere, die noch manches Unternehmen davon abhalten dürfte, den Schritt zum Asic zu wagen, obwohl dadurch die Entwicklungs- und Produktionskosten reduziert werden könnten. Dennoch sind die wirtschaftlichen Aspekte einer Asic-Lösung so attraktiv, dass sie hier noch einmal genannt werden sollen.

Die Tabelle I zeigt den Einfluss von Asics auf die Kosten eines Gerätes. Kostenvorteile ergeben sich nicht nur in der Produktions-, sondern auch in der Entwicklungsphase. Während beispielsweise bei der Asic-Entwicklung mit CAE-Software die Funktionalität inklusive Zeitverhalten durch Simulationen nachgewiesen wird – diese können für die elektrischen Streubereiche nach Temperatur usw. durchgeführt werden –, wird beim Breadboarding schon in dieser Phase, methodisch be-

| <b>Materialkosten</b>             |                          | <b>Tabelle 1</b><br><b>Asics beeinflussen die Kosten</b> |

|-----------------------------------|--------------------------|----------------------------------------------------------|

| Platten                           | Platz-Ersparnis          |                                                          |

| elektronische Bauteile            | Stückzahl-Ersparnis      |                                                          |

| Verkabelung                       | geringerer Aufwand       |                                                          |

| Stromversorgung                   | geringerer Aufwand       |                                                          |

| Mechanik                          | Platz-Ersparnis          |                                                          |

| <b>Direkte Fertigungskosten</b>   |                          |                                                          |

| Bestückung der Platten            | weniger Bauteile         |                                                          |

| Test der Platten                  | weniger Fehlerquellen    |                                                          |

| Fertigung der Baugruppen          | weniger Baugruppen       |                                                          |

| Test der Baugruppen               | weniger Baugruppen       |                                                          |

| Endmontage                        | weniger Baugruppen       |                                                          |

| Endtest                           | weniger Fehlerquellen    |                                                          |

| <b>Indirekte Fertigungskosten</b> |                          |                                                          |

| Einkauf                           | geringerer Aufwand       |                                                          |

| Lager                             | geringerer Aufwand       |                                                          |

| Eingangsprüfung                   | geringerer Aufwand       |                                                          |

| Arbeitsvorbereitung               | geringerer Aufwand       |                                                          |

| Qualitätssicherung                | geringerer Aufwand       |                                                          |

| <b>Fixkosten</b>                  |                          |                                                          |

| Vertrieb                          | kein Einfluss            |                                                          |

| Service                           | weniger Service-Einsätze |                                                          |

| Marketing                         | innovative Produkte      |                                                          |

| Verwaltung                        | kein Einfluss            |                                                          |

| Entwicklung                       | Investitionen            |                                                          |

| <b>Gewinne</b>                    |                          |                                                          |

| Gewinn aus Produkten, brutto      | höherer Produktnutzen    |                                                          |

| Garantie-Leistungen               | weniger Ausfälle         |                                                          |

dingt, eine Fehlerquelle eingebaut. Die gesamte Schaltung verhält sich entsprechend den Daten der physikalischen Einzelkomponenten. Werden baugleiche ICs verschiedener Hersteller eingesetzt, so kann, bedingt durch Fertigungstoleranzen und Temperatureinflüsse, Breadboarding schon fast zum Glücksspiel werden. Bei einer Asic-Realisierung kann dieses Risiko durch die entsprechenden Simulationen eingegrenzt werden. Eine Simulation mit minimalen und maximalen Toleranzparametern ist meist ausreichend, streuen die Elemente eines Asics doch in die gleiche Richtung. Ein weiterer, teilweise unterschätzter Aspekt ist die Zuverlässigkeit. Diese ist für Asics und Standard-ICs durchaus vergleichbar. Die Zuverlässigkeit eines Gesamtsystems hängt von der Anzahl der ICs, Lötstellen und mechanischen Kontakten ab. Integration schafft also Zuverlässigkeit, und das bedeutet neben weniger Service-Einsätzen geringere Kosten und natürlich mehr Qualität. Während die bisher

genannten Aspekte die kurz- und mittelfristigen Vorteile einer Schaltungsumsetzung mit Asics zeigen, ist langfristig zu bedenken, dass abhängig von der gewählten Asic-Technologie ein hohes Mass an Kopiersicherheit gegeben ist.

## Asic-Technologien

Die Wahl der Prozesstechnologie, ob CMOS, Bicmos, GaAs usw., ergibt sich meist zwangsläufig aus den elektrischen Parametern. So werden für Höchstgeschwindigkeitsapplikationen im Giga-Hertz-Bereich nur GaAs- oder bipolare Technologien zur Auswahl kommen, während sich für Standardapplikationen im Bereich bis zu hundert Mega-Hertz die weitverbreiteten CMOS-Prozesse eignen. In den folgenden Ausführungen werden die Asics grob in drei Gruppen klassiert. Diese Aufteilung bietet sich nicht nur wegen der damit realisierbaren Schaltungskomplexität (klein, mittel, hoch) an, sondern auch wegen deren unter-

schiedlicher Entwicklungs- und Fertigungsmethodik.

## Programmierbare Logikschaltungen

PLD, EPLD, PLA, LCA, FPGA usw. sind vorgefertigte Bausteine, deren Funktion in internen Speicherzellen festgelegt ist. Die Verknüpfung der Elemente zur benötigten Funktion erfolgt durch Programmieren von Antifuses oder Speicherzellen (EPROM, RAM) mit einfachen Programmiergeräten. Heute sind bereits FPGA mit über 5000 verfügbaren Gattern erhältlich, die meisten Entwürfe findet man im Bereich von etwa 500 bis 2500 genutzten Gattern. Die Schaltungseingabe erfolgt meist graphisch an PCs (oder Workstations) oder durch eine Beschreibung der Schaltung durch logische Tabellen oder State-Machine-Sprachen. Die Layoutgenerierung sowie die physikalische Realisierung erfolgt im Regelfall im eigenen Hause.

## Semi-Custom-Schaltungen

Gate Arrays stehen als sogenannte Master bis auf die Metallisierungsebenen vorgefertigt zur Verfügung. Sie enthalten eine von der Mastergrösse abhängige, feste Anzahl von Transistoren. Die Verbindung der Transistoren zu logischen Funktionen wird durch die Aufbringung von Metallverbindungen (Maskenprogrammierung) von Halbleiterherstellern durchgeführt. Dafür sind je nach Herstellerprozess eine bis drei Metallisierungsebenen vorgesehen, wobei die einfache Faustregel gilt: je mehr Metallisierungsebenen, desto komplexer (mehr nutzbare Transistoren) und schneller (kürzere Verdrahtungswege) kann der Entwurf sein. Bei Standardzellen-ICs werden alle (zwölf bis achtzehn) Maskenebenen gefertigt. Der Entwickler ist also beim Entwurf nicht an eine bestimmte Anzahl von Transistoren gebunden. Die verbrauchte Siliziumfläche ist immer dem Design angepasst. Während bei Gate Arrays spezielle Transistorstrukturen zur Verfügung stehen, die optimal auf ihre Funktionalität entwickelt wurden, werden Blöcke mit extremer Packungsdichte (RAM, ROM) von den Siliziumherstellern auf Standardzellen-IC angeboten. Es sind heute bereits Gate Arrays mit über 100000 verfügbaren Gattern erhältlich, Standardzellenentwürfe erreichen Komplexitäten von mehr als 200000 nutz-

baren Gattern. Die meisten Entwürfe findet man im Bereich von ca. 1000 bis zu ungefähr 20000 genutzten Gattern. Die Schaltungseingabe erfolgt meist graphisch an Workstations (oder PCs). Es lässt sich ein Trend erkennen, Schaltungen mit einer Gatter-Komplexität ab etwa 20 KBit durch Verhaltensbeschreibungen in einer Hochsprache zu erfassen und anschliessend mit Logik-Synthese-Programmen die Netzliste zu generieren. Die Layoutgenerierung sowie die physikalische Realisierung erfolgen im Regelfall durch den Siliziumlieferanten.

## Full-Custom-Schaltungen

Damit wird die höchste Integrationsdichte (> 500000 Transistoren) erreicht. Schaltungsteile werden manuell auf Geschwindigkeit und Flächenverbrauch optimiert. Daten-Highways (Busstrukturen) werden auf die optimale Strukturbreite ausgelegt, umfangreiches Partitionieren der Schaltung in zusammengehörende Module wird meistens manuell durchgeführt. Wie Standardzellen-ICs werden diese Schaltungen über alle Maskenebenen gefertigt. Zusätzlich zu dem weit höheren Entwicklungsaufwand ist noch eine Verifikation des Designs über alle Transistoren erforderlich. Damit sind diese Bausteine erst ab sehr hohen Stückzahlen wirtschaftlich und für die breite Asic-Anwendung ungeeignet.

## Generelle Auswahlkriterien

Asics finden heute in allen Bereichen der Industrie ihr Einsatzgebiet. Welche Asic-Technologie im konkre-

ten Anwendungsfall am besten einzusetzen ist, lässt sich anhand der folgenden Randparameter eingrenzen:

- technisches Pflichtenheft

- verfügbare Entwicklungszeit

- Entwicklungskosten

- Komplexität

- einsetzbare CAD-Systeme

- geplante Produktionsstückzahlen

- Bausteinkosten

Während das Pflichtenheft durch die elektrischen Anforderungen meist die Prozesstechnologie bestimmt (Hochvolt-Applikationen, Treiberfähigkeit der Baustearausgänge, Stromverbrauch, Temperaturfestigkeit usw.), bestimmen die anderen Faktoren weitestgehend die Fertigungs- und Entwicklungsmethodik. Für kleine Stückzahlen (z.B. Vorserie) eignen sich beispielsweise programmierbare Logikschatungen. Für mittlere bis grosse Stückzahlen (ab einigen 100 bis über 50000) eignen sich, je nach Entwicklungszeit und Komplexität, Gate Arrays oder Standard-Zellen-ICs. Full Custom-Schaltungen werden hauptsächlich bei einem Bedarf ab mehreren 100000 Bausteinen bevorzugt. Die Tabelle II zeigt die typische Asic-Vergleichsmatrix.

Hat man sich auf eine Technologie festgelegt, so müssen natürlich auch die Nachteile der jeweiligen Technologie in Kauf genommen werden. Wählt der Entwickler für die erste Realisierung einer Schaltung eine Implementierung als FPGA (feldprogrammierbares Gate Array), so kann er sich aller Vorteile dieser Technologie bedienen. FPGA-Entwürfe sind leicht modifizierbar, ein Programmiergerät im Hause erlaubt Designän-

derungen in wenigen Stunden, die Schaltungsspezifikation für den Asic kann mit dem Gesamtsystem im Feldversuch dynamisch wachsen. Ist die Vorsierienphase beendet, stellt die Schaltung im FPGA die ideal auf die Anwendung optimierte Funktionalität dar. In der Serienproduktion eines Gerätes aber kommt nun der Nachteil der FPGAs zum Tragen: der relativ hohe Stückpreis. Hier wünscht man sich eine Lösung mit einem maskenprogrammierbaren Gate Array oder Standardzellen-IC. Die Entscheidung zu einer Umentwicklung der Schaltung auf dieser Basis wird aber nicht nur von der Lebensdauer des Endprodukts und den benötigten Stückzahlen bestimmt; die Umsetzung des FPGA-Entwurfes auf ein Gate Array erfordert die Verfügbarkeit eines CAE-Systems, das vom ausgewählten Asic-Lieferanten unterstützt wird. Ist eine Neueingabe des Schaltplans mit einer Gate Array-Bibliothek notwendig, so ist diese aufwendig und fehleranfällig. Synthesetools oder Netlistencompiler, die bereits von einigen Gate Array- oder Standardzellen-IC-Herstellern angeboten werden, können diese Phase vereinfachen, haben jedoch den Nachteil, dass der Schaltungsentwurf nur logisch kompatibel ist. Dynamische Eigenschaften müssen erneut verifiziert werden. Kommt es dabei zu Regelverstößen, z.B. durch nicht eingehaltene Timing-Konditionen an sequentiellen Elementen, muss der Entwurf geändert werden. Da ein Netlistencompiler zur Konvertierung der Datenbasis verwendet wurde, muss entweder der Schaltplan der FPGA-Realisierung (mit FPGA-Bibliotheks-elementen) solange geändert und kon-

| ASIC-Prototyping und Serienfertigung                                    | Typische Merkmale      |                        |                                   | Prototypen               |                          |                        | Serie             |                        |                        |                          |

|-------------------------------------------------------------------------|------------------------|------------------------|-----------------------------------|--------------------------|--------------------------|------------------------|-------------------|------------------------|------------------------|--------------------------|

|                                                                         | Integrations-Dichte    | Kopierschutz           | Werkzeug-Typ / Kosten             | typ. Durchlaufzeit       | Kosten sFr.              | Kosten für Änderungen  | Kosten pro Gatter | Kosten pro Chip        | Zuverlässigkeit        | Lieferanten-Abhängigkeit |

| PAL                                                                     | sehr gering            | sehr gering            | Progr.gerät / gering              | Minuten                  | < 10--                   | klein                  | mittel            | mittel                 | mittel                 | gering                   |

| EPLD<br>- löscharbar<br>- permanent                                     | gering<br>gering       | mittel<br>mittel       | Progr.gerät<br>/gering<br>/gering | Minuten<br>Minuten       | < 100--<br>< 100--       | klein<br>mittel        | mittel<br>mittel  | hoch<br>hoch           | mittel<br>hoch         | gering<br>gering         |

| FPGA<br>- löscharbar<br>- permanent                                     | mittel<br>mittel       | mittel<br>hoch         | Progr.gerät<br>/mittel<br>/mittel | Stunden<br>Stunden       | < 1000--<br>< 1000--     | klein<br>mittel        | hoch<br>hoch      | sehr hoch<br>sehr hoch | mittel<br>hoch         | gering<br>gering         |

| Gate Array<br>- maskenprogrammiert<br>- Direktschreibe-Verfahren        | hoch<br>hoch           | sehr hoch<br>sehr hoch | Masken/hoch<br>- / mittel         | < 2 Monate<br>< 1 Monate | > 10 000--<br>> 10 000-- | sehr hoch<br>sehr hoch | gering<br>gering  | gering<br>gering       | sehr hoch<br>sehr hoch | hoch<br>hoch             |

| Standardzellen-IC<br>- maskenprogrammiert<br>- Direktschreibe-Verfahren | sehr hoch<br>sehr hoch | sehr hoch<br>sehr hoch | Masken/hoch<br>- / mittel         | < 3 Monate<br>< 1 Monate | > 30 000--<br>> 10 000-- | sehr hoch<br>sehr hoch | gering<br>gering  | gering<br>gering       | sehr hoch<br>sehr hoch | hoch<br>hoch             |

| Full-Custom-IC                                                          | sehr hoch              | sehr hoch              | Masken/hoch                       | < 3 Monate               | > 40 000--               | sehr hoch              | sehr gering       | sehr gering            | sehr hoch              | hoch                     |

Tabelle II Asic-Vergleichsmatrix

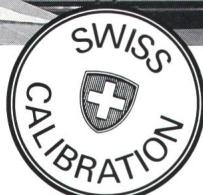

**Bild 1**

Schnittstellen der Asic-Entwicklung

vertiert oder die konvertierte Netzliste editiert werden, bis die Differenzen zwischen dem FPGA und dem konvertierten Gate Array oder Standardzellenentwurf beseitigt sind.

Wählt der Entwickler für die Realisierung gleich zu Beginn eine Implementierung als Gate Array oder Standardzellen-IC, um neben der Kostenoptimierung auch eine Qualitätssteigerung des Produktes zu erreichen, so fallen in jedem Fall die höheren Entwicklungskosten an. Diese werden aber von den geringeren Produktionskosten schnell aufgefangen – der Einsatz eines Gate Arrays oder Standardzellen-ICs kann sich schon bei Stückzahlen ab wenigen Hundert rentieren. Der Break-Even-Punkt verschiebt sich allerdings mit jedem Redesign um den erforderlichen Stückzahlbedarf.

## Mögliche Schnittstellen bei der Asic-Entwicklung

Ein wichtiges Kriterium für die Wahl eines bestimmten Asic-Entwicklungsverfahrens ist der vorgesehene Eigenentwicklungsanteil. Dieser bestimmt auch die Wahl der Designsoftware. Am häufigsten werden CAE-Systeme mit graphischem Schaltplan-Editor eingesetzt. Mit diesem werden vorstrukturierte Elemente (Hard- oder Softmakros, wie kombinatorische Gatter, Flip-Flops, Addierer, Register etc.) zur gewünschten Funktion verknüpft. Den prinzipiellen Entwicklungsablauf bei verschiedenen Schnittstellen zeigt das Bild 1.

### Schnittstelle Turnkey

Hier wird die gesamte Entwicklung an den Hersteller oder ein Designhaus

vergeben. Die Schnittstelle im Ablaufdiagramm ist die Konzeptionsphase und der Schaltungsentwurf. Der Kunde liefert eine System-Spezifikation, die das Verhalten des Bausteins exakt nach Funktion und Einsatzbedingungen wie z.B. Stromaufnahme, Pinning, Gehäuse usw. beschreibt. Obwohl auf den ersten Blick der Weg zum Asic durch diese Schnittstelle einfach erscheint, muss doch betont werden, dass die Planung sehr sorgfältig durchzuführen ist und dass der Aufwand in der Regel genausohoch wie bei einer Eigenentwicklung ist. Die Planung beginnt mit der Festlegung, welche Schaltungsteile in den Asic integriert werden sollen. Da diese System-Partitionierung die Güte und Kosten des Gesamtprodukts beeinflusst, muss dabei sehr sorgfältig vorgegangen werden. Sinnvoll ist eine Diskussion mit mehreren Asic-Lieferanten, um die optimale Lösung zu finden. Dieses Vorgehen kostet zwar Zeit (und damit Geld), ist aber für ein gutes Ergebnis ausschlaggebend. Auch zur elektrischen Spezifikation des Asics empfiehlt sich der Weg zu mehreren Herstellern, denn oft lassen sich Wunsch und Realisierbarkeit nicht vereinbaren. Wenn alle Voraussetzungen für das Asic-Design getroffen sind, folgt die eigentliche Schaltungseingabe, die beim Turnkey-Design vom Designhaus durchgeführt wird. Die Verifikation der Schaltung wird anschliessend mit Hilfe von Simulationen erreicht. Diese können vom Hersteller nur in engem Zusammenspiel mit dem Kunden durchgeführt werden, sollen doch alle Umgebungseinflüsse berücksichtigt werden. Ausserdem sollte der Kunde sein Asic

kennen, da die Verantwortung mit der Abnahme der Simulationsergebnisse (Post-Layout-Simulation) vom Designhaus oder Hersteller zu ihm übergeht.

### Schnittstelle Simulierte Netzliste

Wird die gesamte Schaltungsentwicklung vom Kunden mit einem Designkit eines Herstellers durchgeführt, so ist die Schnittstelle die «Simulierte Netzliste». Die Vorbereitungsphase von der Systempartitionierung bis zur Spezifikation gleicht der beim Turnkey-Design. Zusätzlich übernimmt der Kunde die Eingabe der Schaltung in ein CAE-System sowie die Aufgabe der Simulation (Verifikation). Damit werden natürlich eigene Entwicklungskapazitäten gebunden. Dem steht aber gegenüber, dass zum einen ein internes Know-how aufgebaut wird und zum anderen genaue Kenntnisse über den eigenen Asic erworben werden. Eine spätere Erweiterung auf mehr Funktionalität z.B. ist wesentlich einfacher, die Abhängigkeit von Lieferanten wird geringer. Der Weg zum ausgewählten Asic-Lieferanten ist erst dann notwendig, wenn die Schaltung vollständig simuliert wurde und als «Simulierte Netzliste» vorliegt. Jetzt wird der Halbleiterhersteller nach einer Eingangsqualifikation das Layout zu diesem Asic generieren. Die Aufteilung des Pin Out auf das gewählte Gehäuse wird in enger Absprache durchgeführt; die Verteilung von Stromversorgungsanschlüssen ist von der Anzahl gleichzeitig schaltender Ausgangstreiber und Leistungslasten auf der Platine abhängig. Wie beim Turnkey-Design geht die Verantwortung mit der Abnahme der

Simulationsergebnisse (Post-Layout-Simulation) vom Hersteller an den Kunden zurück. Auch hierfür sollte genügend Zeit einkalkuliert werden. Der Unterschied zum Turnkey-Design betrifft also im wesentlichen die Schaltplaneingabe sowie die Simulation bis zur Netzlistengenerierung.

## Schnittstelle Layout

Zusätzlich zu den Schritten der Schnittstelle «Simulierte Netzliste» wird vom Kunden das Chiplayout inklusive Post-Layout-Simulation durchgeführt. An den Silizium-Hersteller wird ein GDS II-Datenband übergeben, mit dem die Maskengenerierung für den Asic gesteuert wird. Der Vorteil dieser Schnittstelle liegt auf der Hand: die Post-Layout-Simulation erfordert den geringsten zusätzlichen Entwicklungsaufwand. Zudem kann man frühzeitig von der Simulation mit geschätzten auf die Simulation mit realen Leitungslaufzeiten wechseln. Da die Iterationsschleifen direkt im eigenen Hause stattfinden, gewinnt man einen Zeitvorteil gegenüber der Schnittstelle «Simulierte Netzliste». Allerdings, gute Layout-Software ist teuer und sie erfordert zusätzliches Know-how. Dieser Weg ist deshalb für die meisten Asic-Anwender nicht lohnend.

## Methodik der Asic-Entwicklung

Nach der Systempartitionierung, der Festlegung also, welche Schaltungsteile auf der Platine durch discrete Logik und welche in einem Asic realisiert werden sollen, kann prinzipiell parallel zum Board-Design mit der Asic-Entwicklung begonnen werden. Bei der Board-Entwicklung kann der Asic zunächst als Black-Box aufgefasst werden; seine Funktion ist durch die Spezifikation eindeutig beschrieben. Die Aufgabe des Asic-Designers besteht darin, diese Funktionen zu realisieren. Zur Asic-Entwicklung bieten sich zwei bekannte Methoden an: Bottom-up und Top-down. Bei der Bottom-up-Entwicklung wird der Aufbau der Schaltung, ausgehend vom kleinsten Element (z.B. logisches Gatter), über immer grössere Strukturen bis hin zum vollständigen Asic durchgeführt. Dadurch kommt man relativ schnell zu Einzelergebnissen, mit wachsender Komplexität geht aber der Überblick verloren. Hier bewährt sich ähnlich wie bei der System-Partitionierung der Top-down-Ent-

wurf. Zunächst wird der Asic in grobe Funktionsblöcke zerlegt. Steht eine Hardware-Beschreibungssprache zur Verfügung, so kann bereits in diesem Stadium eine Asic-Simulation durchgeführt werden, wenn auch nur grob. Die einzelnen Funktionsblöcke werden nun sukzessive in Unterfunktionsblöcke zerlegt. Auch hier lässt sich das Zusammenspiel der Funktionsblöcke simulieren. Letztendlich wird dann die Ebene erreicht, wo die Logik durch logische Gatter beschrieben wird. Hier werden zum ersten Mal die elektrischen Parameter der Asic-Bibliothek (Gatterlaufzeiten usw.) berücksichtigt. Ein nahezu reibungsloses Zusammenspiel aller bis dahin beschriebenen Funktionsblöcke ist dann zu erwarten, wenn die gesamte Schaltung synchron aufgebaut wurde. Bei Einsatz der Top-down-Methode kann der Übergang von der funktionalen Blockbeschreibung auf die Beschreibung durch Logik-Zellen mittels Synthese-Software durchgeführt werden. Das erspart viel Zeit und hat den zusätzlichen Vorteil der Fehlerfreiheit. Solche Software ist in der Regel nicht gerade billig und deshalb nur für Anwender interessant, die sehr viele Asics entwickeln.

## Anforderungen an CAE-Systeme

Nach der strategischen Entscheidung, Asics einzusetzen, steht man vor der Aufgabe, das richtige CAE-System einzuführen. Bewertungskriterien dafür ergeben sich aus der Asic-Entwicklungsmethodik. Die Konzeptphase nimmt bei einer Schaltungsentwicklung einen wesentlichen Teil der Gesamtentwicklungszeit in Anspruch. Hier helfen CAE-Systeme in den wenigsten Fällen. Ist aber erst einmal dieser Grundstein gelegt, so beträgt der Aufwand für die Schaltplaneingabe erfahrungsgemäss etwa 20% bis 30%, für die Designverifikation etwa 60% bis 70%. Der Aufwand zur Dokumentation mit ungefähr 10% wird meistens vernachlässigt. Die Unterstützung der Verifikationsphase ist also entscheidend. In erster Näherung gilt: Je komplexer eine Schaltung ist, desto effizienter ist die Verifikation durch die Top-down-Methode, je höher die Interaktion zwischen Schaltplan, Regelüberprüfungstools und Simulator, desto einfacher und sicherer ist die Verifikation.

Der Simulator muss, insbesondere wenn auch Submikron-Technologien

unterstützt werden sollen, in der Lage sein, Setup- und Hold-Zeit-Überprüfungen auch lastabhängig durchzuführen, denn gerade bei kleinen Strukturbreiten trägt die Verdrahtung auf dem Chip weit mehr an die Gesamtverzögerung bei als die reine Gatterlaufzeit. Das System sollte zudem so offen sein, dass Third Party-Software, zum Beispiel Tools zur Logik-Synthese oder zur automatischen Testpattern-Generierung (ATPG) ohne grossen Aufwand integriert werden können. Zukunftsorientierte Software unterstützt Standardschnittstellen wie z.B. EDIF oder VHDL und erhöht die Investitionssicherheit. Letztendlich ist auch die Verfügbarkeit der CAE-Software auf Standard-Hardware ein wichtiges Kriterium, kennt man doch die Probleme, die entstehen, wenn von einem Betriebssystem zum anderen gewechselt werden muss. Dies hat auch positiven Einfluss auf die Beschaffungskosten. Wenn nämlich zum Beispiel die gleiche CAE-Software auf PCs und Workstations verfügbar ist, kann mit der preiswerteren PC-Lösung begonnen werden. Ist man mit dem System zufrieden und steigen die Anforderungen an die Performance, so kann man direkt und ohne Neueingabe der Schaltungsdaten eine leistungsstärkere Workstation-Version benutzen. Ist die Bedieneroberfläche auf den beiden Systemen identisch, so ist beim Wechsel vom PC auf die Workstation kein neues CAE-Software-Training notwendig.

Ein weiteres Kriterium zur Beurteilung von CAE-Systemen ist die Bedienbarkeit. Hier gibt es bis auf wenige Standardforderungen keine allgemeingültigen Regeln; der Designstil der Entwickler ist zu verschieden. Es gibt kein System, das allen möglichen Anforderungen genügt, nicht zuletzt, weil diese sich teilweise sogar widersprechen. Hohe Flexibilität der Software bietet hier einen vernünftigen Mittelweg. Leichte Erlernbarkeit und Bedienbarkeit ist Grundvoraussetzung, denn man will ja kein Software-Guru werden, sondern einen Asic entwickeln. Bewährt haben sich dabei die graphischen Benutzeroberflächen, die den Anwender durch das Design führen. Zuviele Pop-up-Menüs, insbesondere die tief verschachtelten, können jedoch den Anwender während der Entwicklung behindern. Ist der Anwender mit dem System erst einmal vertraut, so sollten die wesentlichen Funktionen auch über Softkeys abgerufen werden können, um einen

schnellen Arbeitsablauf zu ermöglichen. Eine Entscheidung für ein System sollte auf genauer Kenntnis des Systems basieren. Ideal ist eine intensive, längerdauernde Prüfung (ca. 1 Woche) durch eigenes Arbeiten am System. Letztlich müssen auch die Kosten berücksichtigt werden: teure und komplizierte Systeme verlangen oft Systemexperten im Hause.

## Minimierung des Asic-Entwicklungsrisikos

Das Hauptproblem bei der Asic-Entwicklung stellt das Redesign-Risiko dar. Mit jedem Redesign verschiebt sich nicht nur der Break-Even-Punkt, sondern auch der Prototypen-Fertigungstermin. Muss zum Beispiel bei einem Gate Array oder Standardzellen-IC nach Abgabe der relevanten Daten beim Hersteller mit vier bis acht Wochen Fertigungsdauer gerechnet werden, so ist bei einem Redesign der Punkt schnell erreicht, wo die Geräteprototypen zu spät in die Testphase gelangen und die Markteinführung verzögert wird. Dieses Risiko wird durch den Einsatz von programmierbaren Logikbausteinen reduziert, da Designänderungen innerhalb weniger Stunden realisiert werden können. Ist durch Feldversuche die Schaltung abgesichert, kann dieser Baustein auf ein Gate Array oder Standardzellen-IC abgebildet werden, um so die Vorteile der geringen Bausteinkosten und

der elektrischen Parameter (z.B. geringerer Stromverbrauch) zu realisieren. Eine erneute Verifikation von Funktionalität und Dynamik ist zwar lästig, muss aber durchgeführt werden, um die Austauschbarkeit der Asics zu gewährleisten.

Voraussetzung dazu ist ein CAE-System, das eine technologie- und herstellerunabhängige Asic-Entwicklung unterstützt. Leider genügt es nicht, verschiedene Hersteller-Designkits auf demselben CAE-System zur Verfügung zu haben, denn die Software, die die Brücke zwischen den Herstellern bildet, ist nur netzlistenorientiert, und die Erstellung zweier verschiedener Schaltpläne für ein Design ist sicher prohibitiv. Wird als Ausgangspunkt für alle alternativen Technologien der gleiche Schaltplan (Datenbasis) gewählt, so bleibt die Kontrolle über die Realisierungsmöglichkeiten beim Entwickler, und die Abhängigkeit von Lieferanten wird geringer. Moderne Software-Tools der neuen Generation unterstützen diese Vorgehensweise und ermöglichen durch einen Migrationspfad von einer Technologie zu einer anderen die Entwicklung von funktional und dynamisch kompatiblen Asics.

## Investitionssicherheit bei der Software

Ist ein CAE-System gefunden, das auf Standard-Hardware (PC und

Workstation) gleichermassen verfügbar ist, ist der erste Schritt zu einer sicheren Investition getan. Natürlich soll auch die PC-Version zumindest Designs bis zu etwa 10000 Gattern erlauben und die oben genannte Forderung nach möglichst identischer Benutzeroberfläche erfüllen. Ist die Performance des PCs nicht mehr ausreichend – mit wachsender Erfahrung bei der Asic-Entwicklung wird auch die Komplexität der Designs steigen –, so kann ohne Bedenken die leistungsstärkere Workstation eingeführt werden. Es ist darauf zu achten, dass neue Software-Produkte, auch die von anderen Herstellern, leicht integriert werden können. Um die Austauschbarkeit von Einzelkomponenten zu erhöhen, sollten idealerweise prozedurale Schnittstellen vorhanden sein, die eine vollständige Auswertung der Designdatenbasis ermöglichen. Eine dritte und letzte Forderung nach Unterstützung der Standardschnittstellen, wie z. B. EDIF oder VHDL, wird heute von allen namhaften CAE-Anbietern erfüllt.

Es werden bereits heute CAE-Systeme zur technologie- und herstellerunabhängigen Asic-Entwicklung für einen Preis in der Größenordnung von 10 000 sFr. auf dem Markt angeboten. Durch die Vermeidung eines Redesigns amortisiert sich diese Investition schon beim ersten Asic-Design.

# Neue Technologien erfordern neue Ideen. R+M hat sie!

Neue innovative Ideen in die Realität umzusetzen ist seit je die Stärke von Reichle+De-Massari.

Kompetente Köpfe in Entwicklung und Konstruktion arbeiten dauernd daran, Ihnen ausgereifte Lösungen mit einzigartigen Vorteilen zu bieten.

Einzigartige Vorteile für Sie! Von der Kommunikationssteckdose bis zum Grossverteiler.

Stellen Sie uns auf die Probe.

Reichle+De-Massari AG

Binzstrasse 31

CH-8622 Wetzikon

Telefon 01/933 81 11

Telefax 01/930 49 41

**Reichle**

**De-Massari**

Elektro- und

Kommunikationstechnik

**ELMES-Messtechnik: Mit weniger Daten mehr wissen.**

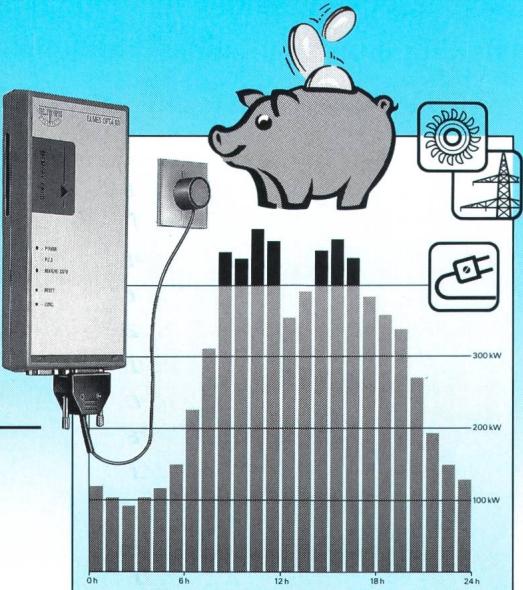

## Können Sie Ihre teuren Lastspitzen verschieben?

**ELMES OPTA** liefert beweiskräftige Fakten über Ihren Energieverbrauch und mit der Software OPTA GRAPH und OPTA TARIF erhalten Sie konkreten Aufschluss über Ihre Sparmöglichkeiten.

Rufen Sie an, wir dokumentieren Sie gerne.

**ELMES STAUB + Co AG**

Systeme für die Messtechnik

**8805 Richterswil**

Telefon 01-784 22 22

Fax 01-784 64 07

Schweizerischer Elektrotechnischer Verein

Association Suisse des Electriciens

Associazione Svizzera degli Elettrotecnic

Swiss Electrotechnical Association

## Die SEV-Prüfstelle Zürich

**kalibriert**

die Genauigkeit von elektrischen Messinstrumenten

(Kalibrierdienst)

**führt**

Abnahmen, Expertisen und Beratungen durch

**Unsere Fachspezialisten stehen zur Ihrer Verfügung. Rufen Sie uns an!**

Schweizerischer Elektrotechnischer Verein, Prüfstelle Zürich

Seefeldstrasse 301, Postfach, 8034 Zürich

Telefon 01/384 91 11 – Telex 817 431 sev ch – Telefax 01/ 55 14 26