|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 83 (1992)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 9                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Gallium-Arsenid und seine Nachbarn im Periodensystem : Einsatz von III-V-Halbleitern im Höchstfrequenzbereich                                                                                                             |

| <b>Autor:</b>       | Patrick, W. / Bergamaschi, C. / Meier, H. P.                                                                                                                                                                              |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-902818">https://doi.org/10.5169/seals-902818</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Gallium-Arsenid und seine Nachbarn im Periodensystem

## Einsatz von III–V-Halbleitern im Höchstfrequenzbereich

W. Patrick, C. Bergamaschi, H.P. Meier und W. Bächtold

**Die Übertragung von immer grösseren Informationsmengen setzt die Erschliessung von immer höheren Frequenzen voraus. Für den interessanten Bereich der mm-Wellen ( $f \gg 30 \text{ GHz}$ ) müssen aktive Bauelemente entwickelt werden. In diesem Artikel werden die Forschungsaktivitäten des Instituts für Feldtheorie und Höchstfrequenztechnik (IFH) der ETH Zürich, im Bereich der III–V-Halbleitertechnologie vorgestellt.**

**La transmission de débits de données sans cesse croissants demande inévitablement l'exploitation de fréquences de plus en plus hautes. Pour le domaine très intéressant des ondes millimétriques ( $f \gg 30 \text{ GHz}$ ) il faut développer des composants actifs. Dans cet article sont présentées les activités de recherche de l'institut de théorie du champ et de technique des très hautes fréquences (IFH) de l'EPF Zurich dans le domaine de la technologie des semi-conducteurs III–V.**

Die Silizium-Technologie dominiert den Weltmarkt für integrierte Schaltungen. Fortgeschrittene Produktionsprozesse ermöglichen die Herstellung von Chips mit mehreren Millionen Transistoren. Zum Beispiel ist der 64-Mbit-DRAM-Chip mit kleinsten Struktur-Dimensionen von nur 0,35  $\mu\text{m}$  eines der nächsten Ziele der Silizium-VLSI-Industrie. Selbst sehr schnelle Schaltungen können heute mit der Silizium-Technologie realisiert werden. So wurde vor kurzem, mittels eines 0,8- $\mu\text{m}$ -selbstjustierten Bipolar-Technologie-Prozesses, ein 30 Gbit/s Multiplexer- und Demultiplexer-Chip hergestellt [1].

Für Höchstfrequenz- und Optoelektronik-Anwendungen haben Bauelemente und Schaltungen auf III–V-Verbindungshalbleitern (erstes Element 3, zweites 5 Valenzelektronen), z.B. Gallium-Arsenid (GaAs) und Indium-Phosphid (InP), eine wichtige Nische im Halbleiter-Markt gefunden. Es wurden Transistoren mit Transitfrequenzen ( $f_T$ ) von 250 GHz [2] und maximalen Oszillations-Frequenzen ( $f_{\max}$ ) von 450 GHz [3] hergestellt, sowie bis zu einer Frequenz von 100 GHz [4] funktionsfähige MMIC-Schaltungen (Monolithic Microwave Integrated Circuits) integriert. Des Weiteren ermöglichen Verbindungs- halbleiter die gleichzeitige Integration optischer wie auch elektronischer Bauelemente auf einem Chip. Ein voll integrierter optischer Empfänger (Wellenlänge 1,3  $\mu\text{m}$ ), bestehend aus einem Wellenleiter, einer Fotodiode und einer Verstärker-Schaltung, wurde kürzlich publiziert [5].

### Aufbau schneller Transistoren

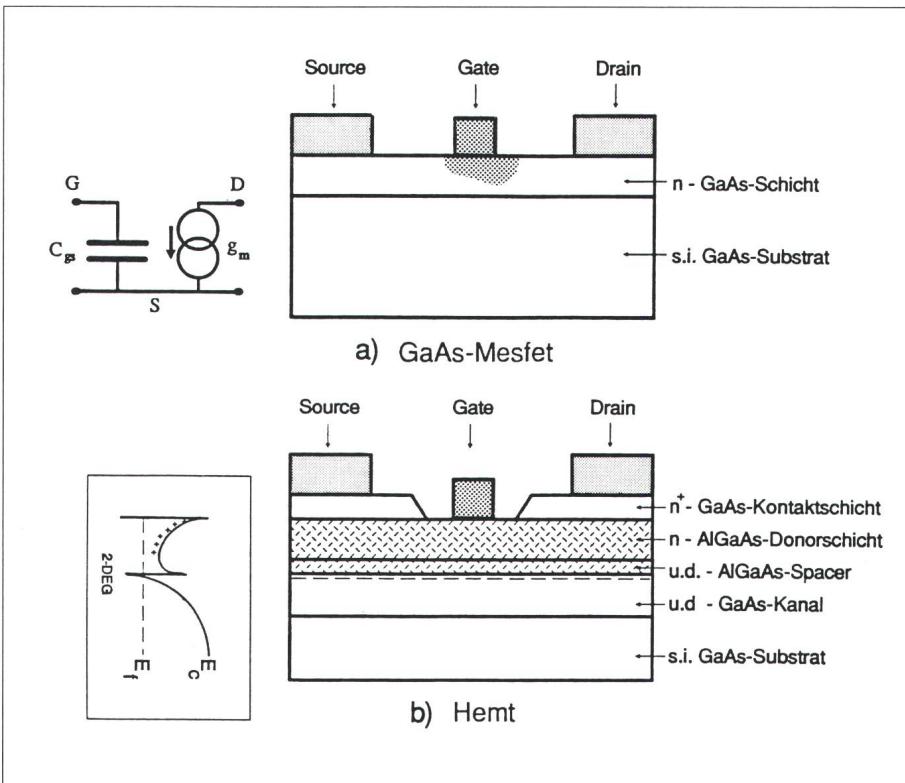

Die im folgenden beschriebenen Transistoren haben alle die Struktur eines Mesfet (Metal-Semiconductor

FET) oder sind daraus abgeleitet. Ein Mesfet (Bild 1a) besteht aus einem leitenden Kanal (n-dotiertes GaAs), der zwischen zwei ohmschen Kontakten Source und Drain liegt. Der Gate-Kontakt, eine in Sperrrichtung polarisierte Schottky-Diode, befindet sich zwischen Source und Drain. Wird am Gate eine negative Spannung angelegt, so ändert sich die Leitfähigkeit des Kanals, da die Schicht unter dem Gate an Ladungsträgern verarmt. Bei genügend hoher negativer Gate-Spannung werden die Ladungsträger unter dem Gate vollständig ausgeräumt, und es kann kein Strom mehr zwischen Source und Drain fließen (Pinch-Off).

In erster Näherung kann man einen Mesfet kleinsignalmäßig als spannungsgesteuerte Stromquelle mit Eingangskapazität  $C_{gs}$  modellieren (Fig. 1a). Die Transitfrequenz  $f_T$  (Frequenz, bei der die Stromverstärkung = 1 ist) wird somit zu [6]

$$f_T = g_m / 2\pi C_{gs} = V_{sat} / 2\pi L_g \quad (1)$$

mit der Transistorsteilheit  $g_m$ , der Gate-Source-Kapazität  $C_{gs}$ , der Sättigungs-Driftgeschwindigkeit  $V_{sat}$ , der Gatelänge  $L_g$ .

Will man die Transitfrequenz des Transistors erhöhen, so muss man entweder die Gatelänge reduzieren oder die Sättigungsgeschwindigkeit der Elektronen erhöhen. Die Gatelänge lässt sich nur bis zu einer Grösse von ca. 0,1  $\mu\text{m}$  reduzieren. Darunter treten sogenannte Kurzkanaleffekte auf, welche die Hochfrequenzeigenschaften wiederum verschlechtern. Die Sättigungsgeschwindigkeit ihrerseits hängt u.a. vom Material (GaAs, InGaAs etc.) und von der Höhe der Dotierung ab. (Je höher dotiert wird, um so mehr Störstellen befinden sich im Halbleiter und desto kleiner wird die

#### Adresse des Autors

Dr. William Patrick, Crispino Bergamaschi, Hans-Peter Meier und Prof. Dr. Werner Bächtold, Institut für Feldtheorie und Höchstfrequenztechnik, ETH Zürich, Gloriastrasse 35, 8092 Zürich.

**Bild 1a** Vereinfachtes Kleinsignalersatzschaltbild und schematische Schichtfolge eines GaAs-Mesfet

**b** Schematische Schichtfolge eines HEMT mit zugehörigem Leitungsbandverlauf

Driftgeschwindigkeit der Ladungsträger). Durch entsprechende Wahl des Kanalmaterials lassen sich somit recht hohe Geschwindigkeiten erreichen, welche jedoch bei konventionellen Mesfets durch die für die Verstärkung notwendige Dotierung des Kanals reduziert wird.

Dieses Dilemma war der Grund für die Entwicklung eines neuartigen Mesfets, des sogenannten HEMT [7] (High Electron Mobility Transistor). In Bild 1b ist eine mögliche HEMT-Schichtabfolge dargestellt. Diese Schichtstruktur verursacht eine spezielle Bänderkrümmung (Bild 1b), welche bewirkt, dass Elektronen aus der sogenannten Donatorschicht an die Oberfläche des undotierten Kanals «gesogen» werden. (Diese Oberflächenladung im Kanal wird auch zweidimensionales Elektronengas 2-DEG genannt.) Da der Kanal dadurch freie Ladungsträger besitzt, ohne dotiert zu sein, wird nicht nur die Reduktion der Sättigungsgeschwindigkeit durch Dotierungsstörstellen eliminiert, sondern zusätzlich auch das Rauschen des Kanals reduziert. Mit diesem Prinzip können Transistoren mit Transitfrequenzen bis 250 GHz und Rauschzahlen von 1,2 dB bei 94 GHz hergestellt werden.

## Herstellung aktiver Bauelemente

Die Herstellung von FET-Bauelementen und -Schaltungen benötigt zwei Haupttechnologien: Wachstum der aktiven Schichten (vertikale Struktur) und Definition der lateralen Struktur (Lithographie und Dünnschichttechnologie).

Die vertikale Struktur aller HEMTs und vieler Mesfets wird mittels Epitaxie hergestellt. Die zwei wichtigsten Wachstums-Methoden sind MBE [8] (Molecular Beam Epitaxy) und MOCVD [9] (Metal-Organic Chemical Vapour Deposition). Bei MBE werden unter sehr hohem Vakuum Molekularstrahlen von geheizten Elementarquellen (Effusionszellen) auf ein geheiztes Substrat gerichtet. Eine Schicht mit der erwünschten Zusammensetzung und Dotierung wird mit der Öffnung der entsprechenden Effusionszellen aufgewachsen. Für die Abscheidung einer Si-dotierten GaAs-Schicht werden zum Beispiel drei Zellen, nämlich Si, Ga und As benötigt. Die Zusammensetzung der Schichten wird durch die Temperatur der Effusionszellen bestimmt. Schichten, welche mit MBE aufgewachsen wurden, sind in Zusammensetzung, Dotierung

und Dicke sehr präzise und deshalb gut geeignet für die Herstellung von hochwertigen HEMTs.

Bei MOCVD werden die benötigten Elemente als gasförmige Verbindungen über das beheizte Substrat geleitet, wo sie sich durch chemische Reaktionen abscheiden. Typische Gase für GaAs-Wachstum sind Trimethyl-Gallium und -Arsen. MOCVD ist die bevorzugte Methode für das Abscheiden von Schichten mit Phosphorverbindungen (z.B. InP), da der Gebrauch von reinem Phosphor in unmodifizierten MBE-Systemen gefährlich sein kann.

Eine neue Wachstumsmethode, die sogenannte Gas-Source-MBE (GSMBE), ein Hybrid-Verfahren von MBE und MOCVD, wird immer mehr für die Herstellung von InP-HEMT-Strukturen verwendet. Am Institut für Feldtheorie und Höchstfrequenztechnik der ETH Zürich (IFH) konzentrieren sich die Aktivitäten auf die Definition der lateralen Strukturen der Bauelemente. Das epitaktische Material wird entweder von anderen Forschungslabors oder von kommerziellen Herstellern bezogen.

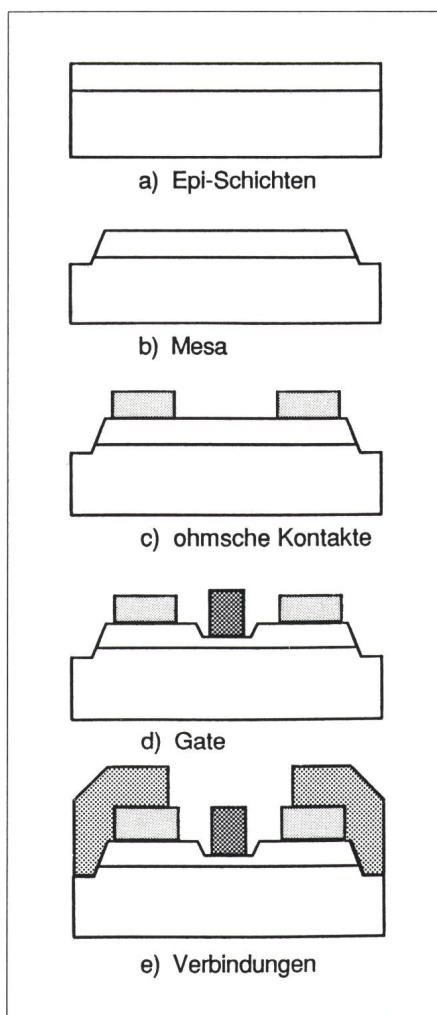

Obwohl sich Mesfets und HEMTs (auf GaAs- und InP-Basis) in der vertikalen Struktur sehr unterscheiden, werden für die Herstellung beider Bauelemente ähnliche Prozesstechnologien verwendet. Der Grundprozess für die Herstellung von FETs (Mesfets oder HEMTs) ist in Bild 2 schematisch dargestellt. Der erste Prozessschritt ist die Isolation der Bauelemente, welche durch das Wegätzen der aktiven Epitaxieschichten zwischen den FETs realisiert werden kann (Bild 2b). Diese Inseln aktiven Materials werden Mesas genannt. Als nächstes werden die ohmschen Kontakte von Source und Drain definiert. Diese bestehen typischerweise aus einer AuGe-Eutektikumsschicht und einer oder mehreren Ni- und Au-Schicht. Um niederohmige Kontakte zu realisieren, wird das ohmsche Metall bei Temperaturen zwischen 360 und 400°C legiert. Dazu wurde ein speziell angefertigter Legierofen, bestehend aus einer Heizplatte und einem einfachen Transfermechanismus für die Wafer konstruiert. Mit diesem Ofen können je nach Substratmaterial niederohmige Kontakte mit Widerständen von unter 0,1  $\mu\text{m}$  hergestellt werden.

Der wichtigste Prozessschritt ist die Definition der Gates. Wie in Bild 1b abgebildet, liegt das Gate nicht immer

auf der Oberfläche des Halbleiters, sondern oft vertieft in einem geätzten Graben, dem sogenannten Gate-Recess. Die Tiefe des Gate-Recesses beeinflusst direkt die Schwellspannung (Pinch-Off) des Bauelementes. Das Recessätzen ist deshalb der heikelste Schritt des ganzen Prozesses. Als Kontrolle der Tiefe des Recessätzens wird die einfache, aber effektive Technik der direkten Strommessung während des Ätzprozesses verwendet [10]. In Zukunft wird eine Trockenätzanlage, welche präziseres Ätzen ermöglicht, das eben erwähnte nass-chemische Verfahren ersetzen. Im letzten Prozessschritt werden die Kontaktanschlussflächen (Bondpads) definiert und die Bauelemente mit ein oder zwei Wiring-Levels untereinander verbunden (Bild 2d).

## Lithographie

Fotolithographie und Elektronenstrahl-Lithographie sind die wichtigsten Werkzeuge des Herstellprozes-

Bild 2 Prozessfolge der FET-Bauelemente-Herstellung

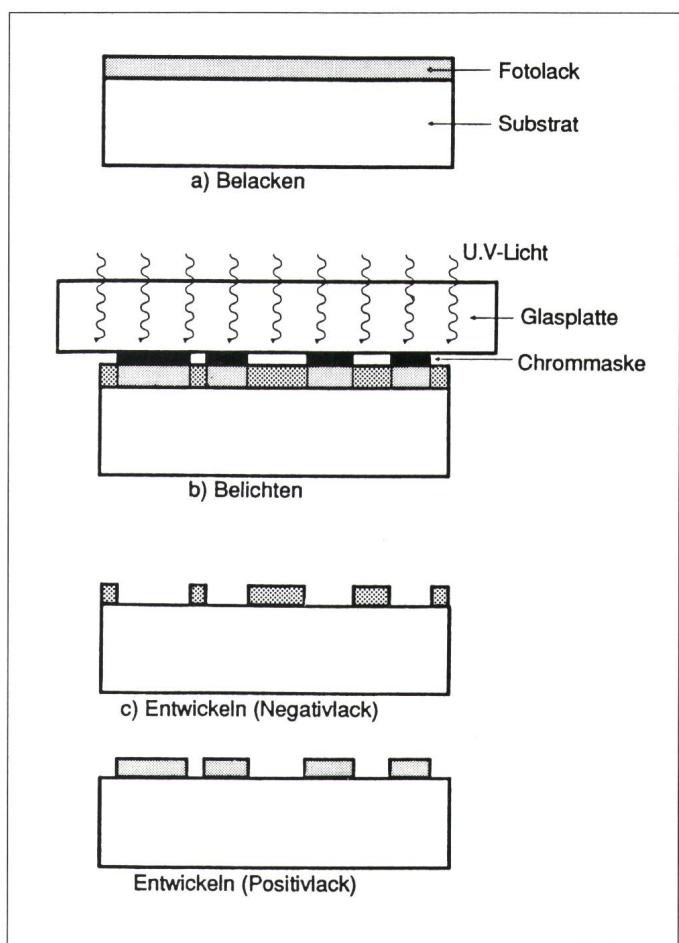

**Bild 3**

Prozessfolge des Fotolithographie-Prozesses

ses. Das Bild 3 zeigt schematisch den Fotolithographieprozess. Zuerst wird ein lichtempfindlicher Lack (Fotolack) auf das Substrat aufgebracht (Bild 3a). Um das Lösungsmittel im Lack zu entfernen, wird das Substrat in einem Ofen oder auf einer Heizplatte ausgeheizt. Eine Glas- oder Quarzplatte mit einer undurchsichtigen Chromschablone dient als Fotomaske zur Strukturierung des Lackes. Diese Maske wird in direkten Kontakt mit dem Fotolack gebracht (Bild 3b). Durch Belichtung mit UV-Licht (Wellenlänge 300–400 nm) wird der Fotolack chemisch so verändert, dass entweder die belichteten Flächen (Positivlack) oder die nicht belichteten Flächen (Negativlack) mit einem geeigneten Entwickler entfernt werden können. Die so entstandene Lackstruktur dient als Ätzmaske, oder sie wird zur Definition der Metallstrukturen in der Lift-Off-Technik (siehe unten) gebraucht.

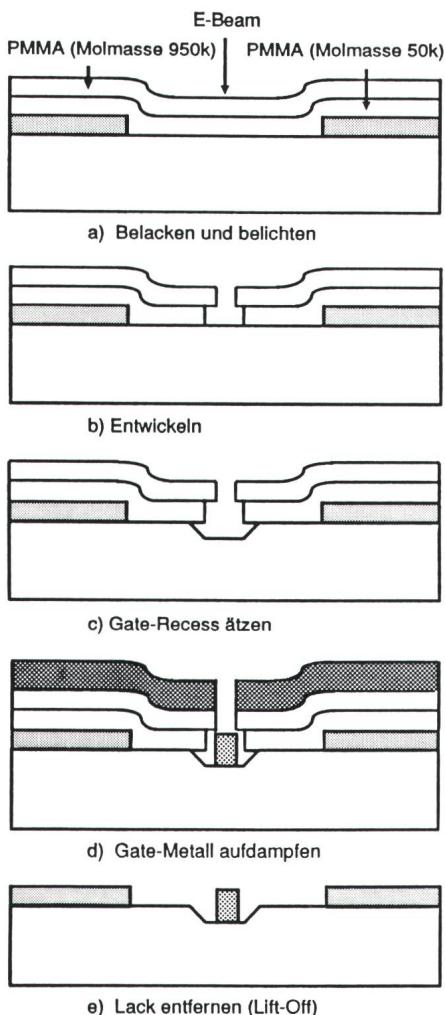

Zur Definition von sehr kleinen Strukturen wird immer öfters die Elektronenstrahl-Lithographie (EBL) eingesetzt. Ein feinfokussierter Elektronenstrahl wird für die Belichtung

des elektronenempfindlichen Lackes verwendet (Bild 4). Während die Auflösung der Fotolithographie durch die Wellenlänge der Belichtungsquelle begrenzt wird, ist die Auflösung der EBL von der Elektronenstrahl-Fokussierung, der Strahlablenkung und vom Lack selbst abhängig. Mit der EBL können 0,1- $\mu\text{m}$ -Strukturen vergleichsweise einfach definiert werden, während mit der Fotolithographie Submikrometer-Strukturen nur schwer zu realisieren sind.

Wie bereits oben erwähnt wurde, sind kleine Gatelängen wichtig, wenn man kurze FET-Schaltzeiten erreichen will. Die bisher schnellsten Bauelemente weisen Gatelängen unter 0,25  $\mu\text{m}$  auf [2;3]. Solch kleine Strukturen können nur mit Elektronenstrahl-Lithographie oder einer ähnlich hochauflösenden Technik, wie z.B. der Röntgenstrahl-Lithographie, definiert werden. Leider sind die Beschaffungs- sowie die Installations- und Betriebskosten kommerzieller EBL-Anlagen enorm hoch; sie sind für Forschungslabors an Universitäten kaum erschwinglich. Glücklicherweise besteht die Möglichkeit, ein Raster-

**Bild 4** Prozessfolge der Herstellung des Gates

elektronen-Mikroskop (REM) in ein Elektronenstrahl-Lithographiesystem umzubauen. Dazu wird eine geeignete Steuerelektronik (Pattern Generator), ein elektrostatischer Beam-Blanker sowie eine Steuerung zur Bewegung des Probentisches benötigt. Derartige Systeme sind heute kommerziell erhältlich. So wurde am IFH zur Entwicklung der III-V-Halbleitertechnologie das Elphy (Electron-Beam Lithography) der Firma Raith GmbH installiert.

Anfänglich wurden alle Strukturen mit der Elektronenstrahl-Lithographie geschrieben. Dieses Verfahren ist jedoch sehr zeitintensiv, da EBL ein sequentieller Prozess ist. Es wurde deshalb eine sogenannte Mix and Match-Technik entwickelt. Hierbei werden nur die schmalen Gatestrukturen mit der EBL definiert, alle anderen Strukturen, wie zum Beispiel die ohmschen Kontakte, mit der optischen Lithographie. Die zur optischen

Lithographie benötigten Maskensätze wurden anfänglich außer Haus hergestellt. Neuerdings können einfache Maskensätze mit dem Elphy-System auch in unserem Institut produziert werden.

Der am IFH entwickelte Prozess zur Herstellung von FETs mit Gatelängen von  $0,2 \mu\text{m}$  unterscheidet sich von einem industriellen Prozess nur in der Grösse des verarbeiteten Substrates. Während in der Industrie serienmäßig Wafer mit 2 bis 4 Zoll Durchmesser verwendet werden, beschränken wir uns auf 2 bis 3 Chips von  $7 \times 7 \text{ mm}$ . Hauptgrund für die Verwendung kleinerer Chips ist neben den Kosten die kürzere EBL-Schreibzeit. Im Gegensatz zu käuflich erhältlichen EBL-Systemen müssen nämlich beim Elphy-System die einzelnen Belichtungsfelder manuell justiert werden. In der Praxis hat sich eine Anzahl von 25 bis 36 Belichtungsfeldern als zeitlich noch tragbar erwiesen. Ein grosser Vorteil des IFH-Prozesses liegt in seiner Flexibilität. So können praktisch jederzeit Änderungen oder Korrekturen an den Layoutdaten vorgenommen werden. Neue Entwürfe können nach Wunsch generiert und innerhalb einer Woche als fertige Schaltungen realisiert werden.

Der Ablauf des  $0,2\text{-}\mu\text{m}$ -Standard-Prozesses wurde anhand von Bild 2 dargestellt. Der prozesskritische Schritt der Gate-Herstellung soll nun im Detail beschrieben werden. Auf dem Chip werden zwei Lagen PMMA (Polymethylmethacrylat) aufgebracht, welche sich in der Molmasse (950000 und 50000) unterscheiden (Bild 4a). Die beiden Schichten weisen bezüglich der Strahldosis unterschiedliche Empfindlichkeiten auf. Die untere Lackschicht (Molmasse 50000) zeigt im Entwickler eine höhere Löslichkeit als die obere Schicht (Molmasse 950000). Dadurch entsteht ein Lackprofil, wie es in Bild 4b dargestellt ist. Diese Lackstruktur dient als Ätzmaske bei der Herstellung des Gate-Recesses (Bild 4c). Im nächsten Schritt wird das Gate-Metall (Ti/Au) aufgedampft. Dabei ist die Gatestruktur genau in der Mitte des Gate-Recesses definiert, da die gleiche Lackstruktur für beide Prozessschritte verwendet wird (Bild 4d). Der Lack wird nun mitsamt der daraufliegenden Metallschicht mittels eines Lösungsmittels vom Substrat entfernt. Diese Methode zur Definition von Metallstrukturen wird als Lift-off bezeichnet und wird in der III-V-Halbleitertechnolo-

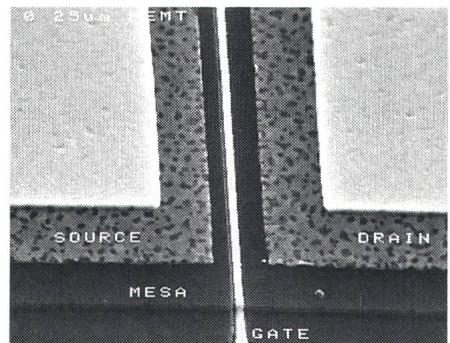

**Bild 5** REM-Bild eines HEMT mit Gatelänge von  $0,2 \mu\text{m}$

gie fast ausschliesslich verwendet. Das Bild 5 zeigt einen am IFH hergestellten HEMT. Die Gatelänge beträgt  $0,25 \mu\text{m}$  und ist somit etwas grösser als die entworfene Gatelänge von  $0,2 \mu\text{m}$ . Diese Abweichung kann mit dem «Proximity Effect» bei der Belichtung mit dem Elektronenstrahl erklärt werden.

## Hergestellte Bauelemente

Das erste Bauelement, welches am IFH selber produziert wurde, war ein einfacher GaAs-Mesfet mit ionenimplantiertem Kanal. Obwohl das implantierte Material nur als Testmaterial zur Optimierung des ohmschen und Schottky-Kontaktes gedacht war, wurden annehmbare FET-Eigenschaften erzielt. Das Bild 6 zeigt die  $I_{ds}$ - $U_{ds}$ -Kennlinie eines typischen Mesfets mit  $0,2 \mu\text{m}$  Gate-Länge und  $50 \mu\text{m}$  Gate-Breite. Ein wichtiger FET-Parameter ist die Steilheit  $g_m$ . Bei diesen FETs wurden maximale  $g_m$ -Werte von über  $350 \text{ mS/mm}$  erreicht.

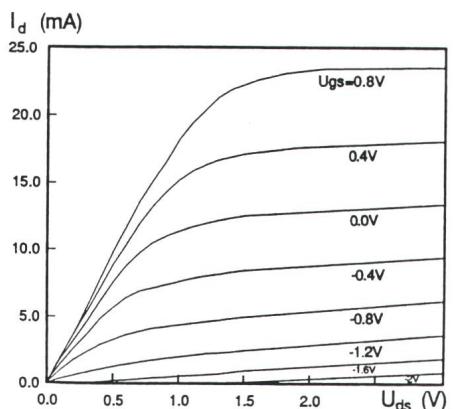

Beim nächsten GaAs Mesfet wurden MBE-gewachsene aktive Schichten verwendet. Eine hochdotierte

**Bild 6**  $I_{ds}$ - $U_{ds}$ -Kennlinien eines implantierten GaAs-Mesfet mit Gatelänge von  $0,2 \mu\text{m}$

Kontaktschicht, welche auf der Kanalschicht abgeschieden wurde, soll die Herstellung der ohmschen Kontakte erleichtern. Um Kurzkanaleffekte (die Injektion von hochenergetischen Elektronen in das Substrat) zu reduzieren, wurde eine leicht dotierte p-GaAs-Schicht zwischen dem Kanal und dem Substrat gewachsen. Die verbesserten Eigenschaften des Epi-Mesfet lassen sich aus der  $g_m$ - $U_{gs}$ -Kurve in Bild 7 ersehen. Der maximale  $g_m$ -Wert ist 590 mS/mm. Ein ohmscher Kontaktwiderstand von 0,13  $\Omega$  mm (vgl. mit 0,25  $\Omega$  mm auf dem implantierten Material) wurde gemessen. Die hohen  $g_m$ -Werte und die niedrigen Kontaktwiderstände sind auf die

Bild 7  $g_m$ - $U_{gs}$ -Kennlinien eines GaAs-Mesfet mit Epitaxie-Kanalschichten

bessere Qualität der Epi-Schichten gegenüber dem implantierten Material zurückzuführen.

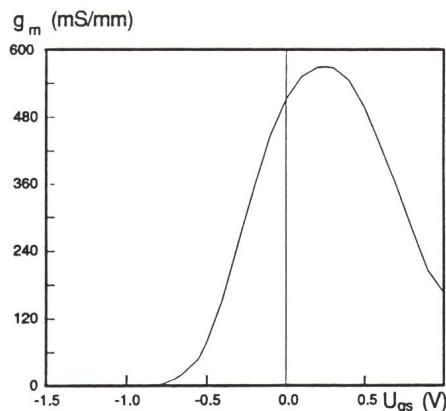

Das erste selbstproduzierte HEMT-Bauelement hatte folgenden Aufbau (von oben): eine  $n^+$ -GaAs-Kontaktschicht, eine  $n^-$ -AlGaAs-Donorschicht, ein undotierter AlGaAs-Spacer, ein undotierter GaInAs-Pseudomorf-Kanal und ein undotierter GaAs-Buffer auf einem semi-isolierenden GaAs-Substrat. Der AlGaAs-Spacer dient als zusätzliche Abstandsschicht, damit die Träger im 2-DEG örtlich von den ionisierten Donoratomen der  $n^-$ -AlGaAs-Schicht getrennt werden. Die Trennung der Elektronen und Donoratome führt zu höherer Elektronenbeweglichkeit. Das Bild 8 zeigt die  $I_d$ - $U_{ds}$  und  $g_m$ - $U_{gs}$ -Kennlinien des HEMT. Der relativ hohe Ausgangsleitwert  $g_{ds}$ , verglichen mit dem Mesfet in Bild 6, wird durch die Injektion von energiereichen Elektronen aus dem 2-DEG zur GaAs-Pufferschicht verursacht. Die Elektroneninjektion könnte durch den Einbau ei-

nes zweiten Heteroüberganges unter dem Kanal verhindert werden. Diese Option wird in künftigen HEMT-Entwürfen berücksichtigt, um den Ausgangsleitwert zu verkleinern. Die  $g_m$ - $U_{gs}$ -Kurve von Bild 8 zeigt einen sehr steilen Anstieg des  $g_m$ -Wertes mit zunehmendem  $U_{gs}$ . Diese Steigung wird als K-Wert [11] bezeichnet und ist ein wichtiger Parameter für Logik-Schaltungen. Der HEMT in Bild 8 zeigt einen sehr hohen K-Wert von 580 mS/Vmm.

Kürzlich wurden auch HEMTs auf InP-Basis hergestellt. Die Schichtfolge ist: eine hochdotierte GaInAs-Kontakt-Schicht, eine undotierte Al-InAs-Schottky-Schicht, eine dotierte AlInAs-Donorschicht, ein undotierter AlInAs-Spacer, ein undotierter GaInAs-Kanal, und eine undotierte Al-InAs-Pufferschicht auf einem InP-Substrat. Von allen bisher untersuchten Materialen wurde auf InP-HEMT-Material die höchste Elektronenbeweglichkeit gemessen: 8500 cm<sup>2</sup>/Vs bei Zimmertemperatur und 22000 cm<sup>2</sup>/Vs bei 77 K. Die InP-HEMTs hatten ähnliche elektrische Eigenschaften wie die Pseudomorf-HEMTs. S-Parameter-Messungen ergaben  $f_T$ - und  $f_{max}$ -Werte von 60 GHz und 100 GHz. Diese Werte sind im Vergleich mit den Rekordwerten [2;3] (250 und 450 GHz) ziemlich bescheiden, wobei zu berücksichtigen ist, dass bisher die Technologie in erster Linie bezüglich der Gleichstrom-Eigenschaften optimiert wurde.

## Diskussion

Die vorangehenden Abschnitte zeigen, wie mit relativ einfacher Technologie die Herstellung von FETs auf III-V-Halbleitern möglich ist. Wie schon erwähnt, wurde der Prozess bisher hauptsächlich für die Gleichstrom-Eigenschaften optimiert. Für Hochfrequenz-Anwendungen sind weitere Prozess-Entwicklungen nötig. Ein Nachteil des jetzigen 0,2- $\mu$ m-Prozesses ist der sehr hohe Gatewiderstand. Da es schwierig ist, mit dem Zweilagen-PMMA-Lacksystem ein Dickenzu-Längen-Verhältnis von grösser als 1 zu realisieren, hat das Gate einen Gleichstromwiderstand von über 600  $\Omega$ /mm. Dieser Wert ist für Mikrowellenanwendungen mindestens zwei Grössenordnungen zu hoch. Der Gatewiderstand könnte durch die Verwendung eines Gates mit T-förmigem Querschnitt deutlich reduziert werden. Eines der nächsten Ziele dieses

Bild 8 Pseudomorf-HEMT mit Gatellänge von 0,2  $\mu$ m

- a  $I_d$ - $U_{ds}$ -Kennlinie

b  $g_m$ - $U_{gs}$ -Kennlinien

Projektes ist deshalb die Herstellung einer T-Gate-Struktur, welche mit einem Mehrlagen-Lackprozess [12] realisiert werden kann. Als weitere Prozessverbesserung ist die Ablösung des nasschemischen Ätzschrittes durch Trockenätzten, zum Beispiel Reaktiv-Ionenätzten (RIE) geplant. Die Verwendung von RIE würde ein gleichmässiges und kontrollierbares Ätzen beim Gate-Recess, dem wichtigsten Prozessschritt, erlauben. Die Ätztiefe könnte zudem durch eine zusätzliche Ätzstopp-Schicht (z.B. AlGaAs oder AlInAs) genau kontrolliert werden. Die Variation der Pinch-Off-Spannung könnte dadurch stark reduziert werden, was ein grosser Vorteil für den Entwurf von integrierter Schaltung ist.

## Zusammenfassung

Es wurde ein Überblick über die einzelnen Prozessschritte zur Herstellung von Mesfet- und HEMT-Bauelementen gegeben. Die Gleichstrom-Eigenschaften unserer Bauelemente lassen sich gut mit äquivalenten Bauelementen aus der Literatur vergleichen.

Obwohl die Hochfrequenzeigenschaften der Bauelemente noch nicht optimiert sind, darf der bereits erreichte  $f_{\max}$ -Wert von 100 GHz als positives Zeichen für künftige Entwicklungen gewertet werden. Ziel dieses Projektes ist nicht, Transistoren mit Rekordwerten herzustellen, sondern möglichst hochwertige Bauelemente zu produzieren, welche in integrierten Schaltungen (z.B. Breitbandverstärker für den Frequenzbereich von 40–60 GHz, optoelektronische Empfänger mit integrierten Fotodioden und Transimpedanzverstärker, sehr schnelle Digitalschaltungen) verwendet werden können.

## Verdankung

Dieses Projekt wird von der PTT (F+E-Projekt Nr. 235) und Lesit (Modul 6) unterstützt. Epi-Material

wurde von P. Vettiger (IBM Forschungslabor, Zürich) und F. Gueissaz (EPFL) freundlicherweise zur Verfügung gestellt. Die implantierten Wafer wurden von A. Hülsmann (Fraunhofer Institut, BRD) hergestellt.

## Literatur

- [1] *H.M. Rein, J. Hauenschild, M. Möller, W. McFarland, D. Pettengill and J. Doernberg*: 30 Gbit/s multiplexer and demultiplexer ICs in silicon bipolar technology. *Electron. Lett.* 28(1992)1, pp. 97–99.

- [2] *U.K. Mishra, A.S. Brown, L.M. Jelloian, M. Thompson, S.E. Rosenbaum and L. Nguyen*: Novel high performance self-aligned 0.15  $\mu\text{m}$  long T-gate AlInAs-GaInAs HEMTs. *IEEE IEDM Proceedings* 1989, pp. 101–104.

- [3] *P.M. Smith, P.C. Chao, P. Ho, K.H. Duh, M.Y. Kao, J.M. Ballingall, S.T. Allen and A. Tessner*: Microwave InAlAs/InGaAs/InP HEMTs: status and applications. *Proceedings of 2nd Int. Conference on Indium Phosphide and related materials* 1990, pp. 39–43.

- [4] *R. Majidi-Ahy et al.*: 5–100 GHz InP coplanar Waveguide MMIC distributed amplifier. *IEEE Trans. MTT*. 38(1990)12, pp. 1986–1993.

- [5] *W.P. Hong, G.K. Chang, R. Bhat, C. Nguyen, M. Koza*: Monolithically integrated Waveguide – MSM detector – HEMT amplifier receiver for long-wavelength lightwave systems. *IEEE Photonics Technol. Lett.* 3(1991)2, pp. 156–158.

- [6] *S.M. Sze*: *Physics of Semiconductor Device*. John Wiley and Sons, New York, 1981, p. 343.

- [7] *F. Ali and A. Gupta, editors*: *HEMTs and HBTs: devices, fabrication and circuits*. Artech House, London, 1991.

- [8] *E.H.C. Parker, ed.*: *The technology and physics of molecular beam epitaxy*. Plenum Press, New York, 1985.

- [9] *D.K. Ferry, ed.*: *Gallium arsenide technology*. H.W. Sams, Indianapolis, 1985, pp. 79–105.

- [10] *W. Patrick, K. Däwyler, B.J. Van Zeghbroeck and P. Vettiger*: Technology for submicron recessed-gate GaAs Mesfets on thin MBE layers using electron beam lithography. *Proceedings 14th Int. Symposium on gallium arsenide and related compounds*, Inst. Phys. Conf. Ser. No. 91 (1987), pp. 637–640.

- [11] *B.J. Van Zeghbroeck, W. Patrick, H. Meier and P. Vettiger*: Submicron GaAs Mesfet with shallow channel and very high transconductance. *IEEE Electron Dev. Lett.*, EDL-8 (1987)3, pp. 118–120.

- [12] *P.C. Chao, P.M. Smith, S.C. Palmateer and J.C.M. Hwang*: Electron-beam fabrication of GaAs low-noise Mesfets using a new trilayer resist technique. *IEEE Trans. Electron. Devices*, ED-32(1985)6, pp. 1042–1046.