|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 83 (1992)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 5                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Implémentation d'un réseau de Kohonen avec facultés d'apprentissage                                                                                                                                                       |

| <b>Autor:</b>       | Peiris, Vincent / Hochet, Bertrand / Creasy, Tim                                                                                                                                                                          |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-902804">https://doi.org/10.5169/seals-902804</a>                                                                                                                                   |

### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 12.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Implémentation d'un réseau de Kohonen avec facultés d'apprentissage

Vincent Peiris, Bertrand Hochet, Tim Creasy, Michel Declercq

**Cet article décrit l'implémentation VLSI d'un réseau de Kohonen à comportement numérique. Ce réseau est pourvu de facultés d'apprentissage et utilise des techniques mixtes analogiques et numériques. Les poids synaptiques sont stockés sous forme analogique, et les signaux d'entrée sont numériques. Les neurones calculent soit le produit scalaire euclidien soit la distance de Manhattan entre le vecteur d'entrée et leur propre vecteur synaptique. Le voisinage d'apprentissage est généré par un réseau résistif non-linéaire.**

**Der Beitrag beschreibt die VLSI-Implementation eines Kohonen-Netzwerkes mit digitalem Verhalten. Das mit Lerneigenschaften versehene Netzwerk basiert auf gemischt analog-digitaler Technik. Die synaptischen Gewichte werden analog gespeichert, die Eingangssignale sind digital. Die Neuronen berechnen sowohl das euklidische Skalarprodukt als auch die Manhattan-Distanz zwischen dem Eingangsvektor und ihrem synaptischen Eigenvektor. Die Lern-Nachbarschaft wird durch ein nicht-lineares Widerstandsnetzwerk erzeugt.**

## Adresse des auteurs

Vincent Peiris, ing. dipl. EPFL, Dr. Bertrand Hochet, ing. dipl. EPFL, Tim Creasy, MSc. Prof. Dr. Michel Declercq, Ecole Polytechnique Fédérale de Lausanne, Laboratoire d'Electronique Générale, EL-Ecublens, CH-1015 Lausanne.

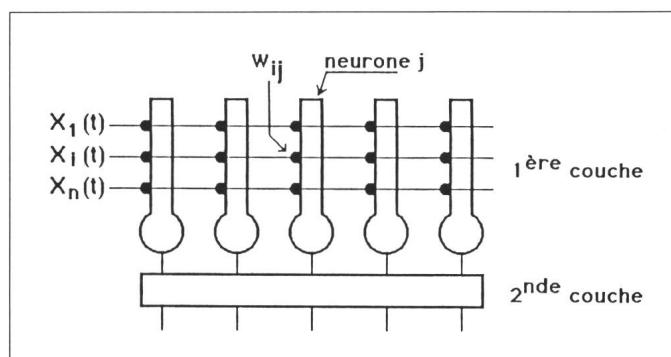

Les réseaux de Kohonen ont montré leur aptitude à résoudre des problèmes complexes de classification d'information [1; 2]. Le problème de leur réalisation est donc intéressant en soi. Du point de vue de l'implémentation, un réseau de Kohonen peut être divisé en deux couches (fig.1). Dans la première, les neurones ont un nombre limité d'entrées, et calculent une mesure de distance entre le vecteur d'entrée  $X$  et le vecteur de leurs poids synaptiques  $w_{ij}$ . L'algorithme d'apprentissage y est aussi implanté. Des simulations fonctionnelles ont montré que la mesure de distance peut être la distance de Manhattan, explicitée ci-après.  $j$  est l'indice du neurone,  $i$  est l'indice des composantes des vecteurs.

$$s_j(t) = \sum_{i=1}^n |x_i(t) - w_{ij}(t)| \quad (1)$$

La seconde couche détecte le neurone de la première couche qui répond le mieux au vecteur d'entrée, c'est-à-dire dont le vecteur synaptique est le plus proche du vecteur d'entrée au sens de la mesure considérée. L'apprentissage est exécuté selon la relation 2 et seuls apprennent les neurones  $j$  situés à l'intérieur d'un voisinage  $N_{sr}(t)$  autour du neurone le plus excité.

$$w_{ij}(t+1) = w_{ij}(t) + \beta(t)[x_i(t) - w_{ij}(t)]N_{sr}(t) \quad (2)$$

Généralement, le gain d'apprentissage  $\beta(t)$  est une fonction décroissante du temps et est constant pour tous les neurones situés dans le voisinage d'apprentissage. Cependant, la convergence de l'algorithme est très améliorée si  $\beta(t)$  dépend aussi de la distance du neurone considéré au neurone le plus excité, autour duquel le voisinage d'apprentissage est centré.

Cet article décrit l'implémentation de réseaux de Kohonen complets à parallélisme total. Ceci est rendu possible par un stockage dynamique discréte des poids synaptiques permettant de simplifier le calcul de distance et les opérations d'apprentissage, ainsi que par la génération analogique du voisinage d'apprentissage. Le réseau exhibe un comportement numérique, et des simulations ont montré que l'utilisation de variables discrètes n'altère pas la fonctionnalité ni la convergence du réseau.

## Implémentation de la première couche du réseau

L'élément central des neurones de la première couche est la cellule synaptique. Les poids synaptiques sont

**Figure 1**

Structure d'un réseau de Kohonen de cinq neurones à trois entrées

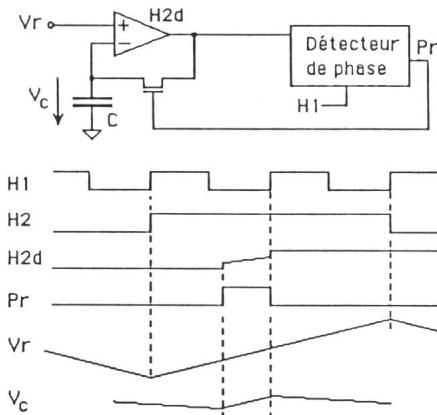

codés sous forme d'une tension aux bornes d'une capacité. Un système de rafraîchissement basé sur le principe de conversion analogique-digital «simple pente» est utilisé pour compenser les courants de fuite des capacités de stockage [3]. Deux signaux d'horloge  $H1$  et  $H2$  sont employés, tels que la période de  $H2$  est un multiple de celle de  $H1$ . Un délai contrôlé en tension génère un signal  $H2d$  dont le retard par rapport à  $H2$  est proportionnel à la tension  $V$  à rafraîchir. Enfin, un détecteur de phase verrouille le front montant de  $H2d$  sur l'un des fronts montant de  $H1$ . Ainsi, une relation est établie entre le poids synaptique et le nombre d'impulsions de  $H1$  entre les fronts montant de  $H2$  et  $H2d$ . Ce principe a été présenté dans une version

**Figure 2 Rafraîchissement de la tension  $V_C$  aux bornes d'une capacité**

Dès que  $V_r$  dépasse  $V_c$ , l'amplificateur passe du mode comparateur au mode suiveur, jusqu'au prochain front montant de  $H1$ .

simple en [4], la figure 2 montre une version améliorée où l'offset du générateur de délai est compensé.

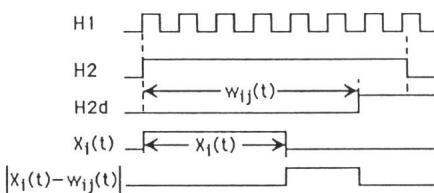

L'entrée  $X_j$  est une impulsion codée en largeur, synchrone avec  $H2$ . Grâce au dispositif de stockage, le poids synaptique est représenté (entre autre) par le délai entre les fronts montant de  $H2$  et  $H2d$ . La distance de Manhattan peut donc être calculée par le «Non-OU exclusif» de  $X_j$  et  $H2d$ , dont la sortie autorise le comptage des impulsions.

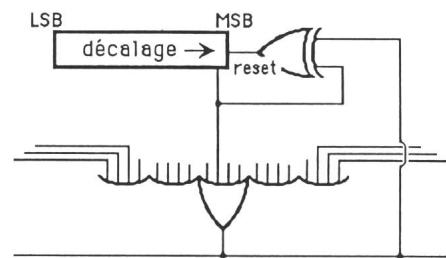

**Figure 3 Calcul de la distance de Manhattan**

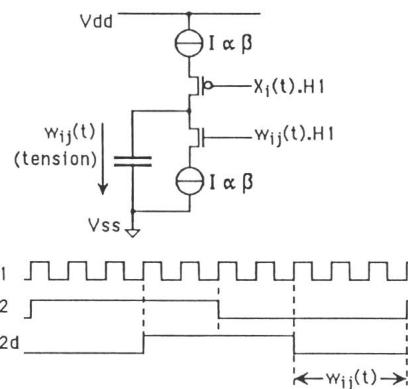

**Figure 4** **Implantation de l'algorithme d'apprentissage**

sions de  $H1$  par un compteur asynchrone (fig.3). Il est à noter que le calcul d'un produit scalaire est effectué par une porte AND, à condition cette fois que le signal d'entrée soit un train d'impulsions équi-espacées.

Pendant la phase d'apprentissage, un pointeur est généré par la seconde couche du réseau, afin de sélectionner les neurones compris dans le voisinage d'apprentissage  $Nsr$ . Les neurones sélectionnés réévaluent leurs poids synaptiques de la façon suivante:  $W_{ij}(t)$  autorise l'horloge  $HI$ , dont les impulsions décrémentent la valeur de  $W_{ij}(t)$  en commutant une source de courant vers la masse; puis  $X_j(t)$  autorise l'horloge  $HI$ , dont les impulsions incrémentent la valeur de  $W_{ij}(t)$  en commutant une source de courant depuis  $Vdd$  (fig.4).

## Implémentation de la seconde couche du réseau

Un aspect important de la conception d'un réseau de Kohonen est la détection du neurone le plus excité, ainsi que la génération du voisinage d'apprentissage avec les différentes valeurs de gain. Les sorties des neurones sont des mots binaires de  $n$  bit,

où  $n$  dépend du nombre de synapses par neurone et de la dynamique des poids synaptiques. Dans notre solution, la détection est réalisée en  $n$  pas, par un détecteur de maximum travaillant en mode numérique (fig.5). Au pas  $k$ , les bits de poids  $k$  de toutes les sorties des neurones sont comparés en utilisant une porte OU distribuée sur le réseau.

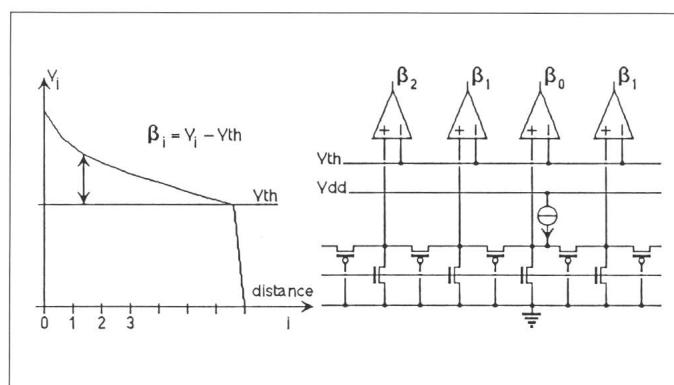

Une fois détecté le neurone le plus excité, le voisinage d'apprentissage est généré par un réseau résistif non-linéaire [7]. Un nœud de ce réseau est associé à chaque neurone de la première couche. Les nœuds sont connectés à la masse via une source de courant, et reliés à leur quatre plus proches voisins par un transistor PMOS dont la grille est à la masse. Un

**Figure 5** Détecteur de maximum en mode numérique

courant est injecté au nœud correspondant au neurone le plus excité. Le profil de tension aux nœuds voisins du point d'injection est montré à la figure 6, il est donc bien adapté à la génération du voisinage. Du fait de la variation brutale de tension sur les bords, le nombre de nœuds à l'intérieur du voisinage est quasiment proportionnel au courant injecté. Des mesures faites sur un réseau orthogonal de  $32 \times 32$  nœuds montrent que le voisinage a une forme circulaire. De plus, en seuillant les tensions aux nœuds du réseau non-linéaire par une tension

**Figure 6**

Génération du

voisinage

d'apprentissage

et du gain variable

constante, il est possible de faire varier le gain d'apprentissage.

Pendant la phase d'utilisation du réseau, seul le détecteur de maximum est opérant.

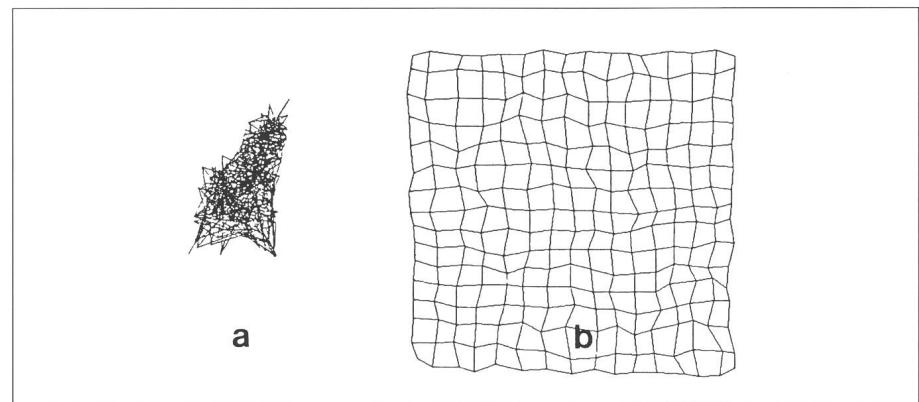

## Simulations et résultats préliminaires

Cette implémentation de réseaux de Kohonen a été validée par des simulations fonctionnelles. Des réseaux de  $50 \times 50$  neurones à deux entrées ont été simulés, où le gain d'apprentissage  $b(t)$  dépend de la distance des neurones au neurone le plus sensible au vecteur d'entrée. Les variables internes (poids synaptiques, entrées et sorties) sont des mots binaires de 8 bit. Les réseaux simulés exhibent une grande rapidité de convergence. La figure 7 montre l'état d'un réseau de Kohonen de  $16 \times 16$  neurones à l'initialisation et après la présentation de 10000 vecteurs d'entrée.

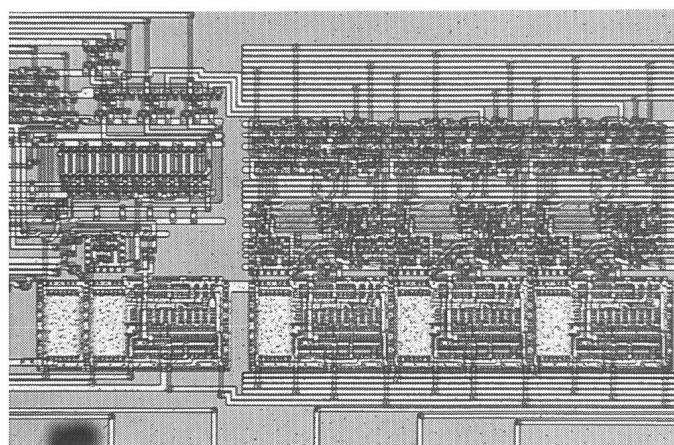

Plusieurs cellules de stockage synaptique ont été réalisées dans une technologie standard CMOS à deux microns de grille et deux niveaux de métal. Les mesures montrent que 200 niveaux de tension peuvent être stockés sur la même capacité. La taille d'une synapse complète incluant le rafraîchissement du poids, le calcul de la distance de Manhattan et l'apprentissage local est de l'ordre de 200 par 300  $\mu\text{m}^2$ . La figure 8 est la photographie

Figure 7 Etat d'un réseau de Kohonen de  $16 \times 16$  neurones

- a Initialisation

- b Après 10000 pas d'apprentissage

Le carré englobant représente l'espace des vecteurs d'entrée de dimension 2. Le treillis représente le réseau de neurones. Une intersection représente un neurone et son vecteur synaptique dans l'espace des vecteurs d'entrée. Les segments représentent les relations de voisinage entre les neurones

d'un neurone complet à trois synapses, la dimension est de l'ordre de 300 par  $800 \mu\text{m}^2$ .

synaptiques peuvent être étendues à d'autres réseaux.

## Conclusion

Grâce à l'utilisation de techniques analogiques et digitales et à un codage efficace des données, les fonctions neuroniques usuelles sont réalisables à un coût très faible en surface de silicium. Ceci devrait permettre la réalisation de réseaux modulaires de grande dimension. De plus, les applications du stockage discret des poids

## Remerciements

Ce projet est supporté par la Fondation Suisse pour la Recherche en Microtechnique. Nos remerciements vont aussi à Samer Abdo et Guy Corbaz pour l'aide apportée.

## Bibliographie

- [1] T. Kohonen: The Neural Phonetic Typewriter. IEEE Computer, March 1988.

- [2] T.M. Martinet, H.J. Ritter, K.J. Schulten: Three-dimensional neural net for learning visuomotor coordination of a robot arm. IEEE Trans. on Neural Networks, 1(1990)1.

- [3] B. Hochet: Multivalued MOS memory for variable-synapse neural networks. Electronics Letters, 25(1989)10.

- [4] B. Hochet, V. Peiris, G. Corbaz, M. Declercq: Implementation of a neuron dedicated to Kohonen maps with learning capabilities. Custom Integrated Circuits Conference 1990, Boston, May 1990.

- [5] B. Hochet, V. Peiris, S. Abdo, M. Declercq: Implementation of a learning Kohonen neuron based on a pulse stream arithmetics. European Solid-State Circuits Conference 1990. Grenoble, France, 19–21 Septembre 1990.

- [6] B. Hochet, V. Peiris, S. Abdo, M. Declercq: Implementation of a neuron dedicated to Kohonen maps with learning capabilities. IEEE Journal of Solid States Circuits, 1991, March.

- [7] P. Heim, B. Hochet, E. Vittoz: Generation of learning neighbourhood in Kohonen feature maps by means of simple nonlinear networks, Electronics Letters, 27(1991)3.

- [8] V. Peiris, B. Hochet, S. Abdo, M. Declercq: Implementation of a Kohonen map with learning capabilities, IEEE International Symposium on Circuits and Systems. Singapore, June 11–14, 1991.

Figure 8

Neurone à trois entrées

réalisé avec une tech-

nologie CMOS  $2\mu$