**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 82 (1991)

**Heft:** 17

**Artikel:** Ist er die Grundlage einer neuen PC-Generation? : Der Eisa-Bus

Autor: Stein, Erich

**DOI:** https://doi.org/10.5169/seals-903000

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 30.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

## Ist er die Grundlage einer neuen PC-Generation?

Der Eisa-Bus

Erich Stein

Der Eisa-Bus wird von vielen PC-Herstellern als eine wichtige Grundlage für eine neue Generation leistungsfähiger PCs betrachtet. In diesem Beitrag wird nach einem kurzen Überblick über wichtige PC- und Workstation-Busse der Eisa-Bus im Detail behandelt. Dabei wird nicht nur die Bus-Definition erläutert, sondern es werden auch Gesichtspunkte wie LSI-Businterfaces, Auswirkungen auf Betriebssysteme und die Marktsituation diskutiert. Ein kurzer Vergleich mit dem IBM-Microchannel und eine Übersicht über allgemeine Trends der Bussysteme runden das Thema ab.

Pour de nombreux fabricants de PCs le bus Eisa est un fondement essentiel d'une nouvelle génération de PCs performants. Après un apercu des bus importants pour PCs et stations de travail. l'article traite du bus Eisa en détail. Outre la définition du bus on discute aussi des points de vue tels que les interfaces LSI, les effets sur les systèmes d'exploitation et la situation sur le marché. Une comparaison succincte avec le Microchannel IBM et une vue d'ensemble des tendances générales des systèmes de bus complètent le thème.

Adresse des Autors

Erich Stein, ABB Informatik AG, 5401 Baden

Der Microchannel, auch als MCA-Bus bezeichnet, wurde im Bulletin SEV/VSE ausführlich dargestellt [1]. In diesem Beitrag wird die Alternative zum MCA-Bus, der Eisa-Bus, beschrieben. Obgleich eine Konkurrenzsituation zwischen Eisa- und MCA-Bus nicht zu übersehen ist, wird dieser Beitrag keine Entweder-Oder-Entscheidung für eines dieser Systeme provozieren; es soll vielmehr versucht werden, einige für die Beurteilung eines Bussystems relevanten Argumente aus einer übergeordneten Sicht einzusetzen.

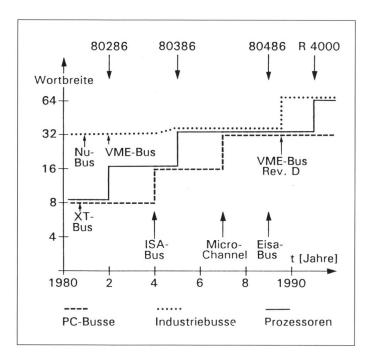

Dem Computeranwender ist es meist gleichgültig, welches Bussystem in seiner Maschine verwendet wird, solange dieses die gestellten Anforderungen erfüllt. Erst bei einer näheren Betrachtung – wie sie der qualifizierte Anwender, der Fachhändler oder der Systemintegrator in der Regel anstellt - erhält das Bussystem eine grössere Bedeutung. Diese Fachleute wissen, dass es eine Anzahl verschiedener Bussysteme, jedes mit seinen spezifischen Vor- und Nachteilen, gibt. Vor einer näheren Betrachtung von Bussystemen ist es deshalb hilfreich, sich zu erinnern, wie sich die Wortbreiten von Prozessoren und Bussen entwikkelt haben (Bild 1).

## **Bussysteme für Personal- Computer und Workstations**

Bevor wir uns den Details des Eisa-Busses zuwenden, seien einige wichtige Bussysteme [2] kurz erwähnt. Damit soll der Eindruck vermieden werden, es gäbe nur den Eisa-Bus.

Der S-100-Bus war einer der ersten Busse, die in PCs verwendet wurden.

Er wurde 1975 mit einer Datenwortbreite von 8 Bit eingeführt und später mit der Bezeichnung IEEE 696 standardisiert und auf 16 Bit erweitert. Über eine Erweiterung auf 32 Bit wird zurzeit nachgedacht.

Der Bus des PC/AT – auch als ISA-Bus, Industry Standard Architecture, bezeichnet, wird heute in mehr als 20 Mio. Geräten verwendet. Allein in den USA wurden über 100 Mia. \$ für Hard- und Software zum AT-Bus sowie für Schulung investiert.

Im IBM PS/2 wurde erstmals der Microchannel – auch als MCA, Microchannel Architecture, bezeichnet – verwendet. Erste Geräte kamen 1988 auf den Markt. IBM hat bis 1989 etwa 3 Mio. PS/2 mit MCA ausgeliefert. Neuerdings wird der Microchannel auch in der Workstation-Reihe RS/6000 verwendet. Der Nu-Bus wurde 1978 im MIT entwickelt und als IEEE 1196 standardisiert. Er wird im Macintosh II verwendet, in modifizierter Form auch in der Next-Workstation.

Der VME-Bus wurde 1982 eingeführt. Er ist im Standard IEEE 996 definiert. Der VME-Bus ist nicht als PC-Bus bekannt; er hat sich jedoch in industriellen Anwendungen sehr stark durchgesetzt. Immerhin wird er im Atari Mega TT als Eingabe-Ausgabe-Bus verwendet. Dies eröffnet die Perspektive, mit einem preiswerten PC auf die Welt der industriellen Prozessinterfaces zugreifen zu können. Andererseits werden immer mehr Rechner vorgestellt, die mit dem PC/AT kompatibel sind, aber auf dem VME-Bus aufbauen.

Zwei weitere Busse, die aus der Workstation-Welt kommen, könnten in Zukunft ebenfalls in PCs Eingang finden: der S-Bus von Sun und der Turbochannel von DEC. Beide sind 32-Bit-Busse, haben hohe Übertragungsraten und verwenden relativ

Der Systemintegrator baut komplexe Systeme aus Hard- und Softwarekomponenten zusammen, die von einer Anzahl verschiedener Hersteller kommen.

Bild 1 Wortbreiten einiger Prozessoren und Busse

kleine Board-Abmessungen. Die Tabelle I fasst die wesentlichen Daten der wichtigsten PC- und Workstation-Busse zusammen.

#### Kenngrössen und Bewertungskriterien für Bussysteme

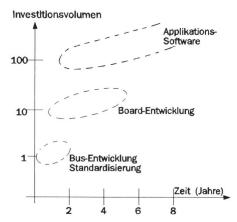

Obwohl das Bussystem ein zentraler Teil eines Computers ist, muss seine relative Bedeutung klar erkannt werden. Während die Entwicklung eines Bussystems und der zugehörige Standardisierungsprozess relativ schnell und billig realisiert werden können, liegen die Investitionen für die Entwicklung darauf aufbauender Boards bereits eine Grössenordnung höher. Die zugehörige Software und die damit verbundenen Kosten liegen nochmals wesentlich höher. Das Bild 2 versucht dies darzustellen. Für die Sicherstellung eines guten Kundennutzens ergeben sich daher folgende Anforderungen:

- Langlebigkeit des Bussystems (Investitionsschutz),

- grosse Breite des Board-Angebots und der zugehörigem Software,

- Konkurrenzfähigkeit des Angebots.

Dies alles kann ein Bussystem nur gewährleisten, wenn es standardisiert ist. Standards können auf zwei verschiedene Arten entstehen. Einerseits können sie von nichtprivaten Institutionen erarbeitet und festgeschrieben werden, andererseits können sogenannte Industrie-Standards entstehen, deren grosse Verbreitung dafür sorgt, dass sich praktisch jedermann an sie hält. Die meisten bekannten Busse gehören in die erste Gruppe. ISA ist eine Ausnahme; die Spezifikation wurde von IBM vorgegeben.

Welches sind nun die Eigenschaften, die von einem Busstandard erfasst werden müssen? Die Definition einer Menge von Signalen und deren Bedeutung stellt nur einen – wenn auch wichtigen – Teil eines Busstandards dar. Damit das Zusammenwirken von Produkten verschiedener Hersteller möglich wird, müssen eine ganze Reihe von Eigenschaften in einem Busstandard festgelegt werden:

- Mechanisch: Hier geht es um Kartenformate, Kartenführungen und um

die mechanischen Eigenschaften der Steckverbindungen.

- Elektrisch: Pegel, Treiberfähigkeiten, das dynamische Verhalten der Leitungen (Reflexionen, Übersprechen), Störstrahlungen und die maximale Strombelastung pro Kontakt.

- Thermisch: Die maximal zulässige Verlustleistung pro Karte muss in Abstimmung mit den vorgesehenen Kühlungsmethoden festgelegt werden.

- Logisch (statisch): Dies betrifft die Auswahl der auf dem Bus möglichen Signale und deren Bedeutung.

- Logisch (funktional): Welche Sequenzen von Signalübergängen sind definiert und welche Funktion haben sie? Welche Sequenzen sind verboten?

Bild 2 Relative Bedeutung von Bussystemen

Logisch (dynamisch): Spezifikation des zulässigen zeitlichen Verhaltens der Signale. Die letzten beiden Grup-

| Bussysteme für PC und Workstations |       |      |      |       |         |         |  |  |

|------------------------------------|-------|------|------|-------|---------|---------|--|--|

| Bus                                | ISA   | Eisa | MCA  | Nu-Bu | s S-Bus | Turbo-  |  |  |

| Übertragungs-<br>rate bei DMA      |       |      |      |       |         | channel |  |  |

| Theoret. Maximum                   |       |      |      |       |         |         |  |  |

| (MByte/s)                          | 8     | 33   | 40   | 37,5  | 100     | 100     |  |  |

| Praktikabel                        |       |      |      |       |         |         |  |  |

| (MByte/s)                          | 6     | 30   | 13   | 35    | 27      | 93      |  |  |

| Taktfrequenz                       | 8     | 8    | _    | 10    | 16,7    | 12,5    |  |  |

| (MHz)                              |       |      |      |       | -25     | -25     |  |  |

| Adressraum                         |       |      |      |       |         |         |  |  |

| (GByte)                            | 0,016 | 4    | 4    | 4     | 0,256   | 16      |  |  |

| Anzahl Steck-                      |       |      |      |       |         |         |  |  |

| kontakte                           |       |      |      |       |         |         |  |  |

| <ul> <li>Signalkontakte</li> </ul> | 88    | 143  | 136  | 51    | 82      | 44      |  |  |

| gesamt                             | 98    | 188  |      |       | 96      |         |  |  |

| Board-Fläche                       |       |      |      |       |         |         |  |  |

| (cm <sup>2</sup> )                 | 406   | 406  | 250  | 332   | 123     | 168     |  |  |

| Max. Verlust-                      |       |      |      |       |         |         |  |  |

| leistung pro                       |       |      |      |       |         |         |  |  |

| Board (W)                          | 22    | 22   | 12,6 | 10    | 10,7    | 26      |  |  |

Tabelle I Bussysteme für PC und Workstations

pen werden meistens gemeinsam in Zeitdiagrammen spezifiziert.

- Komplexe Funktionen: Hierzu gehören Abläufe, die aus einer Folge von Transaktionen zusammengesetzt sind. Beispielsweise die Interruptverarbeitung, direkte Speicherzugriffe (DMA) und Cache-Funktionen.

Die verschiedenen Eigenschaften können nicht unabhängig voneinander festgelegt werden. Bei einem erfolgreichen Bussystem sind sie vielmehr sorgfältig aufeinander abgestimmt. Beispielsweise ist eine kleine Kartenfläche gut, wenn man Rechner mit kleinen Abmessungen bauen möchte. Andererseits erlaubt eine höhere Kartenfläche eine grössere Anzahl von Steckverbindungen und damit eine höhere Flexibilität sowie eine höhere Verarbeitungsleistung. Hingegen werden die thermischen Probleme dadurch verschärft, und die Zuverlässigkeit der Karten sinkt.

#### Eigenschaften des Eisa-**Busses**

#### Entstehungsgeschichte und Verbreitung

Die Entwicklung des Eisa-Busses wurde am 13. September 1988 durch eine Gruppe von neun PC-Herstellern (AST, Compaq, Epson, HP, NEC, Olivetti, Tandy, Wyse und Zenith) formell bekanntgegeben. Ziel dieser Gruppe war, ein Gegengewicht zu IBM zu bilden und die Weiterentwicklung der PC-Technologie in einem anderen und breiteren Rahmen voranzutreiben, als dies von IBM erwartet werden konnte. An der Comdex im November 1989 wurden die ersten, auf dem Eisa-Bus aufgebauten PCs

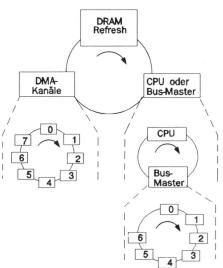

Bild 3 Arbitration beim Eisa-Bus

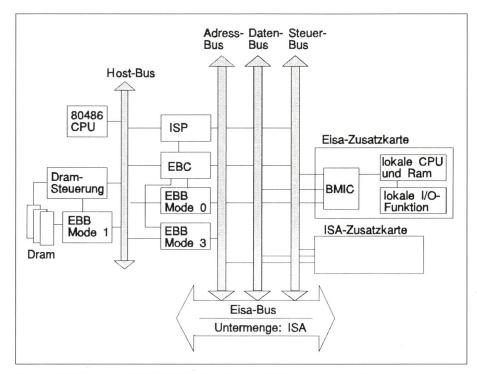

Bild 4 CPU-Platine mit CPU 80486, Eisa-Chipset 82350, Bus und Eisa-Zusatzkarte

Eisa Bus Controller 82358 **FBC**

**FBB** Eisa Bus Buffer 82352

ISP Integrated System Peripheral 82357

BMIC Bus Master Interface Controller 82355

vorgestellt. Seit dem Frühjahr 1991 werden solche Eisa-PCs von über einem Dutzend Herstellern angeboten. Die Zahl der Anbieter von Zusatzkarten ist noch grösser. Unter anderem sind die folgenden Funktionen verfügbar: Controller für SCSI<sup>2</sup>, Ethernet, Arcnet, Token-Ring und FDDI3, Videoadapter und Multiport-I/O-Controller.

#### Standardisierungs-Situation beim Eisa-Bus

Ein Problem des Eisa-Busses besteht darin, dass seine Spezifikation nicht von einem der bekannten Normierungsgremien erarbeitet wurde, sondern dass sie von einer Gruppe privater PC-Hersteller kommt. Dies führte zum immer noch gültigen Zustand, dass die Eisa-Spezifikation nur gegen die Unterzeichnung eines Non-Disclosure-Agreements erhalten werden kann, was weltweit auch einige 100 Firmen getan haben. Dies mag aus Marketing-Gesichtspunkten durchaus akzeptabel sein, hat aber den Nachteil, dass deshalb der Eisa-

SCSI (Small Computer System Interface) ist eine Standard-Schnittstelle zu Massenspeichern und Peripheriegeräten.

FDDI (Fiber Distributed Data Interface) ist ein lokales Netzwerk mit Glasfasern, das Datenraten bis 100 MBit/s zulässt.

Bus nicht als offener Bus bezeichnet werden kann. Es liegt am Eisa-Konsortium, hier Abhilfe zu schaffen.

#### Beschreibung der wichtigsten Daten und Eigenschaften

Kompatibilität zum ISA-Bus

Der Eisa-Bus ist voll kompatibel mit bestehenden ISA-Boards<sup>4</sup>. Dies ist eine seiner wichtigsten Eigenschaften, die den Übergang vom 16-Bit-ISA-Bus zum 32-Bit-Eisa-Bus wesentlich erleichtern und beschleunigen soll. Deshalb haben die Eisa-Boards dieselben Abmessungen wie die bekannten ISA-Boards.

#### Grundsätzlicher Aufbau von Eisa-Systemen

Wie bei ISA-Systemen geht man von einer Systemkarte (Motherboard) aus, auf der sich die CPU, der Systemspeicher und weitere zentrale Funktionen befinden. Diese sind mittels eines Host-Busses miteinander verbunden, an den auch das Eisa-Businterface angeschlossen ist (Bild 4). Auf

Eine Spezifikation des ISA-Busses findet sich in [3].

der Systemkarte sind weiter eine Anzahl Steckplätze für Eisa- und ISA-Erweiterungskarten angeordnet.

Stecker, Anzahl Steckplätze, Steckerbelegung

Für ein Bussystem sind die Leiterplattenstecker von wesentlicher Bedeutung. Sie entscheiden über die mechanische Stabilität, die Lebensdauer der Steckkarten und die elektrischen Eigenschaften der Verbindungen. Aus Kompatibilitätsgründen verwenden Eisa-Boards zunächst den direkten Stecker des ISA-Busses, der zweimal 49 Kontakte aufweist. Dies ist für Eisa-Boards, die nur 16-Bit-Informationen verwenden, auch genügend. Für 32-Bit-Boards gibt es zwei weitere Kontaktreihen unterhalb der bisherigen. Damit werden weitere zweimal 45 Kontakte zur Verfügung gestellt. Durch mechanische Einrastsperren wird verhindert, dass ISA-Boards in die untere Kontaktreihe eingesteckt werden können.

Die Anzahl zulässiger Steckplätze hängt einerseits von der elektrischen

Belastung durch die Busteilnehmer und der kapazitiven Belastung durch die Busleitungen ab, andererseits aber auch von der steckplatzspezifischen Adressierung (siehe unten). Die maximale Anzahl der Eisa-Steckplätze in einer Backplane beträgt 15.

Die Steckerbelegung definiert, welche Bussignale vorhanden sind. Diese Signale und deren Bedeutung sind in Tabelle II dargestellt, wo auch deutlich wird, dass die Eisa-Signale eine Obermenge der ISA-Signale darstellen. Der Eisa-Bus besteht – wie ande-

| Signale des Eisa-Busse       | es                                                                                                                                                                                                                                                                                      |                      |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Signal(e)                    | Bedeutung (Englische Bezeichnung des Signals, gefolgt von einer deutschen Beschreibung seiner Funktion)                                                                                                                                                                                 | vorhanden<br>bei     |

| BCLK                         | Bus Clock. Die gemeinsame Zeitreferenz für Signale auf dem Bus. Die Taktfrequenz darf zwischen 6 MHz und 8.33 MHz liegen.                                                                                                                                                               | ISA/Eisa             |

| [D15:0]                      | Data Bus. Die niedrigwertigen 16 Bit des Datenbusses.                                                                                                                                                                                                                                   | ISA/Eisa             |

| [D31:16]                     | Data Bus. Die höherwertigen 16 Bit des Datenbusses.                                                                                                                                                                                                                                     | Eisa                 |

| SA[19:0]<br>SBHE*            | System Address. Die niedrigwertigen 20 Bit des Adressbusses. Gültig während eines gesamten Buszyklus. System Bus High Enable. Zeigt an, ob das höherwertige Byte eines Wortes am Transfer teilnimmt. Erlaubt ISA-Mastern, zusammen mit dem Signal SA0 auf Bytes oder Worte zuzugreifen. | ISA/Eisa<br>ISA/Eisa |

| LA[31:24]*                   | Unlatched Address. Nichtzwischengespeicherte Adressen LA[31:24]*                                                                                                                                                                                                                        | Eisa                 |

| LA[16:2]                     | Zwischengespeicherte Adressen LA[16:2]. Zusammen mit LA[23:17] (siehe unten) ergibt dies einen 32-Bit-Adressbus.                                                                                                                                                                        |                      |

| LA[23:17]                    | Unlatched Address. Die höherwertigen ISA-Adressbits, nicht zwischengespeichert.                                                                                                                                                                                                         | ISA/Eisa             |

| BE[3:0]*                     | Byte Enable. Jedes Bit von BE zeigt an. welches entsprechende Byte des Datenbusses an einem Transfer teilnimmt.                                                                                                                                                                         | Eisa                 |

| AENx                         | Slot Specific Address Enable Signal for Slot x. Damit lassen sich die Eisa-Zusatzkarten individuell ansprechen.                                                                                                                                                                         | ISA/Eisa             |

| MSBURST*<br>SLBURST*         | Master and Slave Burst. Eisa-Master zeigt mit MSBURST* an, dass er einen Bursttransfer wünscht. Slave kann mit SLBURST* antworten.                                                                                                                                                      | Eisa                 |

| EX32*, EX16*                 | Eisa Slave Size. Die Systemkarte bestimmt mittels dieser Signale die Wortbreite von Erweiterungskarten.                                                                                                                                                                                 | Eisa                 |

| M16*, IO16*                  | ISA Memory and IO-Slave Size Signals. Zeigt an, dass ein Slave 16-Bit-Transfers wünscht.                                                                                                                                                                                                | ISA/Eisa             |

| EXRDY                        | Eisa Slave Ready Signal. Wird von Eisa-Slaves zum Einfügen von Wartezyklen benutzt.                                                                                                                                                                                                     | Eisa                 |

| CHRDY ISA                    | Ready Signal. Wird von ISA-Slaves zum Einfügen von Wartezyklen benutzt.                                                                                                                                                                                                                 | ISA/Eisa             |

| NOWS*                        | No Wait State Signal. ISA-Slaves unterdrücken hiermit den üblichen Wartezyklus des ISA-Zyklus, Eisa-Slaves verlangen damit den komprimierten Zyklus der Dauer 1,5 BCLK.                                                                                                                 | ISA/Eisa             |

| START*, CMD*                 | Start and Command. Timing-Signale für Eisa-Zyklen.                                                                                                                                                                                                                                      | Eisa                 |

| WR VR                        | Write/Read. Statussignal, das einen Schreib- oder Lesezyklus identifiziert.                                                                                                                                                                                                             | Eisa                 |

| MIO                          | Memory-I/O. Statussignal, das für einen Zyklus Speicher- oder Ein-/Ausgabezugriff identifiziert.                                                                                                                                                                                        | Eisa                 |

| IORC*, IOWC*<br>MRDC*, MWTC* | ISA Read and Write Strobes. IO bezeichnet Strobes für IO-Adressen, M solche für Speicheradressen, R und RD stehen für Lese-Strobes, W und WT für Schreib-Strobes. SMRDCH* und SMWTCH* zeigen                                                                                            | ISA/Eisa             |

| SMRDC*, SMWTC*               | an, dass die Adresse zwischen 0 und 000F'FF'FF liegt.                                                                                                                                                                                                                                   |                      |

| LOCK*                        | Bus Lock. Dieses Signal wird von Bus-Mastern aktiviert, um sich den exklusiven Zugriff auf Speicher oder Ein-Ausgabefunktionen zu sichern.                                                                                                                                              |                      |

| BALE                         | Bus Address Latch Enable. Zeigt an, dass der Inhalt des LA-Busses gültig ist. ISA-Slaves übernehmen dann die Adresse. Bei Eisa-Slaves sollen dafür START* oder CMD* verwendet werden.                                                                                                   | ISA/Eisa             |

| MREQx*,                      | Master Request and Acknowledge Lines for Slot x.                                                                                                                                                                                                                                        | Eisa                 |

| MAKx*                        | Slotspezifische Leitungen, mittels denen Eisa-Master anzeigen, dass sie die Bussteuerung übernehmen wollen (MREQx). Der Arbiter teilt über MAKx mit, wann dies möglich ist. x ist eine Hexadezimalzahl zwischen 1 und 15.                                                               |                      |

| DRQ[7:5][3:0]                | DMA Request and Acknowledge. DRQ wird von DMA-Geräten und von ISA-Mastern aktiviert, um die                                                                                                                                                                                             |                      |

| DAK[7:5][3:0]*               | Steuerung des Busses zu beanspruchen. Die Systemkarte bestätigt dies mit DAK*.                                                                                                                                                                                                          | ISA/Eisa             |

| T-C                          | Terminal Count. Ausgangssignal: der DMA-Controller auf der Systemkarte zeigt das Endes eines DMA-Transfers an.                                                                                                                                                                          | ISA/Eisa             |

| MASTER16*                    | Master Size. Aktive ISA- oder Eisa-Master können damit den Bus in den hochohmigen Zustand schalten.                                                                                                                                                                                     | ISA/Eisa             |

| REFRESH*                     | Refresh. Zeigt an, dass ein Refresh-Zyklus abläuft.                                                                                                                                                                                                                                     | ISA/Eisa             |

| OSC                          | Oscillator. Ein Takt der Frequenz 14,31818 MHz für Zeitgeber.                                                                                                                                                                                                                           | ISA/Eisa             |

| RESDRV                       | Hardware Reset. Damit werden alle Karten auf dem Bus zurückgesetzt.                                                                                                                                                                                                                     | ISA/Eisa             |

| IRQ[15:14]<br>[12:9][7:3]    | Interrupt Request Lines. Zusatzkarten können damit Unterbrechung der CPU anfordern.                                                                                                                                                                                                     | ISA/Eisa             |

| IOCHK*                       | I/O-Check. ISA- oder Eisa-Zusatzkarten können das Auftreten eines Fehlerzustandes melden.                                                                                                                                                                                               | ISA/Eisa             |

#### Tabelle II Signale des Eisa-Bus

<sup>\*</sup> kennzeichnet ein invertiertes Signal

re Busse auch – aus einer Anzahl von Subbussen. Dies sind der Adress-, der Daten- und der Steuerbus. Hinzu kommen Masse- und Stromversorgungsleitungen sowie reservierte, das heisst bisher noch nicht belegte Kontakte.

#### Busfrequenz und Buszyklen

Der Eisa-Bus arbeitet wie der ISA-Bus mit einer nominalen Taktfrequenz von 8 MHz (sie darf zwischen 6 und 8,33 MHz liegen). Damit gibt es beim Einsatz alter ISA-Karten in Eisa-Systemen keine Zeitprobleme. Verschiedene Typen von Buszyklen wurden definiert. Beim Standardzyklus wird im ersten Taktzyklus die Adresse übertragen, im zweiten die Daten. Beim komprimierten Zyklus wird pro 1,5 Taktzyklen ein Datenwort übertragen. Dazu wird das CMD-Signal (Tab. II) benutzt. Beim Burst Mode wird in jedem Taktzyklus ein Datenwort transferiert. Damit ergibt sich im Burst Mode eine theoretisch erreichbare Datenrate von 32 MByte/s.

#### Busmaster und Arbitrierung

Eine wichtige Eigenschaft des Eisa-Busses besteht darin, dass mehrere Busmaster abwechselnd den Bus steuern können. Damit können intelligente Peripheriecontroller voll genutzt und Multiprozessorsysteme realisiert werden. Die resultierende Parallelarbeit führt zu einer entsprechend höheren Systemleistung. Die Zuteilung des Busses wird durch einen Arbiter gesteuert. Die Busmaster verlangen die Bussteuerung über eine steckplatzspezifische Leitung MREQx5. Der Arbiter gewährt diese entsprechend einem Prioritätsschema und teilt dies mit steckplatzspezifischen Signal MAKx mit. Die Arbitrierung geschieht zyklisch auf verschiedenen Ebenen (Bild 3). Auf der obersten bekommen zyklisch DRAM-Refreshcontroller, die CPU oder einer der Busmaster sowie ein DMA-Kanal die Steuerung Busses<sup>6</sup>.

#### Direkter Speicherzugriff (DMA)

Auf dem Eisa-Bus sind 7 DMA-Kanäle vorgesehen, von denen jeder einzeln für 8-, 16- oder 32-Bit-Transfers

konfiguriert werden kann. Es sind vier Zyklustypen spezifiziert: der ISA-kompatible Standardzyklus mit 4 MByte/s, der Typ A mit 5,3 MByte/s, der Typ B mit 8 MByte/s und der Typ C (Burst DMA) mit 33 MByte/s. DMA-Adressen können 32 Bit breit sein, so dass Burstlängen von 4 GByte möglich sind. Die Priorität der DMA-Kanäle kann fest oder rotierend (der zuletzt bediente Kanal erhält neu die niedrigste Priorität) gewählt werden.

#### Interrupt-System

Der ISA-Bus verwendet flankengesteuerte Interrupts, 11 Interruptleitungen sind vorhanden. Aus Kompatibilitätsgründen ist dies genauso auch beim Eisa-Bus möglich. Zusätzlich können die einzelnen Interruptleitungen als flanken- oder pegelgesteuert programmiert werden. Im Gegensatz zu den flankengesteuerten Interrupts erlauben die pegelgesteuerten das sogenannte Interrupt Sharing. Das heisst, dass mehrere interruptgenerierende Baugruppen an dieselbe Interruptleitung angeschlossen werden können.

## Automatische Konfiguration von Erweiterungskarten

Es gibt keine Schalter oder Jumper auf den Erweiterungskarten. Die Konfiguration erfolgt über Initialisierungs-Commands, die in einem nichtflüchtigen Speicher abgelegt sind. Die für die Konfiguration notwendigen Daten werden mit jedem Eisa-Board in Softwareform mitgeliefert. Für Karten, die sich an die steckplatzspezifische Adressbelegung halten, ist so eine konfliktfreie Konfiguration möglich.

#### Identifikation von Zusatzkarten

Für jede Zusatzkarte gibt es einen Product Identifier, der Hersteller und Typ enthält. Dieser wird vom Hersteller der Karte frei festgelegt, besteht aus 4 Bytes und befindet sich an einer bestimmten Adresse.

#### **Businterfaces als LSI-Bausteine**

Der Eisa-Chipset 82350 von Intel [4] ist dazu gedacht, die Prozessoren 80386/80387, 80486 und den Cache Controller 82385 mit dem Eisa-Bus zu verbinden. Der Chipset ist vollständig mit der Eisa-Spezifikation kompatibel und besteht aus den folgenden Bausteinen:

- 82358 Eisa Bus Controller (EBC)

- 82352 Eisa Bus Buffer (EBB)

- 82357 Integrated System Peripheral (ISP)

- 82355 Bus Master Interface Controller (BMIC)

Die ersten drei Bausteine sind auf der CPU-Platine anzutreffen, der vierte wird auf jedem Eisa-Master-Board einmal benötigt. Das Bild 4 zeigt das Blockdiagramm einer CPU-Platine mit einer CPU 80486, die als Eisa-Busmaster fungiert. Der Eisa Bus Controller (EBC) befindet sich zwischen dem Host- und dem Eisa-Bus. Er beobachtet Zyklen, die auf einem der beiden Busse angestossen werden. Wenn auf den Beginn eines Zyklus des Host-Busses auf diesem kein Slave antwortet, wird der Zyklus auf den Eisa-Bus weitergeleitet. Der EBC steuert auch die Datenübertragung zwischen Busteilnehmern mit verschiedener Wortbreite.

Der Eisa Bus Buffer (EBB) übernimmt Zwischenspeicher- und Treiberfunktionen zwischen dem Host- und dem Eisa-Bus. Er verfügt über drei verschiedene Betriebsarten und wird typisch in drei Exemplaren pro System eingesetzt. Die Betriebsarten sind Daten-Zwischenspeicher zwischen dem Host- und dem Eisa-Bus, ohne Parity (Mode 0); Übertragung zwischen Host-Bus und dem DRAM mit Parity (Mode 1); Adress-Zwischenspeicher zwischen Host- und Eisa-Bus (Mode 3)<sup>7</sup>.

Das Integrated System Peripheral (ISP) enthält einen DMA-Controller für 7 Kanäle, einen Busarbiter, einen Interrupt-Controller mit 16 Interrupt-Leitungen, eine Steuerung für das Auffrischen von DRAM sowie 5 Zähler und Zeitgeber. Hauptaufgabe des Bus Master Interface Controllers (BMIC) ist die Steuerung von 16-Bitund 32-Bit-Bursttransfers zwischen dem Eisa-Bus und den Funktionsblökken auf dem jeweiligen Eisa-Zusatzboard.

#### Eisa-Bus und Betriebssystem

Ein Bus und das Betriebssystem, das die auf jenem aufbauenden Erweiterungskarten unterstützt, sind nicht unabhängig voneinander. Vielmehr sollten die vom Bus zur Verfügung gestellten Möglichkeiten (z.B. Datenund Adressbreite) auch vom Betriebssystem genutzt werden. MS-DOS ist ein Single-User, Single-Task-Betriebssystem. Aus diesem Grund arbeiten Microsoft und Novell an Betriebssystem-Erweiterungen, die die

x ist eine Hexadezimalzahl zwischen 1 und 15. Das heisst, dass maximal 15 Busmaster am Eisa-Bus angeschlossen werden können. x=0 ist für die Systemkarte reserviert.

Systemkarte reserviert.

Natürlich nur dann, wenn eine Anforderung mittels MREQ\* oder DRQ[i] vorliegt.

Mode 2 ist reserviert.

| Eisa und Microchannel im Vergleich               |                           |                                                |  |  |  |

|--------------------------------------------------|---------------------------|------------------------------------------------|--|--|--|

| Leistungsmerkmal                                 | Eisa                      | MCA                                            |  |  |  |

| 32-Bit-Architektur<br>Kompatibilität zum ISA-Bus | ja<br>ja                  | ja<br>nein                                     |  |  |  |

| Datentransferrate (MByte/s)                      | 33                        | 20                                             |  |  |  |

|                                                  | Burst Mode                | Standardzyklus<br>40 MByte/s<br>Streaming Mode |  |  |  |

| Systemspeicher (Mbyte) (DRAM)                    | 4096                      | 16 (16 Bit-<br>Microchannel)                   |  |  |  |

| 32-Bit-DMA                                       | ja                        | nur 16 Bit                                     |  |  |  |

| Burstlänge Automatische Konfigurierung           | 4 GByte<br>ia             | 64 kByte<br>ja                                 |  |  |  |

| Steckplätze                                      | 15                        | 8                                              |  |  |  |

| Kartenfläche (cm²) Max. Stromaufnahme (+5V) (A)  | $12.2 \times 33.2$<br>4.5 | $8.8 \times 29.2$                              |  |  |  |

| Businterface-Chipsatz                            | Intel 82350               | Intel 82311                                    |  |  |  |

Tabelle III Eisa und Microchannel im Vergleich

volle Nutzung des Eisa-Busses erlauben, ohne die Kompatibilität mit dem bestehenden MS-DOS zu opfern. Im Vordergrund stehen Multi-User- und Netzwerkfunktionen. Eine besondere Rolle spielt hier das Bios, das ja eine gewisse Hardware-Unabhängigkeit von MS-DOS sicherstellt.

Hier muss natürlich Unix erwähnt werden, dessen Verbreitung stetig wächst. Da Unix ein Multiuser-Multitasking-Betriebssystem ist, ist sein Einsatz auf dem Eisa-Bus naheliegend. Die bekannten Unix-Versionen für PCs müssen aber noch erweitert werden, damit sie die Möglichkeiten des Eisa-Busses voll ausschöpfen können. Die wichtigsten Hersteller von Unix-Versionen für die 80X86-Prozessorfamilie arbeiten zurzeit intensiv an dieser Aufgabe.

#### Marktsituation der Eisa-Systeme

Nach einer Studie von IDC wird erwartet, dass 1992 mehr als die Hälfte aller PCs mit 80386- und 80486-Prozessoren ein 32-Bit-Bussystem verwenden werden. Die gesteigerte Leistungsfähigkeit von Systemen mit Eisa-Bus wird vor allem in Anwendungen zum Zug kommen, die Fileund Kommunikations-Server, grafische Arbeitsplätze und Mehrplatzsysteme beinhalten. Das bedeutet, dass bei den klassischen PCs - die durch Single-User-, Single-Task-Betrieb gekennzeichnet sind - der Eisa-Bus keine besondere Rolle spielen wird. Daneben wird es auf dem Eisa-Bus auch neue Funktionen geben, die in bisherigen PCs nicht verbreitet waren. Beispiele sind das Disk Mirroring (Plattenspiegelung), wo sämtliche Daten doppelt (auf zwei verschiedenen Disks) abgelegt sind, um Datenverluste infolge von Diskfehlern zu vermeiden. Ein weiteres Beispiel sind Disk Arrays wie das Intelligent Drive Array, das bis zu 8 Harddisks steuert, die jedoch als ein logisches Laufwerk mit verbesserten Kennwerten erscheinen.

Damit ergibt sich im Vergleich zu den Workstations – die bisher als leistungsfähige Geräte in einer gehobenen Preisklasse am Markt auftraten – eine interessante Entwicklung. Während die Abgrenzung zwischen PCs und Workstations bisher ziemlich eindeutig war, werden sich in Zukunft die Leistungskenngrössen und Preisniveaus stärker überlappen.

#### Ist der Eisa-Bus prozessorspezifisch?

Man kann sagen, dass die Steuersignale des ISA-Busses eine decodierte Version der Prozessor-Steuersignale der 80X86-Familie von Intel darstellen. Wegen der Kompatibilität von ISA- und Eisa-Bus trifft diese Aussage – zumindest teilweise – auch auf den Eisa-Bus zu. Trotzdem wäre es falsch, ihn deswegen als prozessorspezifischen Bus zu bezeichnen. Denn nach Bild 4 sind ja der Host- und der Eisa-Bus durch eine Businterface-Logik voneinander entkoppelt, die typisch als LSI-Chipset realisiert ist.

Ein Beispiel für den Einsatz des Eisa-Busses als Ein- und Ausgabebus zusammen mit einer anderen Prozessorfamilie ist die Advanced Computing Initiative (ACE). Hier versucht eine Gruppe von über 20 Firmen eine einheitliche Rechnerplattform zu definieren, die vom PC bis zum Grossrechner reicht und mit der existierenden 80X86-Umgebung zusammenarbeiten kann. Als Prozessor ist der R 4000 – ein 64-Bit Risc-Chip von Mips

Computer Systems – vorgesehen, als Ein- und Ausgabebus der Eisa-Bus und alternativ der Turbochannel.

#### Vergleich Eisa-Bus – Microchannel

Ein kurzer Vergleich der wesentlichen Daten ist in Tabelle III dargestellt. Der wesentliche Vorteil des Eisa-Busses ist seine Kompatibilität mit dem ISA-Bus. Jedoch ist eine spätere Erweiterung auf 64 Bit kaum vorstellbar. Der Microchannel hat den Vorteil der Kompatibilität mit dem Vorgängerbus nicht. Vielmehr mussten alle Boards dafür neu entwickelt werden. Dafür kann man sich eine spätere Erweiterung des MCA auf 64 Bit gut vorstellen. Dazu könnten die Adressleitungen im Multiplex betrieben und während eines Datentransfers ebenfalls mit Daten belegt werden. Eine Datenrate von 80 MByte/s wäre damit erreichbar.

#### Anforderungen aus Architektur und Technologie an zukünftige Bussysteme

Sicher wird die Entwicklung der Rechnerbusse mit dem Eisa-Bus nicht zu Ende sein. Die Silizium-Technologie wird weiterhin die Entwicklung auf diesem Gebiet antreiben. Die Verfügbarkeit von 64-Bit-Prozessoren wird sich rasch verbessern, ebenfalls werden die Taktfrequenzen noch zunehmen. Auch Caches8 werden eine zunehmende Verbreitung finden, was sich in zusätzlichen Anforderungen an die Bussysteme niederschlägt. Dasselbe gilt für die Multiprozessorsysteme, die immer mehr aus dem Bereich der Forschung in die praktische Anwendung gelangen. Auch Anwendungsbereiche wie Multimedia und Echtzeit werden zusätzliche Anforderungen mit sich bringen.

#### Literatur

- [1] Krähenbühl F.W.: IBM Micro Channel Architecture Wieso, Wozu. Bull.SEV/VSE 81(1990)17 und 21. S.19ff. und 29ff., 82(1991)1 und 5, S.37ff. und 33ff.

- [2] Färber G. (Hrsg.): Bussysteme Parallele und serielle Bussysteme, lokale Netze. München: Oldenbourg-Verlag 1987, 2. Aufl.

- [3] Solari F.: AT-Bus Design. San Diego: Anna Books, 1990.

- [4] Intel: Datenbuch Peripheral Components, 1991. Kapitel: 82350 Eisa Chip Set.

Das sind kleine, sehr schnelle Zwischenspeicher, die die mittlere Zugriffszeit auf Instruktionen und Daten merklich verkürzen.

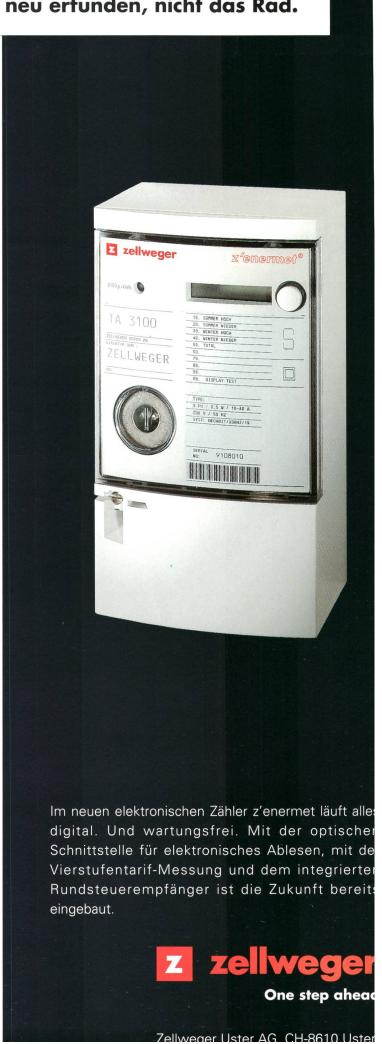

### Wir haben den Stromzähler neu erfunden, nicht das Rad.

nerkömmlichen Zählern rotiert die altbekannte raris-Scheibe, bis sie aufwendig nachkalibriert rden muss. Das eingebaute Register kennt nur und Nachtstrom. Zum Ablesen gibt es nur eine glichkeit: Abschreiben. Aber das ist jetzt gangenheit.

# «Wir sind ganz bei Ihrer Sache.

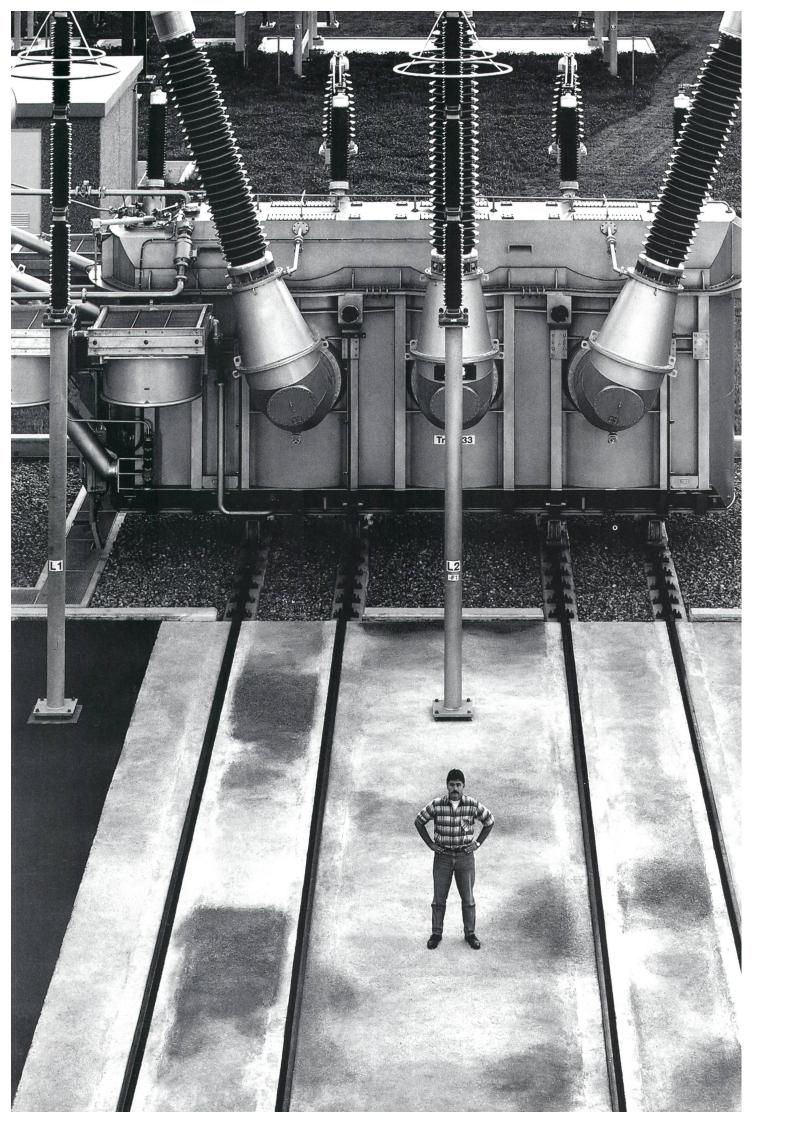

Für mich heisst das, die volle Verantwortung für die mir anvertrauten Anlagen und Objekte übernehmen. Support muss schliesslich etwas mehr sein als nur Service. Damit meine ich das stetige Bemühen um Umweltverträglichkeit. Also zum Beispiel immer weniger Schadstoffausstoss, oder dann die umweltgerechte Entsorgung der PCB-Öle aus Schaltern und Transformatoren. Das meine ich, mit 'volle Verantwortung übernehmen'. Das ist für mich Support!»

S. Wufer

Siegfried Nufer ist Chefmonteur für Neumontagen, Inbetriebsetzungen und Service bei der ABB Hochspannungstechnik AG, Zürich. Er steht auf dem Gelände der 380 kV-Freiluftschaltanlage des Gemeinschafts-Unterwerks Mettlen in Inwil im Kanton Luzern. Hinter ihm steht ein 200 MVA 3-Phasen-Transformator mit 300 Tonnen Gesamtgewicht. Dieser transformiert 380 kV Hochspannung auf 110 kV.

ineltec, Basel 10.-13. Sept. 91 Halle 101, Stand 211

Rittmeyer ist seit 1904 ausschliesslich für die Wasser- und Energiewirtschaft tätig.

Wir entwickeln und fertigen zuverlässige und präzise **Messgeräte** für:

- Durchfluss

- Druck

- Füllstand

- Drehwinkel

Optimal betriebene Wasserkraftwerke, mit einer Wasserhaushalt-Automatik natürlich von...

Unser **RIDAT-Leitsystem** meistert alle Aufgaben zum Führen von technischen Prozessen im automatischen oder manuellen Betrieb. Die Prozessanordnung kann dabei zentral oder dezentral sein.

**Unsere Stärke** sind die umfassenden Prozesskenntnisse in der Wasser- und Energiewirtschaft. Wir liefern **schlüsselfertige Anlagen**

- von der Planung bis zur Realisierung

- vom Messgerät bis zur Leitzentrale

- von der Niederspannungsausrüstung bis zur Prozessdatenverarbeitung

# rittmeyer

#### Schweiz:

Rittmeyer AG Postfach 2143, 6300 Zug 2

#### **Deutschland:**

Rittmeyer GmbH Postfach 1908, 7012 Fellbach

#### Oesterreich:

Rittmeyer Ges.m.b.H. Postfach 69, 1152 Wien