|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 82 (1991)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 5                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | IBM Micro Channel Architecture : wieso, wozu : Teil 4 : Busmaster-Adapter für den Micro Channel                                                                                                                           |

| <b>Autor:</b>       | Krähenbühl, Fred W.                                                                                                                                                                                                       |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-902941">https://doi.org/10.5169/seals-902941</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 20.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# IBM Micro Channel Architecture – Wieso, Wozu

## Teil 4: Busmaster-Adapter für den Micro Channel

Fred W. Krähenbühl

**Im dritten Teil dieser Aufsatzreihe (Heft 1/91) wurde gezeigt, dass die Entwicklung eines einfachen Micro Channel-Adapters sogar dem Amateur gelingen könnte. Dieser vierte Teil befasst sich mit Adapters, die auf dem Busmaster-Prinzip basieren. Diese sehr effizienten Lösungen dürften zwar die Möglichkeiten von Amateuren überschreiten, kleineren und mittleren Unternehmen aber bieten auf dem Markt erhältliche Chips durchaus Chancen, leistungsfähige Busmaster-Zusatzgeräte für PS/2, Risc System/6000 und andere Computer von gleicher Architektur zu entwickeln.**

**Le troisième article de cette série (bulletin 1/91) a montré que même un amateur pouvait parvenir à développer un adaptateur Micro Channel de faible complexité. Le présent chapitre traite des cartes adaptateurs «bus master». Solutions très efficaces, elles dépassent sans doute les capacités d'un amateur, mais les «puces» disponibles sur le marché offrent même aux petites entreprises des chances réelles de mettre au point de puissants dispositifs optionnels «bus master» pour PS/2, Risc System/6000 ou d'autres ordinateurs ayant la même architecture.**

### Adresse des Autors

Fred W. Krähenbühl, IBM Schweiz AG, General Guisan-Quai 26, 8022 Zürich

Wie bereits im ersten und zweiten Teil dargelegt, kann ein Hauptprozessor eines Computers wirksam entlastet werden, indem Teile der Arbeit durch parallel laufende Subsysteme mit eigenen Prozessoren ausgeführt werden. Diese Subsysteme sollen unter direkter Kontrolle des im Hauptsystem laufenden Programms, d.h. der jeweiligen Anwendung stehen. Je unabhängiger vom Hauptsystem nun aber ein Subsystem arbeiten kann, desto effizienter arbeitet das Gesamtsystem.

Als Beispiel diene noch einmal die Ausgabe von Daten auf eine Harddisk. Der Hauptprozessor legt die zu schreibenden Daten im eigenen Hauptspeicher ab und erteilt dem Subsystem den Auftrag, die Daten dort abzuholen und sie korrekt auf der Harddisk zu versorgen, eine allfällige Fehlerbehandlung durchzuführen und dem Hauptsystem zum Ende der Operation den Erfolg zu melden (ausgeführt, nicht ausgeführt, Grund des allfälligen Problems).

Um diese Aufgaben erfolgreich zu bewältigen, müssen folgende Komponenten vorhanden und folgende Voraussetzungen gegeben sein:

- Ein Adapter mit Busmaster-Fähigkeit, der Daten selbständig über den Kanal transferieren kann. Er muss mit eigener Intelligenz ausgerüstet sein, damit der Verkehr mit der Außenwelt unabhängig und fehlerlos ablaufen kann. Mit anderen Worten: Auf dem Adapter muss im Normalfall ein vollständiger, eigener Mikrocomputer mit Prozessor und Speicher, mit Ein- und Ausgabe-Ports vorhanden sein.

- Ein Protokoll, welches den Verkehr zwischen dem Hauptsystem und dem Busmaster-Adapter (physisch und logisch) regelt. Im Fall der IBM Micro Channel-Architektur wird

«Subsystem Control Block Architecture» (SCBA) verwendet (s. Teil 2).

Die Konzepte, welche einen Busmaster-Adapter in einem Micro Channel-System zu seiner vollen Leistung bringen können, sind komplex. Teile der Architektur sind denn auch in integrierten Schaltungen implementiert worden, damit die Entwicklungsarbeit der Hersteller ein vernünftiges Mass nicht übersteigt.

Bis heute haben sich zwei Firmen, Intel und Chips & Technologies, mit der Entwicklung von integrierten Schaltungen, welche auf den Hard- und Software-Architekturen aufbauen, befasst. Diese sollen, zumindest als Samples, im ersten Halbjahr 1991 erhältlich sein. Beide Chips verhelfen einem Adapter zur Busmaster-Fähigkeit, beide unterstützen SCBA. Sie tun dies auf etwas unterschiedliche Art und Weise, und entsprechend unterschiedlich sind ihre Anwendungsbereiche.

Im folgenden werden die Resultate aus einer gemeinsamen Studie mit dem IBM-Entwicklungslabor dargelegt, bei der es in erster Linie darum ging, mögliche Schaltungstechniken für den Einsatz des von IBM und Intel gemeinsam entwickelten Intel-Chip-Satzes kennenzulernen. Die Beschreibungen entsprechen ungefähr dem Dokumentationsstand von Mai 1990 und können demnach für die endgültigen Chips noch einige Abweichungen erfahren.

### Der Chip-Satz 82325 von Intel

Der Chip-Satz Intel 82325 besteht aus zwei Modulen: dem Intel 82325MD, der sich hauptsächlich mit dem Datenfluss befasst und dem Intel 82325MC, welcher die meisten Kontrollsignale produziert. Die beiden Chips können nur als Satz verwendet

werden. Dieser wird im folgenden mit «82325» bezeichnet. Der 82325 unterstützt nicht nur den Verkehr mit und über den Micro Channel, sondern auch zum Adapter gehörige Logiksysteme, deren Nutzung vom Adapterhersteller zu definieren ist. Diese lokale Logik kann beispielsweise einen der Prozessoren Intel 80186, 80376 oder 80386SX enthalten. Der Intel 82325 besitzt die folgenden Hauptcharakteristika:

– Bezuglich des Micro Channels: POS-Unterstützung (alle Register in-

tegriert), Unterstützung von Ein-/Ausgabe- und Speicher-Befehlen (Slave Operation), Busmaster-Fähigkeit, 2 verschiedene Interrupt-Linien, Einsatzfähigkeit in 16- oder 32-Bit-Maschinen in der jeweiligen Datenbreite, Adressen- und Daten-Paritätsprüfung, Streaming Data Protokoll (100 ns Zyklus-Zeit, max. 40 MByte/s Transfergeschwindigkeit), SCBA-Register in Hardware.

– Bezuglich lokaler Mikroprozessoren: Direkt-Ansprechfähigkeit von Intel 80186 und 80376/80386SX, Busma-

ster-Fähigkeit, Fähigkeit zum selbstständigen Transfer von bis zu 16 MByte über den Kanal, paralleler Bypass-Bus, Interrupt, interne Fehlererkennung.

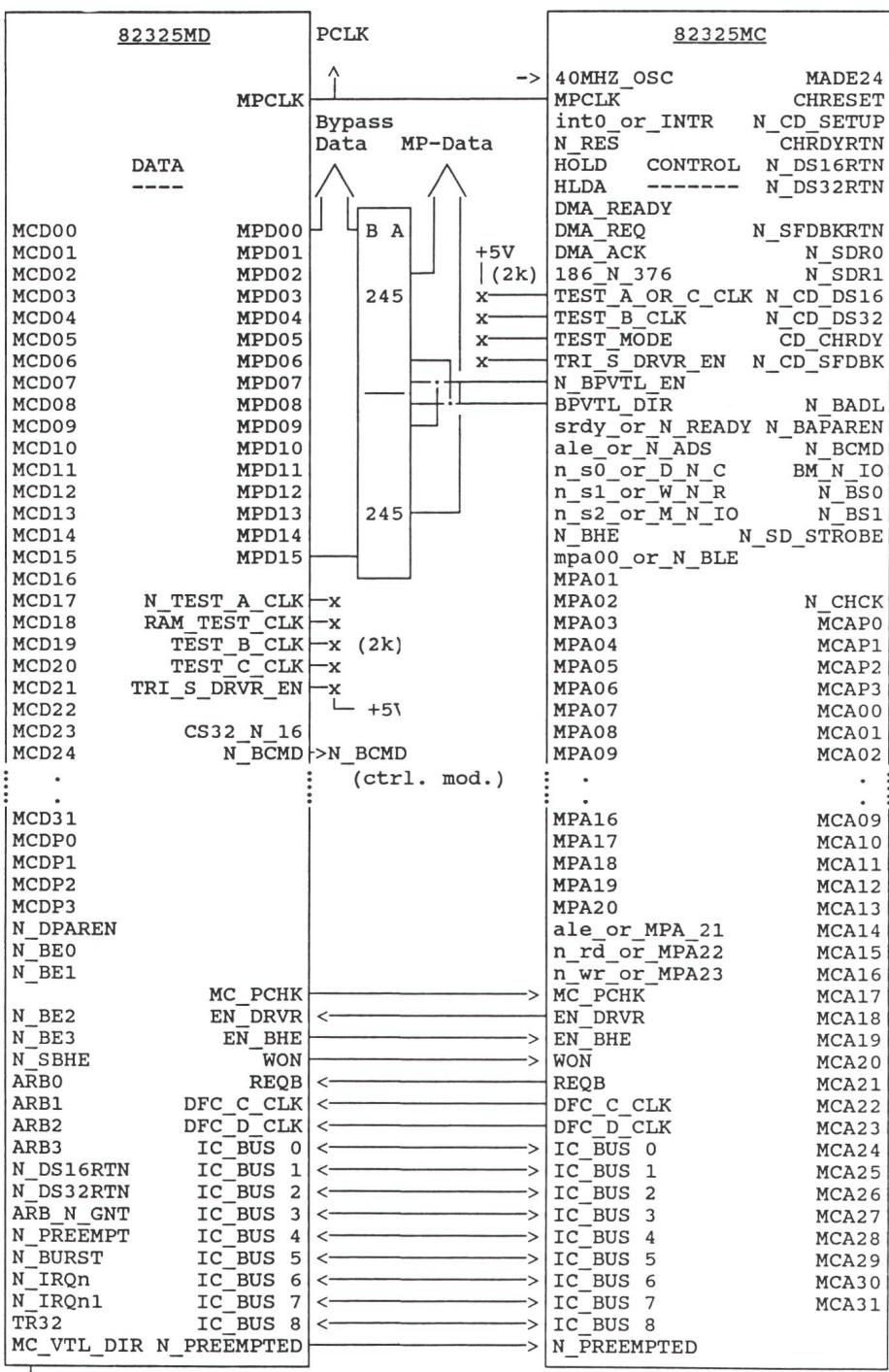

## Die logischen Anschlüsse des 82325MD

Bild 33 a zeigt die Grundschaltung für die Verwendung des Chipsatzes 82325 auf einem Busmaster-Adapter, Bild 33 b ein Teilsystem davon. Ihre Funktionsweise wird weiter unten besprochen. Wir konzentrieren uns vorerst auf die beiden Intel-Chips. Auf der linken Seite des Chips 82325MD sind die Anschlüsse zum Micro Channel zu sehen, rechts die Anschlüsse zu den Komponenten des lokalen Mikroprozessors. Alle Anschlüsse, welche mit N- (für NOT-) beginnen, sind aktiv low, die anderen aktiv high.

### Micro Channel-Anschlüsse

Im folgenden werden nur jene Anschlüsse und Signale besprochen, welche nicht schon in einer früheren Folge dieses Beitrags behandelt oder aus den technischen Handbüchern von Micro Channel-Maschinen im Detail bekannt sind. Jedes Daten-Byte hat sein eigenes Paritäts-Bit, MCDP0...MCDP3. N-DPAREN aktiviert bei jeder Übertragung über den Micro Channel die Generierung und Prüfung der Parität. N-IRQn und N-IRQn1 sind zwei Anschlüsse, welche mit irgendwelchen zwei Interrupt-Leitungen des Micro Channels verbunden werden können. MC-VTL-DIR (Micro Channel Vendor Transistor Logic Direction-Signal) liefert die Richtungskontrolle für einen notwendigen externen '245 Puffer-Baustein.

### Anschluss an die Bausteine des lokalen Prozessors

Die Anschlüsse auf der rechten Seite des Intel 82325MD (Bild 33 a) dienen in erster Linie dem Verkehr mit dem lokalen Mikroprozessor. Neben den 16 Datenleitungen MPD00...MPD15 ist der Signalausgang MPCLK zu erwähnen, welcher dem Mikroprozessor das Taktsignal liefert und so die Arbeit des 82325 mit dem lokalen Prozessor synchronisiert. Die nach unten folgenden fünf Signale dienen der Prüfung während des Herstellprozesses; sie bleiben im Normalbetrieb unbenutzt und werden über Widerstände auf +5 V gesetzt.

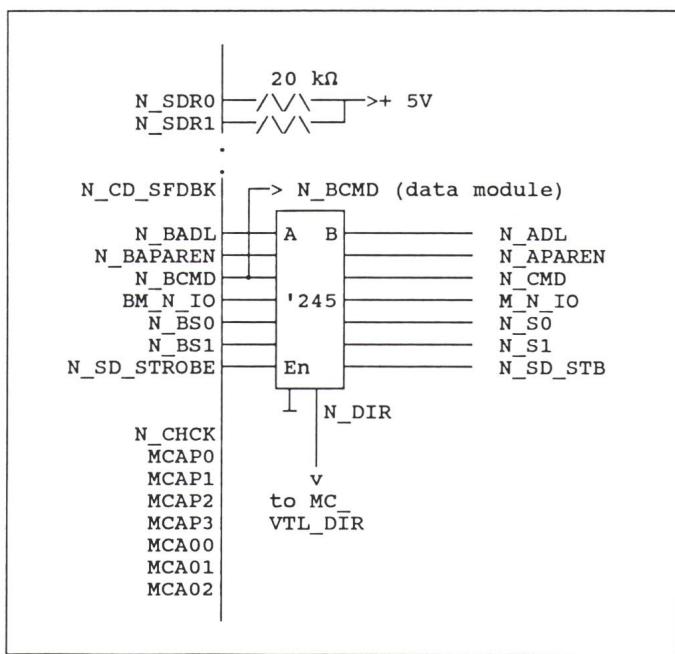

–BCMD entspricht –CMD des Micro Channels und ist eines der gepuf-

Bild 33a Der Chipsatz 82325 in seiner typischen Schaltungsumgebung

**Bild 33b**

Teilschaltung

von 33a

Die Signale sind in

Bild 35 näher

beschrieben

ferten Signale (Bild 33 b). Das Signal CS32-N-16 wird im folgenden Abschnitt eingehend erläutert. Der Interchip-Bus besteht aus 17 Leitungen und dient der Verbindung mit der Partner-Schaltung 82325MC. Alle Pins werden mit den Anschlüssen gleichen Namens verbunden.

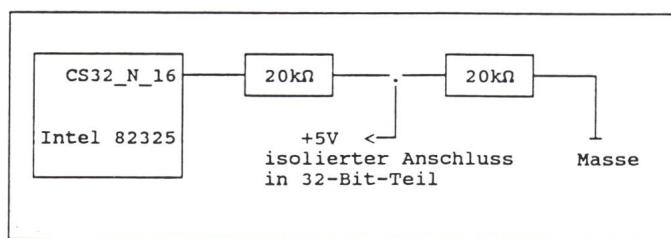

Ein Adapter kann so aufgebaut werden, dass er sowohl in einem Steckplatz für 16 Bit, als auch in einem solchen für 32 Bit arbeiten kann. Dazu wird erstens die Karte mit einer Aussparung so konstruiert, dass sie in beide Steckerarten eingepasst werden kann und zweitens auf der Karte Logik zugesetzt, welche die momentane Steckerart feststellen und eine entsprechende Verarbeitung initiieren kann. Ein Low- bzw. High-Level-Signal am Eingang CS32-N-16 teilt dem 82325MD mit, ob die Karte einen 16- oder einen 32-Bit-Steckplatz besetzt. Eine mögliche Schaltung zur Erzeugung dieses Signals zeigt das Bild 34. Ein Beispiel für einen Adapter mit 32-Bit- und 16-Bit-Anschlussfähigkeit ist der 32-Bit-SCSI-Adapter mit Cache von IBM.

## Die logischen Anschlüsse des Intel 82325MC

Wie bereits gesagt, ist der zweite Baustein des Intel-Satzes, der 82325MC, für die Erzeugung der mei-

35 näher beschrieben werden. Diese 7 müssen gepuffert werden. Für je 8 Bit der Adressleitungen kann mittels MCAP0... 3 bei jedem Kanal-Transfer die Parität überprüft werden. Mit N-APAREN (N-BAPAREN) lässt sich diese Funktion ein- und ausschalten.

### Anschluss an die Bausteine des lokalen Prozessors

Auf der linken Seite des Chips 82325MC sind die Verbindungen zum lokalen Prozessor zu sehen. Der 82325MC benötigt zwei Taktsignale. Das erste, 40 MHz, liefert den Grundtakt. Das zweite, MPCLK, ist wie oben bereits erwähnt, das Taktsignal für den auf dem Adapter verwendeten Mikroprozessor und dient zudem der Synchronisation der beiden Chips.

Der Intel 82325 kann direkt mit einem von zwei Prozessoren, dem Intel 80186 oder dem Intel 80376 (somit auch 80386SX) verkehren. Zur Unterscheidung der beiden Prozessoren wird der Anschluss 186-N-376 an Masse ('376), oder an +5 V ('186) gelegt. Daurch wird die Bedeutung einiger Anschlüsse verändert. Im Bild 36 ist in Kleinbuchstaben die Bedeu-

**Bild 34**

Erkennung des

Steckplatztyps

sten Kontrollsignale verantwortlich. Im folgenden werden seine wichtigsten Signalanschlüsse beschrieben.

### Micro Channel-Anschlüsse

Die logischen Verbindungen zum Micro Channel sind in Bild 33 a auf der rechten Seite des entsprechend beschrifteten Schaltungsblocks zu sehen, wobei 7 Signale in Bild 33 b und

tung beim Betrieb mit einem 80186, in Grossbuchstaben jene für den Betrieb mit einem 80376 genannt. Grossbuchstaben werden auch dort verwendet, wo ein Signal für beide Prozessoren identisch ist. Weitere Information über die Signale der Intel-Schaltungen können den jeweiligen Datenblättern entnommen werden.

## Integration des 82325 in ein Gesamtsystem

Um die beiden Chips unter sich und mit ihrer Aussenwelt (Micro Channel und Mikroprozessor) zusammenzuschalten, muss folgendes beachtet werden: Der Signalaustausch zwischen dem 82325 und dem Micro Channel muss für 7 Signale gepuffert werden, was mit einem '245-Baustein

**Bild 35**

Signale auf der

Micro Channel-

Seite des Intel

82325MC

Diese Signale

müssen gepuffert

werden

| Signal am 82325MC                                                         | Micro Channel                                                    | Bedeutung                                                                                                                                                 |

|---------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| N_BADL<br>N_BAPAREN<br>N_BCMD<br>BM_N_IO<br>N_BS0<br>N_BS1<br>N_SD_STROBE | N_ADL<br>N_APAREN<br>N_CMD<br>M_N_IO<br>N_SO<br>N_S1<br>N_SD_STB | Address Decode Latch<br>Address Parity Enable<br>Command<br>Memory- oder I/O-Zyklus<br>Status Bit 0<br>Status Bit 1<br>Strobe für Streaming Data-Prozedur |

| Signal-Name                                                                                                               | Bedeutung                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| intr_0 / INTR                                                                                                             | Das Signal ist high, wenn der 82325 beim Mikroprozessor einen Interrupt-Service verlangt.                                                                                                                                                         |

| N_RES                                                                                                                     | Das Signal kann benutzt werden, um das Mikroprozessorsystem in die Grundstellung zu bringen (RESET).                                                                                                                                              |

| HOLD                                                                                                                      | 82325 verlangt die Kontrolle über den Bus.                                                                                                                                                                                                        |

| HLDA                                                                                                                      | Der Mikroprozessor hat den Bus abgegeben (Hold Acknowledge).                                                                                                                                                                                      |

| DMA_READY                                                                                                                 | Wenn Daten bereit oder akzeptiert sind, wird das Signal durch einen implizit adressierten I/O-Port gesetzt (Bypass Bus).                                                                                                                          |

| DMA_REQ                                                                                                                   | DMA_REQ wird durch einen implizit adressierten I/O Port gesetzt, um vom 82325 Daten anzufordern (Bypass-Bus).                                                                                                                                     |

| DMA_ACK                                                                                                                   | Der 82325 setzt das Signal, um einen DMA_REQ zu bestätigen (Bypass Bus).                                                                                                                                                                          |

| N_BPVTL_EN<br>BPVTL_DIR                                                                                                   | Diese Signale werden durch 82325 gesetzt und schalten den Datenpfad vom Mikroprozessor zum Bypass Bus.                                                                                                                                            |

| srdy / N_READY                                                                                                            | Ende des Uebertragungs-Zyklus                                                                                                                                                                                                                     |

| ale / N_ADS                                                                                                               | 186-Modus: Signal zur Pufferung der Adressen und Kontrollsignale<br>376-Modus: Gültige Adresse, Zyklus-Definition                                                                                                                                 |

| n_s0 / D_N_C<br>n_s1 / W_N_R<br>n_s2 / M_N_IO                                                                             | Im 186-Modus definieren die Signale den Bus-Zyklus, im 376-Modus werden Daten- von Kontroll-Zyklen (D/N_C), Schreib- von Lese-Zyklen (W/N_R), sowie Ein-/Ausbabe- von Speicher-Operationen (M/N_IO) unterschieden.                                |

| N_BHE<br>mpa00 / N_BLE                                                                                                    | N_BHE signalisiert die Uebertragung eines Byte über die hoherwertigen 8 Bit des Bus. N_BLE bedeutet im 376-Modus die Aktivierung der niedrigewertigen 8 Datenleitungen, während im 186 Modus mpa00 das niedrigstwertige Adress-Signal vermittelt. |

| MPA01 - MPA15                                                                                                             | Im 186-Modus vermitteln diese Anschlüsse zusammen mit MPD01...MPD15 die Adressen und Daten der in Zeitmultiplex arbeitenden AD01 ...AD15. Im 376-Modus übertragen sie die niedrigewertigen Adressbits.                                            |

| MPA16 - MPA20                                                                                                             | In beiden Modi: Adressbits 16..20                                                                                                                                                                                                                 |

| ale / MPA_21                                                                                                              | 186-Modus: Eingabe: Address Latch Enable<br>376-Modus: Adress-Bit 21                                                                                                                                                                              |

| n_rd / MPA22                                                                                                              | 186-Modus: Definition eines Lese-Zyklus<br>376-Modus: Adressbit 22                                                                                                                                                                                |

| n_wr / MPA23                                                                                                              | 186-Modus: Definition eines Schreib-Zyklus<br>376-Modus: Adressbit 23                                                                                                                                                                             |

| Alle weiteren Signale sind für den lokalen Verkehr der beiden 82325-Teilschaltungen oder für Fabrikations-Tests bestimmt. |                                                                                                                                                                                                                                                   |

Bild 36 Pin-Definitionen für den 82325MC

(Bild 33 b) realisiert werden kann. Dabei liefert der 82325 das nötige Richtungssignal. Das Enable-Signal wird an das 0-Potential gelegt und ist damit immer aktiv. Der Bypass-Bus und der Datenteil des lokalen Mikroprozessor-Busses können durch ein Paar von '245-Bausteinen voneinander isoliert werden (s. Bild 33 a und nächster Abschnitt). Die Testsignale werden über 2 k an +5 V gelegt und

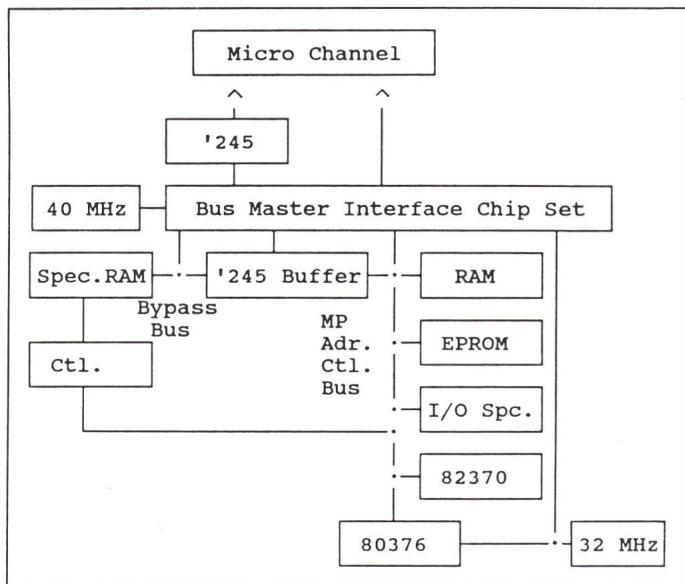

die Anschlüsse des Interchip-Busses verbunden. Damit kann man die typische Busmaster-Schaltung von Bild 37 aufbauen.

## Einige wichtige Entwicklungskriterien

Die Darstellung von Bild 37 zeigt eine typische Implementation eines Busmasters unter Einsatz des 82325

Chipsatzes und eines 80376-Prozessors. Wie bei den meisten Mikroprozessor-Bus-Systemen ist der Prozessor direkt mit seinem EPROM, dem RAM und dem Ein-/Ausgabe-Interface verbunden. Solange kein speziell schneller Datenweg vom Micro Channel zum Ausgabe-Gerät benötigt wird, ist nichts Spezielles an der Verbindung des Mikroprozessor-Busses mit dem 82325 zu vermerken. In diesem Normalfall werden keine Komponenten, welche eine der Bezeichnungen »'245 Buffer«, »Bypass Bus«, »Spec. RAM« oder »Ctl.« tragen, implementiert. Neben dem normalen Datenweg über den lokalen Mikroprozessor-Bus unterstützt nun aber der 82325 einen sogenannten Bypass Bus, einen sehr schnellen, direkten Datenpfad zwischen dem Micro Channel und der Peripherie, der unter Umgehung des Adapter-Mikroprozessors durchgeschaltet werden kann. Dieser Bypass-Bus besteht nur aus den Datenleitungen, im Gegensatz zum normalen Datenweg, der über die bekannte Busstruktur des Mikroprozessors führt. Der Benutzer kann den Datenweg durch Programmierung entsprechender Register im 82325 anwählen, worauf dieser die nötigen Signale an die Pufferschaltungen ausgibt. Sind die Puffer (245) in hochohmigem Zustand, können keine Daten zum Mikroprozessor fliessen. Sie werden zu irgend einem anderen Geräteteil umgeleitet (z.B. zu einem schnellen Zwischenspeicher, wenn der Adapter eine Harddisk kontrolliert). Da für diese Operation weder über den Adressnoch den Kontrollbus zugegriffen werden kann, muss die Kontrollfunktion auf andere Weise bewältigt werden. Der 82325 kennt für diesen Zweck drei Kontroll-Leitungen, DMA-REQ, DMA-ACK und DMA-READY. Mit ihnen wird der Transfer zwischen dem direkten Ein- oder Ausgang und dem 82325 gesteuert. Die Anzahl der zu übertragenden Zeichen muss durch externe Zähler, welche vor dem Transfer zu laden sind, kontrolliert werden.

Ein interessantes Detail des Bypass-Busses besteht darin, dass der lokale Mikroprozessor des Adapters während des Transfers mit seinem eigenen Programm weiterfahren kann. Die Datenlinien der beiden Bus-Strukturen sind ja voneinander isoliert. Damit ist ein sehr schneller direkter Datentransfer vom Speicher des Hauptsystems über den Micro Channel zur Peripherie und umgekehrt möglich

**Bild 37**

Blockschema eines mit Hilfe des 82325-Chipsatzes aufgebauten Micro Channel-Bus-master-Systems

Die Schaltung enthält einen 80376-Prozessor sowie einen 82370 Peripherie-Baustein

(leider sprechen die Handbücher auch hier von DMA), während der Mikroprozessor gleichzeitig langsamere Ein-/Ausgaben erledigen kann.

Eine etwas detailliertere Beschreibung des hypothetischen Beispiels aus dem ersten Teil dieses Beitrags mag den Nutzen noch einmal verdeutlichen: Man nehme an, dass ein Busmaster-Adapter innerhalb einer Audio-Vision-Applikation eingesetzt werde. Es seien zwei Datenpfade zu zwei verschiedenen Ausgabe-Medien nötig: einerseits synthetisiere der Adapter Sprache aus Text, andererseits sollen Bilder auf einen Bildschirm gegeben werden. Ein gesprochener Text belegt in seiner schriftlichen Form vielleicht 10 Zeichen pro Sprechsekunde, eine sehr kleine Datenmenge. Anders bei Bildern. Hier sind Hunderttausende von Bytes nötig, um auch nur ein einziges stehendes Bild mit einiger Auflösung auf den Bildschirm zu bringen. In einer ersten Phase kann der Busmaster nun den Sprachtext aus dem Speicher des Hauptsystems holen und beginnen, die Laute zu synthetisieren, den Satz auszusprechen. Während der Sprechzeit benötigt die Schaltung keine Micro Channel-Verbindung zum Hauptsystem. Dies eröffnet die Möglichkeit, den 245er-Puffer in den hochohmigen Zustand zu bringen und damit den direkten Datenweg vom Speicher des Hauptsystems zum Speicher des Videoteils nutzbar zu machen. Da weder der Prozessor des Hauptsystems, noch derjenige des Busmaster-Adapters an der Übertragung beteiligt ist, gehört dieser Transfer mit zum Schnellsten, was ein Micro Channel-System offe-

riert kann. Bei Verwendung des 82325 lässt sich die Transfergeschwindigkeit auf maximal 40 Mio. Zeichen pro Sekunde steigern, sofern der (Speicher-)Partner diese Geschwindigkeit verkraften kann.

Ein interessantes Detail der Micro Channel-Architektur: Da Geschwindigkeit und Übertragungsart nicht durch den Kanal vorgegeben sind, sondern von den beteiligten Partnern von Fall zu Fall festgelegt werden, richtet sich der Modus immer nach dem schwächeren der beiden Partner. Ein Adapter, der 40 Mio. Zeichen pro Sekunde übertragen kann, wird seine volle Kraft also erst dann entfalten können, wenn sein Partner dieselben Fähigkeiten hat. Zurück zum Beispiel: Der erklärende Satz zum Video-Bild ist noch nicht ausgesprochen, da erscheint das zugehörige Bild bereits auf dem Bildschirm. Ein Beispiel, das aufzeigt, wo die eigentlichen Vorteile eines Micro Channel-Systems zu suchen

sind. Jeder Leser wird weitere eigene Anwendungen finden.

Dies und die folgenden Detailbeschreibungen zeigen eines sehr klar: Die Entwicklung eines Busmaster-Adapters für den IBM Micro Channel liegt trotz der hohen Komplexität und trotz der erreichbaren Leistung nicht mehr jenseits der Möglichkeiten eines kleinen oder mittleren Betriebes, da die komplexen Funktionen für den Verkehr mit dem Kanal einerseits und mit dem Bus des Mikroprozessors andererseits vollständig in den Chip-Satz Intel 82325 integriert sind. Der grösste Teil der Entwicklung ist bereits erledigt und der Hersteller kann sich mit den Funktionen, die sein Adapter für die Anwendung zu leisten hat, befassen.

## Technik des Adapter-Entwurfs

Als Ergänzung zur vorhergehenden Information über die Funktionsprinzipien werden im folgenden einige Techniken vorgestellt. Diese sollen zeigen, wie die Komponenten zusammengeschaltet werden können. Die Beispiele sind einer Anwendungsentwicklung mit dem Intel 80376 und seinen Partner-Chips entnommen. Die Kenntnis der Chips wird vorausgesetzt; es werden deshalb nur «Spezialitäten» im Zusammenhang mit dem Intel 82325 behandelt.

### Clock und Reset

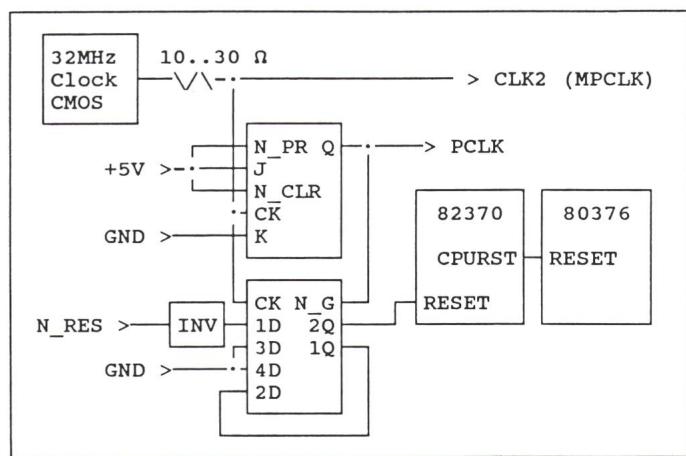

Das Bild 38 zeigt die Schaltung eines Taktgebers, welche von Intel für den Prozessor 80386 und seine Derivate (wie den 80376) vorgeschlagen wird. Die Schaltung findet sich in Intels 80386 Hardware Reference Manual [4]. Anstatt des dort vorgeschlagenen manuell ausgelösten Rücksetz-Impulses wird hier allerdings das in-

**Bild 38**

Taktgeber für die 80386-Prozessorfamilie

vertierte N-RESET Signal des 82325, welches die Länge eines Reset-Impulses des Micro Channels (100 ms) hat, verwendet. Der Rücksetz-Impuls, der an den 82370 geliefert wird, hat die richtige Länge, um eine korrekte Phasen-Abhängigkeit zwischen PCLK und CLK2 sicherzustellen. Der 82370 wird dann eine eigene Rücksetzung für die 80376 mit einer Dauer von 62 CLK-Impulsen generieren. Das ist zwar genug für einen Reset, aber zuwenig, wenn auch noch eine Selbstprüfung ablaufen muss. Will man diese Möglichkeit ebenfalls nützen, ist die Schaltung entsprechend zu ändern.

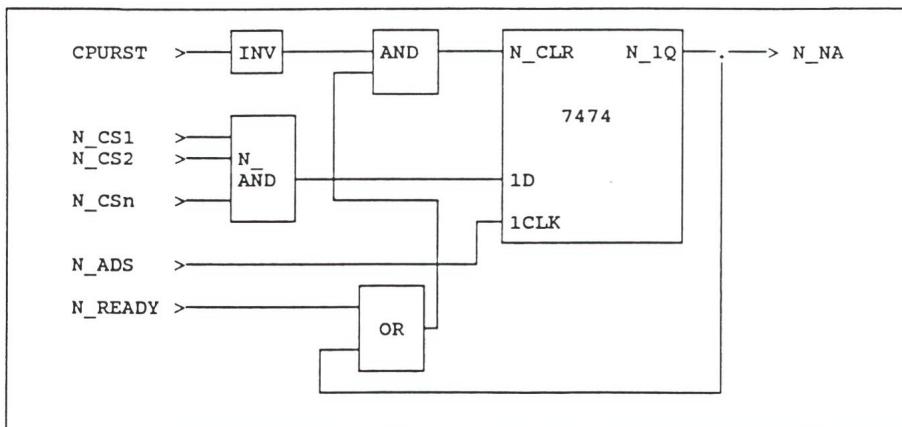

## Erzeugung des Next-Address-Signals

Das Signal N-NA (Next Address) muss bei Verwendung von Pipelining mit dem 80376 generiert werden. N-NA teilt dem System mit, dass die Adresse des laufenden Zyklus nicht mehr länger benötigt wird und, dass jene des nächsten Zyklus geliefert werden kann (Pipelining). Wird das Signal innerhalb eines Zyklus nicht zu einem spätesten Zeitpunkt aktiv, läuft der nachfolgende Zyklus ohne Pipelining ab.

Die nicht gespeicherten (non latched) Chip Selects werden zur Bildung des Signals herangezogen. Die Zyklus-Definition lässt zu, dass N-NA während allen Stadien eines Zyklus gültig ist. Daher kann die Steuerung zwischen der steigenden Flanke von N-ADS und der fallenden Flanke von N-READY erfolgen. Das ist, wie Bild 39 zeigt, mit einer einfachen Schaltung erreichbar. Der Intel 82325 generiert kein Pipelining, kann aber beiden Zyklus-Arten auf dem Mikroprozessor-Bus folgen. Sollten Zeitprobleme auftauchen, so sind sie mit (zusätzlichen) Wartezyklen zu eliminieren.

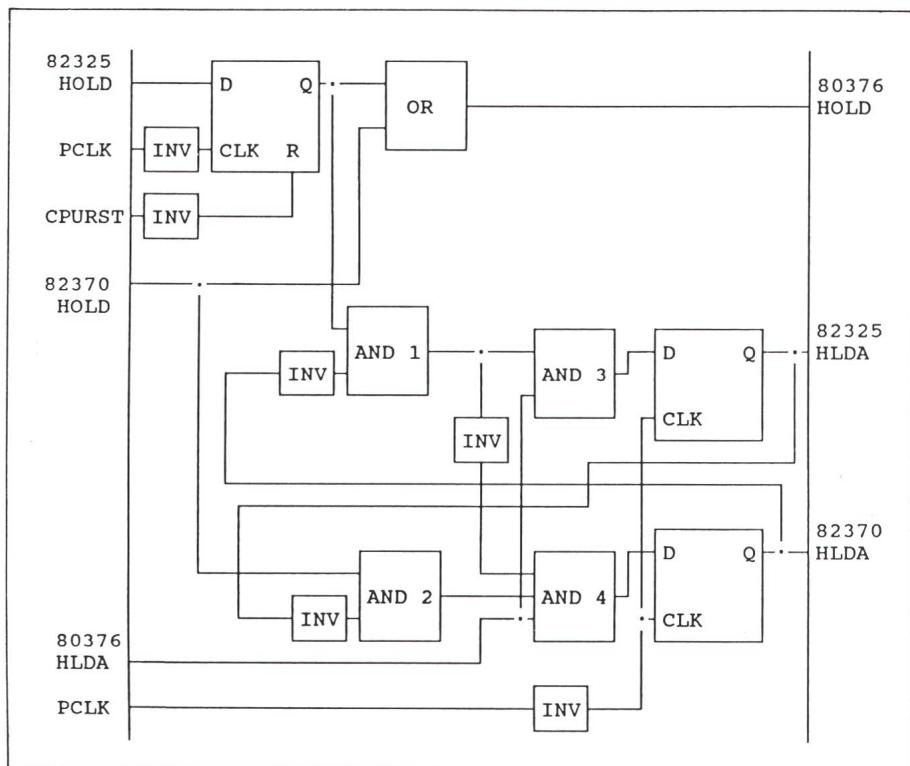

Bild 40 Kaskadierung der Bus-Anforderung

## Busmaster auf dem Mikroprozessor-Bus

Jeder der wichtigen integrierten Bausteine (82325, 80376, 82370) kann als Busmaster arbeiten, wobei selbstverständlich zu einem gegebenen Moment nur eine der Komponenten den Bus besitzen kann. Der Prozessor 80376 wird mittels des HOLD-Signals zur Aufgabe des Busses aufgefordert. Er setzt seine Leitungen zu einem definierten Zeitpunkt in den hochohmigen Zustand und liefert HOLD (Hold Acknowledge) als Quittung, dass der Bus gebraucht werden darf. Der 82325 wird den Bus auf die oben beschriebene Weise anfordern. Wird der Peripheriebaustein 82370 nicht benutzt, können die HOLD und

HOLD-Aanschlüsse des 82325 direkt mit den gleichnamigen Pins des 80376 verbunden werden. Da aber der 82370 die gleiche Anforderungs-Methode wie der 82325 benutzt, ist bei gleichzeitiger Verwendung von beiden in einer Schaltung eine Kaskadierung der Bus-Anforderung vorzusehen.

Das Bild 40 zeigt, wie die Schaltung aufgebaut werden kann. Dabei sind folgende drei Szenarien zu unterscheiden:

1. Intel 82325 verlangt den Bus: Der Chip setzt sein HOLD-Signal auf High. Der 80376 verzichtet auf den Bus und setzt als Quittung HLDA auf High. Falls keine Busanforderung des 82370 vorliegt, gelangt die HOLD-Anforderung an ein D-Latch, welches die Quittung für den 82325 (HLDA) generiert.

2. Intel 82370 (Interface Controller) verlangt den Bus: Der 82370 setzt sein HOLD auf high und veranlasst damit den 80376, sobald wie möglich HLDA als Quittung auf high zu setzen. Da der 82325 den Bus nicht benötigt, wird jetzt das HLDA für den 82370 generiert.

3. 82325 und 82370 verlangen den Bus gleichzeitig: Da beide HOLD-Anforderungen auf high stehen, wird der 80376 HLDA erzeugen. Die invertierte Ausgabe von AND 1 an AND 4 ergibt eine Priorität des 82325 über

Bild 39 Erzeugung des Next-Address-Signals

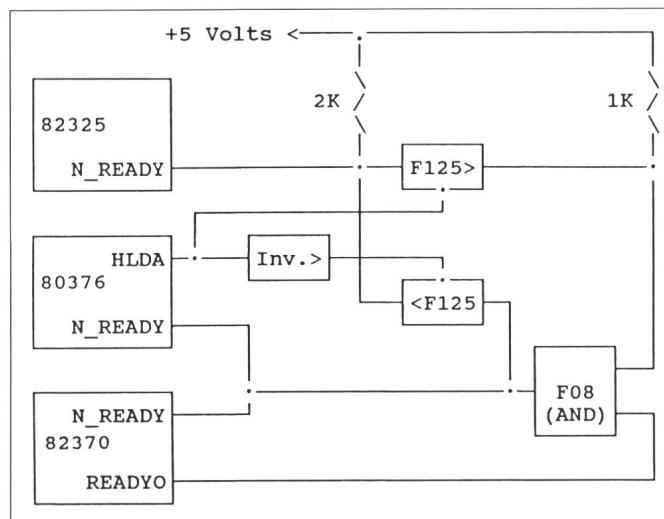

**Bild 41**

Rückmeldung

Zyklus-Ende

den 82370. Somit kommt die zweite Schaltung erst zum Zuge, nachdem der 82325 die Übertragung abgeschlossen hat. Die umgekehrte Priorität ist durch eine ähnliche Schaltung erreichbar. Das wird zum Beispiel dann nötig sein, wenn der 82370 für den Refresh von Adapter-Speicher eingesetzt wird.

#### Wartezyklen

N-READY ist das Signal, mit dem ein Partner dem Initianten eines Transfers die Beendigung seines Auftrages und damit die Möglichkeit zur Beendigung des Zyklus anzeigt. Jede angesprochene Komponente auf dem Bus muss dieses Signal generieren, um zu verhindern, dass das System endlos Wartezyklen einsetzt und hängen bleibt. Die Komponenten (Bild 41) erzeugen N-READY auf unterschiedliche Weise: Der 82325 hat eine bidirektionale Leitung mit offenem Kollektor, während der 82370 separate Leitungen für den Eingang (N-READY) und den Ausgang (READY0) aufweist. Der 80376 braucht natürlich nur einen Eingabeanchluss (N-READY). Alle N-READY-Linien können grundsätzlich zusammengeschaltet werden. Um sicherzustellen, dass die Impulse zum richtigen Zeitpunkt, auf dem richtigen Level in die korrekte Richtung laufen, können zwei Pufferschaltungen (z.B. 74F125), durch das HLDA-Signal des 80376 Prozessors kontrolliert, eingesetzt werden. Zwei Widerstände und ein AND-Tor ist das einzige, was zusätzlich benötigt wird.

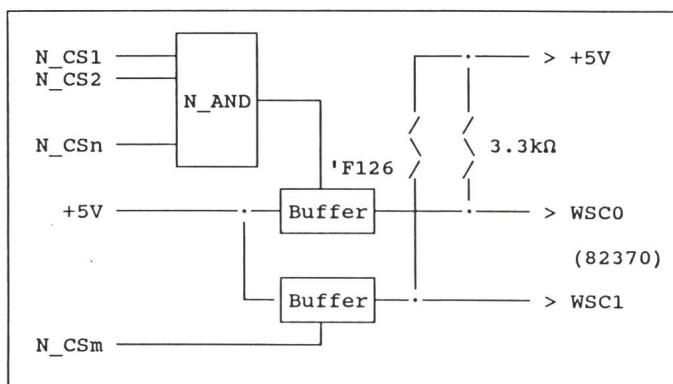

Der 82370 hat einen integrierten Wartezyklen-Generator. Verschiedene programmierbare Zähler kontrollieren die Zyklen (0...15) für die verschiedenen Komponentenarten. Die

Linien WSC0 und WSC1 wählen einen von drei Levels aus, während M/N-IO verschiedene Zyklus-Zahlen für Speicher- bzw. Ein-/Ausgabe Operationen selektieren. Der vierte Level (WSC0 = WSC1 = 1) setzt den Generator ausser Betrieb.

In der gewählten Steuerschaltung (Bild 42) ist der Generator ohne Ansteuerung ausser Betrieb, da die beiden Eingänge WSC0/1 über 3,3 k an +5 V und damit an hohem Potential liegen. Dies ist erlaubt, da der 82325 die N-READY-Linie direkt ansteuert und der 82370 in diesem Fall keine Wartezyklen zu generieren braucht. Wenn eines der Chip Select-Signale aktiv (low) ist, wird auch die entsprechende WSCn-Leitung aktiv. Einer der Level 1 oder 2 des 82370-Generators wird damit ausgewählt und die dort gespeicherte Anzahl der Wartezyklen wird eingesetzt. Ein automatisches Ausschalten des Generators durch Pull-up-Widerstände sollte nur dann vorgesehen werden, wenn im lokalen Mikroprozessor-System keine dynamischen Speicher verwendet werden, da sonst die interne Schaltung für den Refresh ebenfalls ausser Betrieb gesetzt wird.

#### Erster Vergleich mit den Spezifikationen des 82C614 von Chips and Technologies Inc.

Wie bereits mehrfach erwähnt, bringt Chips and Technologies ebenfalls eine zusammen mit IBM entwickelte integrierte Schaltung auf den Markt. Auch sie soll die Entwicklung von Busmaster-Adaptoren vereinfachen, wenn auch in etwas anderer Weise als der Intel Chip-Satz. Einige Schlüsselpunkte – sie entstammen einem Referat – sind im folgenden dargestellt.

Der wohl wesentlichste Unterschied zur Entwicklung von Intel liegt in der Tatsache, dass der C&T-Chip für eine Datenbreite von 16 Bit ausgelegt ist. Damit ist seine maximale Übertragungsgeschwindigkeit unter Benutzung der Streaming Data Prozedur auf 20 MByte/s begrenzt. Unterschiede zeigen sich auch in der Art und Weise der Implementation der Subsystem Control Block Architecture (SCBA). Bei Intel müssen sämtliche Register vom lokalen Mikroprozessor aus programmiert werden, so dass der Hauptprozessor nur einen einzigen SCB sowie die Daten in seinem Speicher bereitzustellen hat; das Subsystem führt dann den Transfer selbstständig durch. Der 82C614 aber erhält die SCB-Information über Ausgabebefehle vom Hauptsystem, was zeigt, dass der C&T-Chip für andere Aufgaben ausgelegt ist. Die folgenden Angaben sollen einige Anhaltspunkte geben, wo die Einsatzgebiete für die C&T-Schaltung liegen.

Der Chip stellt ein komplettes Interface zwischen dem Micro Channel und peripheren Einheiten oder Speicher dar. Während eines Datentransfers über den Kanal wird der Adapter, der den 82C614 einsetzt, als Busmaster arbeiten. Verschiedene Methoden, aus denen die jeweils günstigste durch Programmierung ausgewählt

**Bild 42**

Steuerung des Warte-Zyklen-Generators

werden kann, stehen zur Verfügung. So können Adressen für einen Transfer über den Micro Channel direkt in Lese- und Schreibimpulse für die Peripherie-Bausteine auf dem Adapter konvertiert werden und die Adapter-Elektronik direkt ansteuern. Der 82C614 kann wo nötig Wartezyklen einsetzen, Chip Select-Signale generieren und Interrupts der peripheren Einheit an den Micro Channel weiterleiten.

Die Datenbreite von 16 Bit erlaubt dem Chip, je nach Prozedur bis zu 20 MByte/s über den Micro Channel zu transferieren, sofern der Partner dieser Geschwindigkeit gewachsen ist. Wie in der Micro Channel-Architektur definiert, wird die Art des Transfers zwischen zwei Partnern im Laufe der Übertragung des ersten Zeichens einer Zeichenfolge (Burst) vereinbart. Der 82C614 kann sich selbstverständlich auf die Fähigkeiten des Partners einstellen. Der Chip wird durch eine Übertragung von Kontrolldaten vom Hauptprozessor programmiert. Dies ist einer der Gründe, weshalb in vielen Fällen auf einen lokalen Adapter-Prozessor verzichtet werden kann. Der Chip eröffnet damit eine Möglichkeit, auch dort mit effizienter Busmaster-Technik zu arbeiten, wo sonst aus Kostengründen nur traditionelle Entwicklungen in Frage kämen.

Vier DMA-Controller mit separaten, in ihrer Länge programmierbaren internen FIFO-Puffer-Speichern, steuern den Verkehr auf bis zu vier unabhängigen Wegen im Burst Mode über den Micro Channel. Da die Schaltung sowohl als Busmaster auf dem Micro Channel als auch mit DMA auf der Adapterseite arbeiten kann, ist sie in der Lage, bis zu vier parallele, direkte Datenkanäle zwischen dem Hauptsystem und dem Adapter zu schalten. Damit kann sie bis zu vier laufende Operationen in beiden Richtungen koordinieren.

Der 82C614 stellt einen Signalsatz zur Verfügung, der weitgehend demjenigen des PC AT angeglichen ist. Daher können bestehende Schaltungsentwürfe für den PC AT-Bus auf einfache Art für den Micro Channel modifiziert werden. Zusätzlich stehen eine Reihe von Mehrfunktions-Anschlüssen zur Verfügung, durch welche sich die lokale Schaltung weitgehend den individuellen Bedürfnissen anpassen lässt. Auch der lokale Teil unterstützt eine Datenbreite von 16 Bit. Daneben sind 16 Adressleitungen, die intern im Multiplex-Modus

mit den Datenleitungen arbeiten, aus dem Chip herausgeführt. Programmable Option Select (POS) ist vollständig im Chip integriert. Es können bis zu acht mit dem 82C614 ausgerüstete Adapter identischer Bauart in einer einzigen Maschine installiert werden.

Der 82C614 benötigt mehr POS-Information, als in den POS-Bytes der Micro Channel-Architektur vorgesehen sind. Deshalb werden konstante Informationen vom Hersteller des Adapters in einem 64 Byte-ROM auf dem Adapter vorprogrammiert. Nach jedem Reset des Gesamtsystems wird der ROM-Inhalt in die Register geladen und damit der Chip für seine Arbeit vorbereitet. In diesem ROM können unter anderem die POS-Identifikation, die Ein-/Ausgabe-Adressen für die Register sowie die Adressen für die externe Peripherie (Speicher und Ein-/Ausgabe) festgehalten werden. Am Beispiel eines Transfers vom Micro Channel zu einem lokalen Device sei nun der Ablauf im Prinzip dargelegt.

Sobald mittels Ausgabebefehlen die Information über die durchzuführende Übertragung vom Hauptprogramm (Device Driver im Betriebssystem der Micro Channel-Maschine) gemäss den Regeln der SCBA (Subsystem Control Block-Architektur) in die Register der Schaltung übertragen worden sind und ein Start DMA ausgegeben wurde, werden Daten vom Systemspeicher an die Peripherie übermittelt. Dazu muss der Adapter sich zuerst um den Bus bewerben. Sobald die Zuteilung erfolgt ist, werden solange Datenfolgen (Bursts) übertragen, bis der dem Kanal zugeteilte FIFO-Bereich voll oder die Übertragung beendet ist. Es können dazu mehrere Arbitrations- und Übertragungszyklen nötig sein. Die Adapter-Peripherie holt die Daten aus dem FIFO ab und überträgt sie an ihren Bestimmungsort. Sobald im FIFO wieder Platz frei ist (der Triggerpunkt ist programmierbar), wird automatisch ein neuer Transfer eingeleitet.

Mehrere Operationen können durch die Erstellung einer Linked List (mehrere Befehle für Operationen sind als SCBs gespeichert und miteinander durch Pointer verbunden) vorprogrammiert werden. Ist das der Fall, kann der 82C614 nach der Abarbeitung des ersten SCB automatisch mit der Übertragung fortfahren. Erst wenn sämtliche Daten übertragen sind, wird dem Hauptsystem durch ei-

nen Interrupt das Ende der Operation signalisiert.

Wie die vorstehenden Ausführungen gezeigt haben, ist die Schaltung von Chips und Technologies mehr auf die Dienste des Hauptprozessors angewiesen als diejenige von Intel. Die damit verbundene geringere Unabhängigkeit reduziert im Vergleich die Anforderungen an die Intelligenz des Adapters. In vielen Fällen kann sogar auf den Einsatz eines lokalen Prozessors und damit auf den damit zusammenhängenden, nicht unbeträchtlichen Entwicklungsaufwand (Programmierung des Subsystem-Mikroprozessors) verzichtet werden. Die beiden Systeme ergänzen sich damit sinnvoll bezüglich Leistung und Herstellkosten.

## Zusammenfassung

Die Micro Channel-Architektur von IBM ist eine Definition von Übertragungswegen und Impulsprogrammen zur Datenübertragung zwischen den verschiedenen Komponenten eines Computersystems. Sie ist erarbeitet worden einerseits, um die heutigen Bedürfnisse der Benutzer optimal zu erfüllen, und andererseits als Grundlage für kommende grössere Systeme mit verteilter Intelligenz und verteilten Daten, für Systeme also, welche die Herstellung exakter Abbildungen der Struktur mittlerer und grosser Unternehmungen ermöglichen sollen.

An derartigen Verbundsystemen sind Maschinen aller Grössenordnungen, Betriebssysteme und Architekturen, Datenbanken, Verbindungswege und Anwendungen beteiligt. Sie sind so aufeinander abzustimmen, dass auch neue Komponenten sich nahtlos in die erarbeiteten Konzepte einfügen, damit die Einzelsysteme möglichst lange und möglichst viele Systemänderungen «überleben» können.

## Literaturverzeichnis

- [1] Intel iAPX86/88, 186/188 User Manual, ISBN 0-917017-36-6

- [2] Intel 376 High Performance 32-bit Embedded Processor, Data Sheet

- [3] Intel 82370 Integrated System Peripheral, Data Sheet

- [4] Intel 80386 Hardware Reference Manual

- [5] Interfacing to the 80376, 80386SX and 80386 bus (A simple EPROM design), Intel TechBits MIP-21, Aug. 5. 1988

- [6] Intel 80376 Hardware Reference Manual

- [7] Heath/Rosch: The Micro Channel Architecture Hand book, 1991, ISBN 0-13-583493-7, Distr.: Prentice Hall Trade, Publ.: Brady

Weitere Literatur wurde bereits in Heft 17/90 genannt.