|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 80 (1989)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 15                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | EEPROM-Speicher-Elemente in der analogen Schaltungstechnik                                                                                                                                                                |

| <b>Autor:</b>       | Bleiker, C. / Moser, M. / Säckinger, E.                                                                                                                                                                                   |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-903698">https://doi.org/10.5169/seals-903698</a>                                                                                                                                   |

### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 28.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# EEPROM-Speicher-Elemente in der analogen Schaltungstechnik

Chr. Bleiker, M. Moser, E. Säckinger, W. Guggenbühl und H. Melchior

**An der ETH Zürich wurde untersucht, inwieweit Electrically Erasable and Programmable Read-Only Memories (EEPROM) als nichtflüchtige Speicher in analogen Anwendungen verwendet werden können. Nebst eingehenden Untersuchungen des Speicherverhaltens von Floating-Gate-Elementen wurden entsprechende integrierte Schaltungen realisiert. Der vorliegende Beitrag gibt eine Übersicht über die dabei erzielten Resultate.**

**A l'EPF Zurich on a examiné dans quelle mesure on peut utiliser les Electrically Erasable and Programmable Read-Only Memories (EEPROM) comme mémoires permanentes dans des applications analogiques. A part des examens approfondis du comportement de mémoire des éléments Floating-Gate, on a réalisé des circuits intégrés appropriés. L'article donne un aperçu des résultats obtenus.**

Electrically Erasable and Programmable Read-Only Memories (EEPROM) sind HalbleiterSpeicher, die vom Benutzer mittels Spannungs-impulsen beschrieben und gelöscht werden können, wobei die gespeicherte Information bei Unterbrüchen der Versorgungsspannung nicht verloren geht. Für solche EEPROM-Speicher existieren zahlreiche Anwendungen in Computersystemen sowie in Steuergeräten. Ganze Speicher-Chips (seit 1987 sind Bausteine mit 256k EEPROM-Zellen erhältlich) werden in Computersystemen anstelle von dynamischen oder statischen Random Access Memories (RAM) eingesetzt, um die Entwicklung von Betriebsprogrammen zu erleichtern oder die Datensicherheit bei Spannungsunterbrüchen zu garantieren. Daneben werden EEPROM-Elemente immer häufiger in Mikroprozessor- oder Logik-Schaltungen mit integriert, damit kleine benutzerspezifische Programme oder Erkennungscodes nichtflüchtig abgespeichert werden können. Außerdem wird die nächste Generation von Bank- und Kreditkarten mit EEPROM-Speichern versehen sein, die zur Speicherung des Identifikationscodes und des aktuellen Saldos benutzt werden.

Analoge Größen können einerseits mit digitalen EEPROM und nachgeschaltetem D/A-Wandler gespeichert werden. Sie können aber auch direkt in eine EEPROM-Zelle einprogrammiert werden, wobei die Tatsache ausgenutzt wird, dass abstuftbare Ladungspakete auf das Floating-Gate aufgebracht werden können. Ein solcher Einsatz von EEPROM-Zellen als Analogspeicher ist jedoch nur möglich, falls das elektrische Verhalten, insbesondere das Speicherverhalten, dieser Elemente genau bekannt ist und den Anforderungen genügt. Im Rahmen des Nationalfonds-Projektes

NFP-13 wurde an der ETH Zürich der Einsatz von Floating-Gate-EEPROM mit einem dünnen Tunneloxid (Flotox) als Analogspeicher geprüft, wobei einerseits das elektrische Verhalten der Elemente untersucht und andererseits Integrierte Schaltungen mit EEPROM als Analogspeicher entworfen und hergestellt wurden. Der Aufbau und die Charakterisierung dieser Elemente werden im zweiten Abschnitt dargestellt und die Anwendungen im dritten Abschnitt behandelt.

## Charakterisierung von Floating-Gate-Elementen

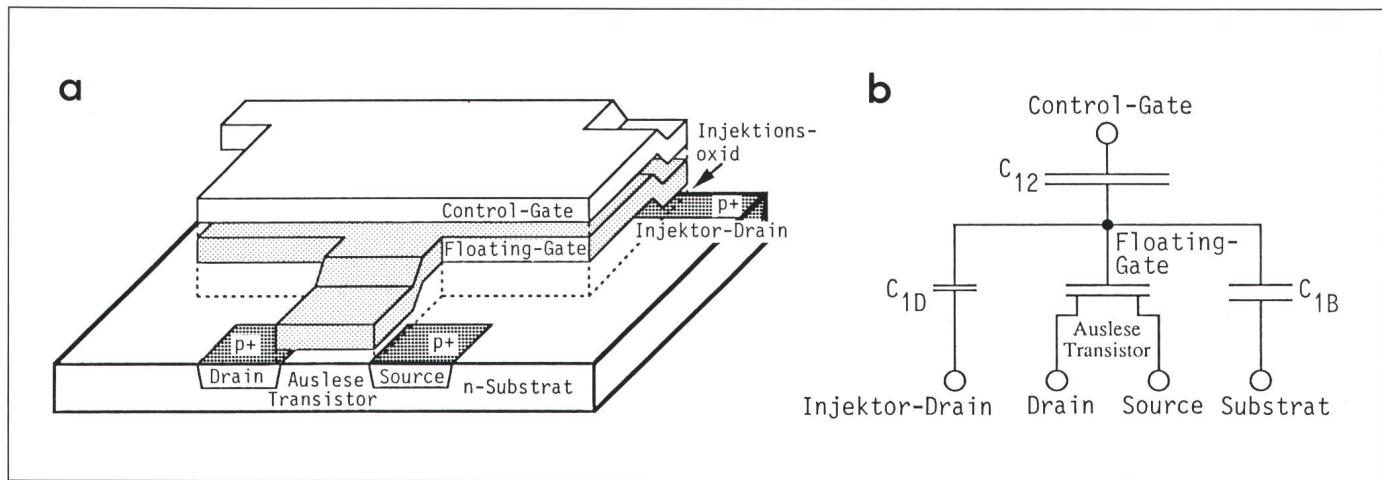

Der Aufbau einer EEPROM-Zelle mit Floating-Gate-Struktur ist in *Figur 1* dargestellt. Das Element besteht aus zwei Gates, dem zugänglichen Control-Gate zum Löschen und Steuern des Auslese-Transistors sowie dem vollständig isolierten Floating-Gate zur Speicherung der Information in Form von Ladungen; einem Injektor-Drain zum Schreiben sowie Source und Drain des p-Kanal-Auslese-Transistors. Zwischen dem Floating-Gate und dem Injektor-Drain liegt ein dünnes Injektionsoxid (8...20 nm). Im Vergleich dazu sind das Gateoxid und der Isolator zwischen den beiden Gates viel dicker (40...100 nm). Damit die Zelle mit niedrigen Spannungen programmiert werden kann, ist eine starke kapazitive Kopplung zwischen Control- und Floating-Gate notwendig, was durch eine grosse gemeinsame Fläche erreicht wird.

Beim Schreiben der Zelle wird am Injektor-Drain eine gegenüber dem Control-Gate negative Spannung angelegt, die bewirkt, dass aufgrund des sehr hohen elektrischen Feldes im Injektionsoxid Elektronen vom Injektor mittels Fowler-Nordheim Tunneling

### Adresse der Autoren

M. Moser, E. Säckinger und Prof. W. Guggenbühl, Institut für Elektronik, ETH-Zentrum, 8092 Zürich. Prof. H. Melchior, Institut für Quantenelektronik, ETH-Hönggerberg, 8093 Zürich.

Figure 1 Aufbau einer Floating-Gate-Zelle mit einem dünnen Tunneloxid zum Programmieren (Flotox)

a Schema      b Ersatzschaltbild

auf das Floating-Gate gelangen. Da die Feldstärken über allen anderen Isolatorstücken viel kleiner sind als im Injektionsoxid, werden die Elektronen auf dem Floating-Gate bleiben. Am Ende des Schreibens wird die Spannung des Injektor-Drains wieder auf Null zurückgesetzt, womit keine Ladungen mehr injiziert werden. Die auf dem Floating-Gate befindliche Ladung bleibt erhalten und bewirkt, dass der Auslese-Transistor bei einer Control-Gate-Spannung  $U_{G2} = 0$  V leitet, d.h., es ist eine logische 1 in die Zelle programmiert. Durch Verändern von  $U_{G2}$  kann die auf dem Floating-Gate gespeicherte Ladung  $Q_{G1}$ , und somit auch der Schwellwert  $U_{T2}$  der geschriebenen Zelle bestimmt werden. Zwischen  $Q_{G1}$  und dem Schwellwert  $U_{T2}$  gilt der lineare Zusammenhang:

$$U_{T2} = \frac{U_T}{\alpha} - \frac{Q_{G1}}{C_{12}} \quad (1)$$

mit  $U_T$  dem Schwellwert bezüglich des Floating-Gates im ungeladenen Zustand ( $Q_{G1} = 0$ ),  $\alpha = C_{12}/C_{\text{tot}}$  dem Kopplungsfaktor der Zelle,  $C_{12}$  der Kapazität zwischen Floating- und Control-Gate,  $C_{\text{tot}}$  der Summe aller auf das Floating-Gate einwirkenden Teilkapazitäten sowie  $Q_{G1}$  der auf dem Floating-Gate gespeicherten Ladung.

Zum Löschen der Zelle wird ans Control-Gate ein gegenüber dem Injektor-Drain negativer Spannungspuls angelegt. Durch die kapazitive Kopplung wird auch das Floating-Gate ein negatives Potential aufweisen und bewirken, dass die Elektronen durch das

Injektionsoxid in den Injektor zurücktunnellen. Am Ende des Löschens bleiben auf dem Floating-Gate mehr positive als negative Ladungen zurück, was bewirkt, dass der Auslese-Transistor für  $U_{G2} = 0$  V nicht mehr leitet.

Die EEPROM-HalbleiterSpeicher werden üblicherweise durch die drei folgenden Messungen charakterisiert:

- *Schreib- und Löschcharakteristik*: Abhängigkeit der gespeicherten Ladung und damit des Schwellwertes  $U_{T2}$  von der Amplitude sowie der Zeitdauer des Programmierpulses. Auswirkungen von zyklischem Programmieren auf die Schreibcharakteristik.

- *Speicherverhalten*: Änderungen der gespeicherten Ladung und des Schwellwertes (nach einem Schreib- oder Löschpuls) in Abhängigkeit von der Speicherzeit bei verschiedenen Temperaturen. Da das Speicherverhalten bei Zimmertemperatur praktisch unendlich gut ist, sind geeignete Beschleunigungsverfahren zur Charakterisierung anzuwenden, aus denen auf das Betriebsverhalten bei Betriebstemperatur geschlossen werden kann.

- *Ausdauerverhalten*: Änderungen des Schwellwertes  $U_{T2}$  in Abhängigkeit von der Anzahl der Schreib- und Löschzyklen. Da bei jedem Programmieren auch Ladungen im Injektionsoxid durch Störstellen eingefangen werden, ist die maximale Anzahl Programmzyklen beschränkt. Messungen des Ausdauer-Verhaltens geben deshalb auch Auskunft über die Qualität des Injektionsoxides.

Analoge Anwendungen von EEPROM-Speichern verlangen so-

wohl ein genaues Schreiben auf einen gewünschten Ladungszustand als auch möglichst geringe Ladungsänderungen während des Speicherns. Der Ladungszustand kann durch einen iterativen Schreibvorgang sehr genau eingestellt werden, womit die Charakterisierung des Schreib-, Lösch- und Ausdauerverhaltens von untergeordneter Bedeutung wird [1;2]. Das Speicherverhalten dagegen bestimmt die möglichen analogen Anwendungen massgebend. Es wurde deshalb eingehender untersucht.

## Speicherverhalten

Die Untersuchungen wurden an Flotox-Zellen durchgeführt, die bei

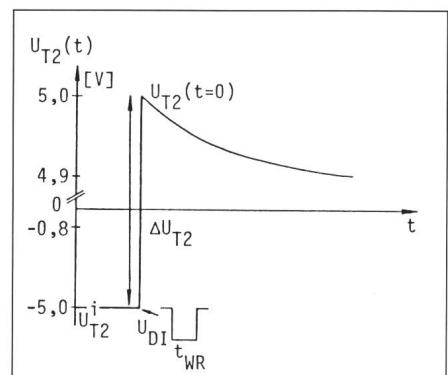

Figure 2 Schreibvorgang einer Floating-Gate-Zelle

Eine gelöschte Zelle ( $U_{T2} < U_T/\alpha \approx -0.8$  V) wird mittels eines negativen Spannungspulses  $U_{DI}$  am Injektor-Drain geschrieben. Dadurch werden Elektronen aufs Floating-Gate gebracht, und der Schwellwert wird positiver. Im Laufe der Zeit ändert sich  $U_{T2}(t)$  aufgrund von Ladungsverschiebungen nach dem Programmieren.

der Firma Faselec AG, Zürich, im 3-µm-Self-Aligned-Contact-MOS (Sacmos)-Prozess hergestellt wurden. Ein typischer Messvorgang ist in Figur 2 dargestellt.

Vorerst wird der Schwellwert  $U_{T2}^i$ , und damit der ursprüngliche Ladungszustand, einer EEPROM-Zelle gemessen. Danach wird auf den Injektor-Drain ein negativer Spannungspuls  $U_{DI}$  der Zeitdauer  $t_{WR}$  angelegt. Unmittelbar danach wird wiederum der Schwellwert  $U_{T2}(t = 0)$  bestimmt, wodurch der neue Ladungszustand  $Q_{G1}(t = 0)$  des Elementes festgestellt werden kann. Schliesslich können durch kontinuierliches Messen von  $U_{T2}$  Veränderungen der Floating-Gate-Ladung  $Q_{G1}(t)$  oder sonstige Ladungsverschiebungen innerhalb der EEPROM-Struktur festgestellt werden.

Die resultierenden zeitlichen Verläufe von  $U_{T2}(t) - U_{T2}(t = 0)$  für verschiedene programmierte Elemente sind in Figur 3 dargestellt. Aus dem beobachteten Speicherverhalten nach dem Schreiben und Löschen kann gefolgt werden, dass

- der Schwellwert  $U_{T2}(t)$  sich in Richtung des vorherigen Zustandes  $U_{T2}^i$ , ändert,

- die Änderung von  $U_{T2}(t)$  proportional zur Schwellwertdifferenz  $\Delta U_{T2}$  ist, die durch das Schreiben (Löschen) entstanden ist, wobei  $\Delta U_{T2} = U_{T2}(t = 0) - U_{T2}^i$ ,

- die Zeitabhängigkeit der Schwellwertänderung bei Zimmertemperatur beinahe logarithmisch verläuft.

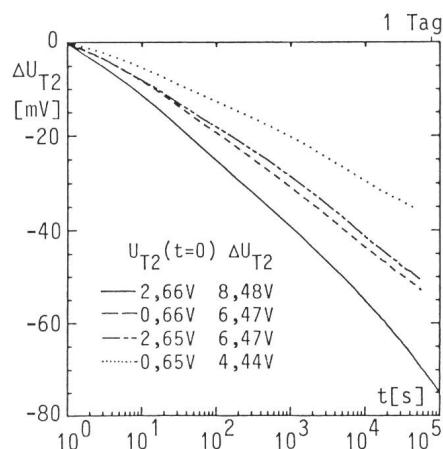

Figur 3 Kurzfristige Schwellwertänderung

Gemessene Schwellwertänderungen  $\Delta U_{T2}(t)$ , bei Zimmertemperatur nach einem Schreibpuls mit verschiedenen Anfangs- und Endbedingungen ( $\Delta U_{T2}$  resp.  $U_{T2}(t = 0)$ ).

$$\Delta U_{T2} = U_{T2}(t) - U_{T2}(t = 0)$$

$t$  Speicherzeit

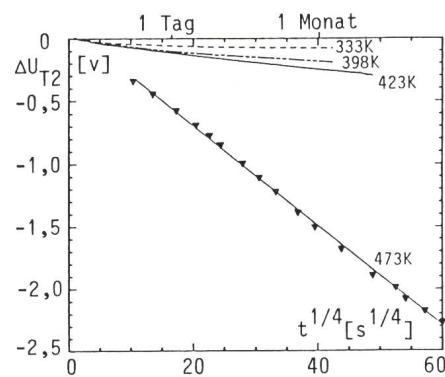

Figur 4 Langfristige Schwellwertänderung

Schwellwertänderungen  $U_{T2}(t) - U_{T2}(t = 0)$  in Funktion von  $t^{1/4}$  bei verschiedenen Speichertemperaturen. Die Zellen waren ursprünglich auf  $U_{T2}^i = -2V$  gelöscht und wurden dann auf  $U_{T2}(t = 0) = 3V$  geschrieben.

$$\Delta U_{T2} = U_{T2}(t) - U_{T2}(t = 0)$$

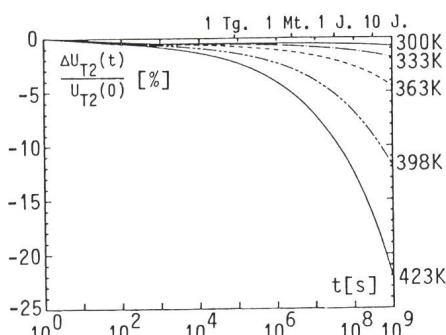

Figur 5 Berechnete prozentuale Änderung des Schwellwertes  $U_{T2}(t)$  nach dem Schreiben für verschiedene Speichertemperaturen

$$\frac{\Delta U_{T2}(t)}{U_{T2}(0)} \text{ Prozentuale Änderung}$$

$$t \text{ Speicherzeit}$$

Durch Erhöhen der Speichertemperatur können die Schwellwertänderungen beschleunigt werden. Aus der Temperaturabhängigkeit lassen sich Rückschlüsse auf die beteiligten physikalischen Vorgänge ziehen. Deshalb wurden Experimente im Temperaturbereich von  $77K < T < 523K$  durchgeführt. Aus diesen Messungen geht hervor, dass das Speicherverhalten zwei verschiedenen zeitlichen Gesetzmäßigkeiten folgt. Der Schwellwert ändert sich zu Beginn logarithmisch in Funktion der Zeit (Fig. 3) und wechselt je nach Speichertemperatur früher (hohe Temperatur) oder später zu einer Zeitabhängigkeit gemäß  $t^{1/4}$  (Fig. 4). Das gemessene Speicherverhalten kann weder mit dem Thermionischen Emissionsmodell noch mit dem Tunneling-Modell beschrieben werden [3;4;5]. Diese in der Fachliteratur verwendeten Modelle nehmen an, dass die auf dem Floating-Gate gespeicherte Ladung entweder aufs Control-Gate oder in den Injektor-Drain entkommen kann und dort rekombiniert. Bei diesem Vorgang sollte die Schwellwertänderung proportional zur gespeicherten Ladung  $Q_{G1}$  auf dem Floating-Gate verlaufen, was unseren Beobachtungen widerspricht. Deshalb wird zur Beschreibung des Speicherverhaltens ein neues, sogenanntes Interface-Trap-Modell vorgeschlagen. Dabei wird angenommen, dass Interface-Traps (-Fallen) an den Grenzschichten des Polysiliziums je nach angelegtem Potential geladen oder entladen werden oder dass durch chemische Vorgänge neue Traps gebildet oder alte

abgebaut werden. Diese Traps werden nicht gleich beim Programmieren der Zelle umgeladen, sondern erst im Laufe der Zeit. Dadurch ändert sich der Ladungszustand des Floating-Gates nach dem Programmieren. Je nach Ausgleichsvorgang resultiert eine Zeitabhängigkeit gemäß  $\log(t)$  fürs Laden und Entladen mittels Tunneling oder  $t^{1/4}$  beim Auf- und Abbau durch chemische Reaktionen. Die gemessenen Temperaturabhängigkeiten der beiden Teilreaktionen entsprechen dabei den von der Physik her erwarteten Werten sehr gut.

Mit der Kenntnis der Ladungsänderungen an den Grenzschichten können die Auswirkungen auf analoge Anwendungen abgeschätzt werden. Dabei wird vorausgesetzt, dass mittels eines iterativen Schreibvorgangs geschrieben wird, was gewährleistet, dass am Ende des Programmierens der gewünschte Ladungszustand auf wenige Promille genau erreicht ist. Demnach bilden die Ladungsveränderungen an den Grenzschichten des Polysiliziums den Hauptanteil der Störeinflüsse, die den Einsatz von EEPROM in analogen Anwendungen einschränken. In Figur 5 sind die berechneten prozentualen Änderungen des Schwellwertes einer typischen EEPROM-Zelle in Funktion der Speicherzeit für einige Temperaturen aufgetragen. Daraus geht hervor, dass bei Genauigkeitsanforderungen von wenigen Prozenten (etwa 3%) und Temperaturen unter 90°C eine Speicherzeit von 10 Jahren garantiert werden kann.

## Anwendungen von Floating-Gate-Elementen

Sowohl Floating-Gate- als auch MNOS (Metal Nitride Oxide Semiconductor)-Speicherelemente können in der analogen Schaltungstechnik eingesetzt werden. In der Literatur finden sich mehrere Beispiele dafür. In [6;7] werden optische Speicher beschrieben, welche durch Licht erzeugte Ladungsträger auf einem Floating-Gate-Element speichern. Die Artikel [8;9] befassen sich mit dem Thema der nichtflüchtigen Analogsignalspeicherung. Programmierbare Kapazitäten lassen sich ebenfalls mit Hilfe der Floating-Gate-Technik realisieren [10]. Mit einer solchen Kapazität kann z.B. ein Uhrenquarz abgeglichen werden [11]. Floating-Gate-Elemente wurden auch zur Ansteuerung (Öffnen und Schliessen) von Analogschaltern eingesetzt [12;13]. Damit können Parameter (z.B. Referenzspannung, Quarzfrequenz) in einer Analogschaltung stufenweise abgeglichen werden.

An der ETHZ wurden die folgenden Schaltungen realisiert und untersucht:

- elektronischer Trimmer zum Abgleich von Offset-Spannung und Linearität eines differentiellen Differenzverstärkers (DDA<sup>1</sup>).

- programmierbares Filter für den Audiobereich,

- digitaler Speicher, der pro Floating-Gate-Element zwei Bit speichern kann,

- Analog-Multiplikator, der eine Eingangsspannung mit einer programmierbaren Konstanten multipliziert [14],

- Spannungswandler für sehr kleine Eingangsspannungen [15],

- programmierbare Strom- und Spannungsquellen [2;16]

Stellvertretend für all diese Schaltungen werden im folgenden der Trimmer, das Filter und der Speicher näher beschrieben.

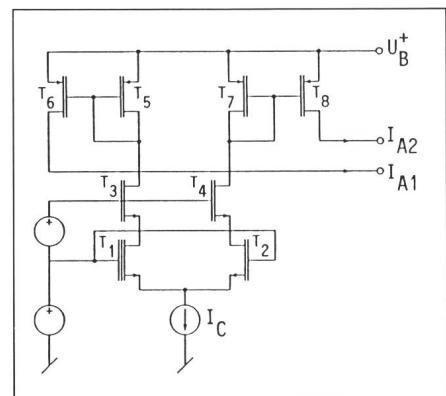

## EEPROM-Trimmer (differentielle Stromquelle)

Beim EEPROM-Trimmer handelt es sich um eine Schaltung, die das Abgleichen der Differenz zweier Ströme erlaubt; das Prinzipschaltbild ist in Figur 7 dargestellt. Der EEPROM-Trimmer stellt also eine Alternative zum mechanischen Trimmer oder dem Laser-Trimmern dar, hat aber den Vorteil, dass er monolithisch integrierbar ist und elektrisch abgeglichen werden kann. Zu seiner Erprobung wurde an der ETH ein differentieller Differenzverstärker (DDA<sup>1</sup>) mit zwei derartigen Trimmern realisiert [18;19]. Der eine Trimmer im DDA dient zum Abgleich der Arbeitspunktströme im Stromspiegel<sup>2</sup> und somit zur Kompensation der Offset-Spannung. Der andere gleicht die Stromquellen in den beiden Differenzstufen und damit die Linearität ab.

Im folgenden soll das Abgleichprinzip an der Hand des EEPROM-Trimmers für die Linearität skizziert werden (Fig. 7).  $T_1$  und  $T_2$  bilden ein Differenzpaar, das den Strom  $I_C$  entsprechend dem Ladungszustand der

Figur 7 Prinzipschaltbild eines EEPROM-Trimmers und dessen Einsatz im DDA

Die Ströme  $I_{A1}$  und  $I_{A2}$  werden zur Korrektur zweier Differenzstufenströme im DDA benutzt. Da die Linearität des DDA von der Gleichheit dieser Ströme abhängt, können eventuelle Abweichungen mit dem EEPROM-Trimmer ( $T_1 - T_8$ ) kompensiert werden.  $T_1$  ist der abgleichbare Floating-Gate-Transistor.

Speicherkapazität auf die beiden Stromspiegel  $T_5/T_6$  und  $T_7/T_8$  aufteilt. Die Kaskodentransistoren  $T_3/T_4$  haben die Aufgabe, die Drain-Source-Spannung über  $T_1$  so klein zu halten, dass eine Upprogrammierung des Elementes durch heiße Kanalelektronen vermieden wird. Die Stromspiegel haben die Aufgabe, den Abgleichstrombereich der Trimmerschaltung ( $\pm I_C$ ) an den benötigten Bereich der jeweiligen Anwendung anzugeleichen. Wenn, wie in unserem Fall, sehr kleine Ströme im nA-Bereich benötigt werden, sind Stromquellen- und Differenzstufen-Transistoren mit langem Kanal und ein untersetzender Stromspiegel angebracht.

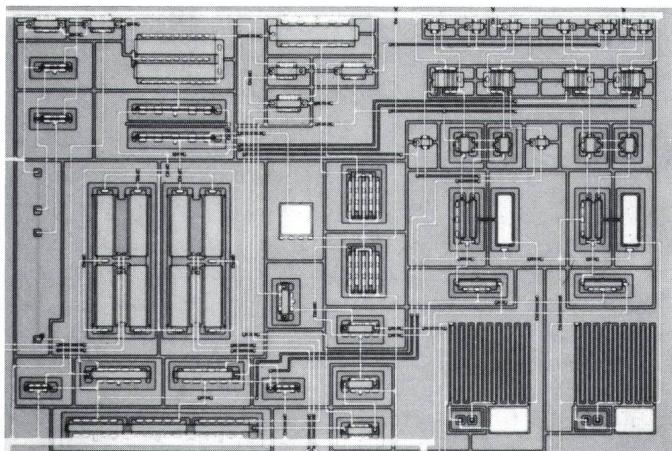

Eine komplette DDA-Schaltung mit den erwähnten zwei Trimmern wurde bei Faselec AG hergestellt (Fig. 6). Mit den Trimmern kann die Offset-Spannung auf typisch 10 mV und die Linearität auf typisch 0,1% bei einem Eingangsspannungsbereich von  $\pm 1,5$  V abgeglichen werden. Der Trimmbereich, der dem maximalen Fehler, der noch abgeglichen werden kann, entspricht, beträgt für die Offset-Spannung etwa 15 mV und für die Linearität etwa 0,7%.

Aufgrund des Driftverhaltens der Floating-Gate-Elemente des 3- $\mu$ m-Faselec-Prozesses (SACMOS), das in Figur 5 dargestellt ist, kann abgeschätzt werden, wie sich die Offset-Spannung nach dem Abgleich verändert wird: Die Kurve für Raumtemperatur

Figur 6

Chip-Foto des Differential Difference Amplifiers (DDA) mit den zwei EEPROM-Trimmern auf der rechten Seite

(300 K) zeigt eine Abweichung von < 1% für die folgenden 10 Jahre. Umgerechnet auf einen Abgleichbereich von 19 mV, bedeutet dies eine Offset-Drift von weniger als 0,1 mV in demselben Zeitraum. Analog kann ein Driften der Linearität um weniger als 0,01% vorausgesagt werden.

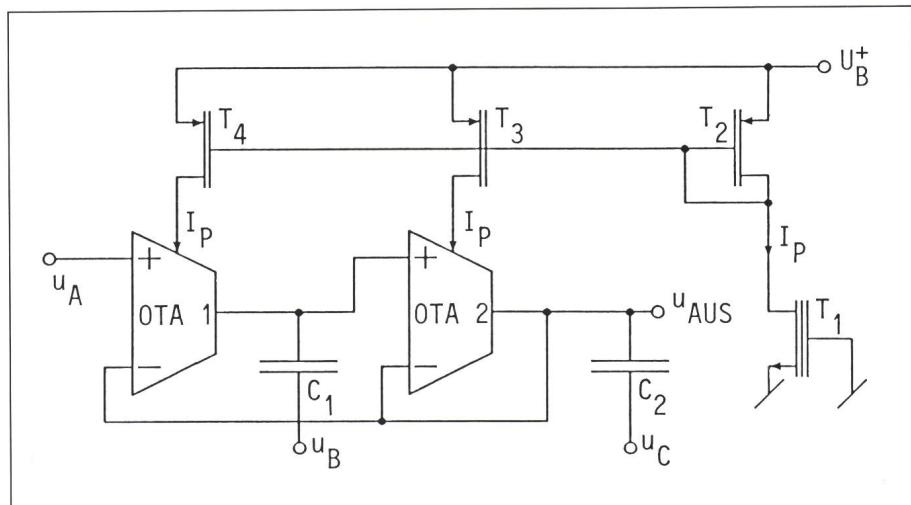

### Filter mit programmierbarer Grenzfrequenz

Bei vielen Anwendungen von Filterschaltungen müssen gewisse Parameter, wie z.B. Güte und Grenzfrequenz, abgestimmt werden. Dies wird heute meist dadurch erreicht, dass trimmbare Komponenten (Potentiometer) eingebaut werden. Zur Miniaturisierung, wie sie z.B. in Hörgeräten notwendig ist, eignet sich ein solches Vorgehen nicht. Es wurde deshalb ein vollintegriertes Filter 2. Ordnung mit einer mittels Floating-Gate-Elementen abgleichbaren Grenzfrequenz entwickelt. Das Filter besteht, wie in Figur 8 dargestellt, im wesentlichen aus zwei OTA<sup>3</sup> (Operational Transconductance Amplifier), die am Ausgang mit je einem Kondensator beschaltet sind. Dadurch werden Integratoren realisiert.

$$u_{\text{AUS}}(t) = \frac{g_m}{C} \int u_{\text{EIN}}(t) dt \quad (2)$$

Durch eine im wesentlichen aus einem Floating-Gate-Element bestehende Stromquellschaltung ( $T_1, \dots, T_4$ ) kann die Transkonduktanz  $g_m$  der OTA verändert werden. Das Ausgangssignal des realisierten Filters berechnet sich – wie man leicht zeigen kann – folgendermassen:

$$u_{\text{AUS}}(t) = \frac{u_C s^2 + u_B s \frac{g_{m2}}{C_2} + u_A \frac{g_{m1} g_{m2}}{C_1 C_2}}{s^2 + s g_{m2} C_2 + \frac{g_{m1} g_{m2}}{C_1 C_2}}$$

Je nachdem, ob die Klemmen A, B, C der Figur 8 mit dem Eingang oder mit Masse verbunden werden, ergeben sich die verschiedenen Filtertypen, wie Tiefpass, Bandpass, Bandsperre oder Hochpass. Die Schaltung wurde so ausgelegt, dass  $g_{m1}$  und  $g_{m2}$  gleich sind,

<sup>3</sup> Ein OTA (Operational Transconductance Amplifier) ist eine spannungsgesteuerte Stromquelle

Figur 8 Prinzipschaltbild des programmierbaren Filters

wodurch sich eine gleichbleibende Filtergüte von eins ergibt; eine Veränderung von  $g_m$  ändert lediglich die Polfrequenz. In Tabelle I sind die gemessenen Daten des Filters zusammengefasst.

### Floating-Gate-Speicher mit vier logischen Niveaus

Der relativ grosse Platzbedarf einer Zelle (typischerweise 100...200  $\mu\text{m}^2$ ) bildet ein grosses Hindernis für die Realisierung von sehr grossen Speicherchips mit EEPROM-Elementen, da die Ausbeute mit steigender Chipfläche meist drastisch sinkt. Bis anhin versuchte man den Platzbedarf der Schaltungen durch Verkleinern der minimalen Abmessungen (Scaling) zu reduzieren, wobei aber das Tunneloxid nicht beliebig dünn gemacht werden kann. Eine andere Möglichkeit besteht darin, pro Speicherzelle mehr als ein Bit Information zu speichern.

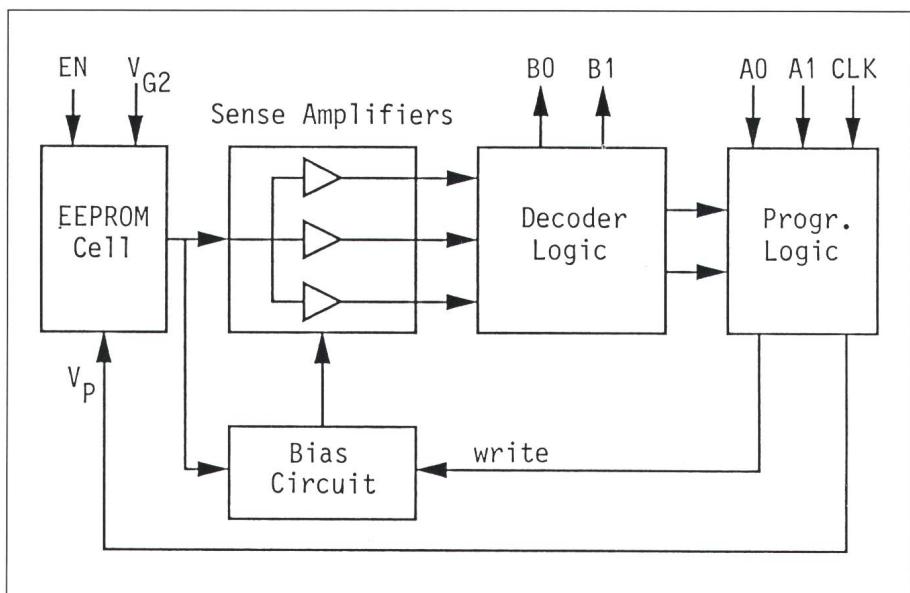

Das Funktionsprinzip einer mehrstufigen Logik wurde an einer Schaltung (Figur 9) mit einer EEPROM-Zelle demonstriert, welche vier verschiedene Ladungszustände realisiert und die gesamte Decodier- und Programmier-Logik enthält [20]. Den vier logischen Zuständen entsprechen verschiedene Bereiche der Floating-Gate-Spannung. Je nach dieser Spannung fließt im Speicherelement ein unterschiedlicher Strom, der auf drei Sense-Amplifiers geleitet wird, wo die Unterscheidung in die vier logischen Zustände geschieht. In der nachfolgenden Decodierlogik werden die drei Ausgänge der Sense-Amplifier in eine binäre 2-Bit-Information umgewan-

delt, die ausgelesen werden kann. Damit spürt der Anwender nichts von der internen Mehrstufen-Logik. Um ein bestimmtes 2-Bit-Muster abzuspeichern, müssen das binäre Signal sowie die negative Programmierspannung am Chip angelegt werden. Durch einen kontrollierten Schreibvorgang wird der Ladungszustand des Elementes solange verändert, bis der nominelle Wert der gewünschten Logik-Stufe erreicht ist. Gelöscht wird die vierstufige EEPROM-Zelle auf gleiche Art wie die binäre, mittels eines negativen Spannungspulses am Control-Gate.

Diese vierstufige Logik erlaubt, den Platzbedarf eines EEPROM-Speichers praktisch zu halbieren, da nur halb so viele EEPROM-Elemente benötigt werden und die Sense-Amplifier sowie die Decodier- und Programmier-Logik nur einmal integriert werden müssen. Aus Messungen des Speicherverhaltens kann gefolgt werden, dass eine Speicherzeit von mindestens 10 Jahren bei 125°C auch für solche vierstufigen EEPROM-Speicher garantiert werden kann.

| Parameter                | Typ. Wert oder Bereich |

|--------------------------|------------------------|

| Polfrequenzbereich       | 100 Hz...2,5 kHz       |

| Filtergüte               | 1                      |

| Eingangsspannungsbereich | $\pm 0,5 \text{ V}$    |

| Verzerrung (THD)         | < 1%                   |

| Speisestrom              | < 25 $\mu\text{A}$     |

| Speisespannung           | $\pm 2,5 \text{ V}$    |

Tabelle I Daten des programmierbaren Filters

## Verdankungen

Wir sind *J. Solo de Zaldivar* von der Firma Philips Faselec für die Herstellung langzeitstabiler EEPROM-Elemente zu Dank verpflichtet. Die verschiedenen Schaltungen mit integrierten EEPROM-Zellen wurden vom Centre Suisse d'Electronique et de Microtechnique S.A. (CSEM) in Neuenburg und von der Faselec AG in Zürich hergestellt. Dem Nationalfonds sei für die Unterstützung dieser Arbeiten im Rahmen des Forschungsprogrammes NF-13, Mikroelektronik und Optoelektronik, gedankt.

Figur 9 Blockschaltbild der Schaltung mit einer Floating-Gate-Zelle zum Speichern von vier logischen Stufen

## Literatur

- [1] C. Bleiker und H. Melchior: Nicht-flüchtige Speicher und ihre potentielle Anwendung im Analogbereich. Bull. SEV/VSE 75(1984)3, S. 158 ... 161.

- [2] E. Säckinger: Untersuchungen über die Realisierbarkeit von programmierbaren nicht-flüchtigen Stromquellen mit EEPROM-Zellen. Technical Report 84/4. Zürich, ETH, Institut für Elektronik, 1984.

- [3] A. Bhattacharya: Modelling of write/erase and charge retention characteristics of floating gate EEPROM devices. Solid-State Electronics 27(1984)10, p. 899 ... 906.

- [4] H. Nozawa und S. Kohyama: A thermionic electron emission model for charge retention in SAMOS structures. Japanese Journal of Applied Physics 21(1982)2, p. L 111 ... L 112.

- [5] H. Nozawa a. o.: Characteristics and reliability of the SEPROM cell. IEEE Trans. ED 31(1984)10, p. 1413 ... 1419.

- [6] Y. Hayashi, K. Nagai und Y. Tarui: Electrically erasable non-volatile optical memory for visible and infrared light pattern. 5th Conference on Solid-State Devices, Tokyo 1973. Japanese Journal of Applied Physics, Supplement 43(1974), p. 362 ... 366.

- [7] T. Ando und H. Yamasaki: New read-out mode in light-sensitive floating gate MOS memory. IEEE Electron Device Letters 3(1982)4, p. 83 ... 85.

- [8] R. Withers, R. Ralston und E. Stern: Nonvolatile analog memory in MNOS capacitors. IEEE Electronic Device Letters 1(1980)3, p. 42 ... 45.

- [9] R. Withers, D. Silversmith und R. Mountain: MNOS/CCD nonvolatile analog memory. IEEE Electron Device Letters 2(1981)7, p. 165 ... 166.

- [10] H. Kalter und H. Kotecha: Programmable voltage-variable capacitor. IBM Technical Disclosure Bulletin 24(1982)3, p. 5052 ... 5054.

- [11] Y. Hattori a. o.: Application of floating MOS variable capacitor for watch IC. Proceedings of the International Congress of Chronométrie, Besançon, 1984; p. 9 ... 12.

- [12] H. Oguey: Référence de tension et détecteur de tension de pile à faible consommation. Acte du 57e Congrès International de Chronométrie, Montreux, 1982; p. 59 ... 63.

- [13] R. Geddes und A. Korom: Clock device with non-volatile memory frequency trimming. Bull. SEV/VSE 75(1984)3, p. 151 ... 153.

- [14] M. Moser und R. Schaffner: Integration eines programmierbaren nichtflüchtigen Analog-Multiplikators in CMOS. Technical Report SA 85/9. Zürich, ETH, Institut für Elektronik, 1985.

- [15] C. Grütter und T. Marty: Spannungswandler für niedrige Speisespannungen. Technical Report SA 86/87/1, Zürich, ETH, Institut für Elektronik, 1987.

- [16] E. Säckinger und W. Guggenbühl: An electrically programmable nonvolatile CMOS voltage source based on a floating-gate device. Technical Report 87/2. Zürich, ETH, Institut für Elektronik, 1987.

- [17] E. Säckinger und W. Guggenbühl: A versatile building block: the CMOS differential difference amplifier. IEEE Journal of Solid-State Circuits 22(1987)2, p. 287 ... 294.

- [18] E. Säckinger: Ein «Differential Difference Amplifier» mit elektrisch abgleichbarer Offset-Spannung und Linearität. Technical Report 87/6. Zürich, ETH, Institut für Elektronik, 1987.

- [19] E. Säckinger und W. Guggenbühl: An analog trimming circuit based on a floating-gate device. IEEE Journal of Solid-State Circuits 23(1988)6, p. 1437 ... 1440.

- [20] C. Bleiker und H. Melchior: A four-state EEPROM using floating-gate memory cells. IEEE Journal of Solid-State Circuits 22(1987)3, p. 460 ... 463.