|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 79 (1988)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 1                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Q-Bus, der Datenpfad für DEC-Kleinsysteme                                                                                                                                                                                 |

| <b>Autor:</b>       | Bucher, H. P.                                                                                                                                                                                                             |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-903966">https://doi.org/10.5169/seals-903966</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Q-Bus, der Datenpfad für DEC-Kleinsysteme

H. P. Bucher

**Den Q-Bus findet man fast ausschliesslich auf Rechnern der Digital Equipment Corporation. Trotzdem hat er einen nicht unwesentlichen Einfluss auf die Entwicklung anderer Bus-Architekturen gehabt. Dies zeigt sich unter anderem darin, dass eine Reihe von Hardwareproduzenten steckerkompatible Baugruppen für den Q-Bus bauen. Vom Hersteller wurde die Architektur des Busses bewusst einfach konzipiert, so dass ein DEC-Produkteanwender ohne allzu grosse Schwierigkeiten Interfacekarten für seine Applikationen herstellen kann. Der Beitrag beschreibt die grundlegenden Eigenschaften dieses weitverbreiteten Bussystems.**

**Bien qu'on ne le rencontre que presque exclusivement sur les ordinateurs de Digital Equipment Corporation, le Q-bus a eu une influence non négligeable sur l'évolution d'autres architectures. En effet, un certain nombre de constructeurs de matériels produit des modules connectables avec le Q-bus. L'architecture de ce Q-bus a été conçue intentionnellement simple, de sorte que l'utilisateur de produits DEC n'ait guère de difficultés à établir les cartes d'interfaces de ses propres applications. L'article expose les propriétés fondamentales de ce système de bus très répandu.**

## Adresse des Autors:

Hans Peter Bucher, Digital Equipment Corp. AG, Schulungs-Zentrum, Murtenstrasse 137a, 3001 Bern.

Der Q-Bus verbindet als allgemeiner Datenpfad alle wichtigen Komponenten eines Rechnersystems miteinander. Der Datenaustausch geschieht asynchron mit Hilfe des sogenannten Handshaking-Verfahrens, das vom Bus-Arbitrator (Bus-Zuteilungssystem) gesteuert und überwacht wird. Adressen und Daten werden im Zeitmultiplexverfahren über die gleichen physikalischen Leitungen übertragen. Von der Hardware her gesehen, sind zwei Ausbaustufen zu unterscheiden:

1. Verbindung mehrerer Leiterplatten auf einer Backplane,

2. Verbindung von maximal drei Backplanes mit Flachbandkabeln.

Um einen möglichst hohen Durchsatz zu erreichen, wurde die physikalische Länge des Q-Busses auf maximal 5,6 m begrenzt.

## 1. Architektur

Die wichtigsten Architekturdaten sind:

- asynchrone Arbeitsweise (Handshaking-Protokoll)

- Zeitmultiplexverfahren zur Übertragung von Adressen und Daten

- 16-bit-Datenbreite

- 22-bit-Adressbreite (4-MByte-Adressraum).

Daten können auf vier verschiedene Arten übertragen werden:

1. Einzeltransfer in Bytes oder Doppelbytes (Words)

2. DMA (Direct Memory Access)

3. Block-Transfer (bis 16 Byte, nur auf neuen Maschinen möglich)

4. DMA-Burst-Mode (bis 64 Kbyte/Burst).

Der maximal mögliche Datendurchsatz des Q-Busses beträgt beim Standardprotokoll 1,66 MByte, im DMA-Burst-Mode 1 MByte und im Block-Mode etwa 3 MByte. Der Hauptvorteil einer asynchronen Architektur liegt in der Möglichkeit, die Geschwindigkeit der einzelnen Baugruppen oder Interfaces sehr flexibel an den Bus anzupassen. Der gegenüber der synchronen Arbeitsweise etwas grössere Overhead (zusätzlich benötigtes Protokoll) wird dadurch mehr als kompensiert.

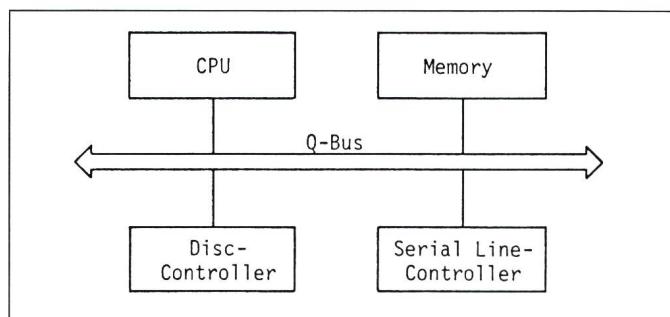

Die Figur 1 zeigt eine übliche Systemkonfiguration: Um den Bus ordnen sich Prozessor, Memory, Disk-Controller sowie der Serial-Line-Controller für Bildschirm und Drucker. Durch Einsticken von weiteren Interfacekarten kann das System für alle möglichen Funktionen problemlos erweitert werden.

Die 16-bit-Datenbreite hat historische Gründe. Der Bus wurde für die PDP-11-Rechnerserie entworfen, und diese hat bekanntlich eine 16-bit-Architektur. Dadurch war aber auch der Adressierumfang auf 64 kByte festgelegt. Ein spezieller Adress-Mapper (Memory-Management) erweitert die Adressbreite für den Q-Bus auf 22 bit, wodurch ein Adressumfang von 4 MByte erreicht wird. Selbstverständ-

**Figur 1**

**Übliche Systemkonfiguration**

Um den Bus ordnen sich Prozessor, Memory, Disk-Controller sowie der Serial-Line-Controller für Bildschirm und Drucker.

lich müssen auch alle Komponenten eines Rechnersystems wie Memory und Interfacekarten mit den zugehörigen Steuer- und Datenregistern adressiert werden können.

Die verschiedenen Arten des Datentransfers wurden bereits angegeben. Die Haupttransferart, welche vom Memory zum Prozessor und in umgekehrter Richtung verläuft, wird üblicherweise Single-Cycle-Mode genannt. Für den Direct-Memory-Access (DMA, z.B. von einem Massenspeicher zum Memory oder umgekehrt) wird der Prozessor kaum belastet; dafür muss auf dem DMA-initialisierenden Gerät eine kompliziertere Hardware zur Überwachung des Transfers installiert sein. Der Burst-DMA-Mode verwendet ein kürzeres Protokoll und erreicht dadurch eine wesentlich höhere Durchsatzquote. Die schnellste Übertragung aber erreicht der Block-Mode, bei welchem ein Minimalprotokoll Blöcke von maximal 16 Byte überträgt. Diese Übertragungsart wird aber nur von Bus-Interfaces und Speichern neueren Datums unterstützt.

## 2. Protokolle

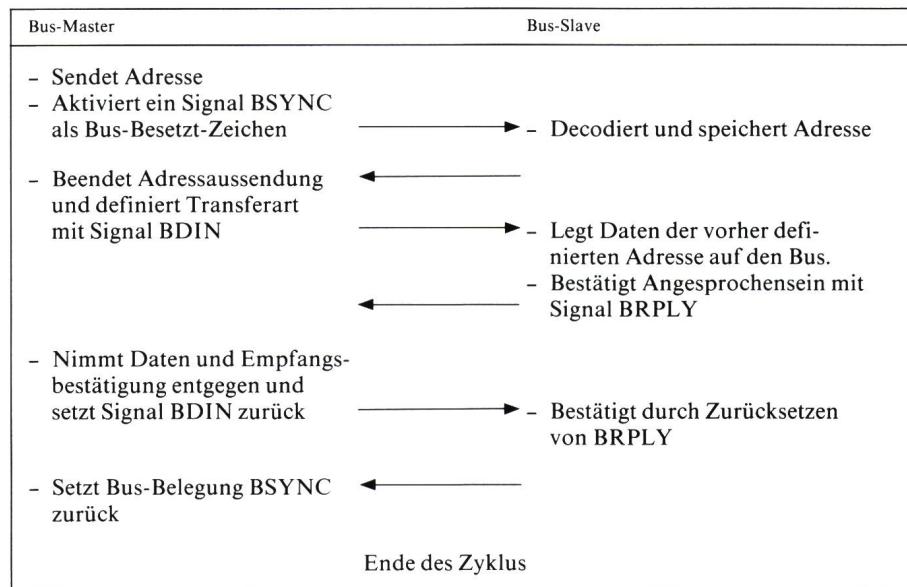

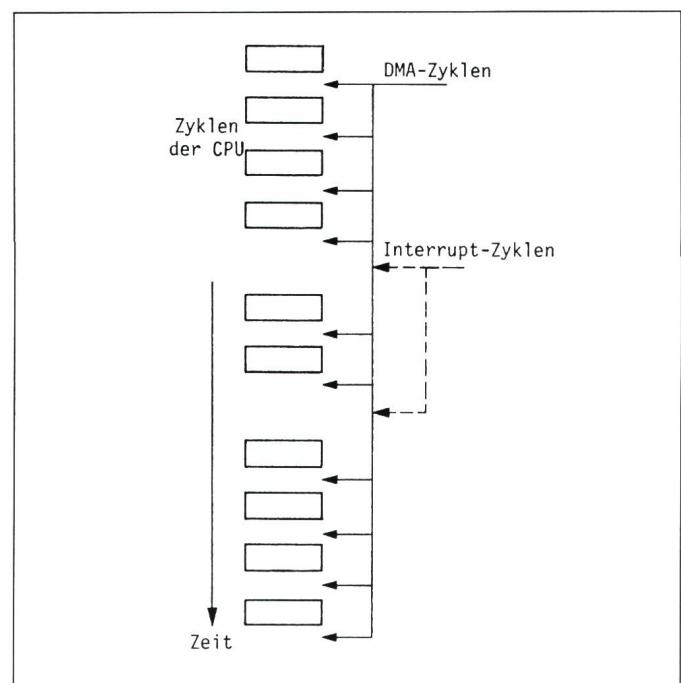

Der Ablauf auf dem Bus wird durch das Handshaking-Protokoll geregelt. Dazu sind folgende Bedingungen einzuhalten: Bevor ein Datentransfer über den Bus laufen kann, muss ein sogenannter Master, d.h. ein verantwortlicher Teilnehmer, definiert sein. In den meisten Fällen ist dies die CPU, es kann aber auch irgendein anderer Busteilnehmer mit Ausnahme des Memorys sein. Der Master übernimmt die Kontrolle des Transfers und startet das Handshaking. Die Tabelle I zeigt ein Beispiel eines Handshaking-Ablaufs und die Figur 2 das zugehörige Zeitdiagramm. Der Datentransfer wird übrigens auch zeitlich überwacht. Wenn auf das Aussenden der Adresse nicht innerhalb von 10 µs das BRPLY-Signal erscheint, reagiert der Bus-Master (CPU) mit einer Time-Out-Funktion.

Neben dem obenerwähnten DATI-(DataIn)-Zyklus kennt der Q-Bus noch folgende weitere Transferarten:

- DATO: DataOut

- DATOB: DataOutByte

- DATIO: DataInOut

- DATIOB: DataInOutByte

- DATBI: DataBlockInput

- DATBO: DataBlockOutput.

Diese weiteren Transferarten unterscheiden sich von der erstgenannten.

**Tabelle I Beispiel eines Handshaking-Prozesses**

Transfer eines 16-bit-Wortes vom Memory zur CPU (DAT I-Zyklus)

DATI Data In      BDIN Bus Data IN      BRPLY Bus Reply

**Figur 2 Beispiel: DATI-Bus-Zyklus**

Die obigen Zeitdiagramme zeigen als Beispiel die Timing-Signale an den Bus-Driver-Eingängen und Bus-Receiver-Ausgängen bei einem DATI-Bus-Zyklus (Dateneingaben), wobei (a) die Signale des Master und (b) die Signale des Slave-Gerätes wiedergibt.

T Bus-Driver-Eingang

R Bus-Receiver-Ausgang

(4) Undefinierte Zustände

Für Einzelheiten dazu wird auf die Dokumentation [1; 2; 3] verwiesen.

### 3. Spezielle Übertragungsmethoden

#### Direct-Memory-Access

Der Direct-Memory-Access (DMA) kennt im Prinzip die gleichen Transferarten wie der oben dargestellte Einzeltransfer. Beim DMA wird der Umstand ausgenutzt, dass der Prozessor den Bus nicht in jedem Moment gleich stark belastet. Der DMA-Transfer läuft in der Regel in den freien Zeitabschnitten und verbessert damit die Auslastung des Busses. Ein DMA-Transfer kann ohne Prozessorunterstützung bis 64 Kbyte von oder zum Memory übertragen.

#### Burst-DMA-Mode

Wie weiter oben erwähnt, wird durch die Reduktion des normalen DMA-Protokolls eine wesentlich höhere Durchsatzrate erreicht. Beim Burst-DMA-Mode behält – im Gegensatz zum normalen DMA, bei dem nach jedem Worttransfer die Kontrolle wieder an den Prozessor zurückgegeben wird – das burstinitialisierende Interface die Bus-Kontrolle bis ans Ende der Übertragung. Es können Datenblöcke bis zu 64 Kbyte in einem Burst übertragen werden.

#### Interrupt

Eine Synchronisation von verschiedenen schnell arbeitenden Systemkomponenten kann durch eine weitere Möglichkeit, den Interrupt, erreicht werden, wie anhand des folgenden Beispiels gezeigt wird.

Ein Programm auf dem Prozessor errechne irgendwelche Zahlenwerte, lege diese an bestimmten Stellen im Speicher (Memory) ab und sende sie zudem an einen Bildschirm. Da der Bildschirm im Vergleich zum Prozessor ein langsam arbeitendes Gerät ist, müsste man ohne spezielle Hilfsmassnahmen die CPU in eine Warteschleife zwingen (Zeichen an Bildschirm senden; warten, bis das Zeichen dargestellt ist; nächstes Zeichen senden usw.). Um dies zu verhindern, wurden zwei Teilprogramme entwickelt, die dieses Problem zusammen mit einem Hardwarezusatz lösen. Das erwähnte Rechnungsprogramm übergibt an definiertener Stelle die am Bildschirm darzustellenden Zeichen einer Ausgaberoutine. Diese schickt sie einzeln an

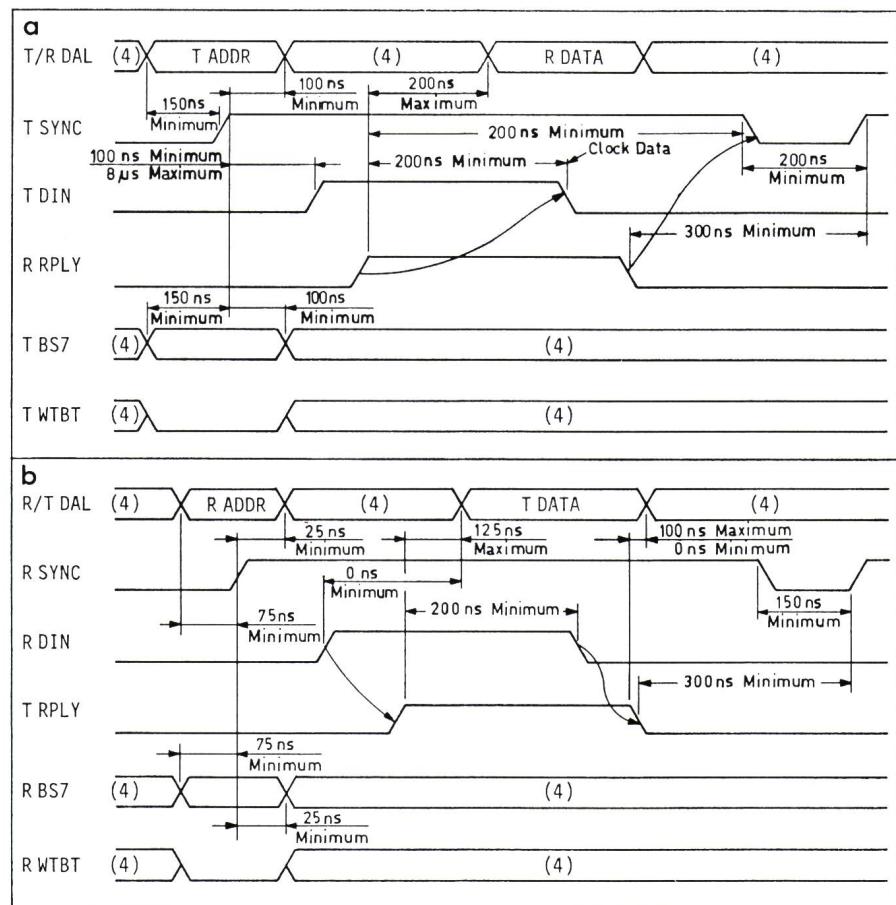

**Figur 3**

Zeitlicher Ablauf von Bus-Übertragungszyklen

— Interrupt-Zyklen

- - - - DMA-Zyklen

Die Blöcke stellen einzelne Zugriffe der CPU auf den Bus dar. Dazwischen laufen DMA- und Interrupt-Zyklen, wobei die letzteren nur am Ende einer kompletten Instruktionssausführung akzeptiert werden.

den Bildschirm, wobei sie die Programmkontrolle nach jedem Aussen- den eines Zeichens dem Rechenprogramm so lange zurückgibt, bis der Bildschirm oder vielmehr seine zugehörige Interfacekarte nach dem nächsten Zeichen verlangt. Das Rechenprogramm wird dann unterbrochen, und die Ausgaberoutine schickt das nächste Zeichen. Eine solche Übertragung wird Interrupt-Betrieb genannt. Praktisch alle Transfers von Daten, die nicht zu oder von der CPU laufen, werden auf diese Weise ausgeführt. Ausnahmen sind DMA- oder Burst-Transfers. Sie sind allerdings vom Interface abhängig.

Das Zeitdiagramm in Figur 3 erläutert die Abläufe für DMA, Interrupt und Einzelzyklen.

#### 4. Hardware

Der Q-Bus benützt für die Übertragung und die Interrupt-Möglichkeit folgende Signalleitungen:

- 16 Multiplex-Data-Adress-Leitungen

- 5 Multiplex-Adress-Leitungen für die Adressierung über 64 kByte

- 6 Datentransfer-Control-Leitungen

- 6 System-Control-Leitungen

- 10 Interrupt-Control- und Direct-Memory-Access-Leitungen

- einige +5-V-Speise- und Masseleitungen.

Die meisten dieser Leitungen sind bidirektional, d.h. die Signale können in Richtung CPU oder in Richtung Pe-

ripherie laufen. Einzig die Interrupt-Beantwortungsleitungen gehen vom Prozessor an die Peripherie. Sie sind im sogenannten Daisy-Chain-Verfahren durch die Interfacekarten der Peripherie geschlauft.

Der Bus besitzt eine feste Impedanz von  $220\ \Omega$ ; er ist am Anfang und am Ende entsprechend abgeschlossen. Die Signalabgriffe erfolgen über genormte Chips, die auf diese Impedanz Rücksicht nehmen. Die Signallogik ist negativ orientiert, d.h. ein Signal von 0 V stellt eine logische 1 dar.

#### 5. Zukünftige Entwicklung

Der Q-Bus löst den älteren UNIBUS, bei dem die Daten und Adressen zwar auf separaten Leitungen geführt werden, die Adressierbreite jedoch auf 18 bit limitiert ist, nach und nach ab. Man findet den handlicheren Q-Bus sogar als Peripherie-Bus der Micro-VAX, trotz deren 32-bit-Architektur. Der Grund dürfte darin liegen, dass für den Q-Bus bereits eine grosse Vielfalt von Interfacekarten existiert.

#### Literatur

- [1] PDP-bus handbook. (EB-17525-20). Maynard/Massachusetts, Digital Equipment Corporation.

- [2] PDP-11 architecture handbook. (EB-23657-18). Maynard/Massachusetts, Digital Equipment Corporation.

- [3] Supermicrosystems handbook. (EB-27713-41). Maynard/Massachusetts, Digital Equipment Corporation.

# LYNX-DIAMANT

## mit Sylvania's brillantem Adapter passt jetzt as modernste Licht in jede herkömmliche Fassung.

brauf viele gewartet haben: Eine Kompakt-Leuchtstoffröhre, die auch ohne das teure Vorschaltgerät ersetzt werden kann. Lynx-Diamant – das neue und revolutionäre, zeitige Lichtsystem.

Einerseits die energiesparende Lynx Kompakt-Leuchtstoffröhre – andererseits der neue, diamantförmige Adapter von Sylvania, dessen Lebensdauer der von 10 Lampen entspricht und der ausserdem mit einer 5jährigen Garantie versehen ist. Wenig Energieverbrauch, warmes, angenehmes Licht, einfacher Unterhalt und lange Lebensdauer verleihen dieser Lichtquelle glänzende Anwendungseigenschaften im Innen- und Außenbereich.

**Sylvania Lynx-Diamant – die brillante Verbindung.**

**Coupon:** Bitte senden Sie weitere Informationen über Sylvania Lynx-Diamant.

Name \_\_\_\_\_

Adresse \_\_\_\_\_

SEV

## SYLVANIA

## GTE

GTE SYLVANIA AG, 4, ch. des Léchères, 1217 Meyrin,

Tel. 022/82 00 72, Tx 28 233

# Wir kuppeln Computer.

Ihre Computer der Netzeleittechnik, Kraftwerkleittechnik oder Industrieleittechnik wie auch Ihre Computer in Büro, Konstruktion, Werkstatt und Lager lassen sich sinnvoll miteinander verbinden. Zu Ihrem Vorteil.

**Mit dem

Partnerbus\*

von BBC.**

\*Der BBC-Partnerbus® ist ein Kommunikationssystem für lokale Rechner-Netzwerke mit verteilten Datenverarbeitungsaufgaben.

Bitte senden Sie mir weitere Unterlagen über den BBC-Partnerbus.

Firma \_\_\_\_\_

Name \_\_\_\_\_

Strasse \_\_\_\_\_

PLZ/Ort \_\_\_\_\_

Tel. \_\_\_\_\_

BBC Brown Boveri AG

Informationstechnik

CH-5401 Baden/Schweiz

Verkauf Leittechnik Schweiz

Weltpoststrasse 20, Postfach 266, 3000 Bern 15

Telefon 031/43 47 01, Telex 912 062 bb ch

**BBC**

BROWN BOVERI