|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 79 (1988)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 1                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Bussysteme : Systemphilosophien                                                                                                                                                                                           |

| <b>Autor:</b>       | Zemp, F.                                                                                                                                                                                                                  |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-903963">https://doi.org/10.5169/seals-903963</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

## Bussysteme – Systemphilosophien

F. Zemp

**Bei Mikroprozessorsystemen werden alle Daten und Kontrolls Signale zwischen den Systemkomponenten über ein gemeinsames Leitungssystem, den Systembus, ausgetauscht. Trotz Standardisierungsbemühungen haben sich in der Vergangenheit verschiedene Bussysteme entwickelt, die mehr oder weniger stark den jeweiligen Stand der Mikrocomputertechnologie und die Systemphilosophie des betreffenden Herstellers widerspiegeln. Dieser Beitrag befasst sich mit den Überlegungen, die den verschiedenen Entwicklungen zugrunde liegen, und gibt eine ordnende Übersicht über die verschiedenen Busrepräsentanten.**

**Avec les systèmes à microprocesseurs, toutes les données et les signaux de contrôle sont échangés entre composants du système par un système de conduite commun, le bus. Malgré des tentatives de normalisation, divers systèmes de bus se sont développés, qui représentent plus ou moins l'état du moment de la technologie des micro-ordinateurs et la philosophie de système du fabricant respectif. Cet article concerne les considérations à la base des divers développements et donne un aperçu ordonné des différents genres de bus.**

### Adresse des Autors

Fritz Zemp, dipl. Ing. HTL, W. Moor AG,

Bernstrasse 34, 3072 Ostermundigen.

Die Aufgabe eines Mikrocomputerbusses ist grundsätzlich nichts Spektakuläres. Er hat die Verbindung von Systemkomponenten wie z.B. Speicher oder Ein- bzw. Ausgabegeräte und einem oder mehreren Mikroprozessoren sicherzustellen. Und doch hat die Wahl einer Busstruktur nach wie vor tiefgreifende Konsequenzen auf die Leistungsfähigkeit und Ausbaubarkeit eines Computersystems. Trotz Standardisierungsbemühungen zeichnet sich noch immer kein eindeutiger Trend für das eine oder andere System ab. Der Anwender muss deshalb bei der Systemevaluation ein relativ breites Angebot an seinen Anforderungen messen. Will er sich dabei nicht in den Details verlieren, so muss er einige grundlegende Begriffe kennen, die im folgenden erklärt werden [1].

### 1. Aufbau von Bussystemen

#### Physikalischer Aufbau

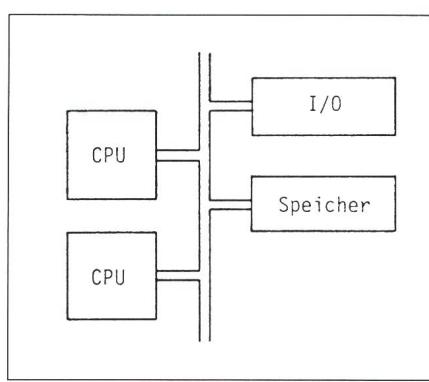

Physikalisch besteht ein Mikrocomputerbus aus einer Anzahl elektrischer Verbindungsleitungen. Die diversen Funktionseinheiten eines Computersystems (CPU, Memory, I/O) werden über einen einfach strukturierten Backplanebus miteinander zu einem Gesamtsystem (Fig. 1) verknüpft. Dieses Bussystem besteht meist aus einem

unidirektionalen *Adressbus* und einem *Datenbus*, auf dem die Daten in beiden Richtungen (bidirektional) transferiert werden. Ein unidirektionaler Kontroll- oder *Steuerbus* wird für die Steuerung bzw. Synchronisierung der Transfers und Interruptleitungen eingesetzt.

Die Hardwarespezifikationen (Anzahl und Layout der Signalleitungen, Busanschlüsse usw.) und die elektrischen Anforderungen (Leitungsimpedanz, -länge, Signalform, Leitungsabschluss) definieren die physikalische Umgebung. Eine Busformatspezifikation definiert Anzahl und Breite des Adress- und Datenbusses (8, 16, 32 bit) und beschreibt zudem die Funktion der Bus-Kontrolleitungen.

#### Übertragungsarten

Die Signale können seriell (2-Drahtleitung) oder parallel (8, 16 oder 32 bit) übertragen werden. In diesem Artikel werden ausschliesslich parallele Bussysteme besprochen.

Oft werden aus Gründen der Komplexität bzw. des hohen Bedarfes an Daten-, Adress- und Kontrolleitungen die vorhandenen Leitungen doppelt belegt. So können beispielsweise Daten und Adressen nacheinander über die gleiche Leitungsgruppe übertragen werden (Multiplexed Lines).

#### Busanschlussbausteine

Für den Anschluss verschiedener Geräte bzw. Einrichtungen stehen zwei oft gebräuchliche Anschluss schaltungen zur Verfügung:

- der Open-Collector/Open-Drain-Output (Wired-OR) mit einem Pull-up-Widerstand zur Verhinderung von Signalstörungen,

- der Totem-Pole-Output (TTL, Tri-state) mit einem dritten, undefinierten logischen Zustand, der sich sehr gut eignet, um ein Gerät vom Bus loszulösen. Diese Schaltungsart

Figur 1 Einfache Busarchitektur

wird bei neuen Bussystemen bei einer Vielzahl von wichtigen Leitungen verwendet.

## Busabschluss

Viele am Bus angeschlossenen Elemente beeinflussen die Form und den Ablauf der Bussignale. Um Übertragungsprobleme (Reflektionen, Übersprechen) auf dem Bus zu vermeiden, wird dieser meist mit einem definierten Widerstand an den entsprechenden Enden abgesichert. Viele Bushersteller schreiben die Länge ihres Busses exakt vor. Es ist zudem darauf zu achten, dass bei Buserweiterungen (Anschluss einer weiteren Rechnerbox) die Herstellerangaben genau befolgt werden.

## Busmanagement

Ein aktueller Busmaster initialisiert und organisiert den Datentransfer. Meist übernimmt der Mikroprozessor die Master-Rolle, während alle anderen Elemente als Slaves gesteuert werden. Mit zusätzlichen Bus-Kontrolleitungen kann die Buskontrolle (Master) temporär an andere Systemteilnehmer abgegeben werden (DMA: direkter Speicherzugriff ohne CPU-Kontrolle). Weitere Leitungen werden benötigt, wenn mehrere CPU auf einem Bussystem integriert werden sollen.

## Buskommunikationsprotokoll

Geräte, welche über den Bus kommunizieren wollen, müssen sich an ein bestimmtes, vom Bus vorgegebenes Kommunikationsprotokoll halten. Jeder Hersteller schreibt die für seinen Bus gültigen Bedingungen mit einem entsprechenden Busprotokoll vor. Jedes am Bus angeschlossene Gerät muss sich an diese Spezifikationen halten. Im allgemeinen können Busoperationen in drei Phasen ablaufen:

### 1. Devicesynchronisation:

Ein am Bus angeschlossenes Gerät (Slave) teilt dem Busmaster, z.B. einer CPU, mit, dass es Daten übertragen möchte (Request). Wenn die Anfrage vom Busmaster geprüft wurde und der entsprechende Slave die höchste Priorität im System besitzt, initialisiert der Master einen Datentransfer.

### 2. Busallokation

Der Master verlangt nun die Kontrolle über den Bus. Wenn der Bus frei wird und zudem der Master die höchste Priorität besitzt, erhält er die Kontrolle.

### 3. Datentransfer

Der Busmaster teilt nun dem Slave mit, dass der Transfer stattfinden kann. Der Slave bestätigt, und der Datentransfer läuft ab.

Die drei Phasen laufen in einer definierten Sequenz ab, die durch das Busprotokoll vorgeschrieben ist. Jedes am Bus angeschlossene Gerät enthält eine Schaltung, welche den Transfermechanismus kennt und somit die entsprechenden, dafür vorgesehenen Kontrollsignale bedient. Man unterscheidet folgende Busprotokoll-Hauptrichtungen:

- *Synchrone Datenübertragung*: Der Datentransfer läuft synchron zu einem zentralen, definierten Bustakt ab. Wenn beispielsweise der Busmaster Daten zu einem Busslave senden möchte, zeigt er dem Slave das Vorhandensein eines Datenwortes mit einer einzelnen Kontrolleitung Data Ready an. Der Slave muss in der Lage sein, dieses Wort in einer definierten Zeit zu übernehmen, sonst geht die Information verloren. Es ist oft schwierig, Geräte mit unterschiedlichen Übertragungsgeschwindigkeiten im gleichen System ohne Leistungsverlust zu kombinieren. Der Hauptvorteil dieses Protokolls liegt in seiner Einfachheit und in einer gleichmässigen, vom zentralen Bustakt bestimmten Übertragungsgeschwindigkeit.

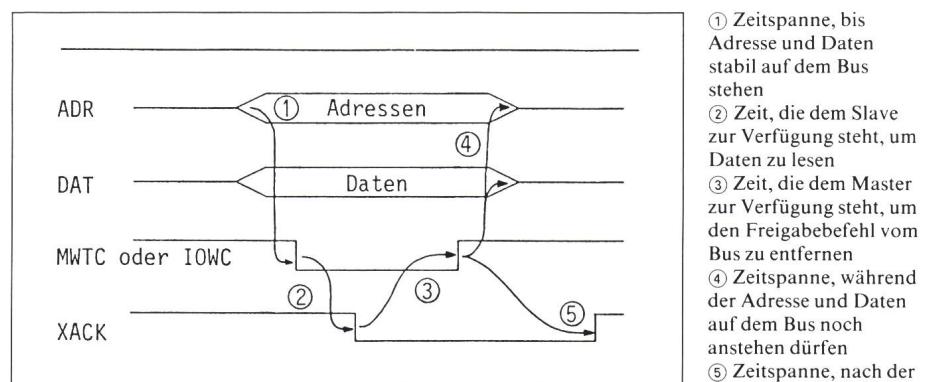

- *Asynchrone Datenübertragung*: Zwei Kontrollsignale (Data Request, Data Ready) werden benutzt, um Geräte, welche Daten über einen Bus austauschen wollen, zu synchronisieren. Die asynchrone Synchronisierungsmethode (Fig. 2), oft auch Handshaking genannt, erlaubt auch Geräte mit unterschiedlicher Arbeitsgeschwindigkeit

optimal zu bedienen. Je nach Komplexität des Bussystems werden die zeitlichen Abläufe dieses Protokolltyps zusätzlich gruppiert (Noninterlocking, Halfinterlocking, Fully Interlocking). Zudem kann eine weitere Steuerleitung für speziell sichere Übertragung zugezogen werden (z.B. Laborbus IEEE 488).

- *Semisynchrone Datenübertragung*: Dieses Protokoll ergänzt das schnelle, einfache Synchronprotokoll mit einem zusätzlichen Kontrollmechanismus für die langsamsten Teilnehmer. Realisiert wird der asynchrone Anteil mit einem *Wait-Kontrollsignal*. Diese Signalleitung kann beispielsweise von einem langsamen Gerät benutzt werden, um den Master anzuhalten, bis der Datentransfer korrekt abgelaufen ist.

## Durchsatz, Grenzen

Die in den vorangegangenen Punkten aufgeführten Fakten zeigen, dass Leistungsgrenzen gesetzt sind. Neben physikalischen Grenzen (Busabschluss, -länge, -breite) kann auch die Art und Weise, wie der Transfer organisiert wird (asynchron, synchron), die Leistungsbandbreite eines Busses massgebend beeinflussen. Heutige Bussysteme sind für einen Arbeitsbereich von 10 bis 40 MHz ausgelegt [2].

## 2. Von einfachen zu komplexen Busarchitekturen

Für neuere, leistungsfähigere Mikroprozessorsysteme genügt meist die *Einfachbus-Architektur* (Fig. 1) nicht mehr. Die stetige Weiterentwicklung

**Figur 2 Beispiel eines asynchronen Busprotokolls**

Speicher oder I/O-Schreibzyklus beim Multibus I. Der aktuelle Bus-Master gibt zuerst Adresse und Daten auf den Bus und dann den Freigabebefehl MWTC oder IOWC (Memory oder I/O), der vom aktuellen Bus-Slave mit XACK (Acknowledged) bestätigt wird.

- ① Zeitspanne, bis Adresse und Daten stabil auf dem Bus stehen

- ② Zeit, die dem Slave zur Verfügung steht, um Daten zu lesen

- ③ Zeit, die dem Master zur Verfügung steht, um den Freigabebefehl vom Bus zu entfernen

- ④ Zeitspanne, während der Adresse und Daten auf dem Bus noch anstehen dürfen

- ⑤ Zeitspanne, nach der XACK vom Bus entfernt sein muss

# Übersicht

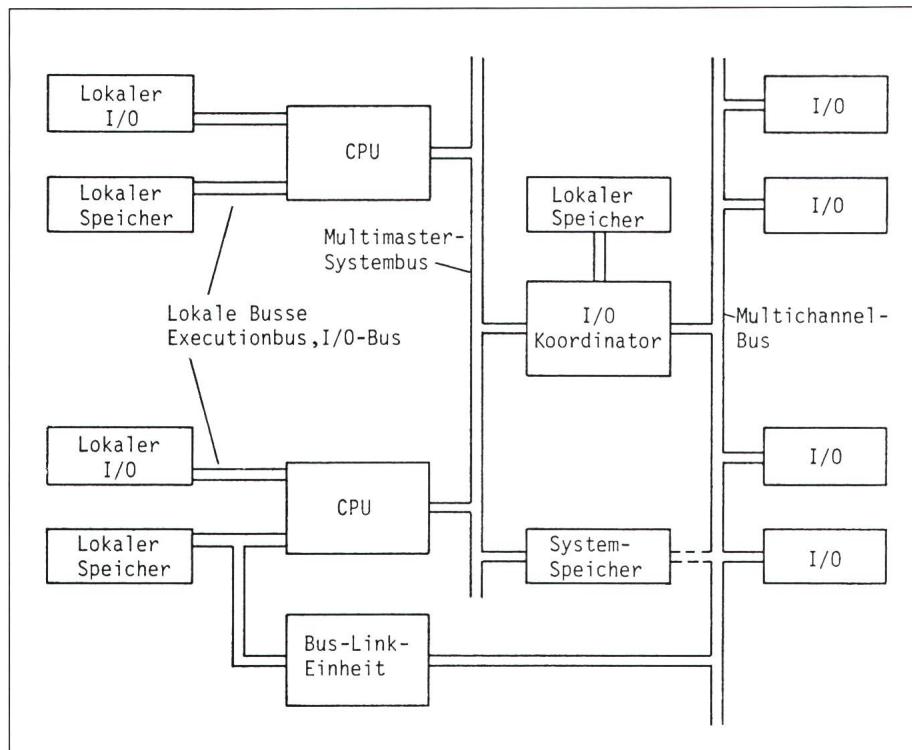

der Komponenten wie CPU und Memory sowie die immer höher werden den Anforderungen an die verschiedenen Computersystemkomponenten haben die Entwickler von Bussystemen vor neue Probleme gestellt. Betrachtet man zudem die verschiedenen Übertragungscharakteristiken der beteiligten I/O-Komponenten, so ist leicht zu erkennen, dass mit einer einheitlichen Architektur nicht mehr alle Aufgaben gelöst werden können. So werden vor allem Speichertransaktionen und eigentliche I/O-Transaktionen unterschieden. Es wird nicht mehr ein einzelner Bus verwendet, sondern mehrere Bussysteme werden in eine *Hierarchie* (Fig. 3) eingeordnet, wo jeder einzelne Bus für eine ganz spezifische Funktion optimiert ist. Das System wird dabei in folgende Funktionsgruppen eingeteilt:

- *Multimaster-Systembus*: Der multimasterfähige Systembus verknüpft die diversen Funktionsgruppen miteinander und dient vor allem der Kommunikation und dem gemeinsamen Datenaustausch.

- *Multichannel-Bus*: Ein I/O-Koordinator bedient die auf dem Multichannel-Bus zusammengefassten, systemweiten I/O-Einheiten (Harddisk, Hochleistungsgeräte). Mit einem auf dem vorgesehenen lokalen Koordinatorenpeicher geladenen Programm kann der Datenfluss gesteuert und zum Teil gar vorverarbeitet werden (zusätzliche Systembuslastung).

- *Lokale Bussysteme*: Sie können den hohen Geschwindigkeitsanforderungen neuer Mikroprozessoren und Komponenten genügen. Mit dem lokalen (residenten) Speicher kann jede CPU autonom arbeiten. Die Leistungsfähigkeit des Gesamtsystems steigt wesentlich. Der Systembus wird nicht mehr wegen jeder einzelnen Instruktion, die von einer der beiden CPU abgearbeitet wird, belastet. Eine vom I/O-Koordinator gesteuerte I/O-Bus-Lokalbus-Link-Einheit ermöglicht den direkten Datentransfer von I/O-Einheiten über den I/O- und den lokalen Speicherbus in den lokalen Speicher.

Die Komplexität eines solchen leistungsfähigen Bussystems erfordert ein Miteinbeziehen von spezieller Bussteuerintelligenz. Zudem verwenden einige Hersteller bereits spezielle Busadapterbausteine, welche die für den Bus vorgesehenen Protokolle enthalten (z.B. Multibus II, BI-Bus).

fest, dass sich die Technologie der hochintegrierten Bausteine in den letzten Jahren extrem rasch entwickelt hat. Diese extreme Entwicklungsgeschwindigkeit hat sich auch auf die Kartenebene (Boardebene) übertragen. Mit immer neuen Standards bzw. Standardisierungsversuchen hoffen die Hersteller, zusehends leistungsfähigere, universelle Systeme auf den Markt zu bringen. Das wiederum bedeutet, dass auch bei der Auslegung der Bussysteme immer wieder neue Aspekte berücksichtigt werden müssen. Nachfolgend sollen diverse, auf dem Markt mehr oder weniger erfolgreiche Bussysteme kurz vorgestellt werden.

## 8/16-bit-Busstandards

Die in der Tabelle I aufgeführten Bussysteme sind wichtige Vertreter dieser Computergeneration [5; 6]. Trotz 32-bit-Trend können sich einige dieser Systeme nach wie vor behaupten. So verfügt der IEEE-standardisierte Multibus von Intel bereits über eine effiziente Bushierarchie, der Q-Bus [7; 8] von DEC wird nach wie vor (mit zusätzlichem, lokalem 32-bit-Memorybus) für die 32-bit- $\mu$ VAX-Computer verwendet, und der IEEE-488-Laborbus (Hewlett Packard) hat sich als Gerätebusstandard etabliert.

## 3. Busstandards

Beobachtet man die Entwicklung des Mikrocomputers, so stellt man

## 32-bit-Busstandards

Die Tabelle II zeigt die neuesten Vertreter [9; 10] der 32-bit-Bus-Generation. Die Komplexität der Systeme geht heute soweit, dass für Bussteuerung, -management und -zugriff bereits vom Hersteller zur Verfügung gestellte Bausteine (Lizenzen) eingesetzt werden müssen (Multibus-II, VAX-BI). Trotz diesen Einschränkungen versuchen die Bushersteller offenkundigere bzw. mikroprozessorunabhängige Systeme anzubieten [11]. Beispiel: Der am MIT entwickelte NuBUS, welcher bereits von einigen bekannten Computer- bzw. Prozessorherstellern (Apple Macintosh II und Texas Instruments) verwendet wird.

## 4. Zukunft

Neue Technologien (Übertragungsmedien, Fertigungstechnik) und auch neue CPU- bzw. Systemarchitekturen können die Leistungsgrenzen bestehender Bussysteme und -philosophien sprengen.

Figur 3 Hierarchische Busarchitektur

|                        | <b>VMEBus</b>                     | <b>Futurebus</b>                  | <b>Multibus II</b>                 | <b>NuBus</b>                  | <b>Fastbus</b>     | <b>VAX BI</b>           |

|------------------------|-----------------------------------|-----------------------------------|------------------------------------|-------------------------------|--------------------|-------------------------|

| Bus Protokoll          | asynchron                         | asynchron                         | synchron<br>10 Mhz Clock           | synchron<br>10 Mhz Clock      | asynchron          | synchron<br>5 Mhz Clock |

| Datenbreite            | nicht multipl.                    | multiplexed                       | multiplexed                        | multiplexed                   | multiplexed        | multiplexed             |

| Primär:                | 16 bit                            | 32 bit                            | 32 bit                             | 32 bit                        | 32 bit             | 32 bit                  |

| Sekundär:              | 32,24,16 u. 8 bit                 | 32,24,16 u. 8                     | 32,24,16 u. 8                      | 32,16 u. 8                    | --                 | 32,16,8                 |

| Adressbereich          | $2^{24}$ (byte)                   | $2^{32}$ (byte)                   | $2^{32}$ (byte)                    | $2^{32}$ (byte)               | $2^{32}$ (4 bytes) | $2^{30}$ (byte)         |

| erweiterbar            | $2^{32}$ (byte)                   | ja                                | nein                               | nein                          | ja                 |                         |

| I/O                    | $2^{16}$ (byte)                   | --                                | $2^{16}$ (byte)                    | --                            | --                 |                         |

| Multiprozessor-support | ja                                | ja                                | ja                                 | ja                            | ja                 | ja                      |

| Bandbreite             | 20(57) Mbyte/s                    |                                   | 40 Mbyte/s                         | 37,5 Mbyte/s                  |                    | 13,3 Mbyte/s            |

| Stecker / Anschluesse  | 2/128<br>IEC 603-2/2x96           | 1/96<br>IEC 603-2/96              | 1/96<br>IEC 603-2/96               | 1/96<br>IEC 603-2/96          | 1/130              | 2/120                   |

| Bus Interface          | TTL Tri-state<br>u.Open Collector | BTL Backplane<br>Tranceiver Logic | TTL Tri-state u.<br>Open Collector | TTL Tri-state<br>u.Open Coll. | ECL                |                         |

| Anzahl Module          | 21                                | 21                                | 20                                 | 16                            | 26                 |                         |

Tabelle I 8/16-bit-Bussysteme

|                        | <b>Gen. Purpose Interface Bus</b><br>IEEE 408/1978<br>(IEC 625) | <b>Multibus (I)</b><br>IEEE 796/1984 | <b>STD Bus</b><br>MOSTEK 1978      | <b>S100 Bus</b><br>IEEE 696/1982 | <b>LSI-11 Bus</b><br>DEC / 1979 | <b>STE Bus</b><br>IEEE 1000/1984                   |

|------------------------|-----------------------------------------------------------------|--------------------------------------|------------------------------------|----------------------------------|---------------------------------|----------------------------------------------------|

| Bus Protokoll          | asynchron<br>(3 Kontr.leitungen)                                | asynchron                            | semisynchron                       | synchron                         | asynchron                       | asynchron                                          |

| Datenbreite            | multiplexed                                                     | nicht multipl.                       | nicht multipl.                     | nicht multipl.                   | multiplexed                     | nicht multipl.                                     |

| Primär:                | 8 bit                                                           | 16 bit                               | 8 bit                              | 16 bit                           | 16 bit                          | 8 bit                                              |

| Sekundär:              |                                                                 | 16/8 bit                             |                                    | 16/8 bit                         | 16/8 bit                        | --                                                 |

| Adressbereich          | 15                                                              | $2^{20}$ (byte)                      | $2^{16}$ (byte)                    | $2^{16}$ (byte)                  | $2^{22}$ (byte)                 | $2^{20}$ (byte)                                    |

| erweiterbar            | ja                                                              | --                                   | --                                 | $2^{24}$                         | --                              | --                                                 |

| I/O                    |                                                                 | $2^{12}$                             | --                                 | $2^{16}$                         | --                              | $2^{12}$                                           |

| Multiprozessor-support | --                                                              | ja                                   | --                                 | ja                               | --                              | --                                                 |

| Bandbreite             | 1 Mbyte/s                                                       | 10 Mbyte/s                           |                                    | 16 Mbyte/s                       |                                 |                                                    |

| Stecker / Anschluesse  |                                                                 | 2/86 u. 60                           | 1/56                               | 1/100                            | 2/72                            | 1/64                                               |

| Bus Interface          | TTL Tri-state<br>u.Open Collector                               | TTL Tri-state u.<br>Open Collector   | TTL Tri-state u.<br>Open Collector | TTL Tri-state<br>u.Open Coll.    | Open Collector                  | TTL Tri-state u.<br>120-Ohm-Abschl. Open Collector |

| Anzahl Module          | 15                                                              |                                      | 24                                 | 22                               | 24                              | 21                                                 |

Tabelle II 32-bit-Bussysteme

## Neue Architekturen

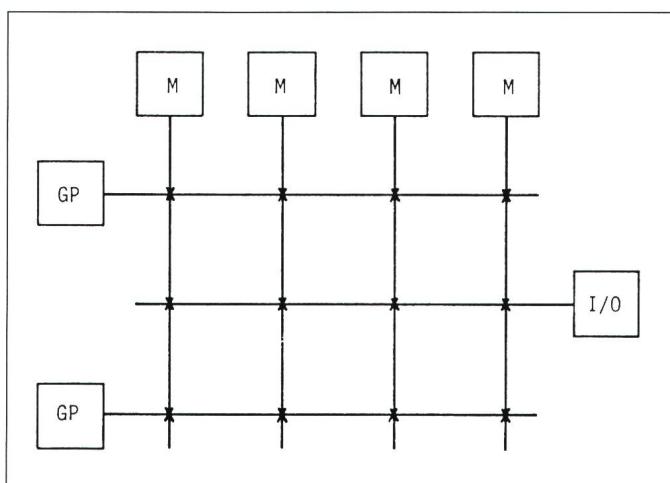

Eine neue Busform [8] stellt das Kreuzschienenbuskonzept (iAPX-432 Intel) dar (Fig. 4). Bei dieser Architektur wird die Problemstellung des Bussystems verallgemeinert. Im Gegensatz zur komplexen, in verschiedene Subsysteme eingeteilten Bushierarchie ist hier jedes einzelne Buselement gleich wie die anderen. Es existiert keine Funktionsunterteilung. Jede Speicher-Einheit kann je nach Durchschalten der Kreuzpunkte als globaler oder lokaler Speicher aufgefasst werden.

Obwohl das Konfigurieren dieses Systems aufwendig ist, dürfte dies die typische Buskonfiguration für Höchstleistungssysteme der Zukunft sein. Ein ähnlicher Lösungsansatz kann beispielsweise auch im Transputer-Kommunikationsmodell beobachtet werden. Obgleich diese CPU-Architektur vor allem die Multimastereigenschaften speziell unterstützt, werden hier bereits wichtige Buseigenschaften in die CPU-Architektur (Kommunikation) verlegt.

## Optische Datenübertragung

Die immer höher werdenden Leistungsanforderungen an neue Bausteine können mit elektrischen Signalen nicht mehr umfassend und schnell genug erfüllt werden. Licht als neuer Informationsträger verspricht das Vehikel für diese zukünftigen Engpässe zu werden [12]. In der Kommunikationsindustrie beginnt sich die Glasfaser als der neue Übertragungswerkstoff durchzusetzen. Auf dem Netzwerkmarkt werden bereits auf Glasfasern basierende LAN (Lokale Netzwerke) angeboten. Forschungsarbeiten für neue Übertragungsstrecken mit bis zu 560-Mbit/s-Kapazität für die Tele-

phonie lassen erahnen, welches Potential sich hinter dieser neuen Technologie verbirgt. Die Integration dieser optischen Übertragungsstrecken in eine vorwiegend mit elektrischen Schaltungen realisierte Umgebung ist zurzeit das Hauptproblem.

Eine optische Verbindung besteht grundsätzlich aus einer Quelle, einem optischen Leiter und einem Empfänger. Die Quelle konvertiert ein ankommendes elektrisches Signal in ein optisches Signal (Laserdiode). Dieses Signal wird über ein lichtleitendes Medium (Luft, Glas, Glasfaser) an einen Empfänger weitergeleitet. Dieser detektiert den Lichtstrahl, wandelt ihn in einen elektrischen Strom um und verstärkt diesen auf die erforderlichen Signalwerte. Diese optisch-elektrische bzw. elektrisch-optische Schnittstelle ist es, welche zurzeit noch viel Kopfzerbrechen bereitet bzw. einen immensen Entwicklungsaufwand erfordert (genaueste Anpassungen, Temperaturschwankungen). Dass man auf dem Weg ist, diese Probleme in den Griff zu bekommen, zeigen aktuelle Forschungsergebnisse. Neue Bausteine sind in der Lage, gleichzeitig bis zu 16 Kanäle elektrisch-optisch oder umgekehrt zu wandeln (Ziel: 256 und mehr).

Wenn man bedenkt, dass die Leistungsbandbreite eines heutigen Parallelbusses im Schnitt 640 Mbit/s (32 bit bei 20 MHz) beträgt, so würden die grossen Vorteile der optischen Übertragungstechnik (geringer Stromverbrauch, hohe Signalunempfindlichkeit, hohe Leitungsbandbreite) bereits heute eine Anwendung finden.

## 5. Zusammenfassung

Die Vielfalt der verschiedenen Mikroprozessorprodukte (1985 mehr als

30 Grundstrukturen), immer leistungsfähigere CPU (32 bit) und höhere Benutzeranforderungen erschweren die Entwicklung eines einheitlichen, standardisierten Bussystems erheblich. Ein heutiges Bussystem soll Aspekte wie Einfachheit, Betriebssicherheit, Wartungsfreundlichkeit, möglichst hohe Prozessortypunabhängigkeit berücksichtigen. Zudem soll es – wenigstens für die nahe Zukunft – für die Integration von neueren, noch leistungsfähigeren Bausteinen (CPU, Memory, I/O) offen sein.

Die Forderung nach *einem* hersteller-unabhängigen Busstandard ist offensichtlich ebenso unrealistisch wie die Forderung nach einer universellen bzw. allesumfassenden Programmiersprache. Wir werden uns nach wie vor mit diversen Standards (Industrie, IEEE usw.) auseinandersetzen müssen.

## Literatur

- [1] A. L. Dexter: Microcomputer bus structures and bus interface design. New York/Basel, Marcel Dekker, 1986.

- [2] J. Beaston: Multiprocessor bus is ready to meet 32-bit applications of future. Electronics 57(1984)6, p. 126...131.

- [3] J. Geyer: Multibus II: 32-bit-Bus für leistungsfähige offene Systeme. Elektronik 32(1983)26, S. 32..37.

- [4] M. Gut: Multibusarchitektur und Kartencomputersysteme. Elektroniker 22(1983)19, S. 49...60.

- [5] D. Bursky: The S-one hundred bus handbook. London, Hayden, 1980.

- [6] M. Campo: The evolution of the STD bus. Electronic Engineering 56(1984)689, p. 105...108.

- [7] Microcomputer processor handbook. LSI-11 bus. Maynard/Massachusetts, Digital Equipment Corporation, 1979.

- [8] VAX hardware handbook. Volume 2. Maynard/Massachusetts, Digital Equipment Corporation, 1987.

- [9] P. L. Borrill: 32-bit-buses, an objective comparison. Malton/North Yorkshire, Spectra-Tek, 1985.

- [10] M. Rudyk: VME-Bus. Modulares Konzept für µC-Karten mit Europaformat. Elektronik 31(1982)10, S. 90...96.

- [11] M. Amundsen u.a.: Kompakt-Lisp-Maschine. Design und Elektronik -(1986)14, S. 12...16.

- [12] L. D. Hutcheson: Optical interconnects replace hardwire. IEEE Spectrum 24(1987)3, p. 30...35.

**Figur 4**

**Kreuzschienenbus**

Kreuzschienen-

element