|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 79 (1988)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 15                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | Prozessrechner mit verteilter Intelligenz und offener Systemarchitektur                                                                                                                                                   |

| <b>Autor:</b>       | Klett, R.                                                                                                                                                                                                                 |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-904059">https://doi.org/10.5169/seals-904059</a>                                                                                                                                   |

### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Prozessrechner mit verteilter Intelligenz und offener Systemarchitektur

R. Klett

**Auf dem Gebiet der Prozessleittechnik kann – bedingt durch die Möglichkeiten der Mikroelektronik – ein starker Trend zur Modularisierung der Soft- und Hardware festgestellt werden. Der vorliegende Beitrag zeigt diese Entwicklung am Beispiel des neuesten AEG-Realzeitrechner-Projektes, welches Teil eines viel grösseren Entwicklungsvorhabens des AEG-Geschäftsbereiches Automatisierungssysteme ist.**

**Dans le domaine des techniques de gestion process on peut constater – grâce aux possibilités de la microélectronique – une tendance prononcée vers la modularisation du logiciel et du matériel. Le présent article montre cette évolution à l'exemple du dernier projet de AEG portant sur le calculateur en temps réel, qui n'est que partie d'un projet de développement bien plus vaste de la division automatismes de AEG.**

Im Maschinenbau ist die möglichst umfangreiche Verwendung von Normteilen längst eine Selbstverständlichkeit. Die sehr junge Computer-Industrie ging und geht zumindest in grossen Bereichen auch heute noch einen anderen Weg. Einerseits wollen nämlich die Computer-Entwickler bei Neuentwicklungen die Ergebnisse des technischen Fortschritts berücksichtigen und ihre neuen Rechner optimieren, und andererseits wollen sich die Computer-Hersteller durch speziell ausgelegte Architekturen am Markt abgrenzen. Dies geschieht durch die Verwendung von zu anderen Herstellern inkompatiblen Elementen, vom Befehlssatz über die Speicherverwaltung und -adressierung bis zur Ein-Ausgabeschnittstelle und zum Betriebssystem (Fig. 1). Eine feste Bindung des Kunden an einen Hersteller

ist die Folge dieser Abgrenzung; der Wechsel zu einem anderen, inkompatiblen Rechnersystem wäre nämlich allzu aufwendig. In der letzten Zeit wird es nun aber zunehmend schwieriger, diese Abgrenzung beizubehalten, weil

1. die Anwender die Hersteller unter Druck setzen, ihre Systeme zu öffnen, und

2. die Hersteller sich bei der markt- und zeitgerechten Weiterentwicklung ihrer Produkte rapide steigenden Kosten gegenübersehen.

Dies hat bereits zu ersten Normen und Standards geführt. Elemente wie SDLC oder HDLC, Ethernet oder SCSI, aber auch die Sprachen Fortran oder C sind heute nicht mehr wegzudenken.

Figur 1 Schnittstellenprobleme

Der Beitrag entspricht dem Fachreferat, das der Autor am 22. Technischen Presse-Colloquium der AEG am 29./30. Oktober 1987 in Konstanz gehalten hat.

## Adresse des Autors

Dipl.-Ing. Rolf Klett, Geschäftsführer der Modular Computer GmbH, AEG-Geschäftsbereich Automatisierungssysteme, 7750 Konstanz.

## In Zukunft mehr Standards

Die Normen hatten bisher vorwiegend «nach aussen gerichtete» Schnittstellen zum Inhalt. Dies wird sich in den nächsten Jahren aber ändern. Die Standardisierung wird sich ins Innere der Computer fortsetzen, wobei sich allerdings weniger echte Normen, sondern durch grosse Halbleiterhersteller am Markt sich herausbildende Quasistandards durchsetzen werden. Dies wird auch bei Realzeitrechnern, die wegen ihrer Spezialisierung für Normungen bisher nur sehr begrenzt zugängig waren, zu veränderten Systemstrukturen führen.

Realzeitrechner unterscheiden sich von Computern der kommerziellen Datenverarbeitung im wesentlichen durch kurze Programmwechselzeiten, kurze Interrupt-Reaktionszeiten, hohe Ein-Ausgabe-Raten sowie durch Betriebssysteme mit vorhersagbarem zeitlichem Verhalten.

Wesentliche auslösende Momente für den erwähnten Strukturwandel sind:

- der Hardware-Preiszerfall und steigende Entwicklungskosten (vollständig neue Architekturen sind nur noch amortisierbar, wenn wenigstens 50000 Stück abgesetzt werden können),

- preiswerte Mikroprozessoren und Speicher, mit denen man grosszügiger umgehen kann,

- die zunehmende Leistungsfähigkeit der Mikroprozessoren (1987 5 MIPS<sup>1</sup>, 1988 10 MIPS und 1991 voraussichtlich 50 MIPS<sup>1</sup>),

- der Druck zu quasistandardisierten Betriebssystemen,

- die steigenden Anforderungen an die Produktpalette (die meisten Hersteller werden nicht mehr in der Lage sein, ein vollständiges Produktspektrum allein zu entwickeln),

- der Wille der Hersteller zur Unabhängigkeit von den Halbleiterherstellern,

- der Wille der Anwender, auf dem freien Markt Standard-Anwender-Software kaufen zu können.

Die neuen Realzeitrechner-Architekturen werden dadurch gekennzeichnet sein, dass ein Computer aus mehreren Prozessoren besteht, die selbst aus Mikroprozessoren mit möglicherweise

### Definition

- Austausch oder Hinzufügen von Komponenten erfordert keine Änderung in bereits vorhandenen Komponenten

- Komponenten (Prozessoren, Betriebssysteme) verschiedener Hersteller sind kombinierbar

### Ziel

- Optimale Komponentenauswahlmöglichkeit

- Bessere Erweiterungs- und Modernisierungsmöglichkeiten

### Voraussetzung

- Kommando- und Datenaustausch zwischen den Komponenten über ein internes Bussystem

- Einheitliches Datenübertragungsprotokoll für das Bussystem

- Einheitliche Aufbautechnik (Formate der Steckleinheiten)

**Tabelle I Offene Systemarchitektur**

unterschiedlicher Struktur aufgebaut sind. In einem Computer laufen mehrere quasistandardisierte Betriebssysteme mit unterschiedlichen Eigenschaften ab, und intelligente Komponenten innerhalb des Computers werden über standardisierte, schnelle Bussysteme miteinander kommunizieren. Es wird eine offene Struktur, d.h. eine Struktur mit standardisierten Schnittstellen sein, in die unterschiedliche Komponenten mit dedizierter Intelligenz integriert werden.

## Offene Systemarchitektur

Ein offenes System ist dadurch gekennzeichnet, dass durch das Hinzufügen oder Austauschen von Komponenten verschiedener Hersteller zwar die Systemeigenschaften verändert werden, bereits vorhandene Komponenten aber deswegen nicht verändert

werden müssen. Dieses setzt voraus, dass alle Komponenten über eine oder mehrere festgelegte Schnittstellen verfügen und dass herstellerspezifische Eigenschaften einer Komponente keinen Einfluss auf andere Komponenten haben (Tab.I).

Die genannten festgelegten Schnittstellen umfassen ein oder mehrere interne Bussysteme, die Aufbautechnik (Formate der Steckleinheiten) und ein festgelegtes Datenübertragungsprotokoll für die Kommunikation zwischen den Teilnehmern (Komponenten) am Bussystem. Diese drei Schnittstellen müssen langfristig konstant bleiben. Änderungen würden sich nämlich zwangsläufig auf alle angeschlossenen Komponenten auswirken.

Das Bussystem bildet zusammen mit dem Datenübertragungsprotokoll das Rückgrat eines offenen Systems. Es muss eine hohe Datenübertragungsra-

### Definition

- Ein Rechner besteht aus mehreren Prozessoren

- Jeder Prozessor übernimmt seinen Anteil an der Lösung der Gesamtaufgabe

### Ziel

- Erhöhung der Gesamt-Verarbeitungsleistung

- Bearbeitung einer Aufgabe durch den Prozessor, der am besten hierfür geeignet ist

### Voraussetzung

- Schnelles internes Bussystem zum Austausch von Kommandos und Daten zwischen den Prozessoren

- Verfügbarkeit hoher Speicher-Datenraten zur vollen Ausnutzung der Rechnerleistung

**Tabelle II Verteilte Intelligenz**

<sup>1</sup> Million Instructions Per Second

te besitzen, um die Ausbaubarkeit des Systems zu gewährleisten. Ein einheitliches Format der Steckleinheit mit vorgegebenen Steckverbindungen stellt sicher, dass alle Komponenten auch mechanisch eingebaut werden können. Zum Bussystem gehört auch ein Protokoll, mit dem die Auftragsvermittlung zwischen den Komponenten des Rechners abgewickelt wird (wer macht was). Dieses Protokoll muss – orientiert am ISO-Schichtenmodell – so definiert sein, dass es auch für die Aufgabenvermittlung zu externen Rechnern eingesetzt werden kann.

Ein System ist um so offener, je mehr Hersteller Komponenten mit den entsprechenden Schnittstellen anbieten, wobei allerdings zu erwarten ist, dass sich nicht nur eines, sondern mehrere Bussysteme am Markt durchsetzen werden. Es werden sich deshalb nicht alle beliebigen Komponenten direkt integrieren lassen. Für den Anwender haben offene Systeme den wichtigen Vorteil, dass neue Komponenten nachgerüstet werden können und damit seine Systeme länger dem Stand der Technik entsprechen. Dem Hersteller bieten sie den Vorteil einer erweiterten Kombinierbarkeit mit handelsüblichen Komponenten und einer Reduzierung der Abhängigkeit vom Mikroprozessorhersteller.

## Verteilte Intelligenz

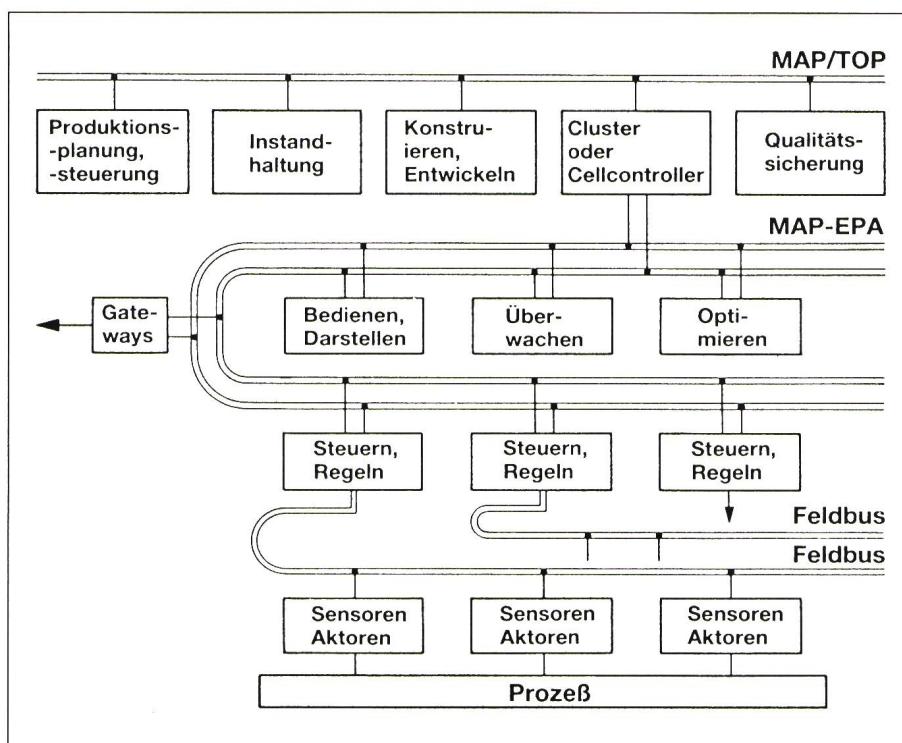

Es ist üblich, zur Lösung von grösseren Automatisierungsaufgaben nicht nur einen Rechner einzusetzen, sondern den Verarbeitungsebenen jeweils eine oder mehrere intelligente Verarbeitungseinheiten zuzuordnen. Diese Einheiten können räumlich über eine ganze Fabrik verteilt sein, und man lässt sie über schnelle, serielle Bussysteme miteinander kommunizieren (Fig.2). Es wird dabei nicht nur die zu lösende Aufgabe zerlegt und verteilt, sondern auch die zur Lösung der Aufgabe insgesamt erforderliche Intelligenz. Ziel ist eine optimale Zuordnung von Aufgabe und Bearbeitungseinheit. Bei den neuen Systemen wird deshalb die bisher vorwiegend zwischen Rechnersystemen praktizierte Intelligenzverteilung auch auf der Prozessrechnerebene praktiziert (Tab. II). Jeder Prozessor und sein zugehöriges Betriebssystem haben ihre speziellen Vorteile (z.B. Realzeitverhalten, Programmierkomfort, Durchsatz, E/A- und Interruptverhalten). Es ist deshalb sinnvoll, beispielsweise für folgende Aufgaben getrennte Prozessoren vorzusehen:

- Realzeitprozessor für Aufgaben mit strengen Anforderungen an das Realzeitverhalten,

- Unix-Prozessor mit komfortabler Benutzeroberfläche für nicht realzeitkritische Aufgaben,

- Ein-Ausgabe-Prozessor zur Abwicklung aller E/A-Vorgänge,

- Prozessor zur Steuerung der Hintergrundspeicher-Peripherie und

- Prozessoren zur autonomen Abwicklung der Protokolle (zumindest bis Schicht 4) für die Bussysteme MAP, Proway C, Ethernet usw.

Voraussetzung für die Realisierung von Rechnern mit verteilter Intelligenz ist ein schnelles zentrales Bussystem (Rückgrat), um erforderliche Daten und Kommandos zwischen den einzelnen Prozessoren mit ausreichender Geschwindigkeit austauschen zu können.

## Normen und Standards

In Rechnersystemen findet man heute Normen und Standards vor allem bei der Datenübertragung, bei ausgewählten Peripherieschnittstellen und im Bereich der Hochsprachen.

Alle Versuche zur Normung von Prozessorarchitekturen hingegen sind

| Busse       | Formate           |

|-------------|-------------------|

| S-100-Bus   |                   |

| Q-Bus       |                   |

| Unibus      |                   |

| STD-Bus     |                   |

| IBM-PC-Bus  | IBM-PC-Format     |

| Multibus I  | Multibus-I-Format |

| AMS-Bus     |                   |

| Multibus II | Europa-Format     |

| VME-Bus     |                   |

| Future-Bus  |                   |

| Nu-Bus      |                   |

Tabelle III Standardisierte Busse (Auswahl) und Steckleinheitenformate

| Prozessoren    | Betriebssysteme |

|----------------|-----------------|

| Intel 80186    | iRMX 86, MS-DOS |

| Intel 80286    | iRMX 286        |

| Intel 80386    | iRMX 386        |

| Motorola 68010 |                 |

| Motorola 68020 | Versados        |

| NS 16000       |                 |

| NS 32000       | Exec            |

| TI 9900        | DX 10           |

|                | Unix            |

Tabelle IV «Quasi-standardisierte» Prozessoren und Betriebssysteme

Figur 2 Basisarchitektur eines modernen Automatisierungssystems

MAP Manufacturing Automation Protocol

TOP Technical and Office Protocols

EPA Enhanced Performance Architecture

bisher gescheitert. Lediglich die Verwendung von genormten internen Busstrukturen und die Festlegung genormter Kartenformate (Europaformat) hat sich breit durchgesetzt (Tab. III). Auf dem wichtigen Gebiet der Prozessorarchitektur selbst und der damit verbundenen Betriebssysteme gibt es lediglich einige Quasi-Standards (Tab. IV), die sich aus der grossen Markt- und Anwendungsbreite ausgewählter Systeme entwickelt haben. Diese Quasi-Standards werden sich mit dem technologischen Fortschritt aber immer wieder ändern.<sup>2</sup>

## Lösungen der AEG

Die zukünftigen Realzeitrechner hoher Verarbeitungsleistung werden mittels 32-Bit-Mikroprozessoren als offene Systeme mit verteilter Intelligenz realisiert. Als Kandidaten für die Verarbeitungseinheiten kamen die Mikroprozessoren Motorola 68020 und Intel 80386 in Betracht. Da die Halbleiterhersteller sich in einem ständigen Wettlauf um höhere Verarbeitungsleistung befinden und jeder Hersteller immer irgendwann die Nasenspitze vorne hat, spielt es keine grosse Rolle, für welchen von beiden man sich entscheidet.

Von entscheidender Bedeutung ist jedoch die Auswahl des Realzeit-Betriebssystems. Versados, das Betriebssystem des Motorola-Prozessors, erfüllt die Anforderungen der AEG bei weitem nicht. Sein Funktionsumfang ist allzu begrenzt. Anders bei Intel. Für den Mikroprozessor 80386 wird zurzeit das wesentlich umfangreicherere und komfortablere Realzeit-Betriebssystem iRMX 386 entwickelt. Hinzu kommt, dass die AEG, die durch einen Kooperationsvertrag mit Intel verbunden ist, auf dieses Betriebssystem Einfluss nehmen, es durch festgelegte Schnittstellen selbst weiterentwickeln und um wichtige Eigenschaften erweitern kann (Tab. V). Bei der AEG hat man sich aus diesen Gründen für das Betriebssystem iRMX 386 und damit auch für den Mikroprozessor Intel

|                          |

|--------------------------|

| <b>Prozessoren</b>       |

| Intel 80386              |

| Intel 80186, 80286       |

| <b>Betriebssysteme</b>   |

| iRMX 386                 |

| Unix                     |

| <b>Busse</b>             |

| Multibus II              |

| Paralleler E/A-Bus (AEG) |

| Bitbus                   |

Tabelle V Komponenten der AEG-Lösung

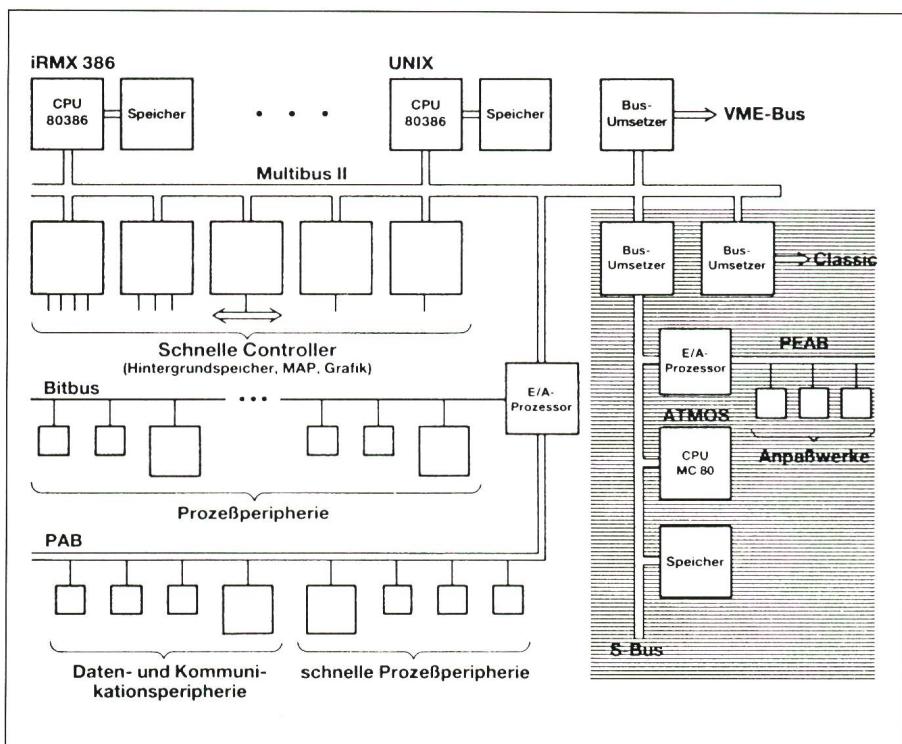

system Unix eingesetzt. Es läuft ebenfalls auf einem Mikroprozessor Intel 80386 ab.

Auch für intelligente Anpasswerke an der Peripherie, z.B. zur Datenübertragung, zur Steuerung der Hintergrundspeicher oder für die Prozessperipherie mit Vorverarbeitung, werden aus Synergiegründen in der Entwicklung ebenfalls vorwiegend Intel-Mikroprozessoren eingesetzt. Hierfür kommen neben dem Mikroprozessor 80386 auch die Prozessoren 80186 und 80286 in Betracht.

Jeder Prozessor verfügt über einen eigenen Speicher mit einem eigenen Speicherbus. Der Grund dafür ist, dass in Zukunft die Gesamtdatenrate, welche zur Ausnutzung der vollen Verarbeitungsleistung erforderlich sein wird, nicht mit einem über einen zentralen Bus angeschlossenen Speicher abgearbeitet werden können. Trotz der Schwerpunktlegung auf Intel-Prozessoren wird im Sinne des offenen Systems in Sonderfällen die Verwendung von anderen Mikroprozessoren nicht ausgeschlossen. Zum Beispiel dann, wenn die Portierung eines speziellen Softwarepaketes zu aufwen-

80386 entschieden. Je nach Anforderungen an die Verarbeitungsleistung werden eine oder mehrere Verarbeitungseinheiten mit je einem Betriebssystem iRMX 386 in einem Rechner konfiguriert (Fig. 5). Für Aufgabenbereiche, die keine hohen Anforderungen an das Realzeitverhalten stellen, z.B. Bedienung, Darstellung, Protokollierung und Datenfernübertragung, wird das weiter verbreitete Betriebs-

Figur 3 Von der heutigen Technik zu zukünftigen Systemen

- █ bestehende Systeme

- ATMOS eigenes Betriebssystem

- PEAB bisheriger paralleler AEG-Bus

- PAB neuer paralleler AEG-Bus

<sup>2</sup> Ob die kürzlich bekanntgewordene Gründung der von acht wichtigen Computerherstellern getragenen «Open Software Foundation» einen Durchbruch bei der Vereinheitlichung von Prozessoren und Betriebssystemen bringen wird, lässt sich derzeit noch nicht sagen.

dig ist. Als Kandidaten für das schnelle Bussystem standen der VME-Bus und der Multibus II zur Auswahl. Insbesondere wegen der Message-Passing-Eigenschaften und des besseren Interrupt-Verhaltens, aber auch wegen der grösseren Verwandtschaft zum Prozessor 80386 und zum Betriebssystem iRMX 386 wurde der Multibus II mit einer Datenübertragungsrate von 40 Mbyte/s gewählt. Alle Prozessoren und schnellen Peripherie-Controller verkehren über diesen Bus miteinander.

Da AEG im Sinne des offenen Systems auch den Anschluss von intelligenten Komponenten mit VME-Bus-Schnittstelle nicht ausschliesst, wird ein Busumsetzer zum VME-Bus bereitgestellt. Für mittelschnelle Peripherie-Anpasswerke wurde zusätzlich ein kostengünstiger 8/16-Bit-Bus mit einer Datenübertragungsrate von rund 2 Mbyte/s eingeführt. Dieser Bus ist eine originäre Lösung von AEG.

Für die langsamsten Peripherie-Anpasswerke schliesslich wird der Bit-Bus von Intel generiert. Dieser Bus kann eine Ausdehnung von bis zu

1200 m haben und erlaubt so insbesondere den Fernbetrieb von Prozessperipherie.

Der Bit-Bus und der mittelschnelle Parallelbus werden von einem speziellen Ein-Ausgabe-Prozessor bedient. Dies hat nicht nur den Vorteil, dass die Verarbeitungsprozessoren von der Verwaltung der E/A-Funktionen entlastet werden, sondern dass auch der Austausch eines Verarbeitungsprozessors keine Auswirkungen auf die Software-Treiber für die Peripherie hat. Die Verwendung der nicht herstellerspezifischen Bussysteme Multibus II und Bit-Bus erlaubt den Zukauf von Anpasswerken.

Die vorgestellte Lösung für die zukünftigen Realzeitrechner der AEG stellt in Hard- und Software einen neuen Lösungsansatz dar. Durch Busumsetzer werden die heutigen Realzeitrechner der AEG, die MC 80 und die Classic-Familie der Modcomp in dieses offene System eingebunden. Dadurch wird ein evolutionärer Übergang von der heutigen Technik in die Zukunft erreicht (Fig. 3). Durch Kombination von alten und neuen Kompo-

nenten können Eigenschaften die auf dem neuen System noch nicht zur Verfügung stehen, realisiert werden, ohne dass auf die Vorteile der neuen Technik verzichtet werden muss. Bereits vorhandene Anwender-Software z.B. kann so problemlos weiterbenutzt werden.

## Schlussbemerkung

In diesem Beitrag wurde nur das Konzept für die leistungsfähigen Realzeitrechner dargestellt. Das gesamte Informatik-Entwicklungsprogramm, das einen Umfang von rund 1000 Mannjahren hat, umfasst auch die Entwicklung von Einzelprozessorlösungen, speicherprogrammierbare Steuerungen, die Realisierung von Fach- und Hochsprachen, die Bereitstellung von Standard-Anwender-Software-Paketen sowie von umfangreichen Software-Entwicklungswerzeugen. Ein weiterer wesentlicher Entwicklungsschwerpunkt liegt bei der Kommunikation der AEG-Systeme mit Fremdsystemen.