|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 79 (1988)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 3                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | 32-bit-VMEbus-Mikrocomputer im Einfach-Europakartenformat                                                                                                                                                                 |

| <b>Autor:</b>       | Eisenbarth, W.                                                                                                                                                                                                            |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-903983">https://doi.org/10.5169/seals-903983</a>                                                                                                                                   |

### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# 32-bit-VMEbus-Mikrocomputer im Einfach-Europakartenformat

W. Eisenbarth

**Sämtliche gegenwärtig angebotenen 32-bit-VMEbus-Lösungen sind auf Doppel-Europakarten implementiert, vorrangig entwickelt für Workstations oder für den CAD/CAE-Markt. Für industrielle Anwendungen besteht jedoch ein Bedarf nach problemorientierter Funktionalität, Kompaktheit, Robustheit sowie Widerstandsfähigkeit gegen Erschütterungen und Vibrationen. Die hohe Rechenleistung soll jedoch beibehalten werden.**

**Toutes les solutions offertes en matière de VMEbus 32 bit sont implémentées sur cartes format Europe double et ont été développées en premier lieu pour les stations de travail ou pour le marché CAD/CAE. Pour les applications industrielles, il existe cependant un besoin en fonctionnalité, compacité et robustesse orientées problèmes, ainsi qu'une résistance contre les chocs et vibrations. Les hautes performances de calcul doivent cependant être conservées.**

Der Beitrag wurde durch Omni Ray AG, Industriestrasse 31, 8305 Dietlikon, überarbeitet.

## Adresse des Autors

Wolfgang Eisenbarth, El.-Ing., PEP Modular Computers, Am Klosterwald 4, D-8950 Kaufbeuren.

## Warum ein Einfach-Europakartenformat?

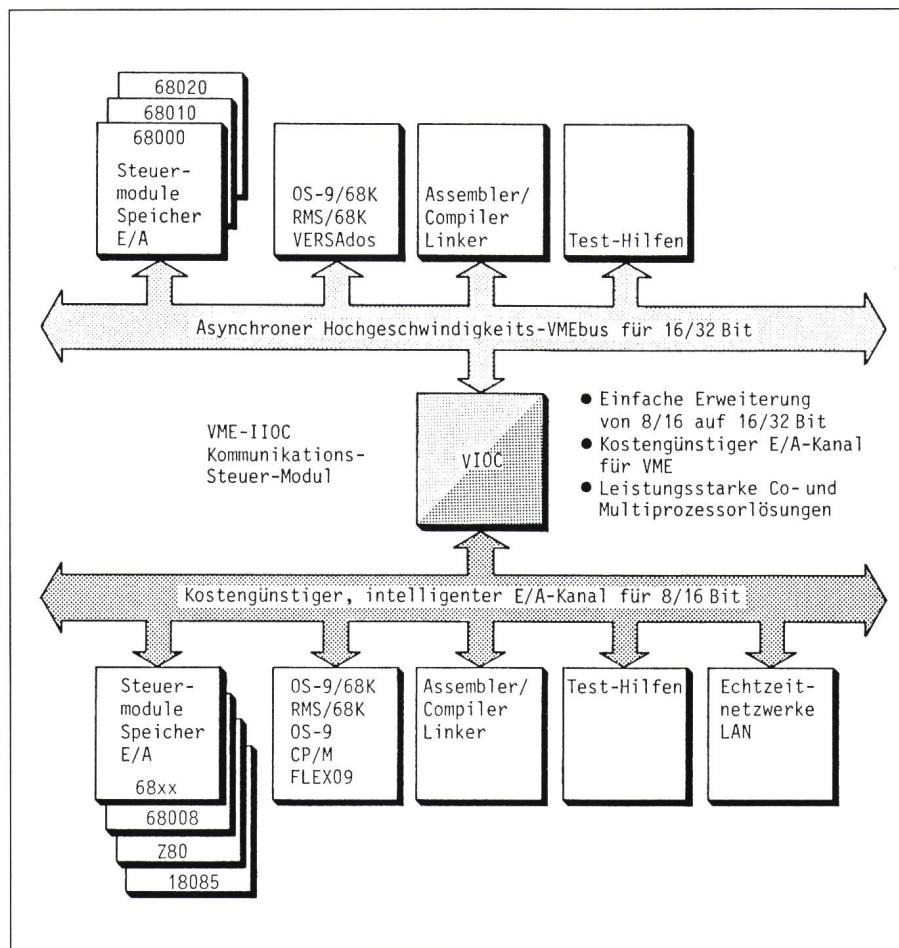

Überwachungsaufgaben, Automatisierungen oder Robotsteuerungen erfordern einerseits schnelle 32-bit-Operationen, während anderseits die Systemarchitektur für die meisten Eingabe-Ausgabe-Funktionen aus 16 bit breiten Komponenten besteht (Fig. 1).

Es gibt zwei Gründe, weshalb E/A-Funktionen auch in den nächsten Jahren 16 bit breit bleiben werden. Erstens haben die E/A-Chips entweder eine 8- oder eine 10 bit breite Schnittstelle, und zweitens sind die Peripheriegeräte im Vergleich zur hohen Geschwindigkeit der CPU sehr langsam. Weil das gesamte für eine Anwendung benötigte RAM/ROM auf der Prozessorkarte selbst implementiert ist, wird der Bus nur für langsame E/A-Zugriffe benutzt. Der P1-Stecker des VMEbus ist somit als Busschnittstelle völlig ausreichend und die Verwendung der kompakten Einfach-Europakarte ein echter Vorteil.

Ziel bei der Entwicklung der VMPM68KC durch die Firma PEP Modular Computers, Kaufbeuren, war, eine leistungsfähige 32-bit-Karte für den VMEbus im Einfach-Europakartenformat mit den folgenden De-

sign-Anforderungen zu entwickeln (Fig. 2):

1. Es soll die beste Systemarchitektur für einen optimierten Leistungsdurchsatz gewählt werden.

2. Die Systemarchitektur muss größte Flexibilität in der Systemkonfiguration ermöglichen.

3. Die Systemarchitektur muss die Eingliederung von zukünftigen Technologien offenhalten.

4. Es sollen neue Technologien angewendet werden, um Platz auf der Karte zu sparen und den Strombedarf zu verringern.

Das neue PEP-Mikrocomputer-Produkt setzt sich aus folgenden Funktionen bzw. Komponenten zusammen:

- CPU MC68020 mit Floating-Point-Co-Prozessor MC 68881

- 1 MByte statisches RAM, Dual Ported<sup>1</sup>, Zero Wait States<sup>2</sup>, 32 bit breit,

- bis zu 512 kByte EPROM, 32 bit breit,

<sup>1</sup> Auf ein Dual Ported RAM kann von zwei verschiedenen Rechnersystemen zugegriffen werden.

<sup>2</sup> Bedeutet, dass Rechner und Memory mit derselben Taktfrequenz arbeiten.

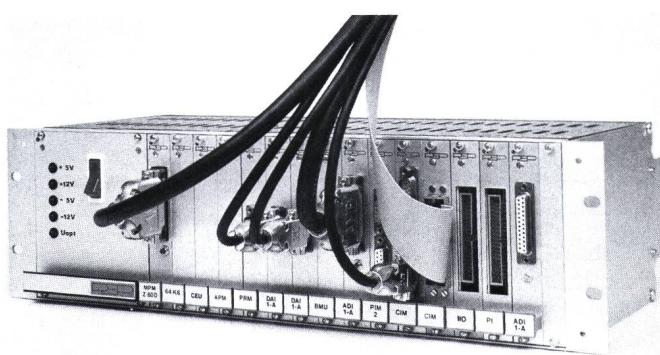

**Figur 1**

Kompakt, robust, klein: so präsentieren sich die VMEbus-Karten im Einfach-Europaformat

- zwei serielle Anschlüsse für Kommunikation,

- vollständige VMEbus-Systemkontrollfunktionen,

- Zählerbaustein für die Generierung von Ticks<sup>3</sup>

- vorbereitete Funktionen für leistungsfähige Multiprozessoranwendungen.

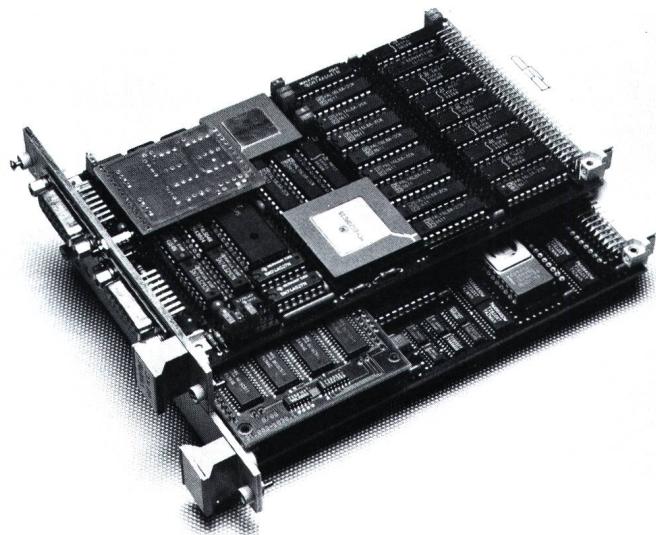

**Figur 2**

Trotz dem kleinen Format zeigt der Mikrocomputer eine hohe Rechenleistung. Die obere Karte ist für Piggy-Back-Bestückung vorbereitet.

## Modulare 32-bit-Architektur

Im industriellen Bereich werden sehr viele Anwendungen mit Prozessoren von Motorola realisiert, hauptsächlich deshalb, weil diese am besten der Industrie-Standardarchitektur des VEMbus entsprechen. Deshalb wurden auch für das neue Mikrocomputermodul der 32-bit-Hochleistungsprozessor MC68020 sowie der FPCP MC68881 ausgewählt, Komponenten welche die geforderte Rechenleistung

und schnelle Ausführung von mathematischen Operationen ermöglichen sollten (Fig. 3). Der Durchsatz eines Systems hängt vor allem auch vom Aufbau und der Zugriffszeit des Speichers ab. Um hohe Transferraten

sicherzustellen, ist eine vollständige 32-bit-Architektur unerlässlich, weshalb von PEP der neue Mikrocomputer als Set von zwei Boards, nämlich Prozessor- und Speicherplatine, angeboten wird. Diese sind mittels eines loka-

<sup>3</sup> Wählbare, rechnerinterne Zeitbasis

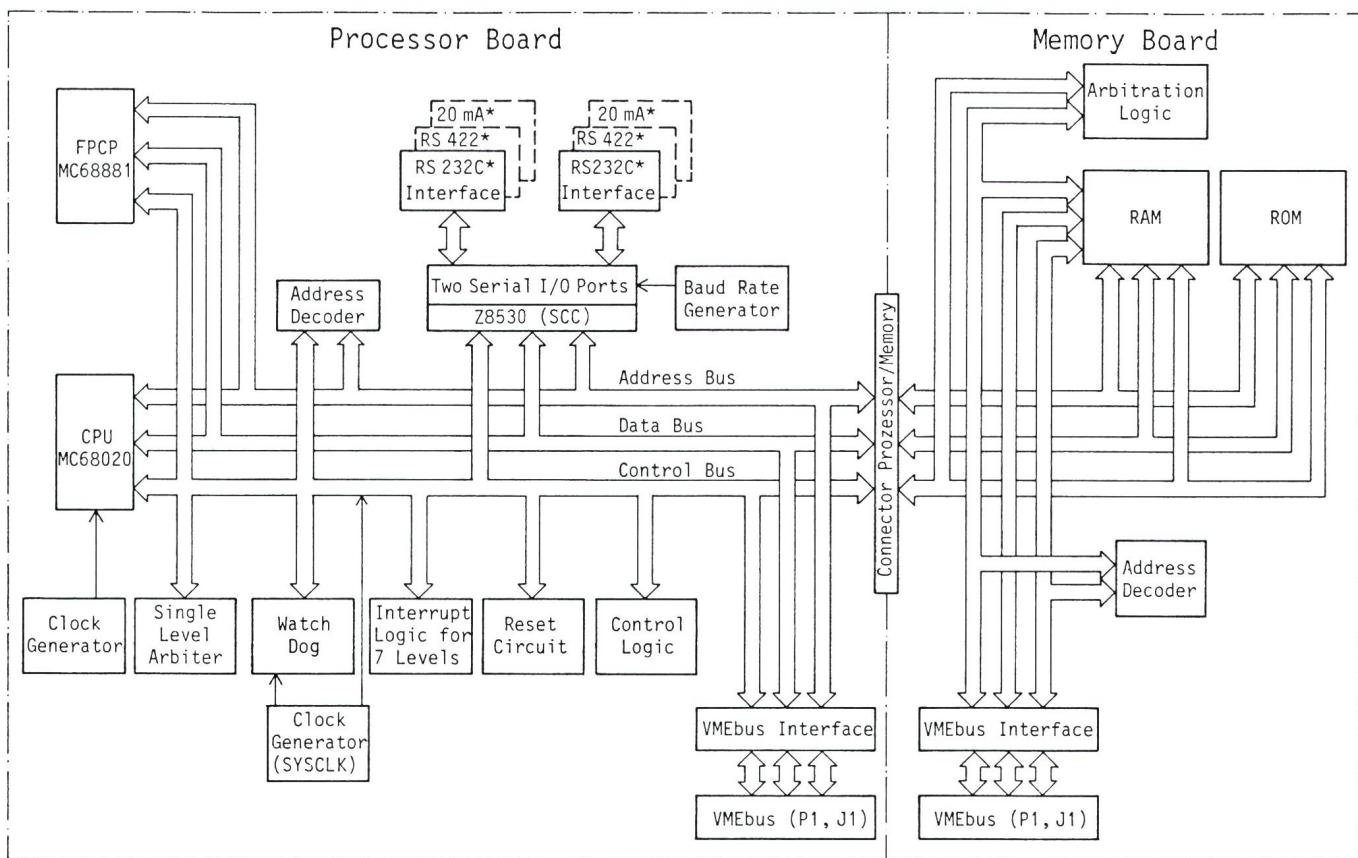

**Figur 3** Blockschema des 32-bit-VMEbus-Mikrocomputers mit einer CPU MC68020

\* Optionen

len, 32 bit breiten Daten- und Adressbussen eng miteinander verbunden.

Die Karte mit dem Prozessor MC68020 und dem Floating-Point-Co-Prozessor MC68881 wird mit einer Taktfrequenz von 12,5 oder 16,7 MHz angeboten. Zwei serielle Schnittstellen basieren auf dem Z8530-Controller und sind individuell konfigurierbar. Im weiteren sind vorhanden:

- ein Timer für Echtzeit-Ticks,

- ein BERR-Timeout (Bus-Error-Zeitüberwachung),

- ein Systemcontroller für den VMEbus.

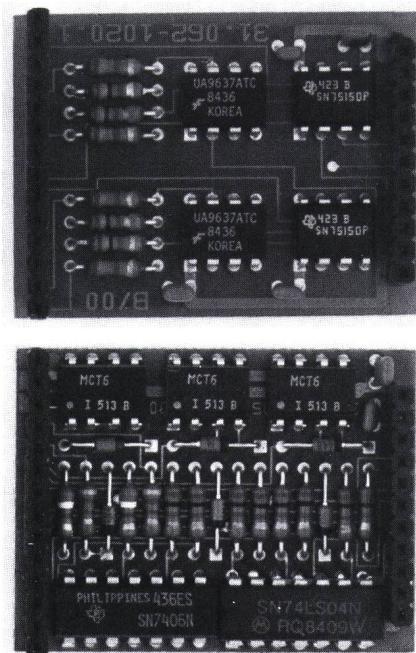

Zwei serielle Schnittstellen gehören bei den meisten PEP-Mikrocomputermodulen zur Standardausrüstung. Die Behandlung der Schnittstellen bleibt dem Anwender überlassen. Zurzeit sind Piggy-Backs<sup>4</sup> für RS232, RS422 und 20-mA-Current-Loop erhältlich (Fig. 4). Die beiden Schnittstellen sind völlig unabhängig voneinander, d.h. die Piggy-Backs können beliebig gemischt werden; dadurch erhält der Anwender flexible Lösungsmöglichkeiten.

## 320 MByte Adressbereich

Beim VME-Bus stehen 24 Adressleitungen einen Adressbereich von 16 MByte zur Verfügung (Tab. I). Für den Benutzer einer Workstation wäre dies sicher eine Einschränkung, nicht aber für den Einsatz in industriellen Steuerungssystemen, wo dieser Adressumfang im Normalfall gar nicht ausgelastet ist.

Weil ein neues Produkt auch für künftige Entwicklungen offen sein soll, sind die Adressmodifikations-Kombinationen (Basis = VMEbus-Spezifikation Rev. C.1.) bereits in die Adress-Map integriert worden<sup>5</sup>.

Zusammen mit allen freien Kombinationen von Adressmodifikations-Codes können 320 MByte Speicherplätze unterschieden werden (Tab. II).

Figur 4 Zwei Piggy-Backs für verschiedene Schnittstellen

## Multiprozessor-Unterstützung

Bei Entwicklern werden Multiprozessorarchitekturen immer beliebter. Diese erlauben z.B., Hardware anstelle

von Software einzusetzen und so die Kommunikation zwischen zwei Prozessoren schneller und sicherer zu machen. Dabei müssen aber die Interrupt-Vektoren in der Systeminterrupttabelle sehr sorgfältig definiert werden. Die Interruptvektoren Level 4 und 5 z.B. ermöglichen die Kommunikation zwischen VMEbus-Mastern. Der höhere Level sollte den Systemcontroller, Level 4, zusammen mit einer CPU-Identifikation, einen untergeordneten Mikroprozessor identifizieren. Ein PAL (Programmable Array Logic) wacht darüber, dass On-board-Interrupts, gegenüber VMEbus-Interrupts der gleichen Stufe, bevorzugt werden.

## 30-ns-Arbitration

Für eine effiziente Busausnutzung ist eine schnelle *Bus-Arbitrations-Logik* nötig; erst damit kann die Gesamtleistung eines VMEbus-Moduls bewertet werden.

Die Arbitration (Buszuteilung) stellt sicher, dass der Zugriff auf andere VMEbus-Module innert kürzester Zeit erfolgt. Der Anwender kann, angepasst an seine Applikation, aus verschiedenen Arbitrations-Protokollen

Tabelle I

VMEbus-Signal

am P1-Stecker

\* aktiver Pegel  $\triangleq$  Low

|                 |                                                                    |                                                                                      |

|-----------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Adreßbus        | A01-A23                                                            | Primärer Adreßbereich 16 Mbyte                                                       |

| Datenbus        | D00-D15                                                            | Primäre Datenbreite 16 Bit                                                           |

| Adreß-Steuerung | AS*<br>AM0-AM5                                                     | Adreß-Strobe Adressen-Modifier                                                       |

| Daten-Steuerung | DS0*, DS1*<br>WRITE*<br>DTACK*<br>LWORD*                           | Daten-Strobe 0 und 1 Lesen/Schreiben Daten-Transfer-Bestätigung Langes Wort (32 Bit) |

| Interrupts      | IRQ1*-IRQ7*<br>IACK*,<br>IACKIN*,<br>IACKOUT*                      | 7 Interrupt-Ebenen Interrupt-Bestätigung (Daisy chain)                               |

| Bus-Arbitration | BR0*-BR3*<br>BG0IN*-BG3IN*<br>BG0OUT*-<br>BG3OUT*-<br>BBSY*, BCLR* | 4 Ebenen Bus-Anforderung Bus grant (daisy chain)                                     |

| VMSbus          | SERDAT<br>SERCLK                                                   | Serielle Daten Takt für serielle Daten                                               |

| Fehler-Signale  | SYSFAIL*<br>BERR*<br>ACFAIL*                                       | System-Fehler Bus-Fehler Netz-Fehler                                                 |

| Netzteil        | +5 V, +12 V,<br>-12 V, GND<br>+5 V Stdby.                          | Netzteil enthält Leitung für Datenerhalt                                             |

| Diverse         | SYSCLK<br>SYSRESET*                                                | 16-MHz-System-Takt System-Reset                                                      |

<sup>4</sup> Kleine steckbare Leiterplatten mit speziellen Funktionen.

<sup>5</sup> Somit stehen zusätzlich zur Verfügung: je 16 kByte für: Standard Privileged, Standard non Privileged und User-Defined-Zugriffe sowie je 64 kByte für Short Privileged und Short non Privileged.

das geeignete auswählen. Normalerweise wird unterschieden zwischen:

- a. Anwendungen mit einem Master, (ROR, Release On Request)

- b. Anwendungen für Multiprozessorumgebungen (RWD, Release When Done)

Die Wahl eines Arbitrationsprotokolls in einem VMEbus-System kann aber auch nach anderen Kriterien erfolgen. So benötigen eventuell auch intelligente E/A-Module oder spezielle Schutzmechanismen das RWD-Protokoll, auch wenn diese nicht in einer Multiprozessorumgebung eingesetzt sind.

## 1-MByte-RAM mit Zero Wait States

Das Modul enthält 1 MByte statische RAM (Dual Ported) sowie vier 32-Pin-Sockel für bis zu 512 kByte ROM. Sowohl RAM als auch ROM sind 32 bit breit angelegt (Tab. II). Da ein 32-bit-Prozessor verwendet wird, ist eine äquivalente Organisation von RAM und ROM notwendig, um die Geschwindigkeit des MC68020 voll auszunützen zu können. Ein Zero-Wait-State-Zugriff auf den Speicher war eine der Hauptvoraussetzungen, um ausreichend Systemspeicherplatz mit sehr kurzer Zugriffszeit auf der Karte zu gewährleisten.

Um hohe Kosten für schnelle Speicherchips zu vermeiden, wurde eine besondere Eigenschaft des MC68020 zusammen mit einer schnellen Hardwarelogik ausgenutzt. Das ECS-Signal (External Cycle Start) gestattet die Voranwahl von kostengünstigeren RAM-Chips mit 100 ns Zugriffszeit, bevor mit dem AS-Signal (Adress-Strobe-Signal) die eigentliche Gültigkeit der Adresse angezeigt wird. Durch diese Eigenschaft des MC68020 können Kosten proportional zur Menge der verwendeten RAM gespart werden. Von PEP werden Speicherchips vom Typ 32K × 8 im SO-Gehäuse eingesetzt, die auf die Speicher-Piggy-Backs in SMD-Technik montiert werden.

## Dual Ported RAM

Dank dem doppelten Zugriff auf den RAM-Speicher (Dual Ported RAM) können intelligente VMEbus-Ein-Ausgabe-Module über den VME-

**Tabelle II**

**Address Map**

|             |                                                                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| \$FFFF FFFF | Reserved                                                                                                                             |

| \$C000 0500 | On-board I/O facilities                                                                                                              |

| \$C000 0000 | External VMEbus;<br>16 MByte standard supervisory/<br>standard non-privileged access<br>AM code 39/3A/3D/3EH                         |

|             | 64 KB short access, AM code 29/2DH                                                                                                   |

|             | 16 MByte user-defined<br>AM code 19/1A/1D/1EH                                                                                        |

|             | 16 MByte user-defined<br>AM code 11/12/15/16H                                                                                        |

|             | Remaining addresses in this section<br>are reserved according to the<br>Address Modifier Table in VMEbus<br>Specifications, Rev. C.1 |

| \$8000 0000 | Reserved                                                                                                                             |

| \$4008 0000 | 512 KByte on-board ROM provision<br>AM code 39/3A/3D/3EH                                                                             |

| \$4000 0000 | Reserved for on-board memory<br>extension                                                                                            |

| \$0010 0000 | 1 MByte on-board static RAM<br>AM code 39/3A/3D/3EH                                                                                  |

| \$0000 0000 |                                                                                                                                      |

bus direkt Daten in Speicherbereiche des Mikrocomputers schreiben, ohne den Prozessor MC68020 zu benutzen. Die Vorteile des Dual Ported RAM kommen auch Multiprozessorsystemen zugute. Eine CPU kann direkt via VMEbus in Datenbereiche der anderen CPU hineinschreiben, die vorab für eine Kommunikation reserviert wurden. Ist die Kommunikation beendet, so kann dies über einen Interrupt angezeigt werden.

## Flexibilität für neue Technologien

Um eine eventuelle spätere Verwendung von neuen Speicherchips zu ermöglichen, sind alle RAM-Chips auf einem speziellen Piggy-Back-Modul angebracht. Hierdurch fallen bei einer späteren Anpassung an erhöhte Speichermöglichkeiten erheblich weniger Entwicklungs- und Produktionskosten an. Die Adressdekodierung auf der Speicherplatine wurde bereits für 16 MByte ausgelegt.

## Viel Platz für ROM-fähige Systeme

In industriellen Anwendungen und in der Roboterindustrie verbietet die Umgebung oft die Verwendung von Massenspeichern, z.B. Hard- oder Floppy Disks. Anderseits ist nicht jedes Betriebssystem völlig ROM-fähig.

Das Betriebssystem OS-9 jedoch ermöglicht dem Entwickler, Betriebssystem und Anwendungssoftware auf EPROM zu schreiben. Dieses war auch der Hauptgrund dafür, soviel ROM wie möglich auf der Speicherplatine zur Verfügung zu stellen. Vier 32-bit-Sockel bieten Platz für neue Mbit-EPROM (271001). Aus Gründen der Kompatibilität und weil 28-Pin-EPROM bis jetzt noch immer die meistverwendeten Read-only-Speicherbausteine sind, können auch diese in den 32-Pin-Sockeln verwendet werden. Das Resultat sind ROM-Kapazitäten von 128 kByte (4 × 27256), 256 kByte (4 × 27512) oder 512 kByte (4 × 271001).

## Geringere Leistungsaufnahme mit CMOS

Neben dem Prozessor und dem Floating-Point-Co-Prozessor, die in HCMOS realisiert sind, wurde auch die PAL in CMOS ausgelegt. Auch die FCT<sup>6</sup>-Treiber, die während der inaktiven Zeit nur 3 mA anstelle der früheren 60 mA konsumieren, tragen dazu bei, dass der VMPM68KC-Mikrocomputer nur etwa die Hälfte des Stroms vergleichbarer Module benötigt. Dies wirkt sich auch auf die Zuverlässigkeit positiv aus und macht den neuen Mikrocomputer für industrielle Anwendungen besonders geeignet.

## Anwendung in der Automatisierung

Der VMPM68KC ist ein Produkt, das besonders auf Anwendungen in der industriellen Automatisierung abzielt. Er erfüllt alle wichtigen Voraussetzungen für dieses Marktsegment, ohne mit überflüssigen, auf dem industriellen Markt nicht geforderten Funktionen, überlastet zu sein.

Er eignet sich speziell für den Einbau in Robotern, in Kontrolleinheiten für Spezialfahrzeuge, in Verkehrsleitsystemen und in vielen weiteren Anwendungen, wo einfach nicht mehr genügend Platz für grössere Computer vorhanden ist und wo seine kompakte Grösse in Anbetracht der rauen Umgebung natürlich auch eine erhöhte Stabilität verspricht.

Mit dem VMPM68KC unterstützt

Figur 5 Konfigurationsbeispiel: OS-9/68000 Multiprozessor-Umgebung mit einem IIOC-Subsystem

Anwendungen z. B. bei Robotersteuerungen

PEP die komplette Linie der Motorola-Prozessoren vom 6809 und 68008 auf dem IIOC (Eurobus) bis zum 68HC000, 68010 und 68020 auf dem VMEbus (Fig. 5). Alle Module sind im Einfach-Europakartenformat realisiert. Mit dieser Produktlinie hat der Anwender die Wahl zwischen verschiedenen Leistungsvarianten auf

Karten des gleichen Formats. Die Unterstützung des OS-9-Betriebssystems durch alle erwähnten Prozessoren garantiert zugleich einen grösstmöglichen Grad von Softwarekompatibilität. Ein Konzept, das OEM-Firmen ermöglicht, mit kurzen Entwicklungszyklen zu arbeiten und die Produkte schnell auf den Markt zu bringen.

<sup>6</sup> Fast Advanced CMOS Technology