**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 78 (1987)

**Heft:** 11

**Artikel:** Prüfung und Vorbehandlung komplexer ICs

**Autor:** Birolini, A.

**DOI:** https://doi.org/10.5169/seals-903876

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 30.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

## Prüfung und Vorbehandlung komplexer ICs

A. Birolini

Eine Prüfung dient zur Feststellung, ob eine gegebene integrierte Schaltung (IC) den Anforderungen, die an sie gestellt werden, genügt. Sie kann von einer einfachen Eingangsprüfung bis zu einer umfassenden Qualifikationsprüfung reichen. Ziel einer Vorbehandlung ist hingegen, die in einem gegebenen Los vorhandenen schwachen ICs zum Ausfall zu bringen (Frühausfälle). Dieser Aufsatz geht auf die technischen und praktischen Aspekte der Prüfung und Vorbehandlung komplexer ICs ein. Der Begriff der Prüfstrategie wird eingeführt und die Frage der Wahl zwischen stichprobenweiser und 100%iger Eingangsprüfung beantwortet.

L'essai a pour but de vérifier si un circuit intégré donné remplit les conditions requises. Il peut aller d'un simple contrôle d'entrée jusqu'à un essai complet de qualification. Le but d'un déverminage par contre est d'éliminer les circuits intégrés faibles contenus dans un lot (défaillances précoces). Cet article examine les aspects techniques et pratiques de l'essai des circuits intégrés complexes. Le concept de stratégie d'essai est introduit et une réponse est donnée quant'au choix entre un contrôle d'entrée à 100% ou par échantillonnage.

Dieser Aufsatz ist eine überarbeitete Fassung eines Übersichtsvortrages, den der Autor an der COMPEURO 87 (11.–15. Mai 1987) in Hamburg gehalten hat.

#### Adresse des Autors

Prof. Dr. A. Birolini, Fachgruppe Zuverlässigkeitstechnik am Institut für Elektronik, ETH-Zentrum, CH-8092 Zürich.

#### 1. Einführung

Die wachsende Komplexität der LSI- und VLSI-ICs übt einen immer grösseren Einfluss auf die Zuverlässigkeit und die Sicherheit von elektronischen Geräten und Systemen aus. In vielen Fällen ist es möglich, das Problem durch Redundanz zu lösen [1; 2]. Wenn aber Kosten-, Platz- oder andere Gründe dies verhindern, ist der Wahl und allenfalls auch der Qualifikation, Prüfung und Vorbehandlung der verwendeten komplexen ICs eine besondere Bedeutung beizumessen.

In diesem Beitrag wird zuerst auf die Eingangsprüfung und die Vorbehandlung von LSI- und VLSI -ICs eingegangen sowie ihre Möglichkeiten und Grenzen aufgezeigt. Dann werden Qualifikationsprüfungen für diese ICs beschrieben und in einem dritten Teil der Begriff der Prüfstrategie eingeführt. Die Frage, ob eine stichprobenweise oder eine 100%ige Eingangsprüfung vorzuziehen ist, wird unter Berücksichtigung der Direkt- und Folgekosten in Abschnitt 5 beantwortet.

# 2. Eingangsprüfung komplexer ICs

Mit der Eingangsprüfung wird festgestellt, ob die angelieferten ICs fehlerfrei sind. Es handelt sich dabei um eine Qualitätskontrolle, die je nach der zu erwartenden Fehlerquote sowie den durch die Verwendung fehlerhafter ICs sich ergebenden Folgekosten 100%ig oder nach einem bestimmten Stichprobenplan durchgeführt wird. Allgemein sind die Vorteile einer 100%igen Eingangsprüfung:

- 1. Unmittelbare Entdeckung aller relevanten Fehler

- Reduktion der Anzahl defekter Leiterplatten

- 3. Vereinfachung der Prüfungen auf Leiterplattenebene

- 4. Schutz gegen Qualitätsschwankungen von einem Los zum anderen oder innerhalb des gleichen Loses

5. Ersatz der defekten Bauteile durch den Lieferanten.

Auch eine 100%ige Eingangsprüfung kann aber nicht die Gewähr geben, dass alle auf einer bestückten Leiterplatte angebrachten ICs fehlerfrei sind. Fehler bzw. Ausfälle können durch falsche Handhabung, transiente Vorgänge sowie Montage- oder Prüffehler verursacht worden sein. Anderseits haben marginale Abweichungen von den Spezifikationen oft praktisch keinen Einfluss auf die Funktionstüchtigkeit der Leiterplatten und können deshalb zugelassen werden.

Die Eingangsprüfung von LSI- und VLSI-ICs besteht im wesentlichen aus einer (externen) visuellen Kontrolle und einer elektrischen Prüfung. Die elektrische Prüfung erfolgt gemäss folgenden Schritten:

- 1. Kontaktprüfung

- 2. Funktionsprüfung und Prüfung der dynamischen Parameter (AC)

- 3. Prüfung der Gleichstromparameter (DC).

Mit der Kontaktprüfung wird festgestellt, ob alle Verbindungen zum Chip in Ordnung sind (kein Kurzschluss und keine Unterbrechung). Dafür werden zuerst alle Pins geerdet. Jeweils ein Pin wird mit etwa -100 μA belastet und die sich aufbauende Spannung gegen Erde gemessen. Für alle üblichen Input- und Output-Pins muss diese Spannung zwischen -0,1 und -3 V liegen.

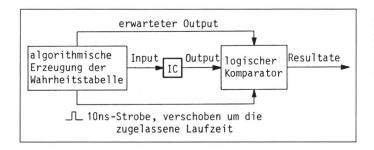

Bei der Funktions- und AC-Prüfung wird die Wahrheitstabelle unter Berücksichtigung der Laufzeiten überprüft. Die Figur 1 zeigt das Prinzip der Messung. Der Generator liefert mit der Frequenz  $f_0$  eine Zeile nach der anderen aus der Wahrheitstabelle, die geprüft werden soll. Für ein IC mit 40 Anschlüssen sind dies 40-Bit-Wörter. Dieses binäre Wort (Testvektor) wird an die Inputs des zu prüfenden ICs angelegt. Dessen Output wird an einem logischen Komparator mit dem erwarteten Output zu einem definierten Zeit-

Figur 1 Prinzip der Funktions- und AC-Prüfung von LSI- und VLSI-ICs

punkt verglichen. Die Strobes wie auch noch andere Steuerimpulse können mit einer hohen Auflösung innerhalb der Periode  $1/f_0$  plaziert werden und erlauben so die Überprüfung der dynamischen Parameter. Bei modernen Prüfanlagen für VLSI-ICs erreicht  $f_0$  50 MHz (100 MHz in Multiplexmode); die resultierende Messgenauigkeit für die dynamischen Parameter liegt damit bei etwa 200 bis 400 ps. Trotz der grossen Leistungsfähigkeit der Prüfanlagen ist aber die direkte Messung von Verzögerungs- sowie von Anstiegs- oder Abfallzeiten heute noch aufwendig.

Das Hauptproblem bei der Funktionsprüfung von VLSI-ICs ist, dass nicht alle Zustände und Zustandsfolgen geprüft werden können. Für einen bitorganisierten Speicher mit n Zellen sind z.B. bis zu  $2^n$  Zustände bei n!Adressfolgen<sup>1</sup> möglich, weshalb bereits für n = 50 etwa  $10^{80}$  Testvektoren erforderlich wären. Einschränkungen sind deshalb notwendig. Solche Einschränkungen stützen sich auf eine Vielfalt von Kenntnissen, wie die spezielle IC-Anwendung, das Vorhandensein von Regelmässigkeiten in der Wahrheitstabelle und die Möglichkeit, das gegebene IC in Module zu zerlegen sowie auf die Erfahrung des Testingenieurs. Sie werfen aber sofort die Frage der Prüfabdeckung bzw. der Fehlererkennungswahrscheinlichkeit auf. Diese Frage ist bis heute nur beschränkt beantwortet worden. Fehlermodelle sind bekannt [3; ...; 7], aber zurzeit noch zu wenig ausgereift.

Die Prüfung der Gleichstromparameter erfolgt ohne Schwierigkeiten mit Hilfe einer Strom- oder Spannungsquelle, die zwischen den Pins kommutiert werden kann. Die sich aufbauenden Spannungen bzw. Ströme werden gemessen.

# 3. Vorbehandlung komplexer ICs

Eingangsprüfung eines VLSI-ICs dauert in der Regel kaum mehr als 5 bis 10 s. Sie bringt deshalb praktisch keinen Frühausfall zum Vorschein. Die Erfahrung zeigt aber, dass abhängig von der Technologie, vom Hersteller und von allfälligen Vorschädigungen die Ausfallrate eines Loses gleicher VLSI-ICs während der ersten 100 bis 3000 Betriebsstunden oft rasch abnimmt. Störend in den Anwendungen sind weniger die (bezogen auf das Los) in der Regel relativ kleinen Änderungen der mittleren Lebensdauer der ICs als vielmehr die Folgekosten jeden Frühausfalls im Feld (z.B. als Garantieleistung für eine ausgefallene Maschine oder Anlage).

Eine wirksame Methode zur gezielten, vorzeitigen Auslösung von Frühausfällen ist die Vorbehandlung (Screening). Sie besteht in einer Folge von Beanspruchungen, denen ein Los gleicher ICs mit der Absicht unterworfen wird, die im Los enthaltenen

schwachen ICs zum Ausfall zu bringen. Im Idealfall sollte eine Vorbehandlung keinen Ausfallmechanismus auslösen oder aktivieren, der bei der vorgesehenen IC-Anwendung nicht auftreten würde, insbesondere sollte sie keine Vorschädigung verursachen. Für die Festlegung geeigneter Vorbehandlungsverfahren und -sequenzen sollte man deshalb in der Lage sein, folgende Fragen zu beantworten:

- 1. Welche Ausfallmechanismen werden durch welche Beanspruchungen aktiviert?

- 2. Was ist die dominierende Beanspruchung für einen bestimmten Ausfallmechanismus? Ist der Einfluss der anderen Beanspruchungen gross?

- 3. Ab welchem Niveau der Beanspruchung werden Zustände angenommen, die unter normalen Bedingungen nicht auftreten würden?

Eine umfassende Vorbehandlungssequenz für ICs im Militärbereich ist in MIL-STD-883 [8] gegeben (Tab. I). Jeder Schritt der Sequenz von Tabelle I aktiviert einen oder mehrere Ausfallmechanismen (Tab. II, [2]). Bezüglich der Verteilung der provozierten Frühausfälle können folgende Richtwerte angegeben werden:

| Hochtemperaturlagerung   | 0 bis 15%  |

|--------------------------|------------|

| Thermische Zyklen        | 5 bis 15%  |

| Konstante Beschleunigung | 0 bis 5%   |

| Burn-in                  | 60 bis 80% |

| Dichtigkeitsprüfung      | 5 bis 15%  |

Tabelle I Vorbehandlungssequenz für ICs gemäss MIL-STD-883C

|                               | T                                     |                |  |  |

|-------------------------------|---------------------------------------|----------------|--|--|

| Vorbehandlungsschritt         | Integrierte Schaltungen (MIL-STD-883) |                |  |  |

| Volbenandlungssentie          | s                                     | В              |  |  |

| Anschlußdrähte                | 100%                                  | -              |  |  |

| Interne visuelle Kontrolle    | 100%                                  | 100%           |  |  |

| Hochtemperaturlagerung        | 24h/150°C                             | 24h/150°C      |  |  |

| Thermische Zyklen             | 10x -65/+150°C                        | 10x -65/+150°C |  |  |

| Konst. Beschleunigung         | 30'000g/60s                           | 30'000g/60s    |  |  |

| Mech. Schocks                 | -                                     | -              |  |  |

| Dichtigkeit (Fine/Gross Leak) | -                                     | -              |  |  |

| Teilchen-Detektion            | 100%                                  | -              |  |  |

| Reduzierte el. Prüfung        | 100%                                  | -              |  |  |

| HochtempRückBias (HTRB)       | 72h/150°C                             | -              |  |  |

| Reduzierte el. Prüfung        | 100%                                  | 100%           |  |  |

| Burn-in                       | 240h/125°C                            | 160h/125°C     |  |  |

| El. Prüfung                   | 100%                                  | 100%           |  |  |

| Dichtigkeit (Fine/Gross Leak) | 100%                                  | 100%           |  |  |

| Röntgenaufnahme               | 100%                                  | -              |  |  |

| Externe visuelle Kontrolle    | 100%                                  | 100%           |  |  |

<sup>&</sup>lt;sup>1</sup> Die Reihenfolge der Adressierung spielt für die Fehler dynamischer Parameter eine wichtige Rolle (Tab. III).

| Ausfallart                                             | Hochtempera<br>Keramik | turlagerung<br>Kunststoff | Thermische Zyklen<br>Keramik Kunststoff |      | Zentrifuge<br>Keramik | Burn-in<br>stat. dyn. |      |

|--------------------------------------------------------|------------------------|---------------------------|-----------------------------------------|------|-----------------------|-----------------------|------|

| Bondung                                                | 20%                    | 30%                       | 20%                                     | 60%  | 35%                   | 15%                   | 20%  |

| Oberfläche (Leckströme,<br>Inversion)                  | 60%                    | 50%                       | 15%                                     | 15%  |                       | 15%                   | 25%  |

| Metallisierung (Korrosion,<br>Elektromigration, Risse) | 5%                     | 5%                        | 5%                                      | 5%   |                       | 20%                   | 20%  |

| Oxid (Durchbruch, Inversion, heiße Elektronen)         | 15%                    | 15%                       | 15%                                     | 15%  |                       | 45%                   | 20%  |

| Diffusion                                              |                        |                           |                                         |      |                       | 5%                    | 10%  |

| Substrat                                               |                        |                           | 5%                                      | 5%   |                       |                       | 5%   |

| Chiphaftung                                            |                        |                           |                                         |      | 15%                   |                       |      |

| Dichtigkeit                                            |                        |                           | 40%                                     | 8    | 50%                   |                       |      |

|                                                        | 100%                   | 100%                      | 100%                                    | 100% | 100%                  | 100%                  | 100% |

Tabelle II Approximative Verteilung der bei den verschiedenen Vorbehandlungsschritten beobachteten Ausfallarten von ICs

Die Dichtigkeitsprüfung (für Keramik- oder Cerdipgehäuse) ist mehr eine Kontrolle als ein Vorbehandlungsschritt. Das Burn-in verursacht den grössten Teil der Frühausfälle. Es stellt damit den wirksamsten, aber gleichzeitig auch den delikatesten (Vorschädigungsgefahr) Vorbehandlungsschritt dar. Für VLSI-ICs wird es vorwiegend dynamisch durchgeführt. Der Beschleunigungsfaktor F beim dynamischen Burn-in kann für eine Burn-in-Temperatur bis etwa 130 °C näherungsweise aus der Gleichung für das Arrhenius-Modell

$$F = \frac{MTBF_1}{MTBF_2} = \frac{\lambda_2}{\lambda_1} \simeq e^{\frac{E_A}{k}} \left( \frac{1}{T_1} - \frac{1}{T_2} \right) \tag{1}$$

gewonnen werden. Dabei sind  $E_A$  die Aktivierungsenergie, k die Boltzmannsche Konstante (8,6·10<sup>-5</sup>eV/K) und  $\lambda_1$  bzw.  $\lambda_2$  die festgestellten Ausfallraten bei den Chiptemperaturen  $T_1$ bzw.  $T_2$  (in K). Die Aktivierungsenergie EA ist je nach Ausfallmechanismus verschieden. Globale Mittelwerte für ICs sind 0,4 bis 0,6 eV fürTTL, 0,6 bis 0,8 eV für NMOS und 0,7 bis 0,9 eV für CMOS. Mit Hilfe von (1) kann die Dauer des Burn-in für eine bestimmte Anwendung geschätzt werden. Beträgt z.B. die Periode der Frühausfälle 3000 h und ist  $\theta_1 = 55$  °C und  $\theta_2 =$ 130 °C, so erhält man für CMOS-ICs in Keramikgehäusen ( $E_A \approx 0.7 \text{ eV}$ ) F  $\approx$ 100 und damit eine Burn-in-Dauer

von 30 h. Für TTL ( $E_A \approx 0,4$  eV) wären dies 210 h.

Vorbehandlungssequenzen für MIL-Bauteile sind aufwendig und beeinflussen den Bauteilpreis. Für den Zivilsektor gibt man sich oft mit einfacheren Sequenzen zufrieden [2; 9].

# 4. Qualifikationsprüfung komplexer ICs

Die in den Abschnitten 2 und 3 beschriebene elektrische Prüfung und Vorbehandlung werden im Rahmen einer Eingangsprüfung durchgeführt.

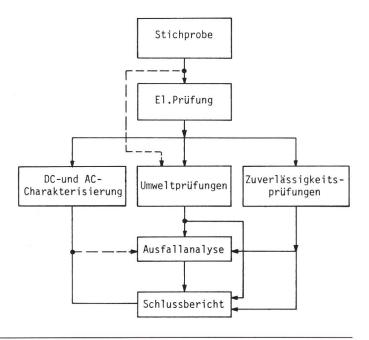

Beide geben nur wenig Auskunft über das Verhalten der betreffenden ICs bei starken Umweltbelastungen und ihre Zuverlässigkeit. Für einen Entwicklungsingenieur, der vor der Wahl eines IC für eine bestimmte Anwendung steht, oder für einen Qualitätssicherungsleiter, konfrontiert mit der Freigabe eines spezifischen IC für gegebene Einsatzbedingungen, reichen die Resultate aus einer Eingangsprüfung oft nicht aus. Erwünscht sind Ergebnisse aus Qualifikationsprüfungen. Die Figur 2 gibt den prinzipiellen Ablaufplan für eine Qualifikationsprüfung komplexer ICs wieder. Die

Figur 2

Prinzipieller

Ablaufplan für eine

Qualifikationsprüfung komplexer ICs

Eine detailliertere

Darstellung findet sich

in [2] oder im Bull.

SEV/VSE 75(1984)1,

Prozedur von Figur 2 findet vor allem bei kundenspezifischen ICs (ASIC) Anwendung. Für marktübliche ICs kann sie oft reduziert werden, weil man sich auf frühere Prüfungen bei ICs gleicher Technologie und des gleichen Herstellers stützen kann.

Nach einer elektrischen Prüfung teilt sich die Qualifikationsprüfung von Figur 2 in drei Zweige: Charakterisierung, Umweltprüfungen und Zuverlässigkeitsprüfungen. Systematische Ausfallanalysen nach jedem Belastungsschritt erlauben die Untersuchung von Ausfallmechanismen.

#### 4.1 Charakterisierung

Die Charakterisierung ist eine parametrische, experimentelle Untersuchung der elektrischen Eigenschaften des betreffenden IC. Sie erlaubt die Bestimmung der Einflüsse der verschiedenen Parameter (Speisespannung, Eingangsschwellen, Frequenz, Temperatur usw.) auf die Funktionstüchtigkeit des IC sowie die Auffindung von Schwachstellen und kritischen Testmustern. Die Resultate erlauben auch die Optimierung des Prüfaufwandes für die Eingangsprüfung der Serienbauteile. Eine Charakterisierung wird stets bei 2 bis 3 verschiedenen Temperaturen und mit mehreren Testmustern durchgeführt. Letzteres trifft vor allem für Speicher zu, für welche die Fehlerentdeckungswahrscheinlichkeit stark von den Testmustern abhängt. Die Empfindlichkeit jedes Testmusters kann mit Hilfe von sog. Shmooplots gezeigt werden [2]. Die Tabelle III gibt für die verbreitetsten Testmuster eine qualitative Beurteilung der Fehlerentdeckungswahrscheinlichkeit und die approximative Prüfdauer für ein 4k×1 statisches RAM [2]. Die Quantifizierung der Fehlererkennungswahrscheinlichkeiten der verschiedenen Testmuster ist noch Gegenstand von Forschungsarbeiten.

#### 4.2 Umweltprüfungen

Die Umweltprüfungen dienen der Untersuchung des IC-Verhaltens unter erhöhten Umweltbelastungen. Es handelt sich dabei oft um destruktive Prüfungen. Art und Umfang der Umweltprüfungen hängen von der vorgesehenen Anwendung ab. Die einzelnen Prüfungen sind in Normen (z. B. MIL-STD-883) und in der Literatur beschrieben. Zur Untersuchung der Ausfallmechanismen sind nach jeder Beanspruchung Ausfallanalysen notwendig. Spezielle Prüfungen für kunststoffverkapselte ICs werden in der Literatur behandelt. Allerdings sind die Modelle zur Berechnung der Beschleunigungsfaktoren bei Feuchteprüfungen noch zu wenig ausgereift

#### 4.3 Zuverlässigkeitsprüfungen

Ziel der Zuverlässigkeitsprüfungen ist die Ermittlung der Ausfallrate (möglicherweise als Funktion der Zeit), von Informationen über das Langzeitverhalten kritischer Parameter und von Angaben über die Zweckmässigkeit von Vorbehandlungen im Rahmen der Eingangsprüfungen von Serienbauteilen. Die Prüfung besteht in der Regel aus einem verlängerten Burn-in mit elektrischen Messungen

und Ausfallanalysen in angemessenen zeitlichen Abständen. Der Umfang der Stichprobe soll so bestimmt werden, dass die erwartete Anzahl Ausfälle während der Prüfung ≥ 5 ist. Die Festlegung der minimalen Anzahl Ausfälle steht im Zusammenhang mit der Breite des *Vertrauensintervalls* für die Ausfallrate. Unter der Annahme einer *konstanten* Ausfallrate lässt sich dieses einfach ermitteln [2].

#### 5. Prüfstrategien

Hinsichtlich der Aufwandoptimierung für die Prüfungen und Vorbehandlungen von elektronischen Geräten und Systemen während der Fertigungsphase hat sich jeder Hersteller die folgende grundsätzliche Frage zu stellen:

Auf welchem Integrationsniveau soll was und wie geprüft und vorbehandelt werden, um möglichst alle Fehler und Frühausfälle kostenoptimal noch vor Beginn der Nutzungsphase zu eliminieren?

Die Beantwortung dieser Frage erfolgt unter Berücksichtigung der Qualitäts-, Zuverlässigkeits- und Sicherheitsziele, der Auswirkung von Fehlern und Ausfällen, der Wirksamkeit der einzelnen Prüfungs- und Vorbehandlungsschritte sowie der direkt anfallenden Kosten und der Folgekosten. Die Erfahrung zeigt, dass nicht gleichzeitig alle Parameter optimiert werden können, sondern dass diese je nach Anwendung gewichtet werden müssen [2; 9; ...; 20].

Die Untersuchung des obigen Fragenkomplexes führt zu einer Prüf- und Vorbehandlungsstrategie auf Geräte-

Tabelle III

Einfluss

verschiedener

Testmuster auf die

wichtigsten

Ausfallarten

statischer RAMs und

approximative

Prüfzeit für ein

4 k × 1 stat. RAM

| Testmuster    | Funktion | sfehler<br>Kopplung* | Fehler an dyna-<br>mischen Parametern<br>A, LV Kopplung** |        | Anzahl<br>Prüfschritte | Approximative<br>Prüfzeit für ein<br>4kx1 stat RAM |

|---------------|----------|----------------------|-----------------------------------------------------------|--------|------------------------|----------------------------------------------------|

| Schachbrett   | mittel   | wenig                |                                                           |        | 4n                     | 8ms                                                |

| March         | gut      | wenig                | wenig                                                     |        | 5n                     | 10ms                                               |

| Diagonale     | gut      | mittel               | wenig                                                     | wenig  | 10n                    | 20ms                                               |

| Umgebung      | gut      | gut                  | mittel                                                    | mittel | ≃24n                   | 50ms                                               |

| Schmetterling | gut      | gut                  | gut                                                       | mittel | ≃8n <sup>3/2</sup>     | 1s                                                 |

| Galpat        | gut      | gut                  | gut                                                       | gut    | ≃4n²                   | 32s                                                |

A=Adressierung; D=Dekodierfehler; H=Halten auf O bzw. auf 1; K=Kurzschluß; LV=Leserverstärker-Erholungszeit; U=Unterbrechung; \*musterabhängig; \*\*muster- und niveauabhängig

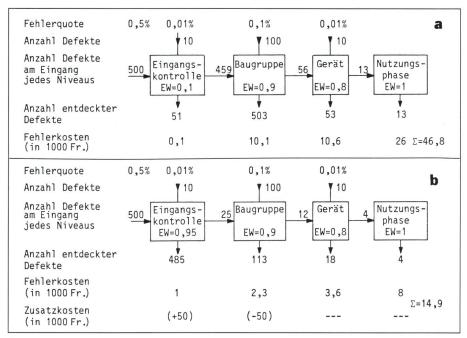

Figur 3 Zwei verschiedene Prüfstrategien im Vergleich

a Schwerpunkt Baugruppenprüfung

b Schwerpunkt Eingangsprüfung

ebene. Zur Illustration zeigt die Figur 3 an einem Beispiel zwei verschiedene Prüfstrategien [2]. In beiden Fällen geht es um die Herstellung einer bestimmten Anzahl Geräte, für welche total 100 000 Bauteile eines gegebenen Typs verwendet werden (z.B. LSI-ICs). Die Bauteile werden mit einer mittleren Fehlerquote von 0,5% geliefert. Im Laufe der Fertigung treten bei diesen Bauteilen infolge falscher Handhabung, Montage usw. weitere Defekte auf. Die entsprechenden Fehlerquoten betragen 0,01% auf Niveau Eingangsprüfung, 0,1% auf Niveau Baugruppe und 0,01% auf Niveau Gerät. Die Kosten für die Entdeckung und Eliminierung eines defekten Bauteils (Fehlerkosten) seien Fr. 2.- auf Niveau Eingangsprüfung, Fr. 20.- auf Niveau Baugruppe, Fr. 200.- auf Niveau Gerät und Fr. 2000.- in der Nutzungsphase. Die beiden Prüfstrategien unterscheiden sich in den Erkennungswahrscheinlichkeiten (EW). Diese betragen für die vier Niveaus 0,1, 0,9, 0,8 und 1 bei der ersten Prüfstrategie und 0,95, 0,9, 0,8 und 1 bei der zweiten Prüfstrategie. Es wird angenommen, dass die zusätzlichen Prüfkosten zur Erhöhung der Entdeckungswahrscheinlichkeit auf Niveau Eingangskontrolle Fr. -. 50 pro Bauteil betragen und durch die Einsparung bei den Prüfungen auf Baugruppenebene kompensiert werden. Wie die Figur 3 zeigt, ist für dieses Beispiel der Erwartungswert der Summe aus Fehlerkosten und

zusätzlichen Prüfkosten im Falle der zweiten Prüfstrategie kleiner als im Falle der ersten Prüfstrategie. Das Modell kann auch zur Erkennung von Schwachstellen im Fertigungsablauf (z.B. zu hohe Fehlerquote auf Niveau Baugruppe) und zur Untersuchung der Wirksamkeit von Massnahmen zur weiteren Senkung der Qualitätskosten verwendet werden.

Im folgenden wird die Frage der Wahl zwischen einer 100prozentigen und einer stichprobenweisen Eingangsprüfung (von Bauteilen oder Baugruppen) gründlich untersucht. Das Modell verwendet folgende Bezeichnungen [2]:

- $A_p$  Annahmewahrscheinlichkeit der Eingangsprüfung, d.h. Wahrscheinlichkeit, in einer Stichprobe vom Umfang n höchstens c defekte Bauteile zu finden (Funktion von  $p_f$ )

- c<sub>e</sub> Ersatzkosten pro Bauteil bei der Eingangsprüfung

- c<sub>f</sub> Folgekosten pro fehlerhaftes Bauteil

- c<sub>p</sub> Prüfkosten pro Bauteil

- K<sub>p</sub> Mittelwert der Gesamtkosten (direkt anfallende Kosten und Folgekosten) für die Eingangsprüfung eines Loses von N Bauteilen

- n Stichprobengrösse

- N Losgrösse

- pf Ausschusswahrscheinlichkeit bzw. Fehlerquote (in der Regel unbekannt).

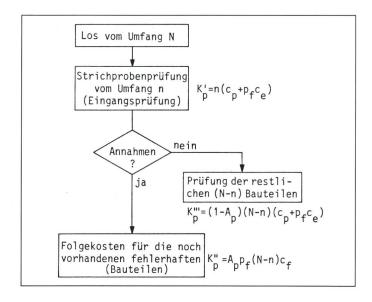

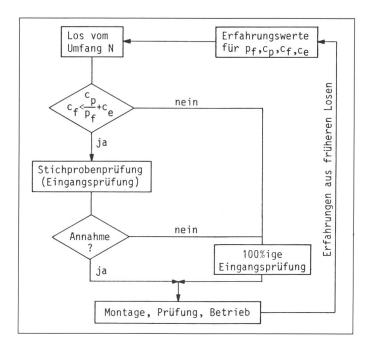

Die Figur 4 zeigt den theoretischen Ablaufplan einer solchen Prüfung. Gegeben sind die Mittelwerte (Erwartungswerte) der Kosten. Aus Figur 4 folgt für den Mittelwert der Gesamtkosten

$$K_{p} = K_{p}' + K_{p}'' + K_{p}''' =$$

$$n(c_{p} + p_{f}c_{e}) + (N - n)A_{p}p_{f}c_{f} +$$

$$+ (N - n)(1 - A_{p})(c_{p} + p_{f}c_{e})$$

$$= N(c_{p} + p_{f}c_{e}) + (N - n)A_{p}[p_{f}c_{f} - (c_{p} + p_{f}c_{e})]$$

(2)

Figur 4 Theoretischer Ablaufplan für die Eingangsprüfung

Die Untersuchung von (2) führt zu den folgenden vier Fällen:

- 1. Für  $p_f = 0$  gilt  $A_p = 1$  und damit  $K_p = n c_p$ . (3)

- 2. Für eine hundertprozentige Prüfung ist n = N und folglich

$$K_{p} = N(c_{p} + p_{f}c_{e}). \tag{4}$$

3. Für

$$c_{\rm f} < c_{\rm e} + \frac{c_{\rm p}}{p_{\rm f}} \tag{5}$$

ist  $K_p < N(c_p + p_f c_e)$  und damit eine Stichprobenprüfung billiger.

4. Für

$$c_{\rm f} > c_{\rm e} + \frac{c_{\rm p}}{p_{\rm f}} \tag{6}$$

ist  $K_p > N(c_p + p_f c_e)$  und damit eine hundertprozentige Prüfung billiger.

Der praktische Ablaufplan für die Eingangsprüfung ist in Figur 5 gezeigt. Da für die Ausschusswahrscheinlichkeit  $p_f$  des aktuellen Loses nur eine Schätzung aus den früheren Prüfungen bekannt ist, enthält der Ablaufplan gemäss Figur 5 als Sicherheit noch eine Stichprobenprüfung.

Das Modell von Figur 4 lässt sich unmittelbar auf den Fall einer Vorbehandlung direkt übertragen. Das Modell für die kombinierte Prüfung und Vorbehandlung ist in [2] untersucht. Wenn  $c_a$  die Folgekosten pro Frühausfall,  $c_v$  die Vorbehandlungskosten pro Bauteil und  $p_a$  die Ausfallquote bei der Vorbehandlung sind, so führen die gleichen Überlegungen wie die zu den Gleichungen (3) bis (6) zur Schlussfolgerung, dass für

$$p_{a}c_{a} + A_{p}p_{f}c_{f} + (1-A_{p})(c_{p}+p_{f}c_{e})$$

$$< c_{v} + (p_{a} + p_{f})c_{e}$$

(7)

eine stichprobenweise Prüfung mit Vorbehandlung billiger als eine 100prozentige Prüfung mit Vorbehandlung ist.

#### 6. Schlussfolgerungen

Bis zu den LSI-ICs sind die Methoden und Verfahren der Prüfung, Vorbehandlung und Qualifikation bekannt und weitgehend etabliert. Auch haben viele dieser Bauteile einen so

Figur 5 Praktischer Ablaufplan für die Eingangsprüfung

hohen Reifegrad erreicht, dass eine 100prozentige Eingangsprüfung bzw. Vorbehandlung nicht mehr unbedingt notwendig scheint. Für die VLSI-ICs und noch mehr für die ULSI-ICs aber sind neue Methoden und Verfahren nötig, einerseits wegen der neuen Fehlerquellen bzw. Ausfallmechanismen, die diese Bauteile charakterisieren, und anderseits weil zur Reduktion der Prüfzeit (Eingangsprüfung) die Frage der Prüfabdeckung bzw. der Fehlererkennungswahrscheinlichkeit besser als bis heute beantwortet werden muss.

Wichtige Aktivitäten auf diesen Gebieten sowohl für komplexe ICs als auch für Baugruppen und Systeme sind von der Fachgruppe Zuverlässigkeitstechnik der ETH Zürich mit grosser finanzieller Beteiligung der Industrie gestartet worden. Mit Hilfe leistungsfähiger Anlagen für Prüfungen und Ausfallanalysen wird eine Gruppe von Hochschulingenieuren die Themen Ausfallmechanismen, Prüfbarkeit, Prüf- und Vorbehandlungsstrategien, störungstolerante Strukturen sowie computerunterstützte Zuverlässigkeitsanalysen systematisch untersuchen.

Literatur

- R.T. Anderson et al.: Reliability design handbook RDH-376. Griffiss AFB, NY 13441: Rome Air Dev. Center, 1976.

- [2] A. Birolini: Qualität und Zuverlässigkeit technischer Systeme: Theorie, Praxis, Management. Berlin: Springer-Verlag, 1985.

- [3] R.G. Bennetts: Design of testable logic circuits. London: Addison-Wesley, 1983.

- [4] J. Bryon et al.: RADC testability notebook, RADC-TR-82-189. Griffiss AFB, NY 13441: Rome Air Dev. Center, 1983.

- [5] H. Fujiwara: Logic testing and design for testability. Cambridge, Massachusetts: The MIT Press, 1985.

- [6] T.W. Williams ed.: VLSI Testing. Amsterdam: North-Holland, 1986.

- [7] M. Zerbst et al.: Mess- und Prüftechnik. Berlin: Springer-Verlag, 1986.

- [8] MIL-STD-883, Test methods and procedures for micro-electronics, Ed. C, 1983. MIL-M-38510. Microcircuits: general specification for, Ed. E, 1981. MIL-HDBK-217, Reliability prediction of electronic equipment, Ed. E, 1986.

- [9] P.H. Welshinger et al.: Environmental stress screening questionnaire analyses. ESSEH-Reports, Inst. of environmental Sciences, Mount Prospect, IL 60056, 1981.

- [10] H.C. Rickers: Microcircuits screening effectiveness, TRS-1. Griffiss AFB, NY 13441: Rome Air Dev. Center, 1978.

- [11] A.E. Saari et al.: Stress screening of electronic hardware. RADC-TR-82-087. Griffiss AFB, NY 13441: Roma Air Dev. Center, 1982.

- [12] D. Karam: Burn-in: Which environmental stress screens should be used. RADC-TR-81-87. Griffiss AFB, NY 13441: Air Dev. Center, 1982.

- [13] D.L. Hough: "Effective efficient thermal screening". Proc. Annual Rel. & Maint. Symp., pp. 87...90, 1982.

- [14] T.D. Schonmaker et al.: "Predicting burn-in performance for a new design". Proc. Annual Rel. & Maint. Symp., pp. 423...428, 1983.

- [15] G.F. Kujawski: "Effects of 'On-off' cycling on equipment reliability". Proc. Annual Rel. & Maint. Symp., pp. 225...230, 1978.

- [16] E.W. Derenthal et al.: "Reliability growth, screened vs nonscreened computers". Proc. Annual Rel. & Maint. Symp., pp. 74...78, 19.

- [17] J.H. Chin et al.: "Reliability growth through an integrated test approach—A case history". Proc. Annual Rel. & Maint. Symp., pp. 432...438, 1982.

- [18] D.M. Marko: "Optimizing spare module burn-in". Proc. Annual Rel. & Maint. Symp., pp. 83...86, 1982.

- [19] J.L. Capitano et al.: "Environmental stress screening (ESS) demonstrates its value in the field". Proc. Annual Rel. & Maint. Symp., pp. 31...35, 1986.

- [20] D.M. Keith: "A report on a survey of the specification and attainment of reliability in communications equipment". Proc. Annual Rel. & Maint. Symp., pp. 579...593, 1975.

## Sie können ruhig zu Hause bleiben. Wir fahren für Sie.

Weshalb sollten Sie Ihre Zeit, Energie und Ihr Geld verschwenden, wenn es uns am Wege liegt? Unser Zustelldienst mit eigenen Camions verkehrt fahrplanmässig.

Und wichtig für Sie: Unsere erfahrenen, zuverlässigen Chauffeure wissen, wie man mit Ihrem wertvollen Aluminium umgeht.

#### Allega AG

Verkaufsgesellschaft der Schweizerischen Aluminium AG Buckhauserstrasse 5

8048 Zürich Telefon 01/497 41 11 Telefax 01/497 43 44 Telex 822 339

# ALLEGA für Aluminium © 01/4974111

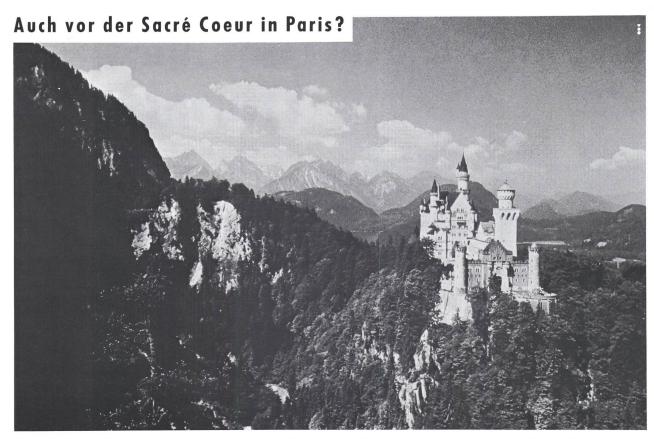

**Auch vor der Sacré Coeur in Paris!** «Tja, Sie waren ja nicht erreichbar.» Diesen Vorwand für ein Fait accompli gibt es nicht mehr. ■ Sie können unterwegs sein, wo Sie wollen: Wenn Sie wollen, sind Sie überall auf

Nicht grösser als ein Päckchen Zigaretten: der Eurosignalempfänger RE828, mit dem Sie auch ausserhalb der Schweiz erreichbar sind.

Empfang. Auch mitten im Gotthardtunnel. Auch im Schloss Neuschwanstein. Autophon, der schweizerische Spezialist für Rufsysteme, lässt Sie nirgends ohne Verbindung. Im Auto meldet Ihnen der Autoruf, dass jemand Ihren Rückruf erwartet. Oder Sie haben das Natel Autotelefon, dann sind Sie direkt verbunden. Im Tram, im Taxi, auf der Strasse: Ihre Sekretärin, sogar Ihr Anrufbeantworter kann Sie per Citycall erreichen. Auch im stillsten Winkel Europas stellt Ihnen das Eurosignal eine dringende Nachricht zu

(in CH, F, D). Autophon hat die Geräte mit vielen raffinierten

Zusatzfunktionen ausgestattet: Signale verschiedener Bedeutung, Termin-Mahner etc. Und wollen Sie wirklich absolut ungestört sein, schalten Sie auf Funkstille. ■ Ein Gespräch verpflichtet Sie zu nichts. Bitte schicken Sie uns den Coupon.

Autophon AG, Radiocom, Hauptsitz in Zürich, Entwicklung und Fabrikation in Solothurn. Niederlassungen und Betriebsbüros CH: Zürich, St. Gallen Basel, Bern, Luzern, Viganello, Chur, Winterthur, Olten, Biel, Neuchätel. In der Westschweiz: Téléphonie SA Lausanne, Sion, Genève-Carouge.

| An Autophon AG, Radiocom,<br>Feldstrasse 42, 8036 Zürich, Tel. 01 248 13 13                     |

|-------------------------------------------------------------------------------------------------|

| ☐ Bitte schicken Sie mir Informationsmaterial zum Thema☐ Ortsruf☐ Autoruf CH☐ Eurosignal☐ Natel |

| ☐ Bitte rufen Sie mich an, um einen Gesprächstermin zu vereinbaren.                             |

| Name:                                                                                           |

| in Firma:                                                                                       |

| Strasse:                                                                                        |

| PLZ/Ort:                                                                                        |

| Telefon:                                                                                        |

| L                                                                                               |

### ZnO-Varistoren schützen

Eine neue Reihe von VDR-Widerständen für Schutzschaltungen ergänzt die Zinkoxid-Varistoren-Familie von Philips. Diese weist einen nach unten bis 30 V erweiterten Spannungsbereich auf. Die Scheiben sind zur Erhöhung der Isolationsspannung und für bessere mechanische Festigkeit mit einer Epoxid-Umhüllung versehen.

Schnellinfo Telefon 01-488 27 19 H. Müller

Philips Bauelemente – die sichere Technologie

Philips AG · Elcoma · Postfach · 8027 Zürich · Tel. 01 - 488 22 11

Bauelemente für die Elektronik **PHILIPS**

# Haefely simuliert Transienten

- Blitzstossspannungen und Ströme nach IEC, IEEE, SAE u.a.

bis 10000 kV/500 kA

- Schaltimpulse

- elektrostatische Entladungen

- NEMP nach NATO Normen und Kundenanforderungen von 0,5 bis 1500 kV, Einzel- und sich repetierende Impulse

- EMV Testgeräte

- Prüfung von Avionics und Flugzeugen nach MIL 461/RSD 5, CS 10 und 11; SAE, AIRBUS usw.

Transientenprüfgeräte für elektronische Komponenten, Baugruppen und Systeme.

Type PSD 15 A für die Simulation von Entladungen statischer Energie bis 15 kV, nach IEC 801-2; Typ RSD 25 A bis 25 kV

PEMI 12 Steilstossgenerator für EMP Simulation bis 12 kV; 50 kV/m E-Feld 130 A/m H-Feld

Burst Generator nach IEC TC65/WG4, erzeugt sich repetierende Spikes bis 4 kV Inpulsform 5/50 ns 8 kV Modul als Zusatz erhältlich

Wenn es Ihnen wichtig ist, ob Ihre Produkte immun gegen transiente Vorgänge sind, sollten Sie mit uns sprechen.

## **HAEFELY**

High Voltage Test Systems Emil Haefely & Cie AG Postfach CH-4028 Basel/Schweiz Tel.: 061/53 51 11 High Voltage Test Systems Micafil GmbH Postfach 4301/44 D-4600 Dortmund 41 Tel.: 0231/40 24 95