|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 78 (1987)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 11                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | Evaluation de la qualité des circuits intégrés                                                                                                                                                                            |

| <b>Autor:</b>       | Frauche, J.-P.                                                                                                                                                                                                            |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-903875">https://doi.org/10.5169/seals-903875</a>                                                                                                                                   |

### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 18.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Evaluation de la qualité des circuits intégrés

J.-P. Frauche

**L'évaluation de la qualité des circuits intégrés nécessite une large investigation de toutes les possibilités de défaillances.**

**Un centre d'évaluation a été mis sur pied dans le cadre du Centre suisse d'Essais des composants électroniques CSEE (ASE). Le travail prévu comporte des analyses de la construction et de l'encapsulation des circuits, ainsi que des essais de déverminage et de durée de vie conduits en parallèle. L'ampleur des essais permettra de prouver un taux de défaillances meilleur que un par 10<sup>7</sup> heures pendant 20 ans.**

**Um die Qualität von integrierten Schaltungen evaluieren zu können, müssen alle ihre möglichen Ausfallarten eingehend untersucht werden. Im Schweizerischen Prüfzentrum für elektronische Komponenten CSEE (SEV) wurde ein Evaluationszentrum gegründet. Die vorgesehene Evaluationsarbeit umfasst Konstruktions- und Verpackungsanalysen der Schaltung sowie Vorbehandlungs- und Lebensdauerprüfungen. Die Schlussüberlegungen zeigen, dass der vorgeschlagene Prüfumfang genügt, um eine Fehlerrate von besser als 1 Ausfall pro 10<sup>7</sup> Stunden während 20 Jahren vorherzusagen.**

## Adresse de l'auteur

Jean-Pierre Frauche, Ing. dipl. EPFL, CSEE, ruelle Vaucher 22, 2000 Neuchâtel.

## 1. Introduction

Le terme de qualité des circuits intégrés concerne leur aptitude à être utilisés. L'évaluation de cette qualité va donc se baser sur l'examen d'une grande variété de propriétés. Il faut tenir compte de toutes les phases de l'utilisation: manutention, montage et soudage, stockage, utilisation proprement dite.

Pour une entreprise, l'utilisation elle-même n'est pas définie en détail. Un type de circuit ne va pas être réservé pour un appareil qui sera vendu dans une ville précise. Au contraire, il est souhaitable que le circuit soit bien adapté à la plus grande partie des produits de l'entreprise. Les cas particuliers devront soit faire appel à de meilleurs circuits plus chers, soit admettre une augmentation du risque de panne.

Il y a donc une grande part d'inconnu dans les contraintes que vont subir les circuits intégrés. De la même manière, les circuits eux-mêmes sont à priori inconnus et n'importe quel défaut peut apparaître. En pratique, toutes les analyses de défaillances, les essais décrits dans les normes et les essais proposés dans la littérature fournissent une connaissance de base qui permet de limiter le champ d'investigation.

Le travail de normalisation (MIL, CECC, etc.) de la qualité des circuits intégrés passe par l'édification d'une feuille de spécification détaillée (par exemple MIL M38510 Slash Sheet) qui décrit non seulement le fonctionnement du circuit mais aussi sa constitution et les tests que doit subir le circuit pour obtenir son label. Si l'on réfléchit sur le rôle d'une spécification bien faite, on voit qu'elle doit permettre non seulement à l'utilisateur de comprendre le fonctionnement du circuit, mais aussi de le garantir en décrivant des possibilités de test et de mesure couvrant toute la plage de fonctionnement. La rédaction d'une telle spéci-

fication exige une somme de travail considérable dans des essais préliminaires. Il en résulte un certain délai. L'évolution très rapide des circuits intégrés dans le domaine VLSI (Very Large Scale Integration) n'a pas permis aux systèmes de normalisation de coller à l'actualité. Dès lors, chaque utilisateur a créé sa propre homologation de circuits sur la base des feuilles de données des fournisseurs et en la complétant par sa propre expérience. En vue d'aider ces activités, si possible en regroupant les efforts, le CSEE a été conduit à créer un centre d'évaluation de la qualité des circuits intégrés. Son programme reste relativement ponctuel puisqu'il n'est pas possible de suivre en permanence toute la production de tous les circuits. Mais il devrait suivre au mieux l'évolution de la complexité des circuits et se situer juste au moment où la production de série démarre. Ce choix devrait permettre d'éviter la période où les corrections de la construction (redesign) sont fréquentes.

## 2. Organisation du travail

Notre travail va s'appuyer le plus possible sur la connaissance des modes de défaillances et des causes de ces modes:

- du point de vue externe, c'est-à-dire par les contraintes et les opérations subies par les ICs,

- du point de vue interne, c'est-à-dire selon la constitution des ICs qui peut plus ou moins être prédisposée à ces défaillances.

### 2.1 Analyse de construction

Au départ, la constitution de chaque type de circuit sera analysée. Les principales caractéristiques du chip, des connexions et de l'encapsulation seront déterminées (tab. I).

| Zone               | Condition | Méthode                                          | Information                                                                                                                                                                             |

|--------------------|-----------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Boîtier            | Etanche   | Classement                                       | Céramique<br>Cerdip glass seal<br>Cerdip frit seal                                                                                                                                      |

|                    | Plastique | Analyse                                          | Composition du plastique<br>Quantité relative de charge<br>Granulométrie de la charge                                                                                                   |

| Grille             |           | Analyse                                          | Composition du métal                                                                                                                                                                    |

| Bonds              |           | Classement                                       | Méthode de Bonding                                                                                                                                                                      |

| Die attach         |           | Classement                                       | Eutectique<br>Plastique                                                                                                                                                                 |

| Puce<br>(Die=chip) |           | Photographie<br>Classement<br>Analyse<br>Analyse | Enregistrement du type<br>Technologie de base :<br>Bip. - MOS - CMOS<br>Caractéristiques les plus<br>accessibles : métallisation,<br>ordre des masques etc.<br>Intégrité de passivation |

Tableau I Analyse de construction

## 2.2 Etude électrique et thermique

Une étude électrique et thermique fournira quelques éléments supplémentaires de caractérisation des circuits (tab. II).

## 2.3 Déverminage

Le déverminage (Screening, Vorberhandlung) est en général défini, dans les normes, comme une suite fixe d'essais. Dans l'approche du CSEE, les méthodes d'essai seront séparées afin de déterminer dans quelle mesure elles permettent de mettre à jour des défauts de jeunesse. Par exemple: les cycles de température mettent à jour les problèmes de dilatation. Est-ce que les dix premiers cycles éliminent les mauvais circuits, et les circuits restants supporteront-ils les milliers de cycles de la vie active?

Le programme du CSEE a pour but d'examiner le déverminage comme une opération adaptable et justifiée pour un but précis, contrairement à l'usage courant. L'étude de qualité va permettre de définir si les composants comportent des défauts de jeunesse et quelles opérations seront aptes à les éliminer. On peut classer les méthodes définies par les normes en trois catégories:

a. Les méthodes qui mesurent un paramètre qui est d'importance vitale

pour le bon fonctionnement ultérieur du circuit:

- test d'étanchéité,

- détection de bruit d'impact de particules,

- test électrique,

- examen visuel,

- radiographie,

- test électrique de continuité à haute température.

b. Les méthodes qui soumettent le circuit à des contraintes qui risquent de lui arriver pendant sa vie:

- accélération constante,

- nondestructive Bond Pull.

c. Les méthodes qui simulent les premières heures de vie du circuit:

- stockage à haute température,

- variations de température,

- rodage (burn-in).

Toutes ces méthodes sont utilisées par les normes de déverminage: MIL883C-Méthode 5004, CECC 90000, MIL-HDBK217D. Une grande part concerne uniquement les boîtiers céramiques où l'on désire assurer une bonne tenue mécanique et l'étanchéité sous des contraintes mécaniques et de dilatation. Pour les boîtiers plastiques, on ne retient que les méthodes destinées à mettre en évidence des modes de défaillances selon la présentation suivante:

- *Stockage à haute température*: défaut de la puce (dispersion de charges, etc.); défaut dû à des relaxations mécaniques.

- *Variations de température*: défaut de connexion dû à la dilatation; fissures de la puce dues à la dilatation.

- *Rodage (burn-in)*: défaut de la puce (concentration ou mouvement de charges, etc.).

Ces méthodes sont reprises par le contrôle de qualité qui en prolonge la durée pour en faire des méthodes de test de durée de vie. Il faudra pouvoir déterminer lors de ces tests l'allure de la courbe du taux de défaillance afin

| Analysé                      | Méthode                                                                                                                         |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| ESD                          | Résistance à des chocs de tension augmentant par pas.<br>Mode de défaillance type (caractérisation électrique des défaillances) |

| Susceptibilité au latch-up   | Injection de courants pos. et neg. augmentant par pas sur entrées et sorties jusqu'à l'apparition d'une dégradation             |

| Thermique                    | Augmentation de température par échauffement propre.<br>Vitesse d'augmentation de la température                                |

| Transistors                  | Caractéristiques de sortie à l'état conducteur                                                                                  |

| Écriture des EPROM et EEPROM | La vitesse d'écriture donne une indication sur la conservation des charges.                                                     |

Tableau II Etude électrique et thermique

| Mécanisme de défaillance                                           | Mise sous contrainte                                                              |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Oxide shorts<br>Dielectric breakdown                               | Accélération par haute tension d'alim. (champ électr. élevé dans oxyde de grille) |

| Electromigration                                                   | Haute température sous tension, charge maximale                                   |

| Micro cracks                                                       | Dilatation par cycles thermiques                                                  |

| Slow trapping<br>Ionic contamination<br>Surface charge spreading ) | Haute température sous tension                                                    |

| Hot electron trapping                                              | Basse température, haute tension d'alimentation                                   |

| Charge loss in EPROM                                               | Haute température                                                                 |

| Charge trapping in EPROM                                           | Cycles d'écriture-effacement répétés                                              |

| Corrosion through bulk humidity                                    | Température, humidité, sous tension intermittente                                 |

| Cleaving plastic-metal                                             | Dilatation par cycles thermiques                                                  |

| Corrosion through lead leakage                                     | Préconditionnement par eau salée, haute pression, haute température               |

| Alloying (Al-Si contact punch)<br>(Al-Au purple plaque)            | Haute température                                                                 |

| Debonding                                                          | Dilatation par cycles thermiques (fatigue)                                        |

| Mechanical failure of ceramic                                      | Température, cycles thermiques, accélération, étanchéité.                         |

Tableau III Mécanismes de défaillances

de connaître l'efficacité du déverminage.

Le seul point délicat concerne les variations de température, qui devraient permettre d'éliminer les pièces trop faibles dans leurs connexions. Mais cette même méthode peut introduire un décollement entre plastique et grille de métal, ce qui conduit à une diminution de la résistance à la corrosion.

## 2.4 Contrôle de qualité

Le contrôle de qualité fait appel à une gamme très vaste d'essais. Si les méthodes ne sont pas destructives, elles peuvent être candidates comme méthode de déverminage. C'est donc tout un lot ou un sous-lot qui subira ces méthodes de contrôle de qualité afin de pouvoir juger de manière statistiquement valable de l'évolution du taux de défaillance. Les essais doivent être représentatifs de la durée d'emploi désirée afin de mettre aussi en éviden-

ce des modes de défaillances significatifs de la fin de vie d'une population d'IC. En introduisant systématiquement une recherche du mécanisme de

Tableau IV

Les différentes méthodes d'essai

défaillance, on évitera de masquer les modes de défaillances liés au temps par des modes provenant de causes différentes (décharges électrostatiques, etc.).

Le déroulement des procédures selon les normes se présente comme une suite fixe d'essais déjà optimisés pour un certain niveau de qualité. Le travail du CSEE, au contraire, sera d'abord orienté par les mécanismes de défaillances qui vont être mis en action par divers essais de sévérités différentes.

Dans le tableau III, on fait correspondre les mécanismes de défaillances avec la méthode de mise sous contrainte.

Les effets sur la fiabilité des mécanismes «dielectric breakdown» et «hot electron trapping» sont encore insuffisamment connus, ils ne seront pas retenus dans nos premiers essais.

Tous les autres mécanismes sont mis en évidence par des contraintes qui sont présentes dans les différentes méthodes d'essai du tableau IV.

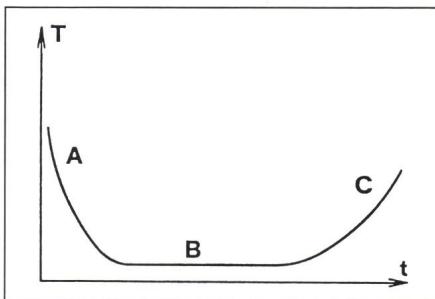

La sévérité des essais est caractérisée par le niveau des contraintes et la durée de l'essai. Si une loi d'accélération est connue, il n'est pas nécessaire de faire l'essai à plusieurs niveaux. La durée est définie par l'instant de la mesure. En effet, deux tests de même contrainte et de durées différentes se réduisent à un test avec deux mesures. Pour définir ces instants de mesure, il faut revenir à la courbe en baignoire (fig. 1). La zone A correspond aux défauts de jeunesse. Les mesures effectuées pendant cette durée doivent permettre de conclure sur l'efficacité d'un déverminage selon cet essai et de fixer la durée optimale du déverminage. La

|                                              |

|----------------------------------------------|

| Essai à froid et haute tension               |

| Stockage à haute température                 |

| Burn-in statique                             |

| Durée de vie à haute température (dynamique) |

| Cycles thermiques                            |

| Essai accéléré d'humidité sous tension       |

| Autoclave avec préconditionnement au sel     |

| Choc thermique de soudage                    |

| Cycles écriture-lecture (pour EEPROM)        |

Figure 1 Courbe en baignoire

T Taux de défaillance

t temps

zone B correspond à la vie du circuit. Le nombre de pièces et la durée de l'essai doivent être suffisants pour calculer un taux de défaillances ou s'assurer qu'il se situe au-dessous d'une certaine limite. La zone C correspond à la fin de la vie des circuits. On veut savoir à quel moment ce phénomène de dégradation intervient ou être sûr qu'il n'arrive pas avant une certaine durée d'utilisation des circuits. En supposant un environnement «moyen», on peut calculer un facteur d'accélération de l'essai et déterminer de cette manière la durée nécessaire de l'essai.

Les différentes méthodes d'essai se présentent selon le tableau IV. Le burn-in statique n'est considéré que dans la partie déverminage (zone A de la courbe baignoire). Son efficacité est mesurée en passant ensuite les pièces à l'essai de durée de vie dynamique. Par analogie, le burn-in dynamique est constitué par les premières heures subies par les pièces soumises à l'essai de durée de vie. Les cycles thermiques ont un double aspect. D'une part, ils peuvent rompre des liaisons par dilatation, et les premiers cycles peuvent jouer un rôle de déverminage. D'autre part, ils peuvent décoller la grille métallique du plastique et créer des possibilités d'entrée de l'humidité. Il sera nécessaire de vérifier à chaque étape si c'est le cas par le test à l'autoclave.

### 3. Organisation des essais

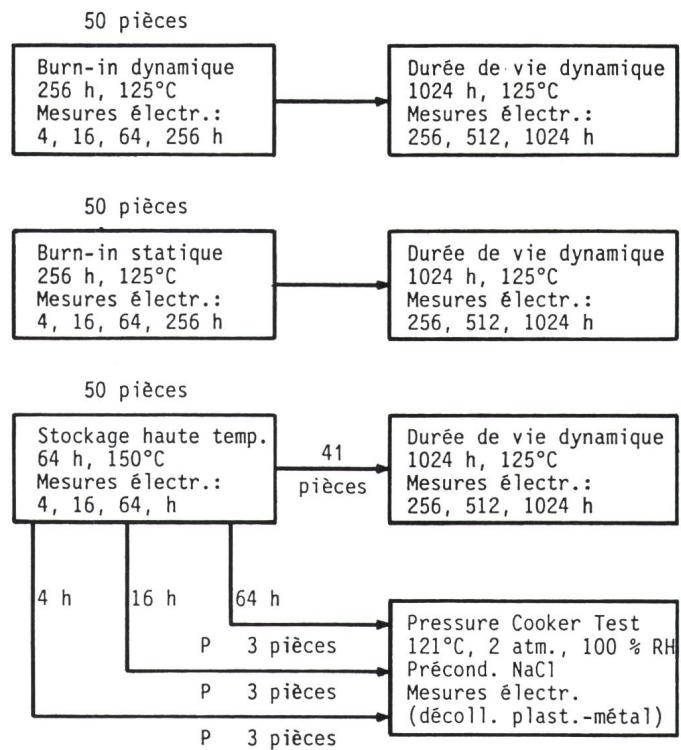

Sans vouloir figer définitivement les diverses valeurs utilisées, le plan des essais se présenterait de la manière suivante.

#### 3.1 Plan des essais

Les circuits soumis aux essais seront séparés en sous-lot de manière à pouvoir commencer toutes les investigations en parallèle. Ces essais sont les suivants:

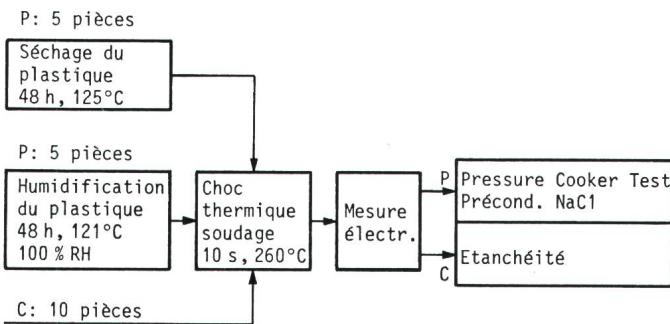

Figure 2 Essai de durée de vie

C encapsulation céramique

P encapsulation plastique

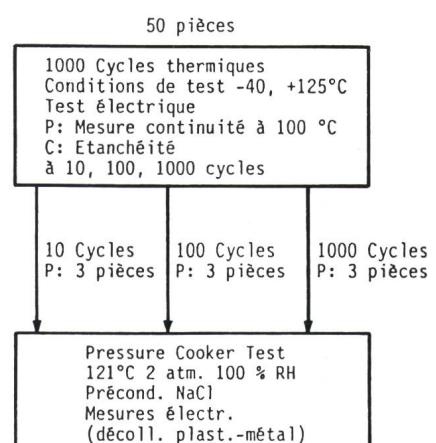

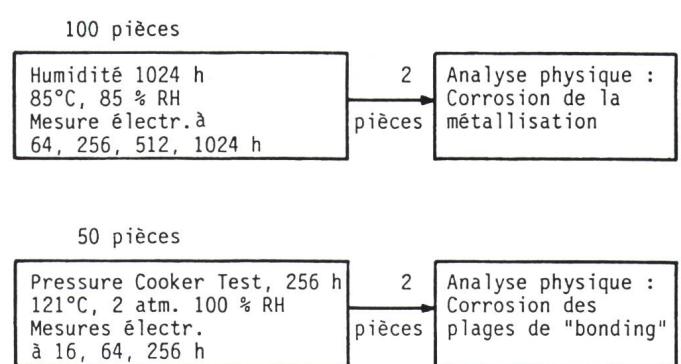

- essai de durée de vie (fig. 2)

- cycles thermiques (fig. 3)

- essais d'humidité (fig. 4)

- chocs thermiques (fig. 5)

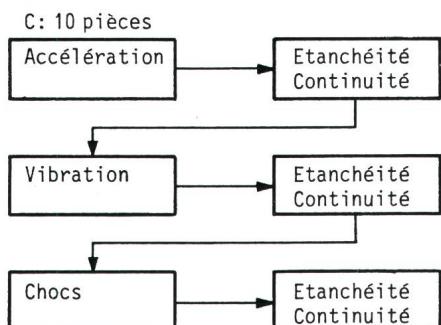

- essais mécaniques (fig. 6)

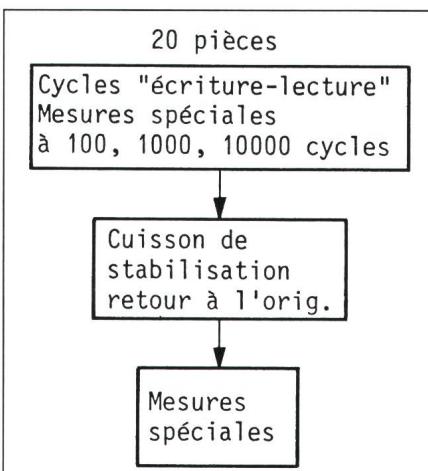

- essais des mémoires (fig. 7).

#### 3.2 Intentions définissant l'ampleur des tests

Le choix des sévérités part de l'idée que les circuits doivent être utilisables pendant 20 ans sans atteindre des phénomènes de fin de vie (partie C de la courbe de défaillance) et que le taux de défaillances devrait être meilleur que 100 FIT (= 100 déf. en 10<sup>9</sup> heures-composants). Il reste encore plusieurs

Figure 3 Cycles thermiques

Figure 4

Essai d'humidité

Figure 5

Choc thermique

paramètres à définir avant de pouvoir faire correspondre les résultats obtenus dans les conditions d'essais avec ceux espérés en utilisation.

### 3.3 Environnement d'utilisation

En pratique, cet environnement change d'une utilisation à l'autre. Mais une partie des grands utilisateurs de circuits intégrés de Suisse prévoit un climat de classe F selon la norme Din 40040. Ceci conduit à des conditions annuelles:

- 30 jours à 23 °C et 85% RH,

- 335 jours à 21 °C et 75% RH.

On admet que l'échauffement propre du circuit est le même dans les conditions d'utilisation et d'essai et qu'il peut être négligé dans une approximation grossière. Par contre, lors de l'utilisation, le circuit est placé dans un appareil pour lequel on prévoira un échauffement intérieur de l'appareil de 20 °C (au total température ambiante + échauffement de l'appareil + échauffement propre du circuit). Cet échauffement n'existe pas dans les essais de circuits (au total température de l'essai + échauffement propre du circuit).

Figure 6

Essais mécaniques

### 3.4 Facteurs d'accélération

Pour l'essai de durée de vie à 125 °C, on choisit une énergie d'activation  $E_a$  de 0,7 eV dans la loi d'Arrhenius:

$$FA = \exp(E_a/kT_1 - E_a/kT_2) \quad (1)$$

avec  $k$  = constante de Boltzman.

Ceci nous conduit à un facteur d'accélération  $FA$  moyen annuel de 235 entre l'étuve à 125 °C et les conditions

Figure 7

Essai de mémoires EEPROM

du paragraphe 3.3 (23+20 °C et 21+20 °C). Pour l'essai d'humidité à 85 °C et 85% RH, on utilise la formule de British Telecom:

$$FA = \exp[4,4 \cdot 10^{-4}(RH_s^2 - RH_0^2) + 7 \cdot 10^3(T_0^{-1} - T_s^{-1})] \quad (2)$$

ce qui conduit à un facteur d'accélération de 136 entre l'étuve à 85 °C et 85% RH et les conditions du paragraphe 3.3 [1].

### 3.5 Durée des essais

Avec ces valeurs, une durée d'utilisation de 20 ans est simulée par 745 heures pour l'essai de durée de vie et par 1287 heures pour l'essai d'humidité. Ces valeurs dépendent directement des hypothèses faites pour le calcul des facteurs d'accélération. Une modification des conditions d'environnement ou de l'énergie d'activation peut entraîner de grandes variations dans ces durées.

### 3.6 Niveau de confiance

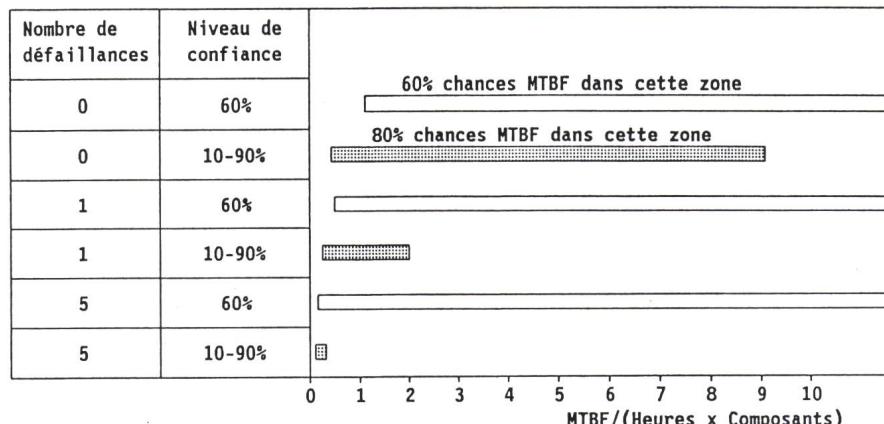

Etant donné le nombre d'heures-composants d'un essai et le nombre de défaillances, il faut encore spécifier un niveau de confiance pour pouvoir calculer une zone où se situera la valeur du  $MTBF^1$  de la population de circuits dont le lot est extrait.

La limite inférieure du  $MTBF$  correspond à la limite supérieure du taux de défaillances. Pour cette raison, le niveau de confiance correspondant est appelé «Upper Confidence Level» (UCL). En prenant une confiance faible de 60%, on trouvera une valeur limite de  $MTBF$  qui peut souvent être débordée. Toutefois, elle se situe vers la moyenne des  $MTBF$  pouvant donner les résultats de notre essai.

La figure 8 représente le rapport entre le  $MTBF$  et le nombre d'heures-composants, selon la quantité de défauts obtenus et selon les niveaux de confiance choisis. Plus le nombre de défaillances augmente, plus la gamme dans laquelle le  $MTBF$  doit se trouver est restreinte.

### 3.7 Nombre de pièces à tester dans les essais de durée

Il est intéressant de pousser les essais jusqu'à l'obtention de défaillances. Il devient ainsi possible de voir quels mécanismes de défaillance sont mis en jeu. Toutefois, ce genre de raisonnement conduit à un coût prohibitif si les circuits sont de bonne qualité. Il est acceptable de n'avoir pas ou que peu de défaillances si les circuits sont de la qualité désirée. Dans le cas contraire, il apparaîtra suffisamment de circuits défectueux pour l'analyse de défaillance.

Le taux de défaillance de 100 FIT correspond à un  $MTBF$  de 10<sup>7</sup> heures.

<sup>1</sup> MTBF: temps moyen entre défaillances; on admet un risque de défaillance constant au cours du temps.

Figure 8 Zones de MTBF prévisibles

En plaçant cette valeur comme limite à 60% de confiance et en n'admettant aucune défaillance, l'ampleur de l'essai doit être de  $0,9 \cdot 10^7$  heures · composants. Si l'essai accéléré représente 20 ans ( $= 175\,000$  h), le nombre de pièces doit être de 51. Par le même calcul, avec une défaillance admise, le nombre de pièces doit être de 114 et avec cinq défaillances de 354.

### 3.8 Résistance aux cycles thermiques

Chaque utilisation peut conduire à des profils de cycles thermiques très

variables. Une mise sous tension quasi-permanente ne conduira pas à plus de 20...50 cycles significatifs. Mais trois enclenchements par jour correspondent à 21 900 cycles. L'ampleur des cycles variera aussi beaucoup. On obtiendra probablement beaucoup de cycles d'amplitude restreinte et peu de cycles de grande amplitude. Dans les essais, on utilise en général des contraintes élevées. Si le premier essai de 1000 cycles produit trop de défaillances, un deuxième essai avec des contraintes plus proches de la réalité sera entrepris. La résistance au choc thermique de la soudure sera examinée dans un essai séparé.

## 4. Conclusion

Ce programme est loin d'être définitif. D'un côté, il implique des coûts élevés pour le mener à bien, d'autre part, il peut être encore augmenté sur de nombreux aspects. Lors du travail effectif, il faudra adapter avec la plus grande précision possible les moyens disponibles avec le programme d'essais. Il ne faudra pas non plus diminuer trop l'ampleur des essais parce qu'ils perdraient toute signification.

Toutefois, on ose espérer que cette présentation explique dans quel esprit ce programme est entrepris et de quelle manière on désire dépasser les essais liés au test d'entrée pour arriver à des essais liés à la durée de vie et au taux de défaillances. Ces informations sont indispensables pour améliorer le travail des constructeurs, de la planification et du service des achats.

## Bibliographie

- [1] R.W. Lawson: A review of the status of plastic encapsulated semiconductor component reliability. British Telecom Technology Journal, 2(1984)2, p. 95...111.

- [2] A. Birolini: Zuverlässigkeitssicherung komplexer Systeme. Teil 1 und Teil 2. Bull. SEV/VSE 70(1979)3, S. 142...148, und 70(1979)5, S. 237...243.