**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 78 (1987)

Heft: 11

**Artikel:** Test des circuits logiques combinatoires CMOS

**Autor:** Perotto, J.-F.

**DOI:** https://doi.org/10.5169/seals-903874

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF: 29.11.2025**

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Test des circuits logiques combinatoires CMOS

J.-F. Perotto

Le test des circuits intégrés réalisés en technologie CMOS ne peut plus reposer sur les principes développés pour les technologies bipolaires. Des approches spécifiques doivent être mises en œuvre pour la génération des vecteurs de test, tenant compte des particularités du transistor et des circuits MOS. Cet article présente une telle approche permettant la génération du test complet des circuits logiques combinatoires réalisés en technologie CMOS.

Die für Bipolarschaltungen gültigen Testprinzipien können nicht ohne weiteres auf CMOS-ICs übertragen werden. Diese verlangen spezifische Verfahren der Testvektorgenerierung, welche den Eigenheiten der CMOS-Technik Rechnung tragen. Dieser Artikel beschreibt ein Vorgehen, das einen umfassenden Test von kombinatorischen CMOS-Schaltungen erlaubt.

### Adresse de l'auteur

J.-F. Perotto, Ing. ETS, Centre Suisse d'Electronique et de Microtechnique S.A. (CSEM), Maladière 71, 2000 Neuchâtel 7.

### 1. Introduction

Lors de la fabrication d'une plaquette de circuits intégrés, d'inévitables imperfections technologiques font qu'une fraction seulement des circuits présente un fonctionnement correct. Une opération de test, appliquée successivement à tous les circuits de la plaquette, permet d'éliminer ceux présentant une défectuosité. Le test consiste à appliquer des stimulus (vecteurs) au circuit et à observer la conformité des réponses avec une référence pré-établie.

L'incidence du test sur le coût d'un circuit dépend de deux facteurs: coût de développement du programme de test et coût d'application du test luimême. Cette incidence croît rapidement avec la complexité du circuit. Dans le cas des circuits VLSI actuels, entre 10 et 30% du prix du circuit revient au test. Afin d'éviter que la situation n'empire, les concepteurs et fabricants de circuits intégrés doivent disposer d'outils efficaces d'aide à la mise au point rapide de programmes de test fortement optimisés. Cet article présente le principe de base d'un de ces outils en développement au CSEM dans le cadre d'un projet de testabilité des circuits intégrés digitaux complexes.

### 2. Généralités sur le test

La majorité des circuits digitaux complexes sont constitués de modules fonctionnels de nature très diverse: ALU, atuomates, PLA, mémoires ROM et RAM, etc. Le test de tels circuits ne peut s'envisager rationnellement que sous la forme d'une vérification individuelle des modules. A chaque classe de modules correspondra une approche spécifique à la génération des vecteurs de test. L'approche présentée ici a trait à la génération des vecteurs permettant le test complet des portes logiques CMOS.

L'approche proposée est du type déterministe. Les vecteurs testant le circuit ont été générés préalablement et constituent un ensemble fixe, appelé ensemble de test ou plus simplement test. La génération de cet ensemble fait appel à une description du circuit, un modèle de fautes et un algorithme de génération. Le test est caractérisé par son taux de couverture des fautes ou plus simplement couverture, qui représente le rapport entre le nombre de fautes détectables et le nombre total de fautes pouvant apparaître dans le circuit. La qualité d'un test sera d'autant meilleure qu'il sera compact et à forte couverture.

# 3. Le test en technologie CMOS

La quasi-absence de courant statique dans les branches des circuits logiques CMOS pose un problème particulier de test: l'apparition de fautes séquentielles. Certains défauts transforment les circuits combinatoires en circuits séquentiels. La prise en compte de cet effet impose la mise au point d'une approche spécifique à la génération du test en technologie CMOS.

### 3.1 Modèle de fautes

Le modèle de fautes représente l'ensemble des types de fautes pouvant apparaître dans le circuit. Le modèle de fautes dépendra fortement de la technologie utilisée pour la réalisation du circuit. Ainsi, le modèle de collage simple (voir encadré 1), largement utilisé pour le test des circuits logiques réalisés en technologie bipolaire (TTL par exemple), présente une faible couverture lorsqu'il est appliqué à la génération du test en technologie CMOS. L'inadéquation du modèle de collage simple au cas du test CMOS conduit à l'abandon des méthodes classiques de génération des vecteurs [1; 2].

### E1 Défauts, fautes et modèle de collage

Les défauts physiques apparaissant dans les circuits intégrés peuvent être représentés par leurs effets au niveau électrique ou logique. L'ensemble de ces effets, appelés fautes, constitue le *modèle de fautes* de la technologie considérée.

Le modèle de fautes le plus simple suppose que tout défaut dans une porte logique se traduit par le «collage» de sa sortie à l'un des états logiques 0 ou 1. Le terme «collage» signifie que le défaut est permanent et indépendant des conditions d'entrées du circuit. La figure représente le cas d'une porte NOR dont la sortie est collée à l'état 0, respectivement à l'état 1.

Figure E1 Collé-à-faute

La faute de collage généralisée s'exprime par «stuck-at-fault» (collé-à-faute), ou de manière plus simple «s-fault». Ainsi, le collage simple à 1 ou 0 s'écrira «s-1» et «s-0». Des modèles de collage plus complexes sont utilisés actuellement pour rendre compte des défauts pouvant apparaître dans les technologies MOS et CMOS.

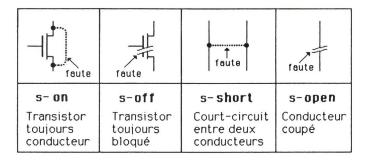

Le modèle de fautes adapté à la technologie CMOS possède quatre composantes: transistor toujours conducteur (notée s-on) ou toujours bloqué (s-off), conducteurs en court-circuit (s-short) ou coupés (s-open). Ce modèle, représenté à la figure 1, permet de rendre compte de la majorité des fautes apparaissant dans les circuits logiques CMOS [3; 4].

### 3.2 Description du circuit

L'algorithme de génération du test fait référence à une description du circuit compatible avec le modèle de fautes adopté. En technologie bipolaire, le modèle de collage simple permet une description du circuit au niveau de la porte logique. Dans le cas du CMOS, la compatibilité impose une description au niveau du transistor.

A ce niveau, la description de circuits complexes devient rapidement fastidieuse. Une représentation hiérarchique du circuit s'impose et rend plus aisée la conception d'algorithmes de génération. La hiérarchie adoptée est la suivante: le circuit complet est com-

Figure 1 Modèle de fautes en technologie CMOS

posé d'un ensemble de modules fonctionnels, chaque module est formé de portes logiques et chaque porte est constituée de transistors.

### 3.3 Génération du test complet d'un module

La génération du test complet d'un module se déroule selon une approche ascendante en trois étapes. La première étape consiste à générer un ensemble de test pour chaque porte du module. Cette génération se fait au niveau du transistor, en accord avec le modèle de fautes adopté. La seconde étape produit un ensemble de test du module sur la base des données issues de l'étape précédente. Finalement, il s'agit de définir les conditions de propagation de ces vecteurs à travers le circuit ainsi que les conditions d'observation des résultats du test, partant des points accessibles au testeur jusqu'au module sous test.

### 4. Portes logiques CMOS

La porte logique ou porte (gate en anglais) constitue l'élément de base de nombreux circuits logiques. Au niveau de la description logique du circuit, la porte est une «boîte noire» comportant N entrées et une sortie.

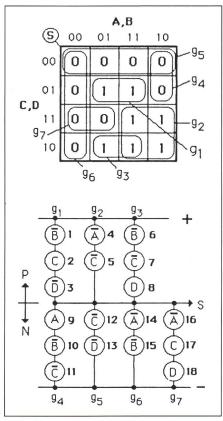

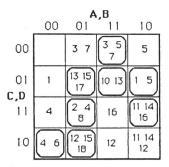

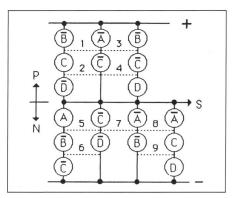

La structure interne d'une porte statique CMOS ainsi que la méthode générale de synthèse des blocs de conduction qui la constituent sont décrites dans l'encadré 2. La méthode de «syntèse séparée» est retenue comme véhicule d'explication dans le cadre de cet article. Elle présente l'avantage de conduire à des blocs de conduction Net P tous deux exprimés sous forme de «somme de produits» des variables d'entrée de la porte, c'est-à-dire par des réseaux parallèles de transistors en série [5]. La figure 2 est un exemple de porte synthétisée de cette manière, à partir de la table de Karnaugh. Le bloc de conduction P s'exprime par la somme de 3 produits g<sub>1</sub>, g<sub>2</sub> et g<sub>3</sub> des variables d'entrée et le bloc N par la somme de 4 produits  $g_4$ ,  $g_5$ ,  $g_6$  et  $g_7$ . Chaque produit  $g_i$  est matérialisé sous la forme d'un groupe de transistors en série, les transistors sont représentés par des cercles à l'intérieur desquels est écrit le nom de la variable commandant la grille. Chaque transistor est, de plus, repéré par un indice.

# 5. Test des portes logiques CMOS

En accord avec le modèle de fautes CMOS, le test d'une porte revient à vérifier le bon fonctionnement de cha-

Figure 2 Exemple de synthèse séparée d'une porte logique CMOS

$P = g_1 + g_2 + g_3 = \overline{B}C\overline{D} + \overline{A}\overline{C} + \overline{B}\overline{C}D$

$N = g_4 + g_5 + g_6 + g_7 = A \, \overline{B} \, \overline{C} + \, \overline{C} \, \overline{D} + \, \overline{A} \, \overline{B} + \, \overline{A} \, CD$

### E2 Synthèse des portes logiques CMOS

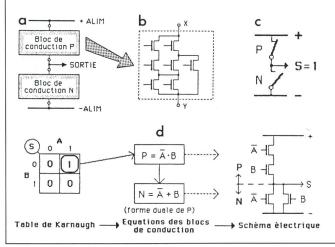

En technologie CMOS, une porte logique statique est constituée par la mise en série de deux *blocs de conduction* (fig. E2a). Chaque bloc de conduction est un réseau de transistors du même type, n ou p, dont les grilles constituent les entrées de la porte (fig. E2b). Vu par ses pôles X et Y, un bloc de conduction est assimilable à un interrupteur dont l'état ouvert ou fermé est fonction des valeurs d'entrée. La porte statique CMOS se modélise ainsi par deux interrupteurs en série dont les états de conduction sont complémentaires (fig. E2c).

Synthétiser une porte logique CMOS revient à définir la structure de chaque bloc de conduction à partir d'une représentation fonctionnelle (table de Karnaugh, équation logique, etc). Une des méthodes consiste à synthétiser un bloc de conduction (N ou P), le bloc opposé étant ensuite obtenu par transformation duale. La forme duale de deux transistors en série est leur mise en parallèle et réciproquement. Au niveau algébrique, la forme duale de l'opération booléenne «+» (OU) est l'opération «·» (ET).

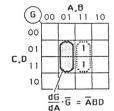

Dans l'exemple de la figure E2d, la porte est synthétisée à partir des 1 la fonction (représentée ici sur une table de Karnaugh), définissant le bloc de conduction P. L'équation  $P = p(A, B, C, D) = \overline{A} \cdot B$

de ce bloc est obtenue de manière directe à partir de la table, en inversant ensuite les variables (un transistor p conduit l'état 1 lorsque sa grille est à l'état 0). L'équation du bloc opposé,  $N = n(A, B, C, D) = \overline{A} + B$ , se déduit simplement de celle du bloc P par transformation duale. Finalement, le schéma électrique de la porte peut être dessiné à partir des deux équations. Il est bien entendu possible de synthétiser la même porte en partant des 0 de la fonction. Dans le cas général, la structure d'une porte synthétisée à partir des 1 est différente de celle obtenue en partant des 0

Par extension, il est possible de réaliser chacun des blocs d'une porte de manière indépendante, le bloc P à partir des 1 et le bloc N à partir des 0. Cette méthode de synthèse, dite séparée, conduit à un système de deux équations indépendantes de la forme «somme de produits des variables». Les blocs de conduction ainsi obtenus sont constitués par la mise en parallèle de groupes de transistors en série, appelés groupes sériels (fig. 2). Une telle topologie se prête bien à l'automatisation du dessin de plans de masques par le fait que les transistors peuvent être disposés sur un réseau régulier et compacte de lignes et de colonnes.

> Figure E2 Principe de la synthèse des portes logiques CMOS

- a Porte logique CMOS

- b Bloc de conduction

- c Principe de fonctionnement

- d Synthèse d'une porte logique CMOS par dual topologique

cun de ses transistors (détection des fautes s-on et s-off) et à s'assurer de l'absence de coupures ou de courts-circuits de conducteurs (détection des fautes s-open et s-short). Ces quatre classes de fautes nécessitent des approches distinctes à la génération des vecteurs de test.

#### 5.1 Test des transistors

### 5.1.1 Génération du test s-on

La détection d'une faute s-on consiste à placer la porte dans un état tel que le transistor sous test soit le seul à bloquer la branche dont il fait partie et que le bloc de conduction opposé soit dans un état conducteur. Si la faute est présente, les deux blocs seront simultanément conducteurs, donnant lieu à un court-circuit d'alimentation. La détection de ce courant anormal (de plusieurs ordres de grandeur supérieur au courant de fuite de la porte) mettra en évidence la présence de la faute. La définition suivante permet de rechercher les vecteurs de test s-on d'un transistor:

Définition 1: La condition pour

Figure 3 Vrais sommets de la branche  $g_1$

- a Table de Karnaugh

- b Table des vrais sommets de la branche g1

qu'un état d'entrée de la porte soit un vecteur détectant une faute s-on sur le transistor  $x_j$  d'une branche  $g_i$  est que cette entrée soit un vrai sommet de la branche  $g_i$  par rapport à  $x_j$  (voir encadré 3). Un vrai sommet, noté  $v_{ij}$ , est défini comme étant l'intersection de la dérivée booléenne de  $g_i$  par rapport à la variable  $x_j$  avec la fonction du bloc de conduction opposé à celui contenant  $g_i$ . La figure 3 représente, sur table de Karnaugh, les vrais sommets associés à la branche  $g_1$  du circuit de la figure 2.

A chaque transistor de la porte correspondra ainsi un ou plusieurs vrais sommets, vecteurs potentiels du test s-on. Le test complet de la porte sera généré en choisissant l'ensemble minimal de vrais sommets couvrant la détection de cette faute pour les transistors de la porte. La figure 4 illustre ce principe de génération, appliqué à la porte complète. Pour obtenir l'ensemble minimal de test s-on, une table des vrais sommets est tout d'abord construite en notant dans chaque case l'indice des transistors associés au vrai sommet qu'elle représente. Une fois cette table construite, l'extraction de l'ensemble minimal de test est réalisé par «élagage itératif». Cette méthode

Figure 4 Génération du test minimal s-on de la porte

8 vecteurs de test s-on (ABCD)

| $v_1$ | =(1100) | V 5 | =(01  | 11) |

|-------|---------|-----|-------|-----|

| V 2   | =(1001) | V 6 | =(10) | 11) |

$v_3 = (0101)$   $v_7 = (0010)$  $v_4 = (1101)$   $v_8 = (0110)$

### E3 Différence booléenne et vrai sommet

Soit une fonction booléenne  $G = g(x_1, x_2, ..., x_n)$  des n variables  $x_j$ . L'ensemble ordonné des variables est un vecteur à n composantes. On appelle différence  $booléenne^1$  de G par rapport à  $x_j$  une nouvelle fonction, notée  $\partial G/\partial x_j$ , telle que:

$$\frac{\partial G}{\partial x_i} = g(x_1, ..., x_{d-1}, 0, x_{j+1}, ... x_n) \oplus g(x_1, ..., x_{j-1}, 1, x_{j+1}, ... x_n)$$

On appelle vrai sommet (true vertex en anglais) d'une variable  $x_i$  de G, le produit

$$V_j = \begin{array}{c} \frac{\partial \, G}{\partial x j} \\ \end{array} \cdot \overline{G}$$

*Propriété*: Le vecteur correspondant à un vrai sommet de G par rapport à la variable  $x_i$  est à distance de Hamming<sup>2</sup> unitaire d'au moins un vecteur correspondant à G.

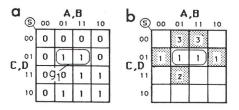

La figure illustre ces notions sur une table de Karnaugh (pour simplifier, seuls les 1 de la fonction sont représentés). Une fonction G de 3 variables A, B et D est donnée en (fig. E3a). La différence booléenne de G par rapport à la variable A est représentée en figure E3b par le groupe de 4 cases entourées. Les deux cases hors de G du groupe (en gris sur la fig. E3c) constituent chacune un vrai sommet de G par rapport à la variable G (ils sont adjacents à G par la variable G).

- <sup>1</sup> Une expliation est donnée dans [9]

- <sup>2</sup> La distance de Hamming entre deux vecteurs représente le nombre d'éléments de même rang par lesquels ils diffèrent.

### Figure E3 Exemple

- a Fonction G de 3 variables

- b Différence booléenne par rapport à A

- c Vrai sommet de la variable A

consiste, dans un premier temps, à marquer le vrai sommet couvrant un maximum de transistors (case entourée). Dans un deuxième temps, les transistors contenus dans cette case sont éliminés de toute la table. L'opération se répète jusqu'à ce que la table soit vide, les cases marquées représentent alors chacune un vecteur de l'ensemble minimal de test s-on. Dans l'exemple de la figure 4, l'ensemble minimal de test s-on de la porte est constitué de 8 vecteurs.

### 5.1.2 Génération du test s-off

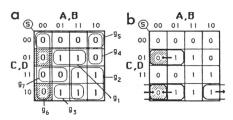

Détecter une faute s-off revient à placer la porte dans un état tel qu'une seule branche soit conductrice. Si l'un des transistors de cette branche est rendu non conducteur par la présence de la faute, la branche sera bloquée. Le nœud de sortie de la porte se trouvera alors dans un état «flottant» (ou haute impédance), conservant capacitivement la valeur de l'état de sortie précédent. Cet effet de mémoire transforme ainsi la porte purement combinatoire

en un circuit à comportement séquentiel [6; 7]. La détection de la faute s-off se fera donc en appliquant deux vecteurs successifs aux entrées de la porte: un premier vecteur (vecteur d'initialisation) initialise l'état de sortie de la porte, un second vecteur (vecteur de manifestation) provoque le changement de l'état de sortie à travers la branche sous test. L'existence de la faute se manifeste par l'absence de ce changement d'état lors de l'application du second vecteur. La génération du test s-on de la porte consiste donc à rechercher l'ensemble minimal de paires (ou doublets) de vecteurs testant la totalité des branches de la porte. Deux définitions permettent de déterminer les doublets de test d'une branche:

Définition 2: La condition pour qu'un état d'entrée de la porte soit un vecteur de manifestation de la faute s-off d'une branche  $g_i$  est que cet état corresponde à une case de la table de Karnaugh couverte uniquement par cette branche.

Définition 3: La condition pour qu'un état d'entrée de la porte soit vecteur d'initialisation d'un vecteur de manifestation donné est que cet état corresponde à une case adjacente à celle du vecteur de manifestation et que cette case soit couverte par une branche au moins du bloc de conduction opposé à celui de la branche sous test

Figure 5 Vecteurs de manifestation et doublets de test s-off de g<sub>6</sub>

- a Deux vecteurs de manifestation

- b Trois doublets de test s-off de la branche g6

La figure 5 illustre la recherche des doublets de test de la branche  $g_6$  de l'exemple, en utilisant les définitions 2 et 3. Sur la table de gauche, les deux vecteurs de manifestation possibles de cette branche sont représentés par les cases hachurées. La table de droite montre les trois doublets de test s-off construits à partir de la définition 3. Ils sont représentés par les couples de cases entourés; une notation plus commode consiste à relier les couples de cases au moyen d'une flèche orientée dans le sens de l'application séquentielle des deux vecteurs.

En appliquant ces deux opérations à l'ensemble des branches de la porte, la table de tous les doublets de test possibles est construite (fig. 6a). Finale-

Figure 6 Génération du test minimal s-off de la porte

10 vecteurs de test s-off:

- =(1010)V 6 =(1101)=(1100)=(0010)V 2 V7 =(0110) $v_8 = (1101)$ V 3 V4 =(0111) $v_9 = (1001)$ =(0101) $v_{10} = (1011)$ V 5

- a Table des transitions

- b Chemin de test choisi

ment, la génération de l'ensemble minimal de test s-off de la porte consiste à chercher un chemin minimal, orienté par les flèches, et couvrant la totalité des branches de la porte. Toutes les cases du chemin constitueront l'ensemble de test. La table de la figure 6b représente un chemin minimal possible conduisant à un ensemble de 10 vecteurs pour le test s-off de la porte.

Afin de minimaliser la taille du test complet des transistors de la porte (s-on et s-off), une contrainte supplémentaire doit être introduite dans la recherche du chemin de test s-off: le chemin doit inclure le maximum de vecteurs du test s-on. Dans l'exemple de la figure 6, le test s-on est totalement inclu dans le chemin de test s-off, les transistors de cette porte seront testables au moyen de 10 vecteurs.

#### 5.2 Test des connexions

Les connexions reliant les transistors d'une porte logique sont réalisées au moyen de zones conductrices diffusées ou déposées sur le silicium (silicium polycristallin et métal). Le test des connexions consiste à détecter la présence de fautes s-open ou s-short sur ces conducteurs.

### 5.2.1 Détection des fautes s-open

Deux types de connexions sont à considérer dans le cas de cette faute: les connexions de grilles des transistors (entrées de la porte) et les branches (connexions de drains et sources des transistors). Dans le premier type, la faute s-open isole un ensemble de grilles des entrées de la porte. Ces grilles, dites flottantes, ont un état électrique quasi constant (à l'échelle de la durée du test) et indéterminé. Les transistors dont la grille est flottante peuvent ainsi être considérés comme toujours conducteurs ou toujours bloqués. La faute s-open se ramène ainsi à

une faute s-on ou s-off et est détectée lors du test des transistors. Dans le second type de connexions, la faute s-open coupe le conducteur reliant deux transistors d'une branche. L'effet est analogue à celui d'une faute s-off apparaissant dans cette branche. Le test des fautes s-open d'une porte est ainsi totalement inclu dans le test de ses transistors et ne nécessite aucun vecteur supplémentaire.

### 5.2.2 Génération du test s-short

Détecter la faute s-short revient à placer les deux conducteurs en court-circuit à des états logiques opposés. En présence de la faute, un courant de court-circuit détectable apparaîtra dans l'alimentation de manière analogue au cas du test s-on des transistors. Les fautes s-short peuvent être classées en trois catégories: entre grilles, entre grilles et nœuds et entre nœuds. On appelle nœud tout point électriquement indépendant du réseau de transistors constituant la porte (voir encadré 2).

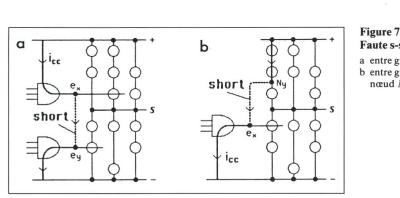

Dans la première catégorie, la faute s-short entre deux grilles correspond à un court-circuit entre deux entrées de la porte (fig. 7a). Générer le test de cette faute revient à trouver un ensemble minimum de vecteurs, tel que toutes les entrées de la porte, prises deux à deux, se trouvent une fois au moins dans un état logique opposé. La présence de la faute se minfestera par un courant de court-circuit dans l'alimentation des portes commandant les entrées de la porte sous test.

Dans la seconde catégorie, la faute crée un chemin conducteur entre une grille et un nœud de la porte (fig. 7b). Le test de toutes les fautes de cette catégorie est simplement composé des deux vecteurs

$$V_{\rm P} = 0 = (0\ 0\ 0\ ...\ 0)$$

et  $V_{\rm N} = 1 = (1\ 1\ 1\ ...\ 1)$ . Le vecteur  $V_{\rm P}$  pla-

Faute s-short a entre grilles  $e_x$  et  $e_y$ b entre grille  $e_x$  et nœud  $N_y$

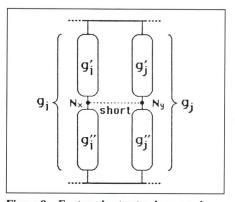

Figure 8 Faute s-short entre deux nœuds

Condition de détection de la faute s-short:

- $g'_{i}$  et  $g''_{j}$  conducteurs

- $-g_i''$  et  $g_i'$  bloqués

- conduction du bloc opposé à celui contenant

g<sub>i</sub> et g<sub>i</sub>

ce toutes les grilles de la porte à l'état 0, rendant conducteurs tous les transistors du bloc P. Ainsi, une faute s-short entre une grille et un nœud du bloc P produira un courant de court-circuit d'alimentation détectable. De manière analogue, le vecteur  $V_N$  rend conducteurs tous les transistors du bloc N, une faute entre une grille et un nœud de ce bloc produira également un courant de court-circuit.

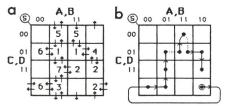

Contrairement à ces deux premières catégories de fautes dont les conditions de détection sont indépendantes de la topologie (diposition géométrique des transistors et des connexions), la génération du test s-short de la troisième catégorie est fortement liée à la topologie de la porte. La figure 8 représente une telle faute située entre les nœuds  $N_x$  et  $N_y$  de deux branches  $g_i$  et  $g_j$  d'un bloc de conduction.

Chacun de ces nœuds divise la branche dont il fait partie en deux sous-branches. La génération du test de la faute repose sur la définition suivante:

Définition 4: La condition pour qu'un état d'entrée de la porte soit un vecteur détectant la faute s-short entre deux nœuds d'un bloc de conduction, est qu'il crée des états logiques opposés sur ces deux nœuds.

Cette condition est réalisée lorsque deux sous-branches diagonalement opposées sont conductrices, les deux autres sous-branches étant bloquées et le bloc de conduction opposé rendu conducteur. Si la topologie de la porte n'est pas connue, la définition 4 doit être appliquée à toutes les paires de nœuds de la porte afin de générer le test complet. L'information topolo-

Figure 9 Sites des fautes s-short entre nœuds et test de détection

6 vecteurs de test s-short:

- = (0111) teste 1, 4

- $v_2 = (1100)$  teste 2

- = (1001) teste 3

- $v_4 = (0101)$  teste 5

- $v_5 = (1011)$  teste 6

- $v_6 = (0110)$  teste 7, 9

faute 8 indétectable

| FAUTE                                                | GENERATION DU TEST                                                                                       |                           |                                                                                                |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------|--|

|                                                      | Base de l'algorithme                                                                                     | Dépendance<br>topologique | Détection de la faute                                                                          |  |

| s-on                                                 | Vrais sommets couvrant tous<br>les transistors de la porte.                                              | NON                       | Courant de court-circuit<br>dans l'alimentation de la<br>porte sous test.                      |  |

| s-off                                                | Doublets initialisation-mani-<br>festation de chaque groupe<br>sériel de la porte.                       | NON                       | Erreur en sortie de la porte<br>sous test.                                                     |  |

| s-open<br>- grille<br>- branche                      | Inclu dans s-on/s-off.<br>Inclu dans s-off.                                                              | NON<br>NON                | Idem que pour s-on/s-off<br>Idem que pour s-off.                                               |  |

| s-short - grille-grille - grille-noeud - noeud-noeud | Entrées complémentaires<br>deux à deux.<br>Deux vecteurs: (00) et (11)<br>Excitation des sites de faute. | evt.<br>NON<br>OUI        | Courant de c-c dans alim<br>des portes en amont.<br>Idem que pour s-on.<br>Idem que pour s-on. |  |

Tableau II Résumé des caractéristiques de la méthode de génération du test complet des portes CMOS

gique de la porte permet de réduire considérablement la taille du test, en supposant que seuls deux nœuds adjacents puissent être en court-circuit. La figure 9 représente les sites potentiels de la faute s-short dans une porte de topologie connue. Dans cet exemple, on dénombre 9 sites de fautes; dans le cas d'une topologie arbitraire, le nombre de sites potentiels de fautes s'élèverait à 67.

La génération du test complet de cette faute commence par l'établissement de la liste des sites de fautes. L'application de la définition 4 à chaque site de la liste produit un ensemble de vecteurs de test, ensemble généralement fortement redondant. L'ensemble minimal de test est finalement obtenu par élagage en ne conservant que les vecteurs couvrant chacun un maximum de fautes.

### 6. Conclusions

Le test complet de la porte, couvrant la totalité des fautes du modèle, résulte du groupement des tests spécifiques à chaque faute. Le tableau I représente le test complet de la porte prise en exemple, composé d'une séquence de 12 vecteurs.

La méthode de génération du test CMOS des portes logiques présentée dans cet article répond aux exigeances spécifiques imposées par cette technologie. Le tableau II résume des caractéristiques principales. Cette méthode se distingue des techniques connues [3: 4: 6; 7] par la simplicité des algorithmes qu'elle met en œuvre, tout en assurant un fort taux de couverture au test généré. Son application manuelle (sur table de Karnaugh), dans le cas de portes

simples, est aisée. L'implantation des algorithmes sous forme d'un logiciel d'ordinateur permet la création d'un outil efficace de génération automatique du test complet des portes logiques CMOS.

**Bibliographie**

- [1] Y.M. El-ziq: Classifying, testing and eliminating VLSI MOS failures. VLSI Design 4(1983)9, p. 30...35.

- [2] A.K. Susskind: Diagnostic for logic networks. IEEE Spectrum 9(1973)10, p. 40...47.

- [3] Y.K. Malaiya and S.Y.H. Su: A new fault model and testing technique for CMOS devi-ces. IEEE International Test Conference 1982, p. 25...34.

- [4] K.-W. Chiang and Z.G. Vranesic: On fault detection in CMOS logic networks. 20th ACM/IEEE Design Automation Conference, June 27...29, 1983, Miami Beach/Florida. Proceedings, p. 50...56.

- C. Piguet a.o.: A metal-oriented layout structure for CMOS logic. IEEE-Journal of Solid-State Circuits 19(1984)3, p. 425...436.

- [6] R. Chandramouli: On testing stuck-open faults. 13th Annual International Symposium in Fault Tolerant Computing (FTCS). June 28...30, Milano/Italy, Digest of papers, p. 258...265...

- [7] J.A. Abrahm: Testable CMOS logic circuits under dynamic behavior. Urbana, University of Illinois, Computer Systems Group, 1983.

- [8] J.F. Perotto: Test des circuits logiques combinatoires. Partie 2: Test structurel des circuits CMOS. Rapport technique CSEM No. 49. Neuchâchtel, Centre Suisse d'Electronique et de Microtechnique, 1986.

- [9] M. Jacomet and A. Reber: Testbarer Schaltungsentwurf eine Übersicht. Bull. tungsentwurf – eine Übersic SEV/VSE 78(1987)11, S. 623...631.

| Test complet de la porte |        |                         |        |  |  |  |  |

|--------------------------|--------|-------------------------|--------|--|--|--|--|

| vecteur                  | fautes | vecteur                 | fautes |  |  |  |  |

| Y <sub>1</sub> = (0000)  | а      | Y <sub>7</sub> = (1101) | c,d    |  |  |  |  |

| $Y_2 = (1010)$           | b      | $Y_8 = (1100)$          | b,c,d  |  |  |  |  |

| $Y_3 = (0010)$           | c,d    | $V_9 = (1101)$          | c,d    |  |  |  |  |

| Y <sub>4</sub> = (0110)  | b,c,d  | $Y_{10} = (1001)$       | b,c,d  |  |  |  |  |

| Y <sub>5</sub> = (0111)  | b,c,d  | $Y_{11} = (1011)$       | b,c,d  |  |  |  |  |

| $Y_6 = (0101)$           | b,c,d  | $V_{12} = (1111)$       | а      |  |  |  |  |

### Tableau I Séquence de test complet de la porte

- a fautes s-short entre grille et nœud

- b fautes s-short entre nœuds c fautes s-on

- d fautes s-off