**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

Herausgeber: Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 78 (1987)

Heft: 11

Artikel: Electronic Packaging

Autor: Stein, E.

**DOI:** https://doi.org/10.5169/seals-903872

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 30.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Electronic Packaging

E. Stein

Der Verfasser unternimmt den Versuch, das Gebiet des Electronic Packaging (EP) abzugrenzen. Nach einem Rückblick auf die bisherige Entwicklung werden der derzeitige Stand und künftige Problemfelder des EP skizziert. Ein weiterer Abschnitt ist den physikalischen und technischen Fragestellungen um Packungsdichte, Kühlung und Verbindungstechnik gewidmet. Es wird gezeigt, dass nur eine integrale Behandlung dieser Problemkreise zu optimalen Lösungen führt. Damit aber wird das Electronic Packaging zum eigenständigen Fachgebiet.

L'auteur tente de délimiter le domaine de la technologie d'assemblage électronique. Après un rappel de l'évolution précédente, l'état actuel et les futurs problèmes dans ce domaine sont esquissés. Il traite ensuite des questions d'ordre physique et technique de la densité d'emballage, du refroidissement et des connexions. Il montre que seul un traitement intégral de ces problèmes conduit à des solutions optimales. L'emballage électronique devient aussi un domaine particulier.

Erweiterte Fassung eines Vortrages an der ITG-Diskussionssitzung Electronic Packaging vom 6./7. März 1986 in Stein am Rhein.

#### Adresse des Autors

Erich Stein, dipl. Ing., Contraves AG, Schaffhauserstrasse 580, 8052 Zürich.

#### 1. Einführung

Electronic Packaging, nachfolgend mit EP abgekürzt, ist heute ein interdisziplinäres Fachgebiet, das sich mit dem Schutz von elektronischen Bauelementen gegen schädigende innere und äussere Einflüsse sowie mit dem Zusammenbau von elektronischen Bauelementen zu Baugruppen und weiter zu elektronischen Systemen befasst. Dabei werden elektrische, mechanische und thermische Eigenschafgleichermassen berücksichtigt. Wichtige Aspekte sind Kosten, Qualität und Zuverlässigkeit. Je nach Anwendungsgebiet stehen beim EP verschiedene Forderungen im Vordergrund: Packungsdichte, Leistungsfähigkeit, Kosten, Zuverlässigkeit usw.

Der vorliegende Beitrag soll die aktuelle Situation des EP beleuchten und Anstösse zu einer systematischen Bearbeitung und Förderung dieses Gebietes liefern. Dabei wird EP als Teilgebiet der Elektroniktechnologie verstanden. Weitere, wichtige Teilgebiete der Elektroniktechnologie sind die Mikroelektronik, das Computer-Aided Engineering (CAE) und die Technologien passiver und elektromechanischer Bauelemente.

Ein deutschsprachiger Begriff für EP ist nicht leicht zu finden. Am nächsten käme «Aufbautechnik elektronischer Geräte und Systeme». Im weiteren behalten wir aber den englischen Begriff bei, da er sich schon weitgehend eingebürgert hat. EP deckt verschiedene Teilgebiete vollständig ab: Das Production Engineering umfasst nur die fertigungsspezifischen Aspekte des Electronic Packaging, also Fertigungs- und Montagetechnik. Der Begriff Verbindungstechnik bezieht sich nur auf die funktionellen, elektrischen Eigenschaften von Verbindungen, vernachlässigt aber thermische und mechanische Eigenschaften. Die vor allem aus dem Maschinenbau bekannte konstruktive Gestaltung wiederum berücksichtigt fertigungstechnische

Eigenschaften hinreichend, funktionelle und elektrische dagegen ungenügend.

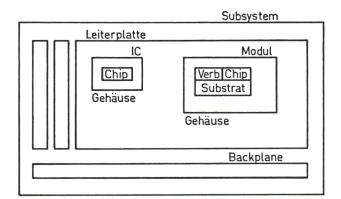

Mit einem leicht einschränkenden Blick auf die digitale Systemtechnik kann man die Hauptfunktionen des EP, wie in Tabelle I angegeben, formulieren. Diese Funktionen werden auf verschiedenen Ebenen erfüllt. Die Figur 1 zeigt einen typischen, hierarchischen Aufbau mit mehreren Packaging-Ebenen.

Beim heutigen Wissensstand liesse sich EP folgendermassen definieren: «EP ist ein Fachgebiet, das sich zum Ziele setzt, methodisch die Fragen, die sich aus dem Aufbau elektrischer und elektronischer Systeme für Funktion und Zuverlässigkeit ergeben, zu stu-

| Ebene       | Funktion                                                                           |  |

|-------------|------------------------------------------------------------------------------------|--|

| Elektrisch: | Signale und Energie zu-<br>und abführen                                            |  |

|             | Signale mit grosser<br>Bandbreite und kleiner<br>Laufzeit transportieren           |  |

|             | Betriebsenergie zuführen                                                           |  |

|             | Elektrische Energie<br>verlustarm transportieren                                   |  |

|             | Unerwünschte<br>Beeinflussungen verhindern                                         |  |

| Mechanisch  | : System gegen die Umwelt abschliessen und schützen                                |  |

| (2)         | Bauelemente und<br>Unterbaugruppen befestigen                                      |  |

|             | Austauschbarkeit von<br>Unterbaugruppen<br>gewährleisten                           |  |

|             | Bedienungselemente zugänglich machen                                               |  |

| Thermisch:  | Kühlung gewährleisten<br>Aufgabengerechte<br>Temperaturverteilung<br>sicherstellen |  |

Tabelle I Funktionen des Electronic Packaging

Figur 1 Packaging-Ebenen

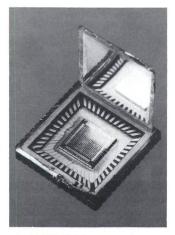

Figur 3 Kurzwellen-Senderöhre

dieren und daraus Regeln und Verfahren für die praktische Anwendung zu erarbeiten.»

### 2. Historische Entwicklung

Bis in die fünfziger Jahre wurden die elektronischen Bauelemente fast ausschliesslich mit einzelnen Drähten verbunden [1]. Anfänglich wurden die Verbindungsstellen geschraubt, später verlötet. Die gedruckte Schaltung, die 1942 erstmals realisiert wurde, brachte grosse Fortschritte durch die Batch-Herstellung von Verbindungen. Die dreidimensionale «fliegende» Verdrahtung wurde ersetzt durch planare Verbindungen, die alle in einer Ebene lagen. Später wurden, bedingt durch die wachsende Komplexität, weitere Leiterbahnebenen hinzugenommen. So entstand zunächst die zweiseitige Leiterplatte, später dann der Multilayer-Print. Die Anzahl der Leiterbahnebenen wuchs stetig. Der Trend zu dreidimensional geschichteten, integrierten Strukturen verstärkte sich noch durch den Einsatz von planaren Widerständen und Kondensatoren in Schichttechnologien, von Masseebenen und Stripline-Netzwerken. In den

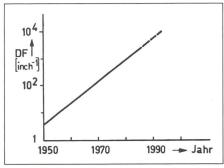

Figur 2 Verbindungsdichte als Funktion der Zeit

DF Density Factor

letzten Jahren ist auch eine zunehmende Realisierung von Verbindungsfunktionen in Bauelementen, z.B. in Hybrid- und LSI-Schaltungen, festzustellen.

Die Verbindungsdichte ist mit der Zeit exponentiell gewachsen.

Wenn LRS die Anzahl der Leiterbahnebenen, GRD der minimale Abstand zwischen zwei benachbarten Kontaktierungspunkten (in Zoll) und LPC die grösste Zahl der Leiterbahnen ist, die zwischen derartige Kontaktierungspunktpaare gelegt werden kann, dann ist die Verbindungsdichte (Density Factor) DF nach [2] definiert als

$$DF = \frac{LRS \cdot (1 + LPC)}{GRD} \text{ [inch-1]}$$

DF ist in Figur 2 als Funktion der Zeit dargestellt. Ähnliche Kurven sind auch aus der IC-Technologie bekannt, wo sie die Zunahme der Komplexität integrierter Schaltungen beschreiben.

Ein interessantes Studienobjekt des EP ist die Kurzwellen-Senderöhre in Figur 3. Im Gegensatz zu Standard-Leiterplatten ist hier die mechanische Struktur durch die Funktion bedingt. Man beherrscht hohe elektrische Spannungen durch geeignete Werkstoffe und konstruktive Massnahmen. Die hohe Verlustleistung wird dank integraler Kühlung zulässig, während man grosse Temperaturdifferenzen und Temperaturzyklen durch konstruktive Massnahmen im Griff hat. Das Element ist dank einer integralen Steckverbindung anwendungsfreundlich, und klimatische Einflüsse werden durch den hermetisch dichten Glaskolben verhindert. Damit kann man sagen, dass Funktion und Packaging eine Einheit bilden, also untrennbar miteinander verbunden sind. Man kann vermuten, dass Packaging-Konzepte, die sich langfristig durchsetzen werden, dieselbe Forderung erfüllen müssen.

# 3. Heutiger Stand

Der Stand der heute etablierten Packaging-Technologie [3] kann mit wenigen Worten umschrieben werden: Als Substrate werden Leiterplatten verwendet, die häufig als Multilayer ausgeführt sind. Die Bauelemente - vorwiegend ICs - haben Stiftanschlüsse, die durch die Leiterplatte gesteckt und mittels Wellenlöten mit den Leiterbahnen verbunden werden. Als Gehäuseform für ICs wird fast ausschliesslich das Dual-in-line-Gehäuse (DIL) verwendet (Fig. 4). Der konstruktive Aufbau von elektronischen Subsystemen aus Leiterplatten, Baugruppen, Baugruppenträgern und Gestellen sowie den zugehörigen Steckverbindungen ist weitgehend normiert, z.B. nach DIN 41494 und DIN 41612 (dies gilt zumindest für die professionelle Elektronik). Für die Kühlung wird praktisch nur Konvektionskühlung, allenfalls zusammen mit einem erzwungenen Luftkreislauf, verwendet.

Diese Form des Electronic Packaging hat sich gut bewährt, und es existiert ein ausgebauter Markt für alle dazu notwendigen Produkte. Der Leiterplattenmarkt allein wird im Jahr 1986 weltweit auf 11 Mia \$ geschätzt.

Figur 4 LSI-IC im DIL-Keramikgehäuse Das Gehäuse ist 62 mm lang bei einer Chip-Kantenlänge von 5 mm.

#### 4. Aktuelle Tendenzen

Trotz dieser günstigen Situation sind in den letzten Jahren zunehmend Wünsche für ein weiterentwickeltes EP aufgekommen, die teilweise aus der Forderung nach kleineren, billigeren Geräten in der Unterhaltungselektronik folgen und teilweise aus stetig wachsenden Forderungen an Komplexität und Leistungsfähigkeit von Systemen, die auf Digitalrechnern basieren. Die zurzeit weitaus wichtigste Technologie, die eine Erfüllung solcher Forderungen erwarten lässt, ist mit dem Begriff Surface Mounting Technology (SMT) oder Oberflächenmontage (OM) umschrieben [4; 5]. Man erwartet, dass in den frühen neunziger Jahren die Hälfte aller Neuentwicklungen SMT verwenden werden. In der Unterhaltungselektronik hat sich - insbesondere in Japan die SMT heute schon weitgehend durchgesetzt.

Der Grundgedanke der SMT wird bei der Betrachtung von Figur 4 deutlich (wir beschränken uns hier auf hermetisch dichte Keramikgehäuse). Man sieht, dass das Gehäuse viel grösser ist als das Chip. Das heisst, der flächenmässig grösste Teil hat keine «logische» Funktion, sondern dient nur dazu, die Verbindung vom Bondpad zur Lötstelle zu ermöglichen. Es liegt nahe, diesen Teil einfach wegzulassen. Dadurch erhält man den Leadless Chip Carrier (LCC, Fig. 5).

Der LCC ist kleiner, und die parasitären Elemente (R, C, L) sind daher ebenfalls kleiner. Die fehlenden Pins zwingen zur Oberflächenmontage. Es sind nun keine Bohrungen mehr zum Durchstecken von Stiften notwendig,

Figur 5 LCC-Gehäuse

Die Kantenlänge des Gehäuses beträgt 14 mm, die des Chips 5 mm.

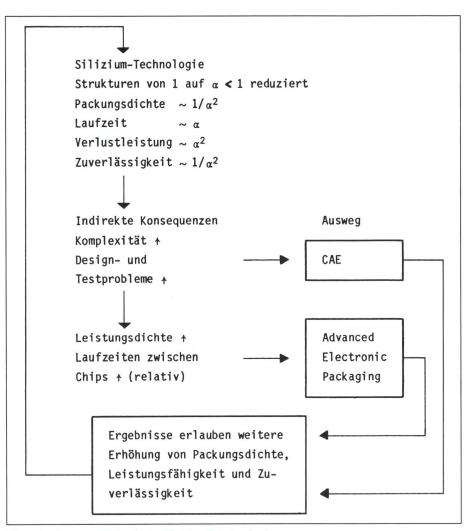

Figur 6 Synergieeffekte in der Elektroniktechnologie α Linienbreite, bezogen auf eine frei gewählte Standardlinienbreite

was Platz und Arbeit spart. Diese Vorteile erkauft man sich durch eine ganze Reihe von Nachteilen. Die kleineren Abstände zwischen den Lötstellen führen leichter zur Brückenbildung beim Löten. Da der Keramik-LCC und das übliche Leiterplattensubstrat verschiedene Ausdehnungskoeffizienten aufweisen, resultieren mechanische Spannungen. Die Handhabung der Bauelemente ist schwieriger und erfordert höhere Präzision. Auch Test und Reparatur der Baugruppen sind erschwert.

Weltweit arbeiten unzählige Köpfe an der Lösung dieser Probleme. Für einzelne Teilprobleme bestehen schon verschiedene Lösungsvorschläge, die jedoch nur schwer auf ihre Brauchbarkeit überprüft werden können. Diese haben aber zu einer Inflation neuer Gehäuseformen geführt [6] mit der Konsequenz, dass die Verfügbarkeit vieler Bauformen relativ schlecht ist und die Einführung der SMT massiv behindert wurde. Trotzdem wird die

SMT in den nächsten Jahren an Bedeutung stark zunehmen.

Obwohl die SMT zurzeit im Vordergrund des Interesses steht, ist damit das Thema EP nicht erschöpft. Vielmehr gibt es eine Reihe grundsätzlicher Fragestellungen, die in Zukunft vermehrt zu beachten sind.

# 5. Grundsätzliche Fragestellungen

Bei EP sind die grundsätzlichen Zusammenhänge zwischen Leistungsfähigkeit, Zuverlässigkeit und Packungsdichte zu beachten. Aus Konkurrenzgründen wird von elektronischen Systemen eine immer grössere Leistungsfähigkeit gefordert, ohne dass dadurch die Zuverlässigkeit abnehmen darf. Zur Erhöhung der Leistungsfähigkeit muss die Packungsdichte vergrössert werden, damit parasitäre Kapazitäten und Signallaufzeiten kleiner werden. Dadurch wird jedoch die Verlustleistungsdichte und als Folge davon die Temperatur erhöht. Durch entsprechende Kühlung muss verhindert werden, dass die Zuverlässigkeit sinkt. Damit sind Packungsdichte und Kühlung als zwei wesentliche Kriterien für EP erkannt.

Es soll hier darauf hingewiesen werden, dass das EP mit anderen Teilgebieten der Elektroniktechnologie in enger Wechselwirkung steht (Fig. 6). Die treibende Kraft ist heute - wie seit einigen Jahren - die Skalierung der Strukturgrössen bei den ICs [7]. Da der Faktor  $\alpha^1$  sich jeweils innerhalb von zwei bis drei Jahren halbiert, erreicht man signifikante Fortschritte bei Chipkomplexität, Gatterlaufzeit, Gatterverlustleistung und Zuverlässigkeit. Die Konsequenzen der verschärften Design- und Testprobleme versucht man mit dem Computer-Aided Engineering (CAE, [8]) zu beherrschen. Für die Probleme erhöhter Leistungsdichte und Leitungslaufzeiten muss das EP Lösungen anbieten.

Erst wenn man alle Technologien synergetisch zusammenfasst, kann man die Entwicklung der Elektronik mitgestalten. In Tabelle II sind die grundsätzlichen Forderungen an ein ideales Packaging-System zusammengestellt. Aus diesen primären Forderungen lassen sich viele sekundäre Forderungen ableiten, die sich jedoch teilweise widersprechen.

Beispielsweise kann die Forderung «leicht» durch die Auswahl von Werkstoffen mit kleinem spezifischen Gewicht und durch eine geeignete Leichtbauweise erfüllt werden. Wahrscheinlich ist dann aber die Forderung «ge-

$^{1}$   $\alpha$  bezeichnet die zu irgendeinem Zeitpunkt erreichte Linienbreite bezogen auf die Linienbreite zu einem bestimmten früheren Zeitpunkt.

- 1 Sicherstellung der nötigen Systemleistung

- 2 Hohe Zuverlässigkeit

- 3 Klein und leicht

- 4 Geringe Herstellungskosten

- 5 Geringe Entwicklungskosten

- 6 Leicht reparierbar

- 7 Wartungsfrei

- 8 Umweltgerecht

Tabelle II Anforderungen an ein ideales Packaging-System

| Anwendungsbestimmte Strategie              | Technologiebestimmte Strategie                              |  |

|--------------------------------------------|-------------------------------------------------------------|--|

| Anforderungen aus der Anwendung vorgegeben | Aufbautechnik vorgegeben                                    |  |

| Aufbautechnik variabel                     |                                                             |  |

| Entwicklungskosten höher                   | Entwicklungskosten niedriger                                |  |

| Herstellungskosten* oft niedriger          |                                                             |  |

| Erfüllung spezieller Forderungen möglich   | Erfüllung spezieller Forderungen<br>schwierig bis unmöglich |  |

<sup>\*</sup> Bei grösseren Stückzahlen

Tabelle III Strategien für Electronic Packaging

ringe Herstellungskosten» nicht mehr hinreichend erfüllt. Daraus folgt, dass es kein optimales Packaging-Konzept geben kann, sondern dass aus einem Spektrum von Konzepten das für den jeweiligen Anwendungsfall beste ausgewählt und eventuell noch modifiziert werden muss.

Aufgrund der Breite dieses Spektrums kann man zwei Strategien für das EP definieren: anwendungsbestimmt und technologiebestimmt (Tab. III). Unter anwendungsbestimmt verstehen wir, dass die von der jeweiligen Anwendung gestellten Anforderungen zur Entwicklung eines darauf zugeschnittenen Packaging-Konzeptes führt. Technologiebestimmt soll heissen, dass das Packaging-Konzept vorgegeben ist und jede Awendung mit den dadurch gegebenen Randbedingungen zurechtkommen muss.

Die anwendungsbestimmte Strategie bedeutet Spezialisierung und damit Vielfalt. Dafür ist jedoch eine weitgehende Optimierung möglich. Das Risiko liegt darin, dass eine gewählte Technologievariante sich nicht durchsetzen kann. Die heutige Situation bei der SMT dürfte im wesentlichen durch den Begriff «anwendungsbestimmt» charakterisiert sein.

Die technologiebestimmte Strategie hingegen führt zu Standardisierung und Normierung. Die Technologie ist vorgegeben und das Produkt ist so zu gestalten, dass es mit ihr realisiert werden kann, womit natürlich Flexibilität verlorengeht. Nachdem sich eine solche Technologie durch «Diffusion» [9] verbreitet hat, kann sie praktisch überall produziert werden. Dies führt zur «Economy of Scale», das heisst infol-

ge grosser akkumulierter Stückzahlen kann kostengünstig produziert werden. Hingegen wird eine standardisierte Technologie für viele Anbieter keine strategische Erfolgsposition [10] darstellen.

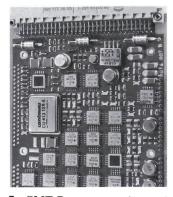

Die Figur 7 zeigt als Beispiel eine SMT-Baugruppe mit gemischter Bestückung. Aus zwingenden Gründen war eine hohe Packungsdichte erforderlich, die durch SMT erreicht werden konnte. Die nicht in SMT-Gehäusen erhältlichen Bauelemente werden mittels konventioneller Durchsteckmontage eingebaut. Das Problem der verschiedenen Ausdehnungskoeffizienten wird stark vereinfacht, indem nur 20polige Chipcarrier verwendet werden.

Die Spannweite, die mit verschiedenen Packaging-Konzepten überdeckt werden kann, geht aus einem Workshop hervor, über den von *Balde* [11] berichtet wurde. Fünf verschiedene Designs derselben hypothetischen

Figur 7 SMT-Baugruppe mit gemischter Bestückung

Figur 8

Rentsche Regel

PGA Pin-Grid-Array

Rechner wurden miteinander verglichen. Die benötigte Leiterplattenzahl lag zwischen 1 und 40, die erreichbare Taktperiode streute von 16 ns bis 44 ns und die geschätzten Herstellungskosten von \$ 4000 bis \$ 21 000.

#### 5.1 Verbindungen

Eine der wichtigsten Funktionen des Electronic Packaging ist die Bereitstellung elektrischer Verbindungen. Verbindungen sind unter quantitativen und qualitativen Aspekten zu betrachten. Der quantitative Aspekt bezieht sich auf die Frage, wieviele Verbindungen auf welcher Packaging-Ebene notwendig sind und welcher Natur (Signal- oder Speisungsverbindungen, feste oder lösbare Verbindungen) sie sein sollen. Der qualitative Aspekt erfasst Eigenschaften und Effekte wie Laufzeiten, Reflexionen, Übersprechen.

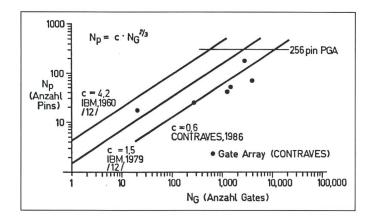

Für die Ermittlung der notwendigen Anzahl von Verbindungen gibt die Rentsche Regel einen Anhaltspunkt [12]. Die Figur 8 zeigt einige Kurven sowie Daten von realisierten Gate Arrays. Die rein empirisch begründete Rentsche Regel gilt für busorientierte Systeme nicht mehr streng, wenn auch der Zusammenhang zwischen steigender Verbindungszahl bei steigender Komplexität erhalten bleibt.

Das Problem der Masseverbindungen wird in diesem Zusammenhang immer wichtiger. Während man sich bei Leiterplatten mit Masseebenen behelfen kann, ist es bei Verbindungen zwischen Packaging-Ebenen (z.B. vom IC zur Leiterplatte oder von der Leiterplatte zur Backplane) notwendig, eine Anzahl Masse-Pins vorzusehen. So wird für Leiterplatten-Steckverbindungen empfohlen, je nach Logikfa-

milie 10 bis 20% der Pins als Masse-Pins zu verwenden [13].

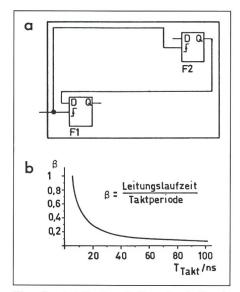

Nun zu den qualitativen Aspekten. Anhand eines einfachen Modells kann man den Einfluss von Leitungslaufzeiten auf die minimale Taktperiode einer Digitalschaltung veranschaulichen (Fig. 9). Die beiden Flipflops werden mit demselben Takt getaktet, und der Ausgang von F2 geht auf den Eingang von F1 zurück (Fig. 9a). In einer einfachsten Näherung berücksichtigt man nur die Laufzeiten der Leitungen und der ICs. Für eine Leiterplatte im Doppeleuropaformat einer realistischen Signalgeschwindigkeit von 14 cm/ns ist das Verhältnis von (konstanter) Leitungslaufzeit zu Zykluszeit in Funktion der Zykluszeit (Fig. 9b) aufgezeichnet. Daraus ist die Bedeutung hoher Signalgeschwindigkeiten und kleiner

Figur 9 Anteil der Leitungslaufzeit als Funktion der Taktperiode

- a Modellfiguration

- b  $\beta$  als Funktion der Taktperiode

Leitungslängen ersichtlich. Weitere Probleme sind Störungen über Speiseleitungen [14] und die richtige Dimensionierung des Wellenwiderstandes von Signalleitungen [15].

#### 5.2 Kühlung

Die Bedeutung der Kühlung für das Electronic Packaging geht schon aus der Vielzahl der dazu publizierten Untersuchungen hervor, z.B. [16; 17].

| Variante                                 | Fläche<br>(cm²) | Leistungsdichte (W/cm²) | Kühlverfahren                                         |

|------------------------------------------|-----------------|-------------------------|-------------------------------------------------------|

| DIL auf LP                               | 368             | 0,14                    | Konvektion                                            |

| LCC auf LP:<br>realistische Packung      | 184             | 0,27                    | Erzwungene Konvektion                                 |

| LCC auf LP:<br>dichteste Packung         | 123             | 0,41                    | Erzwungene Konvektion und<br>Wärmeleitung             |

| Hybrid:<br>Dickschicht-Multilayer auf LP | 105             | 0,48                    | Erzwungene Konvektion und<br>Wärmeleitung             |

| Hybrid:<br>Dünnschicht-Multilayer auf LP | 80              | 0,63                    | Erzwungene Konvektion und<br>Wärmeleitung             |

| Chip on Board                            | 60              | 0,83                    | Wärmeleitung zum Chassis,<br>dort Flüssigkeitskühlung |

Tabelle IV Kühlverfahren für verschiedene Packungsdichten

Heute kommt man noch meistens mit Konvektionskühlung bei erzwungenem Luftkreislauf aus. Beim SMT ist man schon häufiger auf die Wärmeleitung angewiesen, um lokale Temperaturerhöhungen abzubauen. Mittelfristig wird man vermehrt zu Flüssigkeitskühlung übergehen müssen, da mit anderen Methoden keine gute Zuverlässigkeit mehr garantiert werden kann. Am Beispiel eines spezialisierten 16-bit-Rechners in Bit-Slice-Technik kann der Zusammenhang zwischen Packungsdichte und Kühlverfahren illustriert werden (Tab. IV).

## 6. Electronic Packaging als Fachgebiet

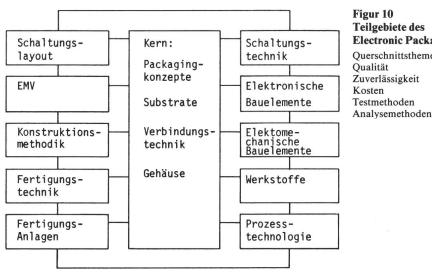

Die Figur 10 fasst zusammen, welche Wissensgebiete zum Electronic Packaging beitragen. Aufgrund der grossen Spannweite kann vorläufig nur eine interdisziplinäre Arbeitsweise zu nutzbaren Ergebnissen führen. Es stellt sich deshalb die Frage, ob eine Zusammenarbeit verschiedener Spezialisten das Problem löst oder ob eigentliche Packaging-Ingenieure benötigt werden. In der Industrie ist meistens eine organisatorische Aufteilung in Entwicklung und Konstruktion vorhanden. Dies führt dazu, dass das Electronic Packaging genau auf dieser Schnittstelle angesiedelt ist, was zu grossen Problemen führen kann, z.B. wenn packaging-bezogene Probleme erst spät im Entwicklungsablauf erkannt werden oder wenn packagingbezogene Zuverlässigkeitsprobleme auftreten.

Eine wirksame, vorbeugende Lösung solcher Probleme dürfte künftig nur möglich sein, wenn Packaging-Ingenieure zugezogen werden. Diese müssen die notwendigen, breitbandigen Kenntnisse besitzen sowie die Fähigkeit, mit vielen verschiedenen Spezialisten und Linienstellen zusammenzuarbeiten.

Interessant ist die Frage, wieweit man Electronic Packaging als eigenständiges Fachgebiet betrachten muss, oder ob ihm diese Bedeutung gar nicht zukommt. Man kann einen Tätigkeitsbereich als Fachgebiet bezeichnen, wenn mindestens einige der folgenden Kriterien erfüllt sind:

- Existenz einer genügenden Menge zusammenhängenden Wissens.

- genügende technische oder wirtschaftliche Bedeutung dieses Wissens.

- explizite Vertretung dieses Gebietes in Lehre und Forschung,

- etabliertes Gebiet bei Industrie und Verbänden.

Es wurde versucht, herauszufinden, wieweit im deutschsprachigen Raum und in den USA diese Kriterien erfüllt sind.

Zur Existenz und Bedeutung des Packaging-Wissens muss an dieser Stelle nichts mehr ausgesagt werden. Aufgrund der vorangegangenen Ausführungen sollte klar sein, dass diese beiden Kriterien erfüllt sind. Hingegen wurden im deutschsprachigen Raum keine Lehrveranstaltungen gefunden, die EP systematisch betreiben. Bei der Forschung sieht es schon etwas besser aus. Die Aktivitäten der Industrie werden am besten deutlich in den Verbänden und den von ihnen durchgeführten Veranstaltungen. Im deutschsprachigen Raum gibt es mindestens sechs Verbände, die Teilgebiete des Electronic Packaging bearbeiten. Allerdings ist eine übergeordnete, systematische Bearbeitung noch nicht gewährleistet.

In den USA haben die Hochschulen erkannt, dass in der Ausbildung etwas zu tun ist. Prince et.al. [18] schreiben dazu: «The emergence of Electronic Packaging Engineering (EPE) as a recognized discipline, and the growing demand in the market place for engineers with some background in EPE gives impetus to the development of educational involvement by universities.»

Die University of Arizona in Tucson bietet drei Kurse zum EP an: EP Applications, EP Design, Special Topics in EP. Die Verbände und die darin vertretene Industrie bearbeiten das EP auf breiter Front. Dabei ist für eine systematische Bearbeitung des Gesamtgebietes schon gut gesorgt, insbesondere in der International Electronic Packaging Society (IEPS) und im Computer Packaging Committee der IEEE Computer Society.

Die meisten der genannten Kriterien sind somit erfüllt, in den USA etwas besser als im deutschsprachigen Raum. Es darf damit geschlossen werden: EP ist eindeutig auf dem Weg, sich als eigenständiges Fachgebiet zu etablieren.

#### 7. Schlussfolgerungen

Die aktuellen Trends in SMT und mehr noch die grundsätzlichen Fragestellungen zeigen, dass das EP für die weitere Entwicklung der Elektronik eine zunehmend wichtigere Rolle spielen wird. Aufgrund aktueller Tendenzen darf man erwarten, dass es sich als eigenständiges Fachgebiet etablieren wird. Einige Zukunftsaufgaben seien angedeutet: Nur durch eine Standardisierung der SMT ist zu erreichen, dass deren inhärente Vorteile breit genutzt werden können. Spezialisierte Packaging-Konzepte für verschiedene Anwendungsgebiete müssen entwickelt werden. Dies sollte schliesslich zu einer Entwurfssystematik führen, die erlaubt, im Einzelfall optimale Lösungen zu finden. Viele Analysemethoden im Zusammenhang mit EP sind heute nur dem Spezialisten zugänglich, weshalb man häufig auf «trial and error» angewiesen ist. Benötigt wird ein integriertes CAE-System, das alle diese

Teilgebiete des **Electronic Packaging** Querschnittsthemen: Qualität Zuverlässigkeit Kosten Testmethoden

Methoden anbietet und langfristig zu einem Expertensystem für EP ausbaubar ist. Fortschritte der Materialtechnologie werden systematisch in das EP einfliessen. Die Wechselwirkung mit neuen Fertigungstechniken (Roboter, CIM) wird die Wirtschaftlichkeit zukünftiger Packaging-Konzepte wahren. Ausserdem sind neue Ansätze in der Forschung nötig, um prinzipielle physikalische oder technologische Grenzen bestehender Methoden zu umgehen. Beispiel hierfür sind optische Bussysteme [19] als Ausweg aus dem Dilemma «Leitungslänge, kapazitive Last, Übersprechen» und Mikro-Steckverbindungen [20], welche die heute begrenzend wirkende Anzahl von Steckerstiften pro Leiterplatte massiv zu erhöhen vermögen.

#### Literatur

- [1] A.D. Hawkins: The changing technology of electronic components and assemblies. IEE Proc., Part A 132(1985)5, p. 311...320.

- [2] W. Loeb: Printed circuits mirror integrated circuits. Electronic Packaging and Production 26(1986)2, p. 168...170.

- [3] H. Müller: Elementare integrierte Strukturen. 2 Bände. Braunschweig, Vieweg-Verlag, 1981.

- [4] H. Müller: Leiterplatten-Technologie. Chip carrier, pin grid array, TAB-Anwendung. Innovationen für die Leiterplatte der Zukunft. Saulgau/Württ., Eugen-G.-Leuze-Verlag, 1984.

- [5] H. Müller: OMD/SMD Oberflächenmontierte Bauelemente in der Leiterplattentechnik. Saulgau/Württ., Eugen-G.-Leuze-Verlag, 1986.

- [6] J.W. Orcutt: Surface mount packaging: Imperfect state of affairs and its impact on users. IEEE Electronic Components Conference 1985, p. 278...281.

- [7] J.L. Prince: VLSI device fundamentals. In: D.F. Barbe: Very large scale integration (VLSI). Fundamentals and applications. Second edition. Berlin/Heidelberg/New York, Springer-Verlag, 1982.

- [8] E. Stein, A. Pedrazza und G. Cott: Anwenderbericht: CAE-Werkzeuge für den IC- und Leiterplatten-Entwurf. Techn. Rdsch. 78(1986)14, S. 86...95.

- [9] E.M. Rogers: Diffusion of innovations. Third edition. New York, The Free Press, 1983.

- [10] C. Pümpin: Management strategischer Erfolgspositionen. Das SEP-Konzept, Grundlage wirkungsvoller Unternehmensführung. 2. Auflage. Bern/Stuttgart, Paul-Haupt-Verlag, 1983.

- [11] J.W. Balde: IEEE Computer packaging committee spring packaging workshop. IEEE Computer Magazine 17(1984)11, p. 90...91.

- [12] J.T. Kolias: Packaging impact on system performance. Third Annual International Electronics Packaging Conference, October 24...26, 1983 Itasca/Illinois. Proceedings of the technical papers, p. 476...489.

- [13] R.D. Cutler: Ground pin optimization in high-speed digital systems. VLSI Systems Design (1986)3, p. 46...48.

- [14] B.K. Gilbert: Packaging and interconnection of GaAs digital integrated circuits. In: VLSI electronics microstructure science. Volume 11: GaAs microelectronics. Edited by N.G. Einspruch and W.R. Wisseman. Orlando a.o., Academic Press, 1985.

- [15] E.E. Davidson: Electrical design of a highspeed computer packaging system. IEEE Trans. CHMT 6(1983)3, p. 272...282.

- [16] D.S. Steinberg: Cooling techniques for electrical equipment. New York a.o., Wiley, 1980.

- [17] A.D. Kraus and A.Bar-Cohen: Thermal analysis and control of electronic equipment. Washington, Hemisphere Publishing Corporation / New York a.o., McGraw-Hill, 1983.

- [18] J.L. Prince a.o.: The role of universities in electronic packaging engineering. Proc. IEEE 73(1985)9, p. 1416...1423.

- [19] K.-R. Hase: Rechnerinternes optisches Bussystem mit Lichtleiterplatte. Elektronik 35(1986)26, S. 81...88.

- [20] E.W. Becker u.a.: Herstellung von Mikrostrukturen mit grossem Aspektverhältnis und grosser Strukturhöhe durch Röntgentiefenlithographie mit Synchrotronstrahlung, Galvanoformung und Kunststoffabformung (LIGA-Verfahren). KfK-Bericht 3995. Karlsruhe, Kernforschungszentrum Karlsruhe, Institut für Kernverfahrenstechnik, 1985.