**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 78 (1987)

**Heft:** 11

**Artikel:** Design-Methoden für analoge Schaltungen

Autor: Schoy, A.

**DOI:** https://doi.org/10.5169/seals-903869

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF: 29.11.2025**

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

### Design-Methoden für analoge Schaltungen

A. Schoy

Es wird ein Einblick in die Methoden der Schaltungsrealisierung für analoge Schaltungen gegeben. Dabei werden Kriterien zur Auswahl des Prozesses, der geeigneten Entwurfsverfahren und der CAD-Werkzeuge aufgestellt sowie Methoden und Werkzeuge beschrieben, die zum jetzigen Zeitpunkt industriell Einsatz finden. Zukünftige Entwicklungen von Methoden und CAD-Werkzeugen werden angedeutet. Ein kurzer Abschnitt über CAD-Hilfsmittel und eine Beschreibung von SPICE als Beispiel eines analogen Simulators beschliessen den Aufsatz.

Un aperçu des différentes méthodologies de construction de circuits analogiques est exposé. Pour ce faire, des critères de choix du procédé, de la marché à suivre ainsi que des outils CAO sont établis. Suit une description des méthodes et des outils trouvant à présent une application industrielle de même que des développements futurs. Un bref paragraphe des outils CAO et une description de SPICE comme exemple d'un simulateur analogique termineront l'article.

#### Adresse des Autors

Albrecht Schoy, dipl. Ing. FH, Dectroswiss Electronic Design AG, 2006 Neuchâtel.

#### 1. Einführung

Grundsätzlich lässt sich der Designvorgang in zwei Hauptbereiche unterteilen, den technologieunabhängigen und den technologieabhängigen. Auf der hierarchisch höheren Ebene müssen die Systemspezifikation und Systemverifikation durchgeführt sowie generelle Überlegungen zur Chiparchitektur gemacht werden. Auf einer niedrigeren Ebene werden die Prozessauswahl, die Wahl der Entwurfsmethoden, der Schaltungs- sowie Layoutentwurf und dessen Überprüfung durchgeführt. Diese Ebenen können jedoch nicht vollständig getrennt betrachtet werden, da beispielsweise eine Systemspezifikation sehr stark von den Möglichkeiten der Schaltungsrealisierung abhängen kann. Es findet also bei diesem ersten Schritt eine starke Auf- und Abbewegung durch die verschiedenen Hierarchien statt.

#### Designphasen

Das Design einer integrierten Schaltung durchläuft im wesentlichen vier Phasen [1]:

- 1. Die *Durchführbarkeitsanalyse* stellt sicher, dass die Entwurfsziele mit der Technologie und den vorhandenen Mitteln machbar sind.

- 2. Während der *Entwurfsphase* wird der Schaltungsentwurf mit der in Phase 1 gewählten Entwurfsmethode durchgeführt.

- 3. In der *Überprüfungsphase* wird die korrekte Implementierung des Entwurfes sichergestellt.

- 4. In der *Realisierungsphase* wird das Chip fabriziert, der Schaltungsentwurf am produzierten Chip verifiziert sowie der Schaltkreis aus der Entwicklung in die Produktion übergeben.

Im folgenden werden im Rahmen der Durchführbarkeitsanalyse die Kriterien für die Auswahl des Prozesses und der geeigneten Entwurfsmethode sowie die Entwurfs- und Simulationswerkzeuge behandelt.

#### 2. Prozessauswahl

Bei der Durchführbarkeitsanalyse findet zwangsläufig eine Prozessauswahl statt. Es stehen dabei zwei Haupttypen zur Auswahl, nämlich bipolare Prozesse und MOS-Prozesse. Die hauptsächlich verwendeten Prozesse sind: NMOS, CMOS, BICMOS, BIPOLAR.

Der Hauptnachteil von NMOS gegenüber CMOS für analoge Schaltungen ist das Fehlen eines komplementären Transistors [2]. Dies begrenzt die mögliche Verstärkung der einzelnen für Operationsverstärker benötigten Verstärkerstufen. Der CMOS-Prozess hat zudem den Vorteil, dass mit ihm Schalter gebaut werden können, welche Signalspannungen über den gesamten Versorgungsspannungsbereich offsetfrei durchschalten können [3]. Der Bipolarprozess hat gegenüber allen MOS-Prozessen die Vorteile, dass eine bessere Transconductance, niedrigeres Rauschen und niedrigere Op.-Amp-Offset-Spannung erreicht. CMOS-Prozesse werden jedoch bevorzugt, wenn höhere Layoutdichte, bessere Ladungsspeicherung und die oben aufgeführten offsetfreien Schalter benötigt werden. Die bipolaren Prozesse werden daher in der Regel für Schaltungen kleiner Komplexität (MSI) mit hohen analogen Anforderungen, z. B für Präzisions-Op.-Amps, benutzt. Dagegen werden Schaltungen hoher Komplexität (VLSI) sowie auch analog/digital gemischte Schaltungen mit niedrigem Stromverbrauch und mittle-Geschwindigkeitsanforderungen vorzugsweise in CMOS-Technologie realisiert. Eine Mischung dieser beiden Technologien, die BICMOS genannt wird, spielt in letzter Zeit eine immer grössere Rolle, da sie die Vorteile beider Technologien vereinigt [4]. Diese bedingt jedoch eine kompliziertere Prozessfolge und damit auch einen höheren Preis. Selbst bei CMOS gibt es noch eine Vielzahl von Prozessvarianten. Aus vielerlei Gründen [5] hat sich N-well-double-polysilicon-CMOS-Prozess als typischer Telecomprozess bewährt. Im Bereich der Telekommunikation ist die Integration von analog-digitalen VLSI-Schaltunweitverbreitet. Grundelemente, die dort zur Verfügung stehen, sind Widerstände. Kapazitäten sowie selbstsperrende P- und N-Kanal-MOS-FETs. Widerstände können mit einer absoluten Genauigkeit von etwa ±20%, Widerstandsverhältnisse aber mit einer Toleranz von etwa 0,2...2% gefertigt werden [5], Kapazitäten mit einer Genauigkeit von ±15%, Kapazitätsverhältnisse mit einer Toleranz von 0,3...1% [5; 3].

# 3. Methoden für den elektrischen Schaltungsentwurf

Beim elektrischen Schaltungsentwurf benützt man heute zwei hauptsächliche Entwurfstechniken. Die erste ist die sogenannte Continuous-Time-Entwurfsmethode, die auch bei Standardbauelementen stark verbreitet ist. Dabei werden Schaltungen mit Kapazitäten, Widerständen und aktiven Elementen über eine kontinuierliche Zeitachse betrieben. Um Streuungen bei Zeitkonstanten oder Nichtlinearitäten aufgrund von prozessabhängigen Ungenauigkeiten auszugleichen, muss nachträglich externes Trimmen erfolgen. Die zweite Entwurfstechnik benutzt die sogenannte Discrete-Time-Entwurfsmethode, Widerstände durch geschaltete Kapazitäten (Switched Capacitors) ersetzt werden. Dadurch können Zeitkonstanten mit Genauigkeiten von 0,1% erreicht werden. Es findet dabei eine

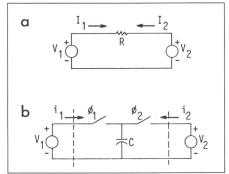

Figur 1 Switched Capacitor - Ausführung eines kontinuierlichen Widerstandes

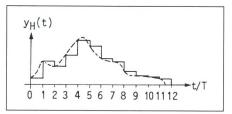

a Kontinuierlicher Widerstand b Switched-Capacitor-Schaltung Transformation der kontinuierlichen Zeit in diskrete Zeitschritte statt. Die Ladung, die bei ohmschen Widerständen in kontinuierlichem Strom fliesst, wird über Schalter mit genau kontrollierter Taktrate von einem Kondensator zum nächsten weitergeschaltet (Fig. 1). Die so erhaltenen diskreten Spannungswerte (Fig. 2) hängen im wesentlichen nur noch von den Kapazitätsverhältnissen und der Oualität der Schalter ab. Bei dieser sogenannten Sampled- data-Technik ist die Benutzung eines Netzwerksimulators wie z. B. SPICE 2 weniger effektiv als beispielsweise SWITCAP, da dieses sowie auch SWAP speziell für die Simulationen im diskreten Zeitbereich konzipiert wurden. Es gibt jedoch Ansätze, die unter Einsatz von speziellen Techniken auch SPICE zur Frequenzanalyse von Filtern heranziehen, mit dem Vorteil, dass das Verhalten der einge-MOS-Operationsverstärker wirklichkeitsgetreuer berücksichtigt wird. Switched-Capacitor-Entwurfsmethoden finden hauptsächlich auf dem Filtergebiet Anwendung, werden jedoch mit Erfolg auch auf D/A-, A/D- Wandler, Komparatoren, Spannungsverstärker, Sinusgeneratoren, Peak-Detektoren und andere Schaltungen übertragen. Praktische Anwendungen, die in zahlreichen Veröffentlichungen beschrieben wurden, sind seit Ende der siebziger Jahre im Einsatz. Umfassende Bücher über dieses Thema liegen jedoch erst seit wenigen Jahren vor. Dem Interessierten werden die Quellen [3; 5; 7; 8; 9] zur Lektüre empfohlen.

# 4. Layoutorientierte Entwurfsmethoden

Für das Layout von analogen Schaltkreisen stehen dieselben Entwurfsverfahren wie für digitale Schaltkreise zur Verfügung. Von Full Custom über Macro Cells und Standard Cells zu Analog Arrays.

#### 4.1 Analog Arrays

Analog Arrays sind entweder sehr stark auf ein Gebiet limitert, z.B. auf die Switched-Capacitor-Filterrealisierung, oder bestehen aus einer Ansammlung von analogen Standardschaltungen und passiven Komponenten, die mit einer oder mehreren Maskenebenen verbunden werden können. Im letzteren Fall werden sie oft für Breadboarding auf Silizium verwendet, mit dem die Prozesstechnologie

Figur 2 Beispiel eines Sampled-Data-Signals

Zero-order sample-and-hold

und der Systementwurf verifiziert werden [10]. Der Vorteil ist hohe Entwurfssicherheit und schnelle Siliziumrealisierung, der Nachteil Platzverlust auf dem Silizium, da vorgefertigte Redundanzen eingebaut werden müssen. Auch muss die Komplexität eines solchen Analog Arrays niedrig gehalten werden, um eine Vielzahl von Anwendungen zu ermöglichen.

In vielen Fällen ist die Systemkomplexität jedoch so hoch, dass die Entwicklungszeit für den gesamten Entwurfszyklus massgebend wird und die Fabrikationszeit eine untergeordnete Rolle spielt. In diesem Fall besteht kein Grund mehr, sich auf wenige programmierbare Ebenen zu beschränken. Zudem wird bei Verwendung aller Masken die Designflexibilität erhöht und damit der Entwurf erleichtert.

#### 4.2 Full-Custom-Methode

Bei der Full-Custom-Methode ist der Freiheitsgrad des Schaltungsentwicklers nur durch die Grenzen der Prozesstechnologie, der Schaltungstechnik und der Chipgrösse beschränkt. Der Schaltungsentwurf wird (gemäss der Funktion) in verschiedenen Basiszellen aufgeteilt, die für sich entworfen und optimiert werden. Nach Fertigstellung der Einzelzellen wird der Schaltkreis «von Hand» wie ein Puzzle in immer komplexere, hierarchisch höhere Strukturen zusammengesetzt. Dabei werden Grundelemente wie Kapazitäten, Widerstände, Schalter, Operationsverstärker usw. zuerst elektrisch entworfen und geometrisch dimensioniert. Es wird dann eine graphische Datenbasis des elektrischen Schemas erstellt, die durch Umformung in eine Simulationsnetzliste als Simulationsgrundlage zur Vorsimulation mit SPICE benützt wird. Danach werden die Entwurfsdaten unter Berücksichtigung entsprechender Auslegungsregeln in eine Layoutdatenba-

sis umgesetzt, die später zur Maskenherstellung benützt wird. Die Auslegungsregeln umfassen - im Gegensatz zum Design von digitalen Schaltungen - nicht nur die sogenannten geometrischen Designrules, sondern auch Regeln, die beispielsweise das Matching von Kapazitäten oder Eingangstransistoren einer Differenzstufe sicherstellen. Die Layoutdatenbasis wird nun mit Hilfe von Prüfprogrammen mit der vorgegebenen elektrischen Netzliste verglichen, und die parasitären Kapazitäten und Widerstände werden in eine neue, komplette Netzliste eingetragen. Eine Nachsimulation mit diesem realistischen Modell der Analogzelle zeigt, ob das angestrebte elektrische Verhalten erreicht wird. Der Entwurf auf Transistorebene setzt detaillierte Kenntnisse der Schaltungs- sowie der Prozesstechnik voraus; er wird anschliessend am Beispiel eines Operationsverstärkers erläutert.

#### Full-Custom-Beispiel: Operationsverstärker

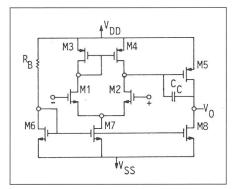

Zuerst werden die Anforderungen wie Slew Rate¹, Verstärkung, Null-dB-Frequenz sowie die Ruheströme bei Verstärkerstufen vorgegeben. Aus der Literatur wird dann ein bekanntes Schaltbild eines CMOS-Operationsverstärkers ausgewählt (Fig. 3). Mittels Kleinsignal-Ersatzschaltbildern der Verstärkerstufen und den Knotengleichungen kann die Gleichung für die

$^{\text{I}}$  Maximale Änderungsrate der Ausgangsspannung unter Grosssignalbedingungen in  $V/\mu s.$

Figur 3 Schaltschema eines ungepufferten CMOS-Operationsverstärkers mit einem n-Kanal-Transistorpaar

V<sub>DD</sub> Drainpotential

VSS Sourcepotential

$V_0$  Outputsignal

R<sub>B</sub> Bias-Widerstand

Gesamtverstärkung ermittelt werden. Unter Berücksichtigung der Prozessparameter können dann mit Hilfe der Modellgleichungen die entsprechenden W/L-(Width/Length-)Verhältnisse der einzelnen Transistoren berechnet werden<sup>2</sup>. Die Ergebnisse werden mit Hilfe von Netzwerksimulatoren wie z. B. SPICE simuliert und danach anhand von Simulationsprotokollen ausgewertet. Mit dem Ergebnis dieser Auswertung wird der Entwurf durch einen iterativen Prozess so lange verbessert, bis die gewünschte Spezifikation erfüllt ist. Bei typischen Werten für den CMOS-Prozess und die Transistorgrössen erreicht die Spannungsverstärkung Werte von 300 bis 40 000. Die Unity Gain Bandwidth liegt im Bereich von 2...0,4 MHz.

# 4.3 Wiederverwendung vorhandener Entwürfe

Die nächsthöhere Ebene des analogen Schaltungsentwurfs besteht darin, bereits vorhandene Schaltungsblöcke zu verwenden, um durch gezielte Anpassung einzelner Teilfunktionen die gewünschte Schaltungsfunktion zu erhalten. Dabei liegen diese Funktionsblöcke bereits als Layout vor, dessen Ausmasse und Formen jedoch nicht festgelegt sind. Daher muss bei diesen bestehenden Layouts oft nach der Anpassung der elektrischen Funktion noch die geometrische Form geändert werden, damit die resultierende Zelle in das neue Design passt. Anschliessend muss die Verifizierung der Schaltung wiederum auf Transistorebene mit einem entsprechenden Simulator durchgeführt werden. Mit dieser Methode werden Kosten eingespart; sie erfordert jedoch wiederum detailliertes Wissen über Prozesstechnologie, Schaltungstechniken sowie Layouterstellung.

# 4.4 Automatische Dimensionierung

Eine weitere Möglichkeit, Kosten zu sparen, besteht darin, die Designzeit für den elektrischen Entwurf einer Zelle zu verkürzen. Durch Benützen des Programms IDAC [12] wird eine Bibliothek von Grundkonfigurationen, z. B. für Operationsverstärker oder

$^2$  Die Kleinsignalanalyse dieses Schaltkreises ist vom Konzept her ähnlich der Analyse des  $\mu A\text{-}741\text{-}Operationsverstärkers}, beschrieben in [11].$

Spannungsreferenzen, vorgegeben. Nach Eingabe der gewünschten Spezifikationen führt das Programm die Dimensionierung der Elemente durch und erstellt eine simulationsgerechte Netzliste. Damit kann der Schaltungsvorschlag anschliessend verifiziert werden. Danach müssen wieder Layout und Nachsimulation durchgeführt werden. Der Vorteil dieser Methode liegt darin, dass die zeitaufwendigen Iterationen beim elektrischen Schaltungsentwurf wegfallen. Allerdings müssen die elektrischen Prozessparameter bei der Initialisierung des Programmes eingegeben werden. Detaillierte Kenntnisse der Prozesstechnologie und Layouterstellung sind somit auch hier notwendig.

#### 4.5 Standardzellenmethode

Da elektrischer Entwurf, Layout und Simulation auf Transistorebene sehr kostspielig sind, ist man seit einiger Zeit dazu übergegangen, Standardzellenbibliotheken herzustellen. Dabei werden dem Benutzer beispielsweise Operationsverstärker, Komparatoren, Widerstände, Kapazitäten und analoge Schalter als Grundelemente zur Verfügung gestellt. Diese werden von deren Herstellern einer ausgiebigen Charakterisierung unterzogen; die Ergebnisse werden anschliessend in Datenblätter übertragen. Der Benutzer kann nun aus diesen die geeigneten Elemente auswählen und zur Simulation deren Makrobeschreibung verwenden. Da nicht mehr auf Transistorebene simuliert werden muss, sind die Simulationszeiten jetzt sehr viel kürzer. Beim anschliessenden Layout des Schaltkreises können Automatic-Place- and-Route-(APAR-)Methoden eingesetzt werden. Beim Plazieren der Zellen müssen jedoch Handeingriffe vorgenommen werden, damit nicht elektrisch störempfindliche tungsteile an Erzeuger von Störspannungen angrenzen. Aus demselben Grund empfiehlt es sich auch, komplett getrennte Spannungsversorgungen für analoge und digitale Schaltungsteile vorzusehen. Da heutige auf dem offenen Markt erhältliche APAR-Programme diesen speziellen Erfordernissen noch nicht genügen, müssen nach dem Plazieren und Verdrahten der Zellen aufwendige Nacharbeiten vorgenommen werden. Um den erforderlichen Zeitaufwand klein zu halten, werden dazu leistungsfähige Layoutsysteme mit Graphikprozessoren eingesetzt. Die Bedienung der APAR-

Programme sowie der Layoutsysteme erfordert hochkarätige Spezialisten mit zusätzlichen Kenntnissen in der Schaltungs- und Prozesstechnologie. Es empfiehlt sich daher, als Schnittstelle zwischen Systementwickler und IC-Entwickler eine elektrisch simulierte Netzliste zu benutzen. So braucht er sich nicht um das relativ komplizierte Layout zu kümmern.

#### Beispiel zum Einsatz von Standardzellen

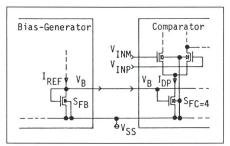

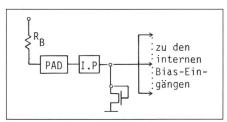

Um die Flexibilität dieser Methode zu erhöhen, werden die Biasspannungen und -ströme den Komparatoren und Operationsverstärkern zugeführt. Damit kann der gewünschte Biasstrom einer Funktionszelle je nach Bedarf mit dem entsprechenden Biasgenerator eingestellt werden (Fig. 4). Dies er-

Figur 4 Beispiel für analoge Standardzellen

Die Standardzelle «Bias Generator» bestimmt das Verhalten der Standardzelle «Comparator»

V<sub>B</sub> Bias-Potential

IDP Bias-Strom

laubt beispielsweise ein Einstellen der gewünschten Null-dB-Frequenz und der Verstärkung. Die Einstellung des Biasstromes kann auch über einen externen Widerstand erfolgen (Fig. 5). Dies bringt zwei Vorteile: zum einen kann der eingestellte Strom genauer bestimmt werden, da externe Widerstände mit einer Toleranz von 1% benutzt werden können, und zum anderen ist die Flexibilität für nachträgli-

Figur 5 Über einen externen Widerstand R<sub>B</sub> kann der Bias-Strom eingestellt werden

PAD Bonding Pad IP Input Protection

R<sub>B</sub> Externer Bias-Widerstand

| Biaswider-<br>stand R <sub>B</sub> ,<br>kΩ | Verstärkung | Bandbreite<br>MHz |

|--------------------------------------------|-------------|-------------------|

| 50                                         | 348         | 1,2               |

| 75                                         | 3950        | 1,1               |

| 100                                        | 5036        | 1                 |

| 200                                        | 9266        | 0,79              |

| 500                                        | 21 480      | 0,5               |

| 1000                                       | 41 310      | 0,39              |

Tabelle I Einfluss des Biaswiderstandes auf Verstärkung und Bandbreite des Operationsverstärkers

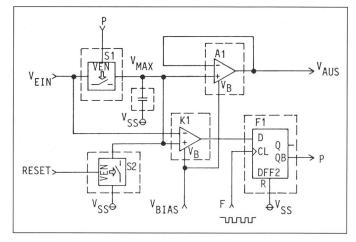

che Spezifikationsänderungen grösser. In Tabelle I ist der Einfluss des externen Widerstandes auf das Verhalten des Operationsverstärkers dargestellt [7]. Den Aufbau eines Switched-Capacitor-Scheitelwertmessers mit Standardzellen zeigt die Figur 6. Die Kapazität C speichert den grössten Wert von  $V_{\rm EIN}$  dadurch, dass der Komparator K1 bei  $V_{\rm EIN} > V_{\rm MAX}$  am Ausgang negativ wird und damit nach einer Clock-Periode über das Signal P den Schalter S1 einschaltet. Die Schaltfre-

quenz des Flipflops F1 muss dabei wesentlich höher sein als die höchste Frequenz von  $V_{\rm EIN.}$  Verstärker A1 puffert das Signal, und über den Schalter S2 kann es zurückgesetzt werden.

#### 4.6 Einsatz von Makroblöcken

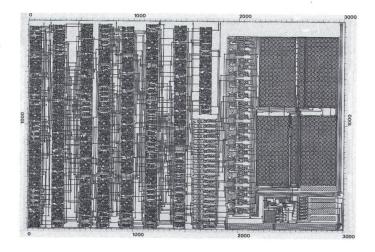

Auf der höchsten Ebene der Schaltungsrealisierung werden Standardmakroblöcke eingesetzt, die vorgängig z. B. mit Standardzellen realisiert wurden. Diese Standardmakroblöcke, die vorzugsweise auf der Transistorebene entworfen und ausgelegt werden, stellen sozusagen den grössten gemeinsamen Nenner dar. Beispiele für diese A/D-Wandler, Blöcke sind D/A-Wandler, Filter mit Standardwerten, Sinusgeneratoren usw. Diese Blöcke sind jedoch nicht parametrisierbar, d. h. die angebotenen Spezifikationen passen oder passen nicht. Diese Makroblöcke können aus gemischt digitalen und analogen Funktionen bestehen und sind im Normalfall als rechteckige Blöcke ausgelegt (Fig. 7). Dies hat beim sogenannten

Figur 6 Switched-Capacitor-Scheitelwertmesser

Realisierung mit Standardzellen

Figur 7 Layout eines 8-bit-A/D-Wandlers

Floorplaning des Chips gewisse Vorteile. Eine Vielzahl von Programmen, die sich jedoch alle zurzeit noch in der Entwicklungsphase befinden, versuchen parametrisierbare Makroblöcke zu erstellen. Diese erlauben eine grössere Flexibilität für die Spezifikation der Blöcke.

#### 5. CAD-Werkzeuge

Die Entwicklung von CAD-Werkzeugen ist für analoge integrierte Schaltungen noch nicht so weit fortgeschritten wie für digitale Schaltungen. Die Gründe dafür sind vielschichtig. Zum einen hat es längere Zeit gedauert, bis sich aus dem anfänglichen Vollkundenschaltungsentwurf eine gewisse Designmethodik herausgebildet hat, zum anderen sind Werkzeuge für analoge Schaltungen erheblich schwieriger herzustellen als für digitale Schaltungen. Bei den heute erhältlichen Programmen für die analoge Schaltungsrealisierung dominieren derzeit Einzelprogramme. Programmpakete wie Silicon Compiler für Analogschaltungen sind zwar in Entwicklung, jedoch noch zu leistungsschwach und daher noch nicht kommerziell einsatzfähig [10]. Auf der Entwurfsebene kann ein Programm wie IDAC die Produktivität beträchtlich erhöhen. Auf der Simulationsebene stehen Programme wie SPICE2 und DOMOS zur Netzwerksimulation. **SWITCAP** SWAP zur Simulation von Switched-Capacitor-Filter und ANDI zur Simulation von gemischt digital/analogen Schaltungen zur Verfügung. Generell ist festzustellen, dass leistungsfähige Simulatoren für gemischt digital/analoge VLSI-Schaltkreise derzeit am freien Markt nicht erhältlich sind. Auf der Schematic-Capture-(Schemaerfassungs-) und Layout-Ebene können dieselben Hard- und Softwaremodule eingesetzt werden, die auch für digitale Schaltkreise zur Verfügung stehen. Dabei ist jedoch zu beachten, dass Softwaremodule mit Automatisierungsroutinen nur sehr begrenzt einsetzbar sind und Handeingriffe auf jeder Entwurfsebene möglich sein müssen.

#### SPICE2, Beispiel eines Analyseprogramms

Auf dem Gebiet der Netzwerksimulation ist SPICE2 [13] ein Analyseprogramm mit langjähriger Tradition. Der Simulator benutzt die Grosssignal-Ersatzschaltbilder zur Ermittlung der DC-Variablen. Aus den DC-Variablen werden die Parameter der Kleinsignal-Ersatzschaltbilder stimmt, die dann zur Analyse des Schaltkreises benützt werden. Typische SPICE2-Simulationen sind Transientenanalyse, AC-Analyse und DC-Analyse. Als Voraussetzung für die Simulation auf Transistorebene muss zuerst das Transistormodell dem aktuellen Prozess angepasst werden. Die aktuellen Prozessparameter können mit speziell dafür vorgesehenen Programmen (z. B. TCAP, MOSAID) aus den gemessenen Ergebnissen so berechnet werden, dass sich bei der Simulation eine Deckung mit der gemessenen Transistorkurvenschar ergibt. Danach kann die Verifizierung des Schaltungsentwurfes auf Transistorebene stattfinden.

Diese Methode erlaubt jedoch nur Komplexitäten von etwa 200 bis 500 Elementen; darüber hinaus wird sie zeitlich ineffizient. Zurzeit arbeiten einige Firmen an Hardwarebeschleunigern für SPICE2. Bei der Netzwerkanalyse sind jedoch im Vergleich zur Logiksimulation weniger Parallelisierungen möglich, daher sind diese Beschleunigungsmethoden noch auf Faktoren von 5 bis 10 [14] limitiert. In Zukunft wird wohl hauptsächlich der Einsatz von leistungsfähigeren Multiprozessorrechnern eine weitere Beschleunigung des Simulationsvorganges erbringen. Softwaremässige Beschleunigung mit Waveform-Relaxation-Techniken [15] gehen auf Kosten der Genauigkeit und finden daher hauptsächlich bei der Zeitsimulation von digitalen Schaltungen Anwendung.

#### 6. Ausblick

Wie die Erfahrung aus der digitalen Designwelt zeigt, werden die CAD-Werkzeuge dann entwickelt, wenn ein Markt dafür vorausgesehen wird. Da der Markt für analoge ASIC wächst, wird auch in Zukunft die Entwicklung in Richtung analoge Silicon Compilation gehen. Anfangs wird sie sich auf Teilfunktionen, wie Filter und Wandler, konzentrieren. Sie wird langsamer verlaufen als bei digitalen Schaltkreisen, da es bei analogen Schaltungen ungleich schwieriger ist, ein Gesamtkonzept zu entwerfen, das alle Möglichkeiten und Notwendigkeiten des Designs unter einen Hut bringt.

#### Literatur

- S. Goto: Design methodologies. Elsevier Science, Publ. Comp., Inc, 1986. p. 123...149 (M. Lang, P. McCormick: Hierarchical design methodologies: A VLSI necessity).

- [2] J. McCreary: Design of bipolar and MOS circuits. VDE-Verlag, Berlin, 1983 (MOS technology and fabrication).

- [3] R. Gregorian and G.C. Temes: Analog MOS integrated circuits for signal processing. J. Wiley & Sons, N.Y., 1986.

- [4] G. Tröster et al.: 1986 IEEE Int. Symposium on Circuit and Systems. p. 113...116 (Potentials of the BICMOS technology for highperf. VLSI).

- Y. Tsividis and P. Antognetti: Design of MOS VLSI circuits for telecommunications. Prentice-Hall, Inc., N. Jersey, 1986. p. 2...29

(E. Demoulin: Fabrication technology of MOS ICs for telecommunications).

- [6] N. Attaie and B. Ahuja: 1986 IEEE Int. Symposium on Circuit and Systems. p. 141...143 (Computer-aided design of a voice band modem sw. cap. filter).

- [7] Ph.E. Allen and E. Sanchez-Sinencio: Switched capacitor circuits. Van Nostrand Reinhold Comp., N.Y., 1984.

- [8] P.R. Gray et al.: Analog MOS integrated circuits. IEEE Press, N.Y., 1980.

- [9] Ph.E. Allen and D.R. Holberg: CMOS analog circuit design. Holt, Rinehart and Winston, N.Y., 1987.

- [10] Ph.E. Allen: A Tutorial Computer-aided design of ICs, p. 608...616 Proceedings of the IEEE 1986 Custom integrated circuits conference, Rochester.

- [11] P.R. Gray and P.G. Meyer: Analysis and design of analog integrated circuits. J. Wiley & Sons, N.Y., 1977.

- [12] M.G. Degrauwe and W.M. Sansen: The current efficiency of MOS transconductance amplifiers. IEEE Journal of Solid-State Circuits, 19(1984)3, p. 349.

- [13] E.E. Hoefer and H. Nielinger: SPICE, Analyseprogramm für elektronische Schaltungen. Springer-Verlag, Berlin Heidelberg 1985.

- [14] G. Bischoff and St. Greenberg: A parallel implementation of the circuit simulator SPICE. IEEE International Conference on Computer-Aided Design, Santa Clara 1986. p. 182.

- [15] M.E. Mokari-Bolhassan et al.: A new robust relaxation technique for VLSI circuit simulation. IEEE International Conference on Computer-Aided Design, Santa Clara 1985. p. 26...32.