**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 77 (1986)

Heft: 7

**Artikel:** Wirtschaftliche Herstellung von kundenspezifischen ICs (ASICs):

Bericht über die ITG-Sponsortagung vom 16. Januar 1986 in Brügg/Biel

**Autor:** Baumann, M.

**DOI:** https://doi.org/10.5169/seals-904189

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

## Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 09.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Wirtschaftliche Herstellung von kundenspezifischen ICs (ASICs)

Bericht über die ITG-Sponsortagung vom 16. Januar 1986 in Brügg/Biel

Zur ersten Sponsortagung im neuen Jahr hat die Firma Lasarray S.A., Brügg, eingeladen, eine Firma der Fela-Gruppe, die letztes Jahr im In- und Ausland einiges Aufsehen mit ihrem laseroptischen Verfahren zur Herstellung von kundenspezifischen ICs erregt hatte. Dem Firmengründer E. Uhlmann wurde übrigens für diese Leistung 1985 der Oekreal-Innovationspreis verliehen. Dass der Einladung sehr viele Interessenten folgen würden, war vorauszusehen, und so kam es, dass auch diesmal wieder nicht alle Anmeldungen berücksichtigt werden konnten; selbst so waren die Platzverhältnisse recht eng. Leider scheint es für das Platzproblem keine Lösung zu geben. Denn erstens kann man der einladenden Firma keine unbegrenzten Kosten zumuten, und zweitens gibt es für solche Veranstaltungen, wenn sie nicht an Effizienz einbüssen sollen, eine obere Teilnehmergrenze. Einzige Garantie für einen sicheren Platz scheint immer noch die frühzeitige Anmeldung zu sein.

Die Einladung der Lasarray war im Anschluss an die ITG-Semicustom-Tagung in Brunnen¹ erfolgt; die Veranstaltung war somit die erste Fortsetzung in dieser wichtigen Diskussionsrunde. Eröffnet wurde sie von Prof. Dr. Leuthold, dem Präsidenten der ITG. Nach ihm gab der Gastgeber E. Uhlmann einen Überblick über die Geschichte der 1967 gegründeten Fela sowie über die Gründe, die zur Entwicklung des Lasarray-Verfahrens führten. Ausgangspunkt für fast alle Tätigkeiten des Unternehmens mit gegen 300 Mitarbeitern ist noch immer die Leiterplatte. Das Angebotsspektrum erstreckt sich vom computerunterstützten Entwurf von Prints über die Herstellung von Leiterplatten und Folientastaturen bis zu Elektronik-Laborsystemen und zur Know-how-Vermittlung bei der Errichtung von Leiterplattenfabriken. In der Schweiz wurden 1984 etwa 5000 neue Leiterplatten aufgelegt. Nach Schätzung von E. Uhlmann lassen sich davon 20% durch ASICs (applikationsspezifische ICs) ersetzen.

Mittelfristig zeichnet sich somit allein in der Schweiz ein Markt für Tausende von ASICs pro Jahr ab, vorausgesetzt, dass die Kosten nicht höher und die Durchlaufzeit nicht länger als für äquivalente Leiterplatten sind. Bis heute liegt der Break-even-Punkt selbst bei Gate-Arrays noch bei einigen tausend Schaltungen. Lasarray will die Limite auf 20 Stück senken. Dass diese Zielsetzung auch internationales Interesse erweckt, demonstrierte die gleichzeitige Anwesenheit zweier japanischer Besucher.

Im zweiten Vortrag wurde von L. Soldani die Design- und Softwareseite des Lasarray-Verfahrens erläutert. Das Design der Gate-Arrays erfolgt mit Hilfe eines spezialisierten Silizium-Compilers. Dieser berechnet die für die gewünschte Kundenschaltung nötigen Verbindungen, welche auf dem speziell für Lasarray vorfabrizierten Waver (Stock Waver) zu realisieren sind. Die Software beinhaltet Programme für die Schaltungserfassung, logische und zeitliche

Simulation, Testvektorengenerierung, automatische Plazierung und Verdrahtung sowie Testvollständigkeitsanalyse und Ausgabe von Steuerdaten für den Fertigungsprozess.

Der nachfolgende Vortrag von E. Döring befasste sich mit der Fertigungstechnik des Lasarray-Verfahrens. Die Fabrikationseinheit, das sogenannte Prozessmodul, ist auf drei Containern untergebracht, was dessen geringen Platzbedarf (etwa 9 m×7,5 m) demonstriert. Der Input in den Prozess-Modul besteht im wesentlichen aus den vorfabrizierten Wavern, den (leider sehr teuren) Keramikgehäusen, der auf dem Si-Compiler generierten Software, etwas Chemie sowie Energie, Luft und Wasser. Kernstück neben vielen andern Geräten, die zusammen immerhin einige Millionen Franken kosten, ist der Lasarray-Pattern-Generator (LPG), der auf der Al-Verdrahtungsebene des Wavers durch Belichten der darüberliegenden Photoschicht die Verbindungslinien definiert, die im folgenden Arbeitsgang herausgeätzt werden. Die fertigen Wavers und später auch die montierten Chips werden mit besonders für Gate-Arravs angepassten, selbstentwickelten Testgeräten geprüft und nachfolgend hermetisch verpackt.

Nach der Kaffeepause kamen, wie an Sponsortagungen üblich, die Kollegen aus der Branche zu Wort; Sponsortagungen werden zwar vom Einladenden finanziert, sind aber keine blossen Werbeveranstaltungen, sondern sollen möglichst objektive Informationen vermitteln.

Ch. Fiechter von der Abteilung Elcoma der Philips AG eröffnete die zweite Vortragsserie mit einem Überblick über die eigenen Gate- und Cell-Arrays. Diese werden in CMOS- (3...15V) und HCMOS-Technik (2...6V) ausgeführt. Die Entwicklungszeit beträgt bei Elcoma 2...10 Wochen, die Fabrikationszeit etwa 5 Wochen. Philips arbeitet auf dem Gebiet der 2-µ-System-Cell-Technik mit TI zusammen, woraus sich für den Kunden eine interessante Second-Source-Möglichkeit ergibt. Nächstes Jahr sollen 1-μ-Cell-Arrays auf den Markt gebracht werden. Die Chipkapazität wird damit auf 1 Mio Transistoren erhöht, und die Delayzeiten werden weiter gesenkt. Laut Ch. Fiechter muss man bei einer Gate-

#### Adresse des Autors

M. Baumann, dipl. El.-Ing. ETH, Redaktor Bulletin SEV/VSE, Seefeldstrasse 301, 8034 Zürich.

<sup>1</sup> Bull. SEV/VSE 76(1985)15, 10. August, S. 935...936: Entwicklung von Semicustom-Schaltungen (CAD).

Array-Entwicklung mit Basiskosten pro Entwicklungseinheit von etwa 20 000 bis 50 000 Franken und Chipkosten von 5 bis 30 Franken rechnen.

Die Bedeutung der Design-Häuser bei der Entwicklung von ASICs vermochte der Vertreter der HMT microelectronics AG, A. Reber, sehr eindrücklich darzustellen. Nach einem generellen Überblick über den Werdegang einer ASIC-Entwicklung zeichnete er die Rolle, die das Designhaus als Entwicklungspartner spielt oder spielen könnte. Als Gründe für diesen Weg führte er unter anderem das Fehlen von Knowhow, von qualifizierten Mitarbeitern und Kapazität sowie die Teilung der Verantwortung und die Weitergabe von Erfahrungen an. Die Hauptschwierigkeit, auf die ein neuer ASIC-Kunde stösst, ist das Testproblem; man kann ja nicht so einfach - wie auf einer Leiterplatte - innerhalb eines ICs auf Fehlersuche gehen; dazu lässt die wachsende Komplexität Ad-hoc-Methoden immer aussichtsloser erscheinen. Der Zeitpunkt, bei dem die Zusammenarbeit zwischen Kunde und Deisgnhaus beginnen sollte, hängt stark von den Möglichkeiten und Erfahrungen des Kunden ab. In Hinsicht auf die genannten Testprobleme empfiehlt sich aber, spätestens bei der definitiven Festlegung der Schaltung mit dem Spezialisten Kontakt aufzunehmen. Die Testbarkeit ist eine eigene Wissenschaft; dies zeigte der abschliessende Überblick über Teststrategien.

Dass die Schweiz von Spezialitäten lebt, bewies wieder einmal der folgende Vortrag

von F. Leuenberger, CSEM, Neuchâtel. Der Schwerpunkt der Arbeiten des CSEM liegt auf dem Gebiet der Full-Custom-Schaltungen, wobei aber nicht in erster Linie Anwendungen mit hohen Stückzahlen, sondern Anwendungen, bei denen niedrige Betriebsspannung, extrem niedrige Leistung, Integration von Analog- oder Sensorfunktionen und von Permanentspeichern (EEPROM) gefordert werden, im Vordergrund stehen. Im Gegensatz zu einem Designhaus muss das CSEM meist tiefer in die Entwicklung eines neuen Produkts einsteigen. In vielen Fällen ist der Ausgangspunkt ein Analogschaltungsblock. Das CSEM hat deshalb sehr vielseitige Beziehungen zu Industrie und Hochschulen. Für die Kleinseriefabrikation betreibt die Firma eine eigene Pilotlinie, Grossserien werden bei industriellen IC-Herstellern gefertigt. Die Pilotlinie kann auch von fremden Firmen und Hochschulen benutzt werden. Aus Kompatibilitätsgründen war dies allerdings bis jetzt nur in begrenztem Umfang möglich. In Zusammenarbeit mit EM Microelectronic Marin und deren US-Partnerin VTI wird deshalb bis März 1987 eine 5V-CMOS-Technologie mit Minimaldimensionen von 2 µm eingeführt. Gegen Ende 1987 soll eine 1,5-V-Variante sowie eine Variante mit 2 Poly-Si-Ebenen zur Verfügung stehen. Derzeit diskutiert man noch, ob gleich von Anfang an 2 Metallebenen vorgesehen werden sollen. In seinen übrigen Ausführungen konnte man von F. Leuenberger noch viele technologisch interessante Details über IC-Spezial-

anwendungen hören. Obwohl der Schwerpunkt Vollkundenschaltung heisst, existiert beim CSEM eine ASIC-Abteilung. Als Zielwerte für die Durchlaufzeiten (ab Magnetband) werden je nach Basistechnologie 4 bis 6 Wochen angegeben.

Den letzten Vortrag hielt Dr. P. Kilius, Dectroswiss Electronic Design AG, Neuchâtel. In eindrücklicher Weise behandelte er die wirtschaftlichen Aspekte der Entwicklung und Fertigung von Kundenschaltungen. Er machte auf die Schwierigkeiten aufmerksam, die sich beim Vergleich verschiedener Angebote ergeben. So werden oft die Entwicklungskosten auf die Fertigungskosten und damit auf den einzelnen IC verlagert. Trotz diesen Schwierigkeiten lassen sich die wirtschaftlichen Grenzen zwischen Lasarray, Gate Array, Cell Array und Full Custom einigermassen angeben, wie der Referent anhand interessanter Diagramme zeigte. Die wichtigsten Parameter eines jeden derartigen Vergleichs sind Stückzahl und Komplexität. Zum Abschluss seines Vortrags gab P. Kilius seiner Meinung Ausdruck, dass der Trend zunehmend in Richtung Standardzellen und Full Custom weise.

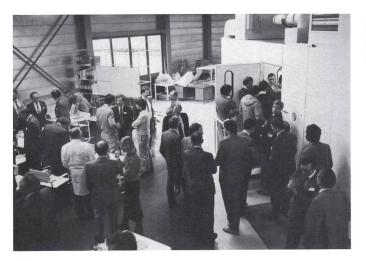

Der Nachmittag war der Besichtigung der Lasarray-Anlage gewidmet. Nachdem man bereits auf Photos die Lasarray-Fabrik auf dem Weg zur Münchner Electronica gesehen hatte, war man allgemein gespannt auf den Blick ins Innere. Und man wurde nicht enttäuscht; die mobile Fabrik macht, wie das obige Bild zeigt, einen durchaus professionellen Endruck.