|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 76 (1985)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 17                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | Softwaresystem CBDS zur Entwicklung von Leiterplatten                                                                                                                                                                     |

| <b>Autor:</b>       | Senn, H. / Bollinger, P.                                                                                                                                                                                                  |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-904668">https://doi.org/10.5169/seals-904668</a>                                                                                                                                   |

### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# **Softwaresystem CBDS zur Entwicklung von Leiterplatten**

H. Senn und P. Bollinger

Der Aufsatz beschreibt das IBM-Programmpaket CBDS, welches der technischen Auslegung, der Prüfung und der Arbeitsvorbereitung bei der Herstellung von Leiterplatten dient.

L'article décrit la série de programmes CBDS d'IBM pour la conception, le contrôle et la préparation du travail d'usinage de plaques imprimées.

## **1. CBDS-Merkmale**

CBDS ist ein CAD/CAM-Programmpaket der IBM, welches den gesamten Prozess der technischen Auslegung, Prüfung und Arbeitsvorbereitung für den Leiterplattenentwurf computermässig unterstützt. Das Paket stammt von Bell-Northern Research, Ottawa, dem gemeinsamen Design- und Researchzentrum der Mutterfirmen Bell-Canada und Northern Telecom. Seine frühere Version lief unter dem Namen COPES; diese wurde umgestaltet und den neuesten Entwicklungen angepasst. Das CBDS2 läuft unter dem VM-Betriebssystem und ist in die weiteren CAD/CAM-Angebote der IBM integriert (CADAM, CAEDS). CBDS zeichnet sich aus durch:

1. vollständige Funktionen und eine durchgehende Dokumentation des Entwicklungsvorgangs, wobei alle Teilgebiete über zwei umfassende Datenbanken, Komponenten-Datenbank und Design-File, mit entsprechender Datenintegrität miteinander verbunden sind,

2. umfassende Entwurfshilfen mit verschiedenen Regeln bis zum automatischen Plazieren und Entflechten,

3. hohe Flexibilität in bezug auf die Grösse der Karten und die Anzahl Schichten,

4. integrierte Prüfung der Logik mit digitaler On-line-Simulation im Entwurfsprozess (eine Analogsimulation ist in Vorbereitung),

5. Analysefunktionen, welche die nicht verbundenen Anschlüsse ermitteln, die Herstellungstoleranzen prüfen und Schema und Entwurf vergleichen,

6. Erstellung der branchenüblichen Fertigungsunterlagen.

Die mit dem System gelieferte *Komponenten-Datenbank* enthält physische logische und administrative Daten von

rund 4000 gängigen Komponenten sowie deren Symbole. Der *Design-File* (Entwurfs- oder Produktdatenbank) hält die gesamte Entwicklung vom Schema über Layout bis zum Endprodukt in allen Details fest.

CBDS besteht aus zwei Lizenzprogrammen, welche je mit verschiedenen Preisoptionen erhältlich sind, nämlich dem

- *Circuit Pack System (CPS)*, welches die Eingabe des Schaltbildes, die Entflechtung der Schaltung und das Erzeugen der NC-Steuerdaten umfasst, und dem

- *Design Verification System (DVS)*, das der Simulation einer digitalen Schaltung und der Erstellung von Testdaten für Fertigungssystemen dient.

## **2. Entwurf einer Leiterplatte**

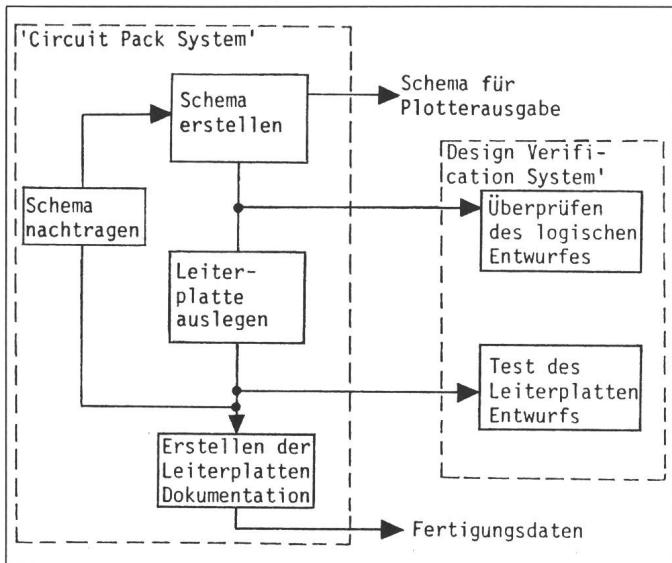

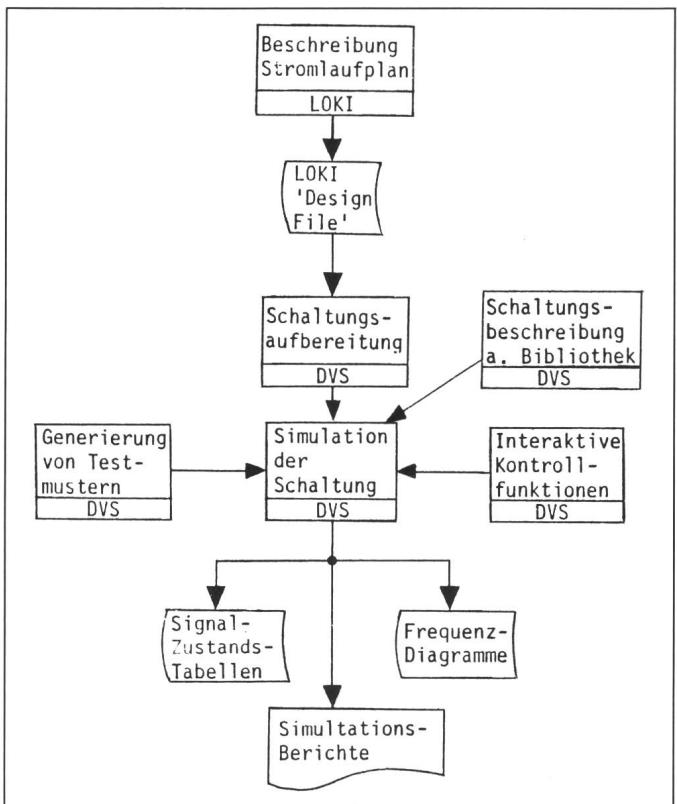

Die Figur 1 zeigt die verschiedenen Phasen und Hauptaktivitäten bei der Entwicklung einer Leiterplatte und deren Eingliederung in die CBDS-Systematik. Mit dem logischen Entwurf beginnt die Arbeit. Am interaktiven grafischen Arbeitsplatz zeichnet der Ingenieur speditiv ein genaues Schema der Logik. Die gespeicherten Daten lassen sich auf einem Plotter ausdrucken. Sie dienen als Grundlage für den physischen Layout, in dem die logischen Elemente den physischen Komponenten zugeordnet werden. Die nötigen Zusammenhänge sind in der Komponenten-Datenbank spezifiziert. Die Komponenten können nach verschiedenen Optimierungskriterien platziert werden. Während dieser Phase überprüft das Programm stets die Einhaltung vorgegebener Regeln.

Das Konzept von CBDS bedingt und sichert, dass der physikalische

### **Adresse der Autoren**

H. Senn, dipl. Ing. ETH, und P. Bollinger, El.-Ing. HTL, IBM Schweiz, 8048 Zürich.

Fig. 1

Die Phasen des

Leiterplattenentwurfs

mit CBDS 2

Layout zwingend mit dem Logik-Schema übereinstimmt. Änderungen am physischen Layout werden im Schema nachgeführt. Das Design-File ist die einzige massgebende Produktdokumentation und dient der Erstellung der Fertigungsunterlagen, d.h. der Datensätze für Photoplotterausgabe, Hardcopyplots, Stücklisten, NC-Bohranweisungen usw.

Mit dem unabhängigen Design Verification System können digitale Schaltungen simuliert und automatisch Testmuster generiert werden. Die Worst-case-Simulation deckt kritische Schaltungsteile bereits in der Designphase auf und ersetzt weitgehend den Bau von Prototypen.

3. das Subsystem FABRIC zur Generierung der Fertigungsdaten, welches, basierend auf den fertigen Entwurfsdaten, u.a. Stücklisten, Steuerdaten für Photoplotter und NC-Bohrautomaten erstellt,

4. die Komponenten-Datenbank (CDB) und die Programme zu deren Pflege (Ändern, Zufügen, Rearrängieren). Sie stellen ein umfassendes Subsystem dar, welches insbesondere eine hohe Standardisierung und technisch gleichbleibende Qualitäten sichern hilft.

### 3.1 Loki-Editor

Bei der grafisch interaktiven Eingabe des Schaltplans werden zunächst

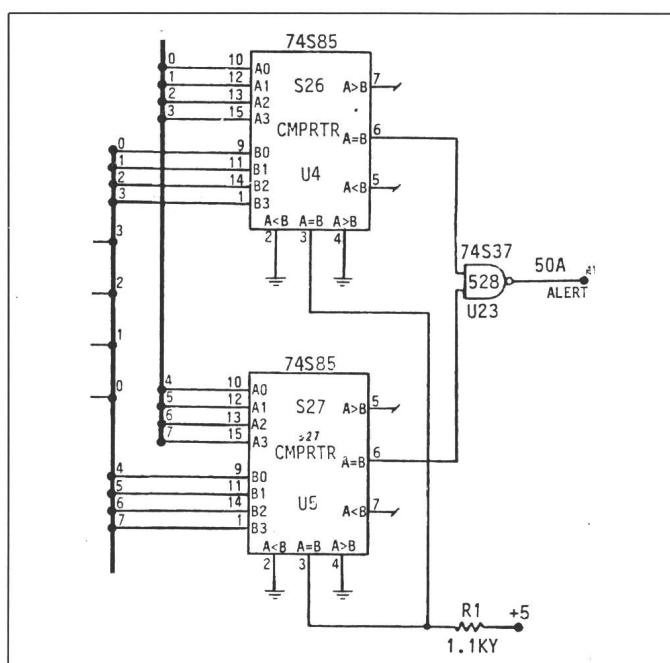

mit dem Loki-Editor Symbole aus der Bauteile-Datenbank aufgerufen und auf frei definierbaren Schaltungsplänen platziert. Ein Entwurf kann bis zu 100 Schemablättter umfassen. Dann werden die einzelnen Anschlusspunkte miteinander verbunden, entweder in einem Vorgang zeichnerisch und elektrisch oder nur elektrisch und bei einem zweiten automatischen Vorgang auch zeichnerisch. Das System vergibt dabei selbständig Signalnamen für die eingegebenen Verbindungen und prüft, ob die gewählten Leitungsverbindungen zulässig sind. Frei platzierbare Kommentare, Leitungsbündelungen (Busse) und Querverweise bei Netzen, die Formulargrenzen überschreiten, verbessern die Lesbarkeit der Schaltbilder. Eine abschliessende automatische Prüfung der gesamten Schaltung findet die letzten formalen Fehler. Das Design-File übergibt den kompletten Schaltungsentwurf an das Modul zur Plazierung und Entflechtung (Fig. 2).

### 3.2 SPRIG-Modul

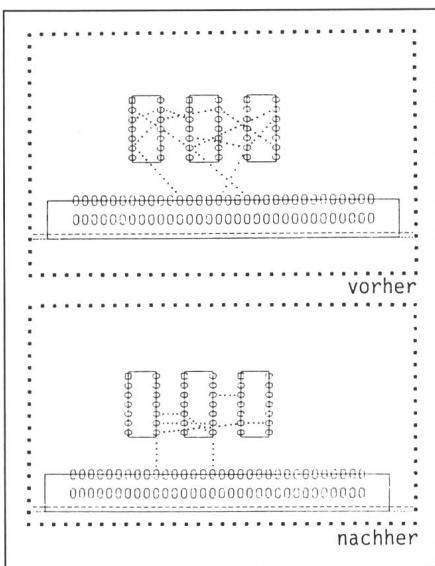

Das SPRIG-Modul (Fig. 3) hat manuell-interaktive, automatisch ablauende und implizite Funktionen, z.B. zur Überprüfung von Sicherheitsabständen, Bauteilüberlappungen, offenen Leiterbahnen usw. Die folgenden automatischen Funktionen werden nach wählbaren Kriterien optimiert:

- das Zuordnen der Gatter zu den Komponenten (Assignment),

## 3. Das Circuit Pack System (CPS)

Dieses Schlüsselpaket umfasst vier Subsysteme. Jedes dient einer Sparte im PCB-Entwurf und in der PCB-Fertigung:

1. das Subsystem für Schema- oder Stromlaufplan (LOKI), eigentlich ein interaktiver grafischer Editor zur Erfassung oder Erstellung von Schemata sowie zur Definition von Schaltungssymbolen für die Komponentendatenbank,

2. das Subsystem für den physischen Layout (SPRIG), zur Plazierung der Bauteile auf der Schaltplatte (Board) und der Entflechtung ihrer Verbindungen (Routing) dient, beides manuell-interaktiv oder automatisch, wobei unterschiedliche Entflechungsstrategien eine weitgehend automatische Leiterbahnverlegung, selbst bei komplexen Schaltkarten, erlauben,

Fig. 2

Schemasymbole

Fig. 3 Optimierung von Gatter- und Pinzuordnung

- das Plazieren der Bauteile (Placement),

- die Optimierung der Gatter- und Anschlussbelegung (Optimizing),

- das Entflechten der Leitungen (Routing),

- die Nachbearbeitung nach fabrikatorischen Gesichtspunkten (TIDY).

Im vorgezeigten Ablauf werden automatisch alle relevanten Prüfungen vorgenommen. Das Einschnüren (Neck-down) von Leiterbahnen kann manuell oder automatisch erfolgen oder unterdrückt werden. Bauteile können durch andere ersetzt oder ganz entfernt, neue Schaltungsteile hinzugefügt und alle Änderungen automatisch in den Schaltplan übernommen werden. Automatische Funktionen erlauben abschliessend, überflüssige Durchkontakte zu beseitigen, Ecken abzuschäragen, Treppenstufen zu entfernen, Sicherheitsabstände zu vergrössern, um damit die Produktionsmöglichkeiten der Leiterplatte zu verbessern.

### 3.3 FABRIC-Modul

Das FABRIC-Modul für die Erstellung von Fertigungsdaten liest und prüft den vom Entflechtungsmodul komplettierten Design-Datensatz. Dann lassen sich unter anderem folgende Fertigungsunterlagen erzeugen:

- Steuerdaten für Fotoplotter wie Masken für die einzelnen Leiterbahn-ebenen, Lötstopmasken, Siebdruckmasken, Bohrkontrollfilme, Bestückungsplan,

- Lochstreifen zur Bohrmaschinensteuerung,

- Daten für Bestückungsautomaten,

- Liste unbenutzter Gatter,

- Verbindungsliste,

- Stückliste.

Die drei vorgenannten Hauptmodule können auch im Stapelbetrieb verwendet werden (Playback-Funktion). Sinnvoll ist dies, wenn langwierige und komplexe Entflechtungen gemacht werden sollen. Aus allen drei Modulen lassen sich beliebige Zeichnungen erzeugen, die dann über die mitgelieferten Plot-Programme ausgegeben werden.

### 3.4 Komponentendatenbank (CDB)

Alle Programme greifen auf die zentrale Bauteile-Datenbank zu. Diese ist hierarchisch strukturiert und erlaubt einzelnen Benutzern, dann jedem Projekt und schliesslich unternehmensweit gültige Bauteile zu definieren. Dadurch wird eine strenge Kontrolle über die verwendeten Bauteile und deren verschiedene Versionen und auch über deren Darstellung auf dem Schaltplan sowie auf der fertigen Schaltkarte möglich. Ein firmenspezifischer Standard lässt sich einführen, der von den Benutzern verwendet werden muss. Die Einträge in der Datenbank zu einem Bauteil können umfassen:

- die zeichnerische Darstellung auf dem Schaltbild und auf der Leiterplatte,

- die Zuweisung von Gattern zu Komponenten,

- die logische Verknüpfung der Anschlusspunkte,

- die Information für automatische Bestückung,

- die physikalischen Masse,

- die elektrischen Werte,

- die Lieferant(en) usw.

Der Informationsumfang der Datenbank lässt sich, falls notwendig, durch eine Änderung der Datenbankdefinition den Kundenwünschen anpassen; gewisse zeichnerische, logische und physikalische Einträge sind zwingend notwendig. Über eine Programmschnittstelle (CALL-Ebene) kann man mit selbstgeschriebenen Programmen (Fortran, PL/1 usw.) auf die Datenbank zugreifen, um eigene zusätzliche Funktionen auszuführen.

## 4. Das Design Verification System (DVS)

Das DVS ergänzt das CPS als selbstständiges Anwendungspaket mit digitaler Logiksimulation und der Erzeugung von Testdaten für Prüfautomaten. Die Schaltungsbeschreibung kann entweder im DVS erstellt oder direkt von der Schaltplanerstellung im CPS übernommen werden. Ziel der Simulation ist in erster Linie, Entwicklungsfehler frühzeitig, d.h. in der Designphase zu entdecken und zu beseitigen. Damit kann weitgehend auf den Bau von Prototypen verzichtet werden. In der Folge lassen sich komplexere, kompaktere und technologisch schwierigere Schaltkarten als bisher bauen, die in manchen Teilen nach herkömmlicher Art als Prototyp nicht durchgemessen werden könnten.

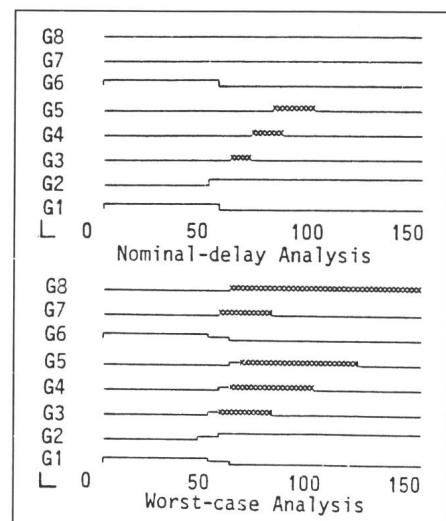

Zur Simulation gibt man Eingangssignalbelegungen vor, die dann durch das Simulationsmodell verarbeitet werden. Es lassen sich an jedem Gatterausgang die berechneten Signalwerte ausgeben, so dass ein fehlerhaft erkannter Wert zurückverfolgt und die Schaltung korrigiert werden kann. Die Signalzustände lassen sich als Wertekurve im zeitlichen Verlauf ausdrücken, auf Papier zeichnen (Hardcopy) oder grafisch auf dem Bildschirm zeigen. Interaktiv können Eingangswerte verändert, die Simulation erneut gestartet und die neuen mit den alten Ergebnissen verglichen werden (Fig. 4 und 5).

Das zweite Ziel, das sich mit DVS erreichen lässt, ist die Erzeugung von Testdaten, mit denen man Schaltkarten auf Fertigungsmängel untersuchen kann. Es werden dabei Testpunkte vorgegeben, und das System generiert ein Testmuster mit maximaler Prüftiefe. Dabei wird angezeigt, welche Fehler mit dem entsprechenden Test nicht erfassbar sind. Im folgenden ein paar weitere Kurzinformationen zum DVS:

Fig. 4 Taktdiagramm

Fig. 5

Der Simulationsprozess

Fig. 6 IBM 5080 Grafik-Arbeitsstation

- bis 32 000 Gatter pro Design,

- 6 logische Statusangaben (ein, aus, unbekannt, hochimpedant, steigend, fallend),

- frei definierbare Zeitunterteilung (Standard: 0,1 ns),

- bis 1000 parallele Fehlermöglichkeiten.

ten Auflösungsvermögen, dynamische Menüsteuerung via Bildschirm, unterstützt mit Puck/Tablett zur Lokalisierung und mit alphanumerischer und Funktionstastatur zur Daten- oder Parametereingabe. Ein separater Grafikprozessor pro Arbeitsstation offeriert hohe lokale Intelligenz und Speicherfähigkeit. Die IBM-5080-Arbeitsstation (Fig. 6) stellt heute in vielen Beziehungen die fortschrittlichste Lösung auf dem Markt dar. Sie offeriert neben einem hohen Bedienungskomfort und bester Ergonomie in Zusammenarbeit mit der leistungsfähigen Rechnerhard- und -software sehr kurze Antwortzeiten und sichert eine hohe Produktivität.

## 5. Arbeitsplatz und Computersystem

Für den gesamten geschilderten Ablauf steht dem Ingenieur eine sehr leistungsfähige neue grafische Arbeitsstation zur Verfügung: ein 19"-Farbbildschirm mit 1024×1024 Bildpunk-

Die CBDS-Anwendungsprogramme laufen auf IBM-Rechnern der 43XX-Serie, der IBM-30XX- und IBM/370-Serie. Diese Rechner sind leicht individuellen Bedürfnissen anpassbar und bieten insbesondere die Möglichkeit, die Anzahl Arbeitsplätze schnell und problemlos auf fast jede gewünschte Zahl zu erhöhen. Ebenso kann auf dem gleichen Rechner gleichzeitig z.B. CAD-Mechanik oder eine andere CAD/CAM-Software gefahren werden. Integrationsprobleme sind weitgehend unbekannt. Die neueste aktuelle Version trägt die Bezeichnung *Release 2.4*, womit angedeutet ist, dass das Paket eine kontinuierliche Erweiterung und Anpassung offeriert. So sind auch Multilayers, Surface mounted Devices, Multiwire-Technik oder Hybridschaltungen keine Hindernisse für eine optimale computermässige Bearbeitung. Es ist zu hoffen, dass der in den USA schon sehr verbreitete Einsatz dieser und anderer Lösungen im CAD/CAM-Bereich auch in Europa breit Fuss fassen kann.