|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 75 (1984)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 11                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | Circuit horloger à structure de processeur                                                                                                                                                                                |

| <b>Autor:</b>       | Perotto, J. F.                                                                                                                                                                                                            |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-904416">https://doi.org/10.5169/seals-904416</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 18.02.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Circuit horloger à structure de processeur

J.F. Perotto

La technologie microélectronique permet actuellement d'intégrer des milliers de fonctions logiques sur une seule puce de silicium. Parallèlement à l'évolution technologique, de nouvelles méthodes de conception de circuits, issues de la technique des ordinateurs et des méthodes VLSI, systématisent l'organisation des éléments du circuit.

Cet article décrit la conception d'un circuit horloger CMOS, réalisé grâce à ces apports technologiques et conceptuels. Il s'agit, en fait, d'un micro-ordinateur spécialisé, muni de périphériques propres à l'application horlogère, dont le fonctionnement est régi par un programme placé dans sa mémoire ROM. Ce circuit, entièrement conçu et intégré au CEH, comporte plus de 20 000 transistors sur une surface de 40 mm<sup>2</sup> et consomme moins de 0,5 µA. Il a été réalisé sous mandat pour la maison ETA AG, Grenchen.

Dank Mikroelektronik können heute Tausende von logischen Funktionen auf einem einzigen Siliziumchip untergebracht werden. Zu dieser Technologie sind auch neue Methoden für den Entwurf von Schaltungen entwickelt worden, bei denen die Verteilung der Elemente der Schaltung mittels Computertechnik und VLSI-Methoden systematisiert wurde.

Der Aufsatz beschreibt den Entwurf einer mit diesen Techniken entwickelten CMOS-Schaltung. Es handelt sich um einen speziellen Mikrocomputer mit besonderen peripheren Elementen für die Uhrenanwendung, gesteuert durch ein in einem ROM untergebrachten Programm. Im Auftrag von ETA AG, Grenchen, wurde die Schaltung vollständig im CEH entworfen und integriert. Sie umfasst über 20 000 Transistoren auf einer Fläche von 40 mm<sup>2</sup> und nimmt weniger als 0,5 µA auf.

## Adresse de l'auteur

J.F. Perotto, Collaborateur scientifique du département «Systèmes», CEH Centre Electronique Horloger S.A., Maladière 71, 2000 Neuchâtel.

## 1. Introduction

Lorsque la complexité des fonctions demandées à un circuit intégré dépasse un certain seuil, il devient pratiquement impossible de le réaliser en logique câblée. Le recours à la logique programmée apparaît être une nécessité et présente de nombreux avantages: conception systématisée, utilisation intensive de tableaux programmables assurant une haute densité d'intégration, fonction du circuit régie par un programme dont la mise au point est aisée, etc.

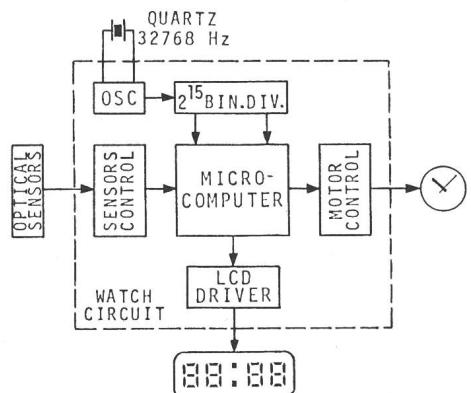

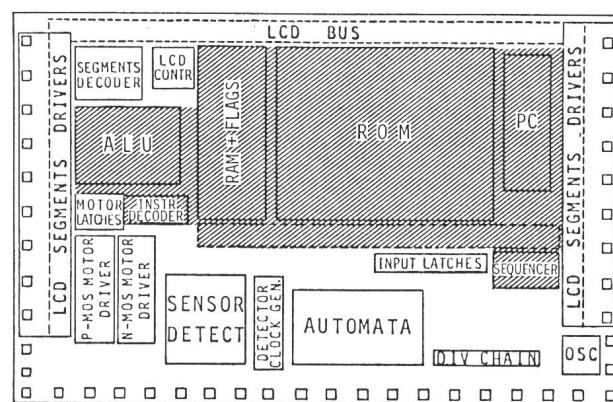

Cet article présente la conception d'un circuit horloger réalisé en logique programmée et, plus particulièrement, le micro-ordinateur qui en constitue l'élément central. La figure 1 représente très grossièrement ce circuit. On distingue le micro-ordinateur, les blocs spécifiques à la commande des éléments externes (cellule d'affichage LCD, moteur pas à pas et senseur optique) ainsi que la base de temps à quartz générant le signal d'horloge du processeur et la base de temps à 1 Hz.

## 2. Organisation du circuit

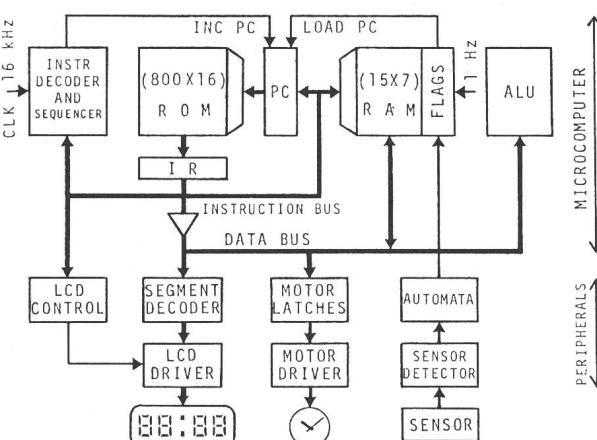

Le circuit complet est donc constitué de deux parties distinctes: le micro-ordinateur et les éléments périphériques

Fig. 1 Circuit horloger à structure de processeur

propres à l'application horlogère. La figure 2 représente de façon plus détaillée la structure interne du circuit.

### 2.1 Structure du micro-ordinateur

Il s'agit d'une machine du type Harvard dans laquelle instructions et données résident dans des mémoires distinctes. Le programme d'application est contenu dans une mémoire morte (ROM), il assure le calcul de l'heure, la gestion des modes d'affichage, la correction des informations horaires et la commande du moteur pas à pas. Les informations horaires et de conduite

Fig. 2

Schéma-bloc du circuit complet

|    |   |                          |   |      |   |                 |           |            |                 |            |

|----|---|--------------------------|---|------|---|-----------------|-----------|------------|-----------------|------------|

| 15 | 0 | branch address (10 bits) | P | FLAG | 0 | JPZ, JPNZ       |           |            |                 |            |

| 2  | 0 | branch address (10 bits) | 0 | 1    | 1 | JMP             |           |            |                 |            |

| 3  | 1 | 0                        | 0 | 1    | H | data (7bits)    | RAM       | RAM ← data |                 |            |

| 4  | 1 | 0                        | 0 | 0    | H | 0 0 0 0 0 0 0 0 | RAM       | RAM ← AC   |                 |            |

| 5  | 1 | 1                        | 1 | 0    | H | 0 0 0 0 0 0 0   | OP        | RAM        | AC ← (OP)RAM    |            |

| 6  | 1 | 1                        | 0 | 1    | H | data(7bits)     | 0 0 0 0   | AC         | = data          |            |

| 7  | 1 | 0                        | 1 | 1    | H | 0 0 0 0 0 0 0   | SR        | FLAG       | SR FLAGS        |            |

| 8  | 1 | 1                        | 0 | 0    | H | 0 0 0           | R         | M1 MC M2   | 0 0 0 0         | MOTOR      |

|    |   |                          |   |      |   | moteur run      |           |            | commande moteur |            |

| 9  | 1 | 0                        | 1 | 0    | H | 0 0 0 0         | HZ ED     | 0          | 0 0 0 0         | RESET      |

|    |   |                          |   |      |   | base de temps   |           |            | entrée données  |            |

| 10 | 1 | 0                        | 1 | 0    | H | 0 0 0 0 0 0 0 0 | 0 0 0 0   | NOP        |                 |            |

| 11 | 1 | 1                        | 1 | 1    | H | 0 SUP COL       | FLASH G D | DIGIT      | RAM             | NUM OUTPUT |

| 12 | 1 | 1                        | 1 | 1    | H | 1 SUP COL       | FLASH G D | DIGIT      | RAM             | ALPHA OUT  |

Fig. 3

Répertoire d'instructions du processeur

dynamique de la machine entre chaque calcul de l'heure, soit pendant plus de 99% du temps.

Le champ de droite, formé de quatre bits, pointe toujours une position RAM ou un booléen de décision de branchement (FLAG).

/ Les autres champs sont propres à chaque instruction, ils spécifient des données immédiates, les opérations ALU et les commandes de l'affichage LCD ou du moteur.

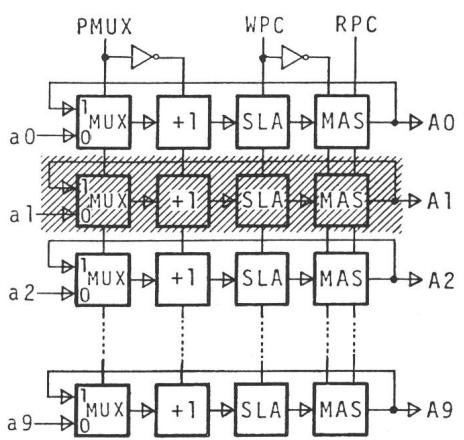

### 3.2 Mémoire ROM et compteur de programme

La mémoire ROM contenant le programme d'application est adressée par le compteur de programme (PC). Ce dernier est réalisé au moyen de 10 tranches de 1 bit comme le montre la figure 4. Chaque tranche est composée d'un multiplexeur d'entrée sélectionnant la source d'adresse (adresse actuelle ou de branchement), suivie d'un demi-additionneur. La sortie de l'additionneur est mémorisée dans une cellule «master-slave» (MAS-SLA) dont la sortie constitue l'adressage de la ROM.

Cette structure de PC présente l'avantage d'être facilement adaptable à diverses tailles de ROM et peut contenir une pile d'adresses de retour câblée, par simple adjonction d'étages MAS supplémentaires.

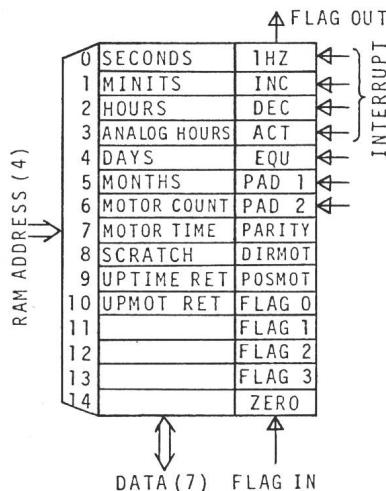

### 3.3 Mémoire des données et booléens de décision logique

Toutes les données vives du processeur résident dans une mémoire RAM de 15 mots et une banque de 15 booléens (FLAGS) dont l'organisation est représentée à la figure 5.

Les données vives sont de trois types: les informations horaires, les compteurs internes et les pointeurs

Fig. 4 Compteur de programme réalisé en tranches de 1 bit

du processus résident dans une mémoire vive (RAM), associée à un ensemble de variables booléennes (FLAGS) utilisées comme éléments de décision dans le programme. Finalement, le traitement de l'information est réalisé dans l'unité arithmétique (ALU) sur un format de 7 bits codé BCD. Les transferts d'information sont commandés par le séquenceur associé au décodeur d'instructions. Tous ces éléments sont reliés entre eux par deux bus distincts: le bus d'instructions qui véhicule les divers champs constitutifs de l'instruction et le bus de données assurant les transferts d'information dans le processeur et vers les périphériques.

### 2.2 Circuits périphériques

Le micro-ordinateur opère sur des données binaires représentatives de l'information horaire. Pour être compréhensibles, elles doivent être transformées et affichées, ce sont les périphériques qui assurent ce lien entre le micro-ordinateur et les éléments d'affichage et de commande de la montre.

Ces circuits périphériques sont tout à fait conventionnels, mis à part le dispositif d'entrée de données optique réalisé au moyen d'un automate spécialisé [2], transformant des séquences de manipulation de photo-détecteurs en ordres de commandes de la montre.

La suite de cet article décrira en détails la conception du micro-ordinar-

teur constituant la partie originale de ce circuit.

## 3. Architecture du processeur

L'architecture du processeur est l'ensemble de ses ressources internes, les chemins de données qui les interconnectent et son jeu d'instructions. La figure 2 représente les deux premiers éléments de l'architecture précédemment décrits et la figure 3 donne le répertoire d'instructions du processeur. Ce dernier appelle quelques commentaires.

### 3.1 Répertoire d'instructions

Les 12 instructions du processeur ont un format fixe de 16 bits répartis en divers champs. Le code opératoire de chaque instruction occupe le champ de gauche, il est formé d'un seul bit pour les instructions de branchement (1 et 2) et de quatre bits pour les autres instructions (3 à 12).

Le champ H, commun à toutes ces instructions, est un booléen capable de stopper le processeur à la fin de l'exécution de l'instruction qui le contient sous sa forme logique active (état 1). Cette caractéristique n'existe pas dans les processeurs à usages généraux du commerce, elle est par contre fondamentale dans notre cas puisqu'elle permet de supprimer la consommation

Fig. 5 Organisation de la RAM et de la banque de booléens

d'adresse de retour de sous-routines. L'ensemble de ces données réside dans 11 positions RAM.

La banque de booléens est adressée par le même décodeur que la RAM. Ces variables sont réparties en deux catégories: les sept premières ont une commande d'écriture câblée, c'est-à-dire que leur état est défini et imposé par un élément du processeur ou un périphérique (ALU, pad,...) tandis que les autres sont purement logicielles, leur état est imposé par une instruction. Le dernier flag (ZERO) est un booléen câblé à l'état logique zéro, il est utilisé par l'instruction de branchement inconditionnel.

La sortie de la banque de booléens constitue la variable de décision lors des branchements conditionnels.

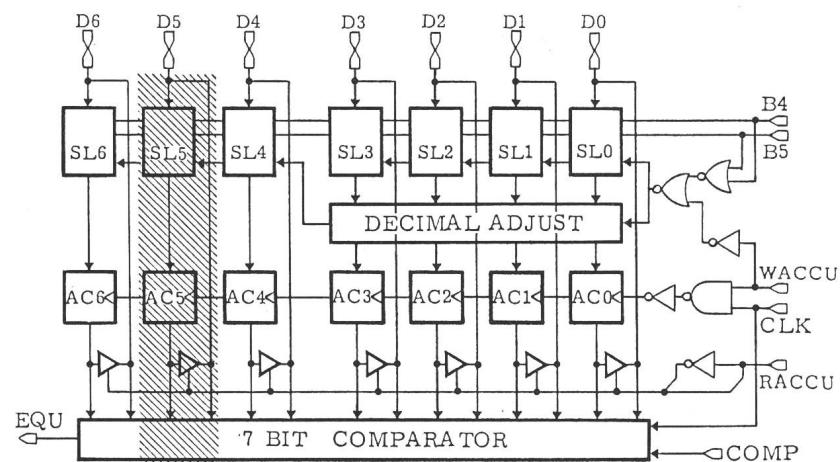

### 3.4 Unité arithmétique

Le dernier élément faisant partie de l'architecture du processeur est l'ALU dont le schéma est représenté à la figure 6. Opérant sur des nombres de 7 bits codés en double BCD (modulo 79), elle est réalisée par 7 tranches de 1 bit formées d'un opérateur arithmétique SL, d'un accumulateur AC et du comparateur. Sa structure étant purement binaire, on lui incorpore un étage d'ajustage décimal câblé qui la transforme en ALU décimale.

Les opérations réalisées par cette ALU sont limitées à quatre: incrémentation, décrémentation, comparaison et transparence (entrée directement transmise à la sortie). Le choix de l'opérateur est effectué par les deux lignes de commande B4, B5.

La sortie EQU du comparateur commande directement le booléen EQU et permet de réaliser un branche-

Fig. 6 Unité arithmétique en format double BCD (modulo 79)

ment conditionnel au résultat d'une comparaison arithmétique entre le contenu de l'accumulateur et le champ «data» de l'instruction de comparaison (6).

## 4. Séquencement du processeur

### 4.1 Le séquenceur [3]

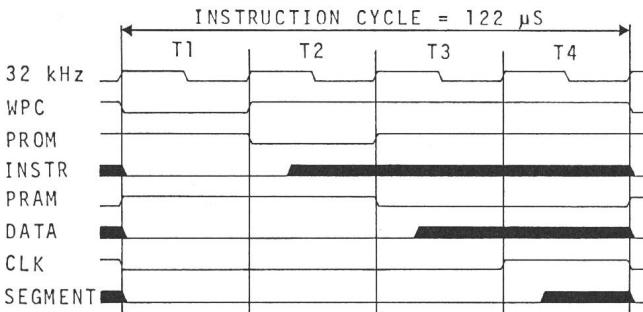

L'exécution de chaque instruction de la machine nécessite l'ouverture de chemins de données entre diverses ressources internes et la génération de signaux de validation des données. Ces opérations sont réalisées par le séquenceur associé au décodeur d'instructions. Pour des raisons de simplicité conceptuelle, chaque instruction est séquencée selon quatre phases fixes: T1, T2, T3 et T4 comme le montre la figure 7.

La phase T1 est statique (elle peut avoir une durée quelconque) et constitue la phase d'attente lorsque le processeur est en état HALT. Pendant cette phase, tous les éléments dynamiques sont en état de précharge.

La phase T2 permet de lire la mémoire ROM et de transférer l'instruction à exécuter dans le registre d'instruction. Cette phase constitue la par-

Fig. 7 Signaux de séquencement du processeur

tie «fetch» de l'exécution de l'instruction.

Les phases T3 et T4 sont destinées à la partie «execute» de l'exécution. Pendant T3, une donnée est placée sur le «data bus» et T4 valide la donnée dans la ressource réceptrice au moyen du signal CLK.

Outre les signaux issus du décodeur d'instruction, le séquencement est assuré par quatre signaux seulement: WPC qui incrémente ou charge le compteur de programme, PROM et PRAM qui préchargent la ROM et la RAM ainsi que CLK qui valide l'information dans la ressource réceptrice.

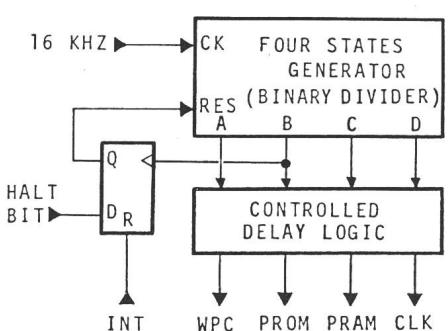

La figure 8 représente de façon schématisée le séquenceur du processeur. Il

Fig. 8 Schéma de principe du séquenceur

est composé d'un diviseur binaire dont les quatre sorties A, B, C, D sont mises en forme par un circuit combinatoire fournissant les signaux de séquencement.

#### 4.2 Système d'interruption

Nous avons vu que le processeur peut être mis dans un état HALT par toute instruction dont le bit du champ H est à l'état 1. La détection de cette demande d'arrêt est assurée par la bascule D du séquenceur qui maintient le diviseur binaire dans l'état correspondant à la phase statique T1.

La sortie de cet état HALT est assurée par la ligne d'interruption INT qui est la somme logique des quatre premiers booléens de la banque (fig. 5). Il ne s'agit donc pas ici d'une interruption au sens classique mais de l'interruption d'un état HALT.

Ainsi, lorsque le processeur est en HALT, l'activation d'un quelconque des booléens d'interruption lui fait reprendre l'exécution du programme. La base de temps à 1 Hz et les trois entrées de commande de la montre constituent la source d'interruption.

#### 4.3 Décodeur d'instruction

Cet élément n'appelle que peu de commentaires pour la présente réalisation. Il s'agit d'un simple système logique combinatoire à quatre entrées (les 4 bits du code opératoire) et dix sorties (les signaux d'ouverture de chemins de données). A chaque état d'entrée du décodeur d'instructions correspondra une configuration des sorties propre à l'exécution de l'instruction.

### 5. Logiciel d'application

L'architecture du micro-ordinateur est relativement universelle; c'est le logiciel d'application, résidant en ROM, qui donnera sa «personnalité» au circuit. Dans le cas présent, la principale restriction à l'universalité du micro-ordinateur tient à l'ALU dont les possibilités sont limitées. Il serait, par exemple, très difficile de réaliser une opération d'addition arithmétique avec cette machine (bien qu'elle soit possible au prix d'une durée d'exécution certainement prohibitive). Si l'on s'en tient aux applications purement horlogères, ce micro-ordinateur peut être facilement reprogrammé pour répondre à un cahier des charges différent.

Le programme d'application, pour lequel sa conception a été optimisée, a

Quelques caractéristiques conceptuelles du circuit

Tableau I

| Caractéristiques de dessin du circuit complet  |                                        |

|------------------------------------------------|----------------------------------------|

| Technologie                                    | C-MOS,<br>6 µm Layout Rules            |

| Surface de la puce                             | 8,17 × 5,00 =<br>40,85 mm <sup>2</sup> |

| Nombre de transistors                          | 20 230 MOS                             |

| Densité d'électronique                         | 495 MOS/mm <sup>2</sup>                |

| Régularité design                              | 18,7                                   |

| Caractéristiques de dessin du micro-ordinateur |                                        |

| Surface                                        | 15,90 mm <sup>2</sup>                  |

| Nombre de transistors                          | 16 313 MOS                             |

| Densité d'électronique                         | 1026 MOS/mm <sup>2</sup>               |

| Régularité design                              | 41,2                                   |

une taille de 650 instructions réparties en trois groupes: gestion des modes de la montre (426 instructions), calcul de l'heure (104 instructions) et commande du moteur pas à pas (120 instructions). A cela vient s'ajouter un programme d'auto-test du processeur destiné à faciliter le test en production du circuit; ce programme d'auto-test occupe 110 instructions supplémentaires.

Ainsi, l'application horlogère et l'auto-test du circuit constituent un programme de 760 instructions placées dans la mémoire ROM dont la taille a été fixée à 800 instructions.

### 6. Caractéristiques du circuit

#### 6.1 Conception

Il est intéressant de connaître quelques caractéristiques conceptuelles d'un tel circuit. Le tableau I résume les principales valeurs caractérisant le circuit complet et le micro-ordinateur seul aux fins de comparaisons.

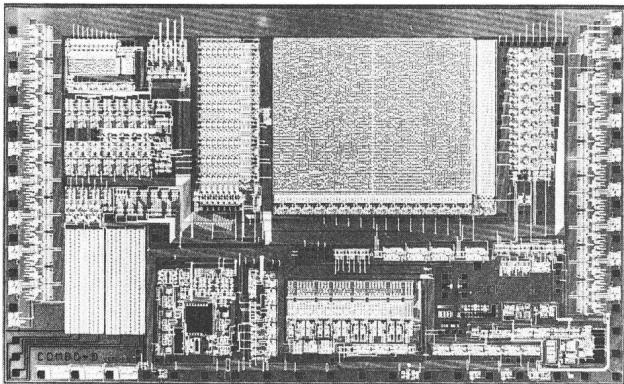

Fig. 9

Schéma d'implantation des éléments du circuit complet

Caractéristiques électriques du circuit

Tableau II

| Paramètre              | Min  | Typ  | Max  | Unit |

|------------------------|------|------|------|------|

| Tension d'alimentation | 1,00 | 1,55 | 2,50 | V    |

| Consommation           | 400  |      |      | nA   |

| Fréquence horloge      | 4    | 16   | 200  | kHz  |

| Température            | -10  | 28   | 100  | °C   |

On remarque en particulier la haute densité d'électronique atteinte avec le micro-ordinateur (1026 MOS/mm<sup>2</sup>) alors que le reste du circuit présente une densité de 178 MOS/mm<sup>2</sup>. Il en va de même pour la régularité de dessin (rapport du nombre de MOS total au nombre de MOS effectivement dessinés par le concepteur) qui est de 41,2 pour le micro-ordinateur et seulement de 5,5 pour le reste du circuit.

Ces valeurs sont d'une grande importance, car d'elles dépendent la taille et le temps de dessin du circuit, donc finalement les coûts de développement et de fabrication du produit.

#### 6.2 Caractéristiques électriques

Le tableau II donne quelques caractéristiques électriques importantes du circuit complet. La consommation typique de 400 nA est liée à l'application spécifique de ce circuit.

En fonctionnement permanent, le micro-ordinateur présente une consommation dynamique de 200 nA/kHz (la fréquence est celle de l'horloge du processeur). Ainsi, pour une application sans états HALT, la consommation peut atteindre 40 µA sous une fréquence d'horloge de 200 kHz.

#### 6.3 Topologie

La disposition des divers éléments du circuit est représentée à la figure 9.

Fig. 10

Microphotographie du circuit

Toute la partie hachurée constitue le micro-ordinateur, la surface restante étant attribuée à l'application. La connexion de la puce avec le circuit

imprimé s'effectue par les 42 pads de contact à la périphérie du circuit. La figure 10 est une microphotographie du circuit complet.

## 7. Conclusions

Cette réalisation a montré la faisabilité d'un circuit horloger complexe organisé selon une architecture de processeur et consommant 0,4 µA sous une tension d'alimentation de 1,5 V. La versatilité du micro-ordinateur permet, moyennant une réadaptation du jeu d'instructions et des fonctions de l'unité arithmétique, de couvrir une large gamme d'applications, horlogères ou autres.

## Bibliographie

- [1] H.G. Cragon: The elements of single-chip microcomputer architecture. IEEE Computer Magazine 13(1980)10, p. 27...41.

- [2] C. Clare: Designing logic systems using state machines. New York, McGraw-Hill, 1973.

- [3] C. Piguet e. a.: Le séquenceur d'un microprocesseur. Bull. ASE/UCS 70(1979)3, p. 126...132.