**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

Herausgeber: Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 75 (1984)

Heft: 7

Artikel: Ein Telefonie-Mikrocomputer

Autor: Müller, P. / Lenggenhager, M.

**DOI:** https://doi.org/10.5169/seals-904385

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF: 28.11.2025**

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Ein Telefonie-Mikrocomputer

P. Müller, M. Lenggenhager

Der 8-bit-CMOS-Einchip-Mikrocomputer 3340, eine Spezialschaltung für die Anwendung in Telefonie-Teilnehmerstationen, wird vorgestellt. Minimaler Stromkonsum sowie die Unterstützung des seriellen Datenverkehrs standen bei der Entwicklung im Vordergrund.

Le type 3340 est un micro-ordinateur 8 bits en technologie CMOS destiné aux stations téléphoniques d'abonnés. Les buts fixés au cours du développement ont été une consommation minimale et l'implantation d'un interface intelligent, indépendant du CPU, pour contrôler la transmission et la réception des données d'un bus-série.

### 1. Einleitung

Einchip-Mikrocomputer bewältigen seit einigen Jahren erfolgreich Aufgaben wie Prozessregelung oder Ablaufsteuerung in komplexen Messeinrichtungen. Auch als zentrales Element in Geräten der Unterhaltungselektronik werden sie immer häufiger verwendet. Die hier beschriebene Schaltung, der 3340, wurde speziell für den Einsatz in künftigen Telefonie-Teilnehmerstationen entworfen. In der Architektur lehnt er sich an den bekannten 8048 an, dessen Instruktionssatz weitestgehend übernommen wurde. Um im Batteriebetrieb möglichst stromsparend arbeiten zu können, wurde der 3340 in einer CMOS-Technologie mit niedrigen Transistorschwellwerten ausgelegt. Zudem können Betriebsarten gewählt werden, die den Stromverbrauch auf ein Minimum absinken lassen.

Eine Teilnehmerstation mit dem 3340 kann in Zukunft mit vielen interessanten Funktionen aufwarten:

- Tastenwahl

- Wahlwiederholung

- Notruf

- Notizbuch

- Kurzwahl

- Gebührenzähler

Parallel zur integrierten Schaltung wurde auch die entsprechende Software entwickelt, die in einer modular aufgebauten Bibliothek zur Verfügung steht.

#### 2. Aufbau

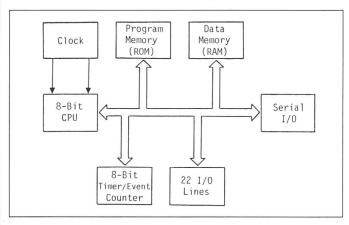

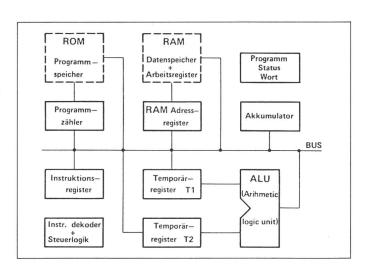

Das Blockdiagramm des 3340 ist in Figur 1 dargestellt. Figur 2 zeigt die

Fig. 1 Blockschaltbild des 3340

Der Aufsatz ist eine überarbeitete Fassung des Vortrages von *P. Müller* vom 3. Dezember 1983 im Rahmen des Kolloquiums über «Moderne Probleme der theoretischen und angewandten Elektrotechnik» an der ETHZ.

#### Adresse der Autoren

Paul Müller, Markus Lenggenhager, Faselec AG, Räffelstrasse 29, 8045 Zürich.

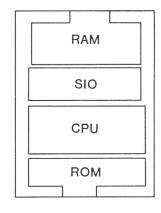

Fig. 2 Anordnung der Baugruppen auf dem Chip

Anordnung auf dem Silizium. Hier soll nur ein kurzer Überblick gegeben werden, die wichtigsten Teile werden anschliessend detaillierter beschrieben.

Der Arbeitsspeicher (RAM) dient zur Datenspeicherung während des Betriebs. Sollten die 224 Byte nicht ausreichen, so können externe RAM hinzugezogen werden, die dann über die serielle Schnittstelle mit dem 3340 kommunizieren.

Das ROM enthält das Anwenderprogramm sowie allenfalls benötigte Datenkonstanten.

Der Instruktionssatz der zentralen Recheneinheit (CPU) umfasst über 80 Befehle, aufbauend auf jenen des 8048.

Die serielle Schnittstelle (SIO) erlaubt den Datenverkehr mit anderen am Zweidraht-Bus angeschlossenen Schaltungen, ohne die CPU zu belasten. Sie enthält einen Controller, der selbst komplizierte Systeme mit mehreren sog. Masters bedienen kann.

Der interne Bus, über welchen alle Transferaktionen ablaufen, ist lediglich 8 bit breit. Es fehlt somit die Aufspaltung in Adress- und Datenbus, wie sie oft bei Mikrocomputern angetroffen wird. Man gewinnt dadurch einiges an Chipfläche, opfert aber Geschwindigkeit, weil die Transferoperationen nur streng sequentiell stattfinden können.

Der Oszillator erlaubt den Anschluss eines Quarzes oder Keramikresonators ohne zusätzliche Komponenten, da Belastungskapazitäten und ein Parallelwiderstand auf dem Chip integriert sind.

Die 20 Ein-/Ausgänge sind als 2½ Ports zu je 8 bit organisiert. Für jeden Pin ist hardwaremässig eine der folgenden Optionen wählbar:

- Standard (100-μA-Stromquelle als Pull-up)

- Open Drain (gestattet die WIRED-AND-Verknüpfung mehrerer Ausgänge)

- Push-Pull (mit einigen mA Ausgangsstrom)

Daneben kann der Anwender noch spezifizieren, welche Pins nach einem Reset hoch oder tief stehen sollen.

Der Timer arbeitet wahlweise in zwei Betriebsarten:

- zählen von Maschinenzyklen (direkt oder über einen Vorteiler ÷32),

- zählen von positiven Flanken eines extern angelegten Signals.

Sein Register kann jederzeit gelesen, aber auch auf einen bestimmten Wert gesetzt werden. Bei einem Überlauf wird das Timer Flag gesetzt und, falls aktiviert, ein Interrupt ausgelöst.

#### 3. Betriebsarten

#### 3.1 Normalmode

Im sog. Normalmode, wo alle Schaltungsteile in Betrieb sind, liegt der Stromverbrauch des 3340 bei ungefähr 600  $\mu$ A (f=3,58 MHz,  $V_{DD}=3$  V). Wird die Rechenleistung für kürzere oder längere Zeit nicht benötigt, lässt sich der Stromverbrauch dank zwei speziellen, softwaremässig anwählbaren Betriebsarten entscheidend reduzieren. Besonders für batteriegespeiste Anwendungen mit langen Wartezeiten zwischen den aktiven Perioden ist dies ein grosser Vorteil.

#### 3.2 Wait Mode

In dieser Betriebsart laufen lediglich noch der Oszillator, der Timer sowie die serielle Schnittstelle. Gegenüber dem Normalmode wird eine Reduzierung des Strombedarfs um 50% erreicht. Reaktiviert werden kann der Computer durch folgende Ereignisse:

- Reset

- externer Interrupt am entsprechenden Pin

- SIO Interrupt (der Computer wurde von irgendeiner anderen Schaltung am seriellen Bus mit seiner Adresse angesprochen)

- Timer Interrupt (Überlauf des Zählers)

Spezielle Bedeutung hat die letzte Möglichkeit, weil damit eine von äusseren Ereignissen unabhängige Rückkehr in den Normalmode erfolgt. Selbst für kurze Wartezeiten im Programm, wo ein konventioneller Prozessor beispielsweise in einer Schleife wartet, bis das Timer Flag gesetzt wird, lohnt es sich also, den stromsparenden Wait Mode zu benutzen.

#### 3.3 Stop Mode

Hier stehen auch Oszillator, Timer und SIO still. Der momentane Zustand der ganzen Schaltung (alle CPU-Register, das RAM und alle I/O-Pins) bleibt jedoch erhalten. Der Stromverbrauch beträgt nur noch 1...2 μA. Eine Rückkehr in den Normalmode ist aber verständlicherweise nur noch durch ein externes Ereignis möglich, entweder durch Reset oder einen externen Interrupt.

# 4. Der Arbeitsspeicher (RAM)

In diesem Abschnitt wird das RAM zuerst aus der Benutzerperspektive betrachtet, dann soll kurz auf den internen Aufbau eingegangen werden.

Entsprechend den Bedürfnissen in den meisten Applikationen sind die 224 RAM-Byte aufgeteilt in zwei Blökke mit je 8 Registern, einen Stack von 16 Byte sowie den eigentlichen Datenspeicher, der die restlichen 192 Byte umfasst.

Die Register werden dazu verwendet, die Operanden der arithmetischen Operationen und logischen Verknüpfungen abzuspeichern. Sie sind direkt adressierbar: MOV A,R3 beispielsweise lädt den Inhalt des Registers R3 in den Akkumulator. Der zweite Registerblock ist besonders bei Sprüngen in Unterprogramme oder Interrupt-Routinen wertvoll, da die Daten aus dem Hauptprogramm unverändert bleiben. Der Stack speichert Rücksprungadresse und Statuswort, wobei bis zu acht verschachtelte Unterprogramme möglich sind.

Der restliche Datenspeicher schliesslich ist nur durch indirekte Adressierung über die Register R0 oder R1 möglich (bzw. über R0' oder R1', falls im zweiten Registerblock gearbeitet wird). Die Instruktion INC ((R0)) z. B. inkrementiert den Inhalt der durch das Register R0 adressierten Speicherzelle. Abgesehen von der indirekten Adressierung sind aber genau die gleichen Instruktionen möglich wie mit den Registern, und zwar ohne mehr Rechenzeit zu beanspruchen.

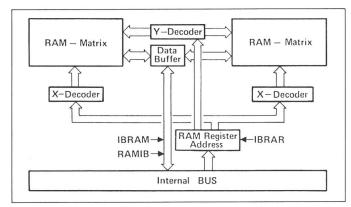

Wie im Blockschaltbild (Fig. 3) dargestellt, ist die Speichermatrix (Memory Array) in zwei Hälften aufgeteilt. Dazwischen befinden sich die Daten-Zwischenspeicher (Data Buffer) wie auch die Y-Adressdecodierung. Da der 3340 mit nur einem Bus auskommt, muss auch die Adresse der anzusteuernden Speicherzelle über diesen Bus gelangen. Sie wird mit dem Kommando IBRAR ins RAM-Adress-Register (RAR) geschrieben. Dieses Register besteht aus Master-Slave-Flipflops, da bei der indirekten Adressierung die RAM-Daten gleich wieder ins RAR übernommen werden, um damit die gewünschte Speicherzelle zu adressie-

Die zwei Steuersignale RAMIB (lese Daten aus dem RAM und schreibe sie auf den Bus) und IBRAM (lese Daten vom Bus und schreibe sie ins RAM) re-

Fig. 3 Blockschaltbild des RAM

$_{\star}v_{DD}$ **→**1/0 N IVSS **▲**Enable

Fig. 4 Einzelne RAM-Zelle

geln den Datenverkehr zwischen RAM und Bus.

Ausser einigen Teilen in der Adressdecodierung arbeitet das RAM statisch. Die einzelne RAM-Zelle besteht aus sechs Transistoren (Fig. 4). Die zwei antiparallel geschalteten Inverter ergeben eine bistabile Charakteristik. Dieser Aufbau ist bezüglich Ruhestrom sehr vorteilhaft (er liegt in der Grössenordnung von pA), jedoch etwas weniger günstig punkto Platzbedarf (48 µm auf 40 µm für ein einzelnes bit der Matrix).

## 5. Der Programmspeicher (ROM)

Das maskenprogrammierte ROM des 3340 umfasst 2048 Byte. Der Anwender liefert sein fertiges Programm auf einer Diskette oder in einem EPROM. Dieser Code wird mittels Programmpaketen speziellen Layout-Information umgearbeitet, die mit der Beschreibung der übrigen Schaltungsteile zusammengefügt wird, um die Masken für die Diffusion herzustellen. Maskenprogrammierte Programmspeicher garantieren dem Software-Entwickler einen weitgehenden Schutz seiner Arbeit, sind aber nur für grössere Stückzahlen wirtschaftlich.

Für den Benutzer sind die ersten paar Byte am Anfang des Adressbe-

reichs von spezieller Bedeutung: im Fall eines Reset (entweder durch ein Signal am entsprechenden Pin oder durch Einschalten der Stromversorgung) oder eines der drei Interrupts wird der Programmzähler auf eine dem eingetretenen Ereignis zugeord-

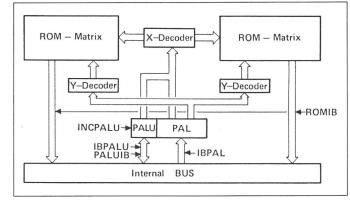

Fig. 5 Blockschaltbild des ROM

nete Adresse gesetzt.

Figur 5 zeigt schematisch den Aufbau des ROM. Erwähnenswert ist die Gestaltung des Adressregisters: Da die Adressierung von 2 K 11 bit erfordert, der Bus aber nur 8 bit breit ist, wird das Adressregister in zwei Teile aufgespalten. PAL (Parallel Address Latch) umfasst die unteren 8 bit der Adresse und ist eine Kopie des Programmzähler-Registers in der CPU. Bei jeder Lese-Operation erhält dieser Teil die neue Adresse via den internen Bus. PALU (Parallel Address Latch Upper) speichert die drei obersten Adressbit. Im Normalfall bleiben diese in ihrem Zustand. Beim Übergang in den nächsthöheren 256-Byte-Block (sog. Page) wird in der CPU das Kommando INCPALU ausgelöst, welches das PALU-Register inkrementiert, ohne den Bus zu belasten. Beim Sprung in ein Unterprogramm muss PALU allerdings über den Bus auf den Stack ins RAM gelangen, wo zusammen mit dem Programmzähler aus der CPU die vollständige Rücksprungadresse abgelegt wird. Ebenfalls über den Bus werden danach PAL und PALU mit der Adresse des Sprungziels neu geladen.

### 6. Zentrale Recheneinheit (CPU)

Die CPU (Central Processing Unit) des 3340 besteht, wie Figur 6 zeigt, aus mehreren Registern, der Steuerlogik sowie der arithmetisch-logischen Einheit. Ein Befehl wird in verschiedenen aufeinanderfolgenden Schritten ausgeführt, wobei praktisch sämtliche Operationen über den Bus ablaufen. Als Beispiel soll die Instruktion MOV A,R3 genauer analysiert werden, durch welche der Inhalt des Registers R3 in den Akkumulator transferiert wird. Diese Instruktion wird in der Maschinensprache mit hexadezimal FB wiedergegeben (binär: 1111 1011). Dabei handelt es sich insofern um einen Spezialfall, als die Registeradresse (011) in der Instruktion selbst enthalten ist.

Fig. 6 **CPU** mit ROM und RAM

#### 6.1 Internes Timing und Maschinenzyklus

Durch Teilung der Oszillatorfrequenz werden drei Taktphasen gewonnen: Φ1 zur Entladung des internen Busses, Φ2 für Bus zu Register Operationen, Φ3 für Register zu Bus Operationen. Diese drei Phasen laufen starr in der Reihenfolge Φ1, Φ3, Φ2 ab und bilden einen Timeslot. Ein Maschinenzyklus ist aus zehn solchen Timeslots zusammengesetzt.

#### 6.2 Ausführung der Instruktion

Im ersten Timeslot eines Maschinenzyklus wird die Instruktion (MOV A,R3) über den Bus ins Instruktionsregister geladen. Gleichzeitig gelangt die Registeradresse (011) ins RAM-Adressregister, wodurch das Arbeitsregister R3 bereits angewählt ist. Anschliessend wird die Instruktion decodiert. In einem zweistufigen PLA (Programmable Logic Array) werden Kommandosignale abgeleitet, die in bestimmten Timeslots aktiv werden. Bei der MOV-A.R3-Instruktion wird durch das Kommando RAMIB im 4. Timeslot der Inhalt des Registers R3 auf den Bus gegeben und anschliessend durch IBACCU in den Akkumulator gelesen. Damit ist der Befehl eigentlich ausgeführt. Um die nächste Instruktion einlesen zu können, muss noch der Stand des Programmzählers erhöht werden. Dazu wird der Inhalt des Programmzählers ins Temporärregister T2 geschrieben. Das Temporärregister T1 wird auf null gesetzt. Nun addiert die ALU die beiden Temporärregister, wobei der ersten Addiererstufe durch das Carry-Flipflop ein Übertrag eingegeben wird. So erhält man den um eins erhöhten Zählerstand, der im 8. Timeslot von der ALU zurück in den Programmzähler geladen wird.

# 7. Die serielle Schnittstelle (SIO)

Der 3340 unterstützt das von Philips spezifizierte I<sup>2</sup>C-Bus-Konzept, bei welchem ein serieller Datentransfer zwischen Mikrocomputer und peripheren Bausteinen über einen Zweidrahtbus möglich ist. Dank diesem Bus kann die Anzahl Verbindungen zwischen den integrierten Schaltungen eines Systems reduziert werden, was einen kostengünstigeren Printlayout erlaubt.

#### 7.1 Das I2C-Bus-Konzept

Für den I<sup>2</sup>C-Bus wurde ein Protokoll definiert, das den Datenfluss zwi-

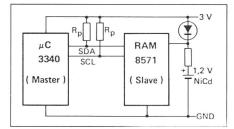

Fig. 7 Anwendungsbeispiel des I2C-Bus

SDA Serial Data Line SCL Serial Clock Line R<sub>p</sub> Pull-up-Widerstand

NiCd Nickel-Cadmium-Backup-Batterie

schen den angeschlossenen Schaltungen festlegt. Jedem Datenbit ist ein Taktpuls (Clock) zugeordnet, so dass zum seriellen Informationsaustausch zwei Leitungen genügen, eine für die Daten (Serial Data Line) und eine für den Clock (Serial Clock Line). Der Clock für die Übertragung wird von «Master» genannten Schaltungen erzeugt. «Slaves» dagegen sind Schaltungen, die auf den Clock eines Masters angewiesen sind. Master und Slave können sowohl als Sender oder Empfänger arbeiten. Jede Schaltung verfügt über ihre eigene spezifische Adresse und reagiert nur auf Protokolle, die diese Adresse enthalten.

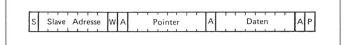

Als Beispiel soll ein Minimalsystem (Fig. 7), bestehend aus einem 3340 (Master) und einem mit serieller Schnittstelle ausgestatteten RAM 8571 (Slave), erläutert werden. Der Mikrocomputer soll über den Bus Daten ins RAM abspeichern. Dazu erzeugt er als erstes eine Startbedingung. Dann wird das RAM als Slave angesprochen, indem seine Adresse gefolgt vom Richtungsbit gesendet wird. Der 8571 quittiert seine Adressierung (Acknowledge). Im nächsten Byte wird die Pointeradresse übertragen, welche festlegt, an welcher Stelle im RAM die folgenden Daten abzuspeichern sind. Anschliessend werden die eigentlichen Datenbytes über den Bus geschickt. Der Slave quittiert jedes empfangene Byte und erhöht automatisch die Pointeradresse, bis eine vom Master erzeugte Stopbedingung die Übertragung abbricht (Fig. 8).

#### 7.2 Aufbau der seriellen Schnittstelle

Die serielle Schnittstelle des 3340 umfasst drei Register, nämlich das Clockkontroll-, das Status- sowie das Datenshiftregister. Diese Register können vom Mikrocomputer mit Move-Instruktionen geschrieben oder gelesen werden.

Das Clockkontrollregister legt die Betriebsart des Busses fest. Seine unteren 5 bits bestimmen die Busfrequenz. Im Bereich von 100 kHz bis 1 kHz können 32 Übertragungsarten angewählt werden. Das 7. bit dient der Erzeugung des Clockpulses für das Acknowledge.

Das Statusregister gibt Auskunft über den Zustand der seriellen Schnittstelle. Es bestimmt, ob der 3340 als Master oder Slave, als Sender oder Empfänger arbeitet. Einzelne seiner Bits dienen als Flags, welche anzeigen, ob der Bus frei ist und ob das zuletzt ausgesendete Byte ungestört am Ziel angekommen ist. Entsprechend gesetzt, erzeugt das Register eine Startoder Stopbedingung. Während einer Übertragung kann es jederzeit abgefragt werden, wodurch eine Kontrolle des Datenverkehrs durch den Mikrocomputer leicht möglich ist.

Das Datenshiftregister übernimmt die Serie/Parallel-Wandlung der Daten. Das laufende Programm wird durch Aktivitäten auf dem Bus nicht unterbrochen. Jedoch wird nach der Übertragung eines vollständigen Bytes ein Interrupt erzeugt. Dadurch ist der 3340 in der Lage, in ein entsprechendes Unterprogramm zu springen, das die Anweisungen enthält, wie die übertragenen Daten weiterverarbeitet werden sollen.

#### 8. Zusammenfassung

Der 3340 wird bei Faselec im 4-µm-Prozess mit selbstjustierenden Kontakten (SAC) hergestellt. Die Abmessungen des Chips betragen 4,6 auf 6,0 mm.

Das Beispiel des 3340 zeigt, wie man durch eine bewusste Konzentration auf Spezialitäten auch in der Schweiz auf dem Gebiet der Mikroelektronik mithalten kann. Die Integration der seriellen Schnittstelle macht die Tendenz zur verteilten Intelligenz deutlich. Mit jedem Fortschritt in der Integrationsdichte können zusätzliche Funktionen auf das Silizium gebracht werden, sowohl analoge wie digitale.

Diese rasch zunehmende Komplexität der elektronischen Systeme bedingt einen Wandel im Denken der betroffenen Berufswelt, der als eigentliche Herausforderung der nächsten Jahre verstanden werden kann.

Fig. 8 Bus-Protokoll

S Startbedingung

W Richtungsbit (Write)

A Acknowledgebit

P Stopbedingung