**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 75 (1984)

Heft: 3

**Artikel:** Méthodes et résultats d'essais sur les mémoires non volatiles

**Autor:** Van Vlaenderen, R.

**DOI:** https://doi.org/10.5169/seals-904350

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 30.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

## Méthodes et résultats d'essais sur les mémoires non volatiles

R. Van Vlaenderen

Ce rapport présente les résultats des tests effectués au CSEE ces trois dernières années sur les mémoires non volatiles. Après avoir différencié les divers types de défauts l'auteur montre la répartition des taux de défauts ainsi que la corrélation existant entre la procédure de test utilisée et le taux moyen de défauts

Der Aufsatz berichtet über die Resultate der Prüfungen an nicht-flüchtigen Speichern im CSEE (Schweiz. Komponentenprüfzentrum, Neuenburg). Es wird zwischen verschiedenen Arten von Ausfällen unterschieden; die entsprechende Verteilung wird gezeigt. Ferner untersucht der Autor den Zusammenhang zwischen der verwendeten Prüfmethode und der mittleren Ausfallrate.

Conférence présentée le 18 octobre 1983 au «Fall Meeting, IEEE Swiss Section, Chapter on Solid State Devices and Circuits», sous le thème général: «Non-Volatile Semiconductor Memories».

#### Adresse de l'auteur

R. Van Vlaenderen, ASE-CSEE, 2000 Neuchâtel.

Le Centre Suisse d'Essais des Composants Electroniques (CSEE) est une institution de l'ASE.

#### 1. Avant-propos

Le CSEE est un centre de test indépendant équipé pour l'essai des circuits intégrés logiques et analogiques. Dans ce but il dispose d'une large gamme d'équipements pour le test électrique et le déverminage des circuits intégrés selon la norme MIL 883-B. Pour l'essai électrique des mémoires non volatiles, l'appareil de test utilisé est une SENTRY VIII de Fairchild. La majorité des programmes de test pour ces mémoires ont été mis au point au CSEE. Pour la partie déverminage il est équipé de fours pour le stockage à haute température, le test en humidité et le burn-in statique ou dynamique. Il a également les moyens de soumettre les composants à des cycles thermiques entre -60° et +150° avec un équipement à chambre mobile. Des équipements spécialisés permettent de vérifier la résistance à l'accélération jusqu'à 70 000 g ainsi que l'étanchéité des boîtiers céramiques. Et enfin, il dispose d'équipements de programmation pour entrer les patterns de test dans les mémoires à tester. Grâce à ces équipements sophistiqués, il peut non seulement effectuer des tests électriques complets à toutes températures entre -55 et +150 °C, mais aussi réaliser des études de qualification ou des caractérisations. Depuis sa création en 1980 le CSEE a testé environ 3 mio. de composants dont 235 000 composants mémoires. Le rapport qui suit commentera les résultats d'essais obtenus sur ces mémoires non volatiles.

### 2. Types de mémoires non volatiles testées au CSEE

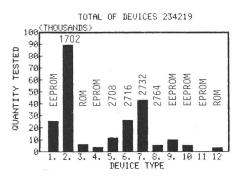

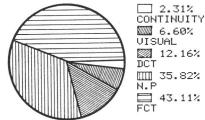

Cette statistique a été établie sur la période s'étendant de 1978 à mi-année 1983, c'est-à-dire depuis la création du CSEE. Cela représente un total de 234 219 composants mémoires testés. Il faut remarquer que les mémoires représentent moins de 10% des composants testés. Ces 234 219 composants

Fig. 1 Répartition des composants mémoires testés

| 1                 | <b>EEPROM</b> | 100*14             | XXXX |

|-------------------|---------------|--------------------|------|

| 2                 | <b>EPROM</b>  | 256**8             | 1702 |

| 3                 | ROM BIP       | 256*4              | XXXX |

| 4                 | <b>EPROM</b>  | 4K*8               | XXXX |

| 5                 | <b>EPROM</b>  | 1K*8               | 2708 |

| 6                 | <b>EPROM</b>  | 2K*8               | 2716 |

| 7                 | <b>EPROM</b>  | 4K*8               | 2732 |

| 8                 | <b>EPROM</b>  | 8K*8               | 2764 |

| 9                 | <b>EEPROM</b> | 16*16              | XXXX |

| 10                | <b>EEPROM</b> | 1K*4               | XXXX |

| 11                | <b>EPROM</b>  | 512 <b>*</b> 8     | XXXX |

| 12                | ROM BIP       | 256 <del>*</del> 4 | XXXX |

| (BIP = Bipolaire) |               |                    |      |

mémoires se répartissent en 12 différents types comme on peut le constater sur le diagramme de la figure 1. Pour ces différents types on ne mentionnera la dénomination exacte du composant que s'il y a au moins trois sources différentes pour ces composants, de façon à ce qu'on ne puisse pas faire de rapprochements entre les chiffres cités et un fabricant spécifique.

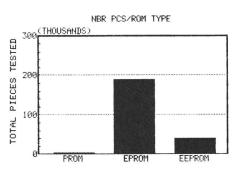

Dans la figure 2 on peut voir la répartition du nombre de pièces testées

Fig. 2 Répartition selon la catégorie de composants

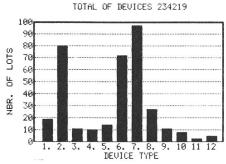

Fig. 3 Nombre de lots testés de chaque type

en fonction de la catégorie de composants, ceci pour donner une idée des types de composants sur lesquels le CSEE a pu acquérir une certaine expérience dans le domaine des mémoires non volatiles. Enfin, le diagramme de la figure 3 montre la répartition du nombre de lots de pièces traitées en fonction du type de composant. Les conclusions que l'on peut en tirer sont les suivantes:

- Les résultats des statistiques s'appliqueront principalement aux EPROM de 2 à

- La part prise par les ROM bipolaires est insignifiante.

- La part prise par les EEPROM est encore faible mais a tendance à s'accentuer.

- Il faut également mentionner que les composants complexes qui contiennent soit de la ROM masquée soit de l'EPROM n'ont pas été pris en compte.

#### 3. Taux de défauts obtenu pour chaque type

La figure 4 montre le taux de défauts constaté sur chacun des types de composants. Ce diagramme appelle des commentaires:

Tout d'abord on constate que les types 9, 10, 11 présentent des taux de défauts anormalement élevés. En ce qui concerne les types 9 et 10, il faut dire qu'il s'agit d'EEPROM relativement nouvelles sur le marché au moment où elles ont été testées, ce qui fait

qu'il y a probablement eu des problèmes de marginalité des valeurs annoncées sur les feuilles de spécifications ou des problèmes de mise au point des conditions de test. Dans les cas où il y a des problèmes de marginalité, un dialogue avec le client et le fournisseur permet généralement de résoudre le problème, ce qui semble avoir été le cas pour ces composants 9 et 10. En effet, si pour ces deux composants on refait un calcul du taux de défauts pour les cinq derniers lots testés, on obtient des taux de défauts respectifs de 1,9% et 1,5%. Il ne reste donc plus que le composant no 11 qui présente un taux de défauts anormalement élevé, mais pour ce composant seulement 3 lots représentant un total de 290 pièces ont été testés. Alors, soit le composant ne tient pas les spécifications, soit il s'agit de «freak components», la faible quantité de pièces testées ne permet pas de lever le doute.

Les taux de défauts pour les autres composants s'échelonnent entre 0,26% et 5,14% et expriment des résultats réels valables (avec quelques réserves cependant pour le type 2764 dont plusieurs lots ont été testés sans vérification de la rétention d'informations).

#### 4. Différentiation des types de défauts

La figure 5 montre la répartition selon les catégories de défauts:

Continuité: Elle comprend les circuits pour lesquels une ou plusieurs pattes de connexion ne sont pas reliées au «chip», ou présentent un court-cir-

Visuel: Ce sont les composants qui présentent un défaut dans leur aspect extérieur, par exemple pattes pliées ou oxydées, boîtiers cassés ou inscriptions illisibles.

DCT: Ce sont les défauts des paramètres statiques, c'est-à-dire courants de fuite tolérés dans les entrées, niveaux VOL et VOH au maximum des

grammation ou après des cycles programmation-effacement successifs. La figure 5 montre que les défauts fonctionnels ainsi que les pièces non programmables représentent la majorité des défauts (78%). La conclusion principale que l'on peut tirer de ces ré-

sultats est qu'il est important, dans une séquence de test d'EPROM, de les programmer une ou plusieurs fois et de s'assurer après chaque programmation que le contenu et les timings sont toujours corrects. Il faut insister sur ce point parce que les séquences de test demandées par les clients ne contiennent pas toujours de programmation et que, par conséquent, les circuits défaillants détectés dans ce cas ne représentent qu'une faible partie (moins de 20%) des circuits défaillants que l'on aurait pu détecter avec une séquence de test complète puisque les défauts paramétriques statiques ne représentent que 12% du total des défauts.

La séparation entre les défauts DCT et FCT n'est pas toujours parfaitement claire. En effet, un défaut des diodes de protection d'entrées ou un défaut des caractéristiques des transistors de sorties feront apparaître dans certains cas le composant comme mauvais au test de fonctionnement étant donné que ce test est effectué avant le test DCT. Il faudrait donc analyser les rapports de défauts (datalogs) de chaque pièce pour décider si l'origine du défaut de fonctionnement est due à la logique interne ou aux conditions paramétriques d'un élément d'entrée-sortie, ce qui, pour des raisons de temps, n'est pas possible en production. Les chiffres de la figure 1 sont donc probablement quelque peu élevés en ce qui concerne la catégorie FCT, et trop bas pour la catégorie DCT.

# EEPROM DEVICE TYPE

Fig. 4 Taux de défauts

Fig. 5 Répartition selon le type de défauts

DCT défauts paramétriques FCT défauts fonctionnels non programmables

#### 5. Répartition des pourcentages de défauts

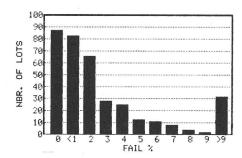

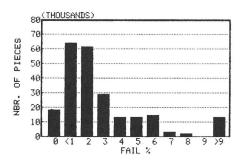

Les diagrammes des figures 6 et 7 tracent la répartition du nombre de lots et du nombre de pièces par catégorie de pourcentage de défauts. Pour 0 et >9% de taux de défauts on constate entre ces deux diagrammes un décalage important. Il y a en effet beaucoup

Fig. 6 Nombre de lots en fonction du pourcentage de défauts

de petits lots de pièces qui montrent 0% de défauts mais représentent peu de pièces. Cela vient du fait que beaucoup de caractérisations ou évaluations de composants sont réalisées avec des petites séries et que bien souvent ces composants ont déjà fait l'objet d'un tri soigné de la part du fabricant.

Pour la catégorie >9% de défauts on constate également que beaucoup de lots représentent peu de pièces; on peut éventuellement expliquer cela par le fait que les clients qui ont des ennuis en cours de production avec certains composants ne font parvenir au CSEE qu'un échantillonnage de leurs lots afin de déterminer où est le problème et non pas pour faire un contrôle d'entrée à 100%.

La figure 6 permet également de voir que 74% des lots testés présentent moins de 3% de défauts.

A ce sujet il faut préciser que dans la production du CSEE, dès qu'un lot présente un taux de défauts supérieur à 2%, ce lot fait l'objet d'un «engineering», destiné à s'assurer que:

- l'appareil de test est en parfait état,

- les spécifications du programme sont bien adaptées au composant,

- les défauts sont tous de même nature ou au contraire répartis,

- que les défauts sont francs ou marginaux.

Fig. 7 Nombre de composants des lots de la figure 6 en fonction du pourcentage de défauts

Dans le cas de défauts marginaux, le client est averti et prend lui-même la responsabilité en fonction de son application de décider s'il veut oui ou non élargir les limites de test.

La figure 7 donne une image réaliste de la distribution du taux de défauts qui est centré aux alentours de 2%. Le taux de défauts moyen sur l'ensemble des mémoires non volatiles testées au CSEE est de 3%. Le taux de défauts moyen calculé sur les 18 derniers mois est de 2,08%.

#### 6. Influence des procédures de test sur le taux de défauts

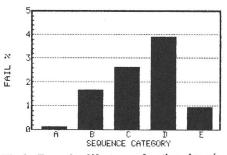

Le diagramme de la figure 8 illustre les taux de défauts en fonction des procédures utilisées. Ces catégories représentent les séquences de test suivantes:

A. Contrôle électrique sans programmation préalable ni aucune autre opération de déverminage. On constate dans ce cas que le taux de défauts est faible (0,15%), mais dans ce cas beaucoup de paramètres ne sont pas testés étant donné que les sorties ne changent pas d'état et qu'en plus, rien ne permet d'affirmer que le composant est réellement programmable.

B. Séquence où le composant a été programmé au moins une fois mais sans autre opération de déverminage. Dans ce cas on peut vérifier de manière presque complète le comportement fonctionnel, paramétrique ainsi que la possibilité d'effacer l'information. Cette séquence comporte généralement au minimum deux tests électriques, c'est-à-dire un test après programmation selon un pattern connu et ensuite un test après effacement.

Le fait que de la séquence A à la séquence B le taux de défauts passe de 0,15 à 1,68% montre déjà l'importance du cycle programmation-effacement.

Fig. 8 Taux de défauts en fonction des séquences de test

C. La séquence C est celle qu'on appelle séquence réduite au CSEE. Elle comporte généralement une programmation, un stockage de 24 h à 125 °C, un test électrique complet, un effacement suivi à nouveau d'un test électrique complet. Le stockage à haute température permet de vérifier le bon comportement du composant pour la rétention des informations. A nouveau la progression du taux de défauts est nette puisque l'on passe de 1,68 à 2,64% de défauts, ceci marquant l'intérêt du stockage à haute température séquences de test des dans les EPROM.

D. La séquence D est une extension de la séquence C. En fait elle comporte un cycle additionnel programmationtest complet-effacement, qui permet d'avoir actionné toutes les sorties dans les deux états et d'avoir soumis le composant à un stress complémentaire de programmation-effacement. Une fois de plus on peut constater l'augmentation des défauts. Toutefois les données à disposition' pour établir cette statistique ne permettent pas de quantifier l'influence due au stockage à haute température ou aux cycles programmation-effacement. Cependant certaines expérimentations effectuées sur de petits lots de composants semblent montrer que les cycles programmation-effacement seraient à l'origine d'une part plus importante de défaillances.

E. La catégorie E est totalement différente et est montrée ici à titre purement indicatif, elle montre le taux de défauts (0,93%) trouvé sur des composants à boîtiers céramiques qui ont été testés seulement pour leur étanchéité. Il s'agit donc ici seulement de défaillances mécaniques puisque ce taux de défauts a été déterminé par une séquence qui ne comprend qu'un test à l'accélération (30 000 g) suivi d'un test de détection de fuites.

#### 7. Conclusions

La forme qui a été choisie pour la présentation des résultats d'essais au CSEE était dictée par les types de composants soumis et les procédures d'essais demandées par les clients. Elle n'a donc pas la valeur d'une étude systématique de procédures de test avec des échantillons d'égales valeurs pour des technologies identiques. Cependant il est intéressant de constater que les taux de défauts varient fortement selon les procédures de test puisque selon les procédures utilisées on trouve

des taux moyens de défauts s'échelonnant entre 0,15 et 3,9%. Cela confirme l'intérêt qu'il y a à choisir des procédures de contrôle d'entrée des composants adaptées à l'utilisation et aux conditions climatiques auxquelles seront soumis les circuits une fois montés dans un équipement.

A l'avenir il est prévu d'étoffer ces résultats par des essais de burn-in statique et dynamique sur des lots importants de mémoires non volatiles afin de pouvoir se forger une opinion sur la valeur comparative du déverminage entre le stockage à haute température et le burn-in soit statique soit dynamique et d'éliminer ainsi le mieux possible les défaillances précoces. Il faut également noter que, même si la répartition du taux moyen de défauts est distribuée autour des 2%, il y a toujours des lots de composants qui présentent un pourcentage élevé de déchets et qu'il est important de décou-

vrir ces lots avant le montage des composants dans un système.

Enfin, il faut préciser que ce rapport se voulait être un simple constat des résultats d'essais et non une approche des mécanismes de défaillances des mémoires non volatiles, sujet qui demanderait à lui seul un volume bien plus conséquent et des connaissances précises des différentes technologies utilisées par les fabricants pour chaque type de circuit.