**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 75 (1984)

Heft: 1

**Artikel:** Die Integration in der Halbleitertechnik und ihre Grenzen

Autor: Reiner, H.

**DOI:** https://doi.org/10.5169/seals-904332

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF: 28.11.2025**

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Die Integration in der Halbleitertechnik und ihre Grenzen

H. Reiner

Seit rund 30 Jahren steht die Halbleitertechnik in dauernder rasanter Entwicklung. In nächster Zeit ist eine weitere Erhöhung der Integrationsdichte zu erwarten. Doch sind auch Grenzen abzusehen, einerseits technologischer Art, vor allem aber auch infolge stark zunehmendem Entwicklungs- und Prüfaufwand.

Depuis une trentaine d'années, la technique des semi-conducteurs n'a cessé de se développer. La densité d'intégration continuera à augmenter, mais certaines limites se dessinent d'une part de nature technologique et d'autre part et surtout en raison du coût considérable de la recherche et des essais.

## 1. Vom Transistor zur integrierten Schaltung

Vor etwa dreissig Jahren war die Nachrichtentechnik, insbesondere die Nachrichtenverarbeitung, hinsichtlich der Komplexität ihrer Geräte an eine Grenze gestossen, gegeben durch die Eigenschaften der verwendeten Verstärkerelemente und der Elektronenröhren. Ausfallrate, Verlustleistung und Raumbedarf begrenzten die Zahl der in einem Gerät oder System sinnvoll einsetzbaren Röhren. Ein Beispiel ist der 1948 fertiggestellte ENIAC-Rechner, der 18 000 Röhren besass und einen Leistungsbedarf von 174 kW hatte. Dieser Rechner war sehr teuer, sehr wartungsbedürftig und sehr unzuverlässig, und seine Einsatzmöglichkeiten waren dementsprechend be-

Die Entwicklung der digitalen Rechner erhielt neue Impulse durch den 1948 erfundenen Transistor. Etwa zehn Jahre später kam der Silizium-Planar-Transistor auf den Markt, und damit stand ein Verstärkerelement zur Verfügung, das hinsichtlich Zuverlässigkeit, elektrischer Eigenschaften, Leistungsbedarf und Raumbedarf fast alle Wünsche der elektronischen Gerätetechnik erfüllte. Bei der Herstellung dieses Elements werden durch aufeinanderfolgende Oxidations-, Fotoätzund Diffusionsprozesse in einen Silizium-Einkristall Störatome so eingelagert, dass sich zwei eng benachbarte Sperrschichten bilden, die Emitterund die Kollektorsperrschicht (Fig. 1). Dabei nutzt man eine Reihe von wichtigen Materialeigenschaften aus, nämlich

- dass sich das Halbleitermaterial Silizium (Si) leicht in grossen hochreinen Halbleiterkristallen herstellen lässt:

- dass Si eine hohe Trägerbeweglichkeit - sowohl von Elektronen als auch von Defektelektronen - und einen günstigen Bandabstand besitzt;

- dass Si sich durch thermische Oxidation an der Oberfläche in einer dünnen Schicht in amorphes SiO<sub>2</sub> umwandelt, das chemisch sehr stabil ist, den Si-Kristall schützt und gleichzeitig als Diffusionsmaske für Bor, Phosphor und andere als Donatoren und Akzeptoren geeignete Elemente verwendet werden kann.

Oxidation der Oberfläche

Fenster ätzen für Kollektor

Erste Diffusion (p)

4. Zweite Oxidschicht aufbringen

5. Fenster ätzen für Emitter

6. Zweite Diffusion (n)

7. Dritte Oxidschicht aufbringen

8. Fenster ätzen für Anschlüsse

Vortrag des STR-Symposiums 1983 «Von den elektronischen zu den biologischen Technologien – eine Bestandesaufnahme am Beginn einer Ära», 15. Juni 1983 an der ETHZ.

#### Adresse des Autors

40 (A 40)

Prof. H. Reiner, dipl. Physiker, Standard Elektrik Lorenz AG, Forschungszentrum, Helmuth-Hirth-Strasse 42, D-7000 Stuttgart 40.

Fig. 1 Herstellprozess des Si-Planar-Transistors

Die Strukturierung der Fenster im SiO2 für die Diffusion sowie für die Metallisierung erfolgt durch Fotoätztechnik, die hohe Strukturgenauigkeiten mit Toleranzen unter 1 um ermöglicht. Die Diffusions- und Oxidationsprozesse verlaufen bei Temperaturen oberhalb 1000 °C in Zeiten von etwa einer Stunde. Alle diese Prozesse sind sehr genau steuerbar. Der Planarprozess ermöglicht daher eine Fertigung von Transistoren mit eng tolerierten elektrischen Eigenschaften bei hoher Ausbeute. Auf einer Si-Scheibe von 10 cm Durchmesser können gleichzeitig viele tausend Transistoren hergestellt werden. Anschliessend wird die Scheibe in einzelne Plättchen, die sog. Chips, zerteilt, die je einen eindiffundierten Transistor enthalten. Diese Chips werden auf den Boden eines Transistorgehäuses aufgelötet. dünnen Gold- oder Aluminium-Drähtchen werden anschliessend die Emitter- und Basisanschlüsse hergestellt. Das Gehäuse dient dem mechanischen Schutz, der Wärmeabfuhr und der Manipulation des Elements in der Gerätefertigung. Sein Volumen ist oft um mehr als 6 Grössenordnungen höher als das aktive Volumen des Halbleiterkristalles

Die Eigenschaften dieser Planartransistoren erlaubten es, die Komplexität von Nachrichtengeräten gewaltig zu erhöhen. Diese Möglichkeit wurde auch bald ausgenutzt, und ab 1960 entstanden Grossrechner, elektronische Vermittlungssysteme und andere Systeme, bei denen Hunderttausende von Transistoren zusammenarbeiteten. Dabei zeigte es sich bald, dass die Zuverlässigkeit solcher Geräte im wesentlichen von den passiven Bauelementen, den Lötstellen und Verbindungsleitungen bestimmt wurde. Es zeigte sich, dass jede für die Gerätefunktion relevante Grenzschicht eine mögliche Fehlerursache darstellte. Um die Ausfallrate der Geräte zu verringern, musste man versuchen, die Zahl dieser Grenzschichten möglichst klein zu halten.

Im Jahre 1959 wurden die ersten integrierten Halbleiterschaltungen hergestellt. Die Grundidee war dabei, mehrere Bauelemente direkt auf einem Si-Chip durch Mikroverbindungen zu einer Schaltung zusammenzufassen. Voraussetzung dafür ist aber, dass auf dem Chip auch passive Bauelemente herstellbar sind und dass diese Elemente gegeneinander und gegen das Substrat isoliert werden. Es gelang, mit den Verfahren der Si-Planartech-

nik auf einem Si-Kristall nicht nur Transistoren und Dioden, sondern auch Widerstände, Kondensatoren und Verbindungsleitungen integriert herzustellen und diese Elemente gegen das Substrat zu isolieren. Allerdings wiesen dabei die passiven Bauelemente hohe Toleranzen und einen eingeschränkten Wertebereich auf. Daher hat man sich bei diesen integrierten Schaltungen von Anfang an im wesentlichen auf Digitalschaltungen konzentriert.

Die ersten integrierten Schaltungen umfassten nur einige wenige Bauelementefunktionen. Ihre geringen Abmessungen sowie ihre durch die geringe Zahl der für ihre Funktion notwendigen Grenzschichten bedingte niedrige Ausfallrate legten ihre Anwendungen bei militärischen Geräten und in der Raumfahrt nahe.

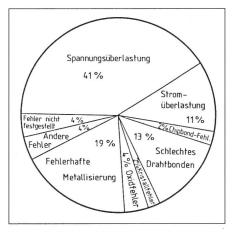

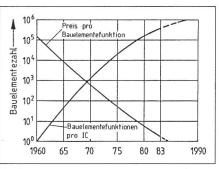

Bald erkannte man, dass diese Integration auch Kostenvorteile mit sich bringt, die um so höher ausfallen, je Bauelementefunktionen einem Chip untergebracht werden. Bei einem Halbleiter, sei es ein Einzeltransistor oder ein 64-kbit-Speicher mit mehr als 120 000 Bauelementefunktionen, überwiegen bei genügend grosser Stückzahl die Fertigungs- gegenüber den Entwicklungskosten, und bei gut eingelaufener Fertigung werden stets die Kosten für das fertig diffundierte Chip klein sein gegenüber den Kosten für das Gehäuse, die Herstellung der Anschlüsse, das Verschliessen und die Prüfung. Diese Kosten wiederum sind proportional zur Zahl der Anschlüsse. Die Hauptkosten bei der Fertigung integrierter Schaltungen sind also bedingt durch die elektrischen Anschlüsse nach aussen. Auch die Ausfälle bei integrierten Schaltungen treten grossenteils an diesen Anschlüssen auf (Fig. 2). Bei einer Steigerung der Inte-

Fig. 2 Verteilung der Fehlerarten bei integrierten Schaltungen

Fig. 3 Zeitlicher Verlauf von Komplexität und Preis pro Bauelementefunktion bei integrierten Schaltungen

gration, d.h. einer Erhöhung der Zahl der Bauelementefunktionen pro Chip, verringert sich aber im allgemeinen die Zahl der Anschlüsse pro Bauelementefunktion. Damit sinken Fertigungskosten und Ausfallrate pro Bauelementefunktion. Dies ist die hauptsächliche Triebfeder für die seit nunmehr fast 25 Jahren anhaltende Steigerung der Komplexität der integrierten Schaltungen (Fig. 3). Diese Steigerung der Integration wurde im wesentlichen erreicht durch Vereinfachung Grundfunktion von Schaltungen (Design Cleverness), Vergrösserung der Chip-Abmessungen sowie durch Verkleinerung der Strukturen.

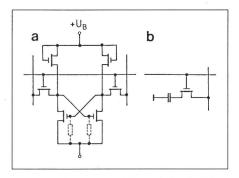

Fig. 4 Statische (a) und dynamische Speicherzelle (b)

Ein Beispiel für die Vereinfachung von Schaltungen ist der Übergang von der statischen Speicherzelle mit 6 Transistoren pro bit auf die dynamische Speicherzelle mit einem Transistor pro bit (Fig. 4). Von entscheidender Bedeutung für die Vereinfachung von Schaltungsstrukturen war aber die Einführung der MOS-Technik¹) um das Jahr 1970. Diese führte gegenüber der Bipolartechnik zu einer drastischen Verringerung der Zahl der Pro-

MOS = Metal-Oxide Semiconductor

CMOS = Complementary Metal-Oxide

Semiconductor

zessschritte, einer Vereinfachung der geometrischen Form der Elemente und zu beträchtlichen Schaltungsvorteilen. Beispiel hierfür sind die CMOS-Technik<sup>1</sup>), die Verwendung von Transistoren als passive Widerstände und die Ausnutzung der Bidirektionalität von MOS-Transistoren.

#### 2. Grenzen der Integration

#### 2.1 Geometrien

Der Vergrösserung der Chipfläche sind Grenzen gesetzt durch die Verringerung der Absolutausbeute und durch mechanische Probleme beim Einbau in Gehäuse. Man hat aber hier in Sonderfällen den Wert von 1 cm² überschritten.

Die wichtigste Massnahme zur Erhöhung der Integration war aber die Verkleinerung der geometrischen Abmessungen. Man erreicht damit nicht nur eine Erhöhung der Zahl der Schaltungsfunktionen auf einer vorgegebenen Fläche, sondern erzielt gleichzeitig eine Erhöhung der Funktionsgeschwindigkeit und eine Verringerung der Verlustleistung pro Schaltungsfunktion. Allerdings führt steigende Integration zu einer Verringerung der Ausbeute, wenn nicht gleichzeitig die Verteilungsfunktionen der Parameter der Einzelbauelemente auf dem Chip verbessert werden. Damit steigen aber die Anforderungen an die Technologie beträchtlich.

Die technologischen Fortschritte der vergangenen Jahre haben es möglich gemacht, immer höher integrierte Schaltungskomplexe kostengünstig zu fertigen. Heute liegt man bei etwa 100 000 Bauelementen pro Chip. Der 64-kbit-Speicher mit etwa 130 000 Bauelementefunktionen pro Chip dürfte etwa 1984 das technische Kostenoptimum für Speicher erreichen. In wenigen Jahren wird dieses Kostenoptimum bei mehr als 1 Mio Bauelementen pro Chip liegen.

Bei den meisten heutigen Halbleiterprodukten liegen die Minimalgeometrien, wie z.B. die Breite metallischer Leiterbahnen oder die Kanallängen von MOS-Transistoren, bei 3...5 µm. Mit Minimalgeometrien von 2 µm werden heute bis zu 500 000 Bauelementefunktionen auf einer Chipfläche von etwa 40 mm² untergebracht. Ein Beispiel hierfür ist der 262-kbit-Speicher, der zurzeit bei mehreren Halbleiterherstellern in Produktion geht. Bei Übergang auf 1-µm-Geometrien

wird man auf der gleichen Chipfläche etwa 2 Mio Bauelementefunktionen unterbringen.

Wie geht diese Entwicklung weiter? Wo sind ihre Grenzen? Strukturen mit einer Minimalgeometrie von 2 um erreicht man heute unter Verwendung optischer Projektionsverfahren. Die Grenze dieser Technik wird bei etwa 1 um erreicht. Dazu muss man aber bereits monochromatisches kurzwelliges Licht verwenden. Durch Verwendung von Röntgenstrahlen sowie von Elektronenstrahlen bzw. Ionenstrahlen lassen sich Strukturen mit Minimalgeometrien von weniger als 0,1 µm herstellen. Die verwendeten Photolacke liessen sogar sehr viel feinere Strukturen zu. Bei Minimalgeometrien von weniger als 0,1 µm würden aber die heutigen Halbleiterbauelemente nicht mehr richtig funktionieren. Legt man nämlich an eine pn-Schicht eine Sperrspannung, so entsteht eine Raumladungszone, deren Dicke selbst unter Annahme günstigster Bedingungen nicht unter 0,03 µm gebracht werden kann. Daraus ergibt sich eine minimale Basisdicke für Bipolartransistoren von 0,1 µm. Der gleiche Wert ergibt sich für die minimale Kanallänge eines MOS-Transistors. Unter dieser Annahme wird man für einen Transistor eine Gesamtfläche von 1 µm², für ein einfaches Gatter von 4 µm² benötigen. Damit wird die maximale Gatterdichte bei 2,5×10<sup>7</sup>/cm<sup>2</sup> liegen. Diese kann aufgrund der heutigen Erkenntnisse bei Verwendung üblicher Halbvermutlich leitermaterialien überschritten werden.

Man kann ferner eine Abschätzung der Transitzeit eines Elektrons bei einem Transistor mit minimalen Abmessungen durchführen und kommt dabei zu Werten von etwa  $1,5 \cdot 10^{-12}$  s. Die minimale Schaltzeit eines Gatters lässt sich auf 2 ps abschätzen. Damit ergibt sich die maximal mögliche Taktfrequenz zu  $f_T = 100$  GHz.

#### 2.2 Halbleiterkennlinien

Will man aber diese Taktfrequenz ausnutzen, so kommt man mit der Verlustleistung in Schwierigkeiten. Um diese niedrig zu halten, wird man versuchen, die Versorgungsspannung und die Signalpegel so niedrig als möglich zu halten. Der Verringerung der Versorgungsspannung sind durch die für Digitalschaltungen notwendigen Nichtlinearitäten Grenzen gesetzt. Man braucht Kennlinienknicke, um

logische Verknüpfungen zu realisieren. Den schärfsten Kennlinienknick liefert die Halbleiterdiode. Für die ideale Diode gilt:

$$I_{\rm D} = I_{\rm s} (e^{\frac{q \cdot U}{kT}} - 1)$$

mit

q = Elementarladung

k = Boltzmann-Konstante

Für T = 300 k wird die Knickspannung  $U_0 = kT/q = 25 \text{ mV}.$

Das bedeutet: Bei Zimmertemperatur kann sich der Diodenstrom bei einer Spannungsänderung um  $U_0 = 25 \text{ mV}$  maximal um den Faktor e = 2,718.. ändern. Damit ist die Maximalkrümmung der Diodenkennlinie vorgegeben.

Es ist zurzeit kein physikalischer Effekt bekannt, der es erlauben würde, Bauelemente herzustellen, die bei Zimmertemperatur schärfere Kennlinienknicke aufweisen würden als Halbleiterdioden. Aus praktischen Gründen ist es notwendig, einen Signalhub von mindestens dem 20fachen der Knickspannung  $U_0$  zu verwenden. Die minimalen Versorgungsspannungen  $U_m$  liegen daher bei etwa 0,5 V. Eine wesentliche Unterschreitung dieses Wertes ist nur bei entsprechend niedrigeren Temperaturen möglich.

#### 2.3 Verlustleistung

Die minimale Verlustleistung erhält man bei Schaltungen, bei denen die Ruheleistung null ist. Hier wird nur für die Umladung von Kapazitäten Leistung verbraucht. Für einen vollständigen Übergang 0–1–0 eines Gatters wird die Energie  $E = C_{\rm L} \cdot U_{\rm m}^2$  benötigt. Dieser Betrag wird auch als Geschwindigkeits-Leistungs-Produkt K bezeichnet. Mit einer Lastkapazität  $C_{\rm L} = 1 \cdot 10^{-3}$  pF und  $U_{\rm m} = 0,5$  V wird  $K = 2,5 \cdot 10^{-4}$  pJ.

Will man die volle Funktionsgeschwindigkeit auf dem Chip ausnutzen, so wird die Leistung pro Flächeneinheit

$$P = \frac{1}{2} m \cdot f_{\rm T} \cdot K$$

mit

$m = \text{Zahl der Schaltkreise pro cm}^2$

$f_{\rm T}$  = maximale Taktfrequenz

$K = 2.5 \cdot 10^{-16} \,\mathrm{Ws}$  $m = 2.5 \cdot 10^7 / \text{cm}^2$

$f_{\rm T} = 100 \, \rm GHz$

wird dann  $P = 312,5 \text{ W/cm}^2$ .

Tatsächlich lassen sich aber bei Luftkühlung maximal 2 W/cm², bei Flüssigkeitskühlung maximal W/cm<sup>2</sup> abführen. Die Ausnutzung der maximal möglichen Gatterdichte und der maximal möglichen Funktionsgeschwindigkeit führt somit zu Problemen bei der Wärmeabfuhr. Aus thermischen Gründen muss daher entweder die Gatterdichte oder die Funktionsgeschwindigkeit unter die maximal möglichen Werte gesenkt werden. Bei maximaler Gatterdichte erhält man damit eine maximal zulässige Taktfrequenz von 640 MHz (2 W/cm<sup>2</sup>) bzw. von 6,4 GHz (20 W/cm<sup>2</sup>).

Reduziert man anderseits die Pakkungsdichte, um die maximal mögliche Taktfrequenz zuzulassen, so erhöht sich die mittlere Länge der Signalleitungen zwischen den Gattern, und man muss dann von der Annahme einer wesentlich höheren Lastkapazität ausgehen.

#### 2.4 Signallaufzeit

Die Laufzeiten auf den Signalleitungen begrenzen auch die Fläche und damit die Komplexität des Netzwerkes, innerhalb dessen Taktsynchronisierung gefordert werden muss. Die Signalgeschwindigkeit einer elektromagnetischen Welle auf einer Signalleitung liegt bei integrierten Schaltungen etwa bei v = 0.1 c(c = Lichtgeschwindigkeit =  $3 \cdot 10^{10}$  cm/s).

Nimmt man weiter an, dass die Impulse innerhalb eines synchron arbeitenden Netzwerkes um 10% der Taktzeit differieren dürfen, so kann man abschätzen, dass die Schaltungen mit Taktsynchronisierung in einem Rechteck der Kantenlänge

$L = 0.01 \, c/f_{\rm T}$

liegen müssen. Bei einer Taktfrequenz von 10 GHz wird L = 0.3 mm und damit die Zahl der synchron zusammenarbeitenden Gatter gleich 22 500.

Tabelle I zeigt einen Vergleich der Grenzen der Halbleitertechnik mit dem heutigen Stand der Technik. Hierzu ist allerdings zu bemerken, dass es derzeit nicht möglich ist, mehrere dieser Grenzwerte, wie z.B. Funktionsgeschwindigkeit und minimale Leistung, gleichzeitig zu erreichen. Ähnlich wird

Grenzen der digitalen Halbleitertechnik im Vergleich zum Stand der Technik

Tabelle I

|                                                                                     | Grenzen                                                                                   | Stand der Technik                                                               |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Minimale Grösse von<br>Einzeltransistoren                                           | $\approx 1 \mu\text{m}^2$                                                                 | 100 μm²                                                                         |

| Maximale Integrationsdichte (geometrisch)                                           | $\approx 2.5 \times 10^7  \text{Gatter/cm}^2$<br>\approx 5.0 \times 10^7 \text{ bit/cm}^2 | 10 <sup>5</sup> Gatter/cm <sup>2</sup><br>7·10 <sup>5</sup> bit/cm <sup>2</sup> |

| Minimale Schaltzeit                                                                 | ≈ 1,5 ps                                                                                  | 100 ps                                                                          |

| Maximale Taktfrequenz eines<br>synchronen Netzwerkes mit<br>10 <sup>5</sup> Gattern | ≈ 3 GHz                                                                                   | 30 MHz                                                                          |

| Minimales Geschwindigkeits-<br>Leistungsprodukt                                     | 2,5 · 10 <sup>-16</sup> Ws                                                                | 10 <sup>-12</sup> Ws (Si-bipolar)<br>1,4×10 <sup>-14</sup> Ws (MESFET)          |

| Minimale Zugriffszeit für<br>Speicher mit einigen 10 <sup>4</sup> bit               | ≈ 100 ps                                                                                  | 6 ns                                                                            |

MESFET = Metalized Semiconductor Field-Effect Transistor

es wohl in Zukunft bei der Annäherung an die physikalischen Grenzen gehen. Man kann aber damit rechnen, dass eine Erhöhung der Komplexität um den Faktor 100 und der Funktionsgeschwindigkeit um den Faktor 10 möglich sein wird, bevor man ernsthaft an physikalische Grenzen anzustossen beginnt. Von der Technologie her erscheint es daher möglich, die Rechenleistung heutiger Mikroprozessoren noch um den Faktor 1000 zu steigern. Man wäre damit beim Superrechner auf einem Chip angelangt. Ob und wann ein solcher Super-Mikroprozessor zur Verfügung stehen wird, ist aber eine Frage, die weniger von der Technologie abhängen wird.

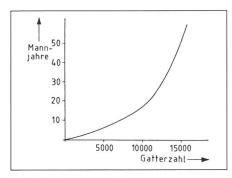

#### 2.5 Entwicklungs- und Prüfaufwand

G. Moore hat kürzlich gezeigt, dass der Entwicklungsaufwand für einen Mikroprozessor etwa mit dem Qua-Komplexität der (Fig. 5). Diese Feststellung klingt plausibel. Bei der Erweiterung eines vorgesehenen Komplexes müssen die

Fig. 5 Design-Aufwand in Abhängigkeit von der Gatterzahl (nach Moore)

LSI-Schaltungen mit unregelmässiger Struktur. Optimiertes manuelles Lavout.

Wechselwirkungen mit den bereits vorhandenen Teilen untersucht werden. Dieser Teil des Entwicklungsaufwandes folgt einem Quadrat-Gesetz. Stimmt diese Behauptung von Mooreund alles spricht dafür -, dann werden. diese steigenden Entwicklungskosten pro Gatter irgendwann zu einer Verlangsamung der Erhöhung der Integration bei Komplexen mit nicht regelmässiger Struktur führen. Das Mooresche Gesetz gilt nicht für Schaltungen mit regelmässiger Struktur, wie z.B. Speicher. Alle zurzeit bekannten grösstintegrierten Schaltungen sind denn auch entweder Speicher oder regelmässig aufgebaute Mikroprozesso-

ren mit hohem Speicheranteil.

Noch problematischer sieht es bei der Prüfung grosser Schaltkreiskomplexe aus. Eine vollständige statische Prüfung eines Schaltwerkes mit z.B. 20 Eingängen und 50 internen Speichern ist aus quantitativen Gründen nicht möglich. Die Zahl der notwendigen Prüfschritte nimmt exponentiell mit der Zahl der Eingangsvariablen und der internen Speicher zu. Dazu kommen noch dynamische und parametrische Prüfungen. Eine Erleichterung der Prüfaufgabe durch zusätzliche Testanschlüsse führt zu zusätzlichen Kosten und macht den ganzen Sinn der Grossintegration zunichte. «Prüffreundliche Strukturen» und «Testschaltung auf dem Chip» sind heute Schlagworte, die in Zukunft helfen werden, Testprobleme besser zu lösen. Die heute üblichen Testprogramme für grossintegrierte Schaltungen erfassen 80...95% der durch statistische Prüfungen erfassbaren Fehler. Man muss also damit rechnen, dass bei der Geräteerprobung oder im Einsatz Fehler auf-

Fig. 6 Softfehler durch Alpha-Teilchen

treten, die auf eine unvollständige Funktionsprüfung zurückzuführen sind. Diese Prüfproblematik entsteht zu einem Zeitpunkt, in dem auch wegen der weiteren Verkleinerung der Abmessungen mit einem starken Ansteigen der Fehlerraten gerechnet werden muss. Dies ist darauf zurückzuführen, dass die Verringerung der Abmessungen

- die Gefahr von Fehlern an der geometrischen Struktur erhöht (man denke nur an das noch ungelöste Problem der Vermeidung von Staubteilchen mit Abmessungen unter 1 μm);

- zum Auftreten neuer und der Zunahme bekannter Fehlermechanismen (z.B. Korrosion im Sub-μ-Bereich) führt;

- zu erhöhter Belastung (Stromdichte, elektrisches Feld usw.) führt;

- eine erhöhte Dotierung erfordert (dies führt zu einer Erhöhung der Defektdichte im Kristall).

### 2.6 Neuartige technologische Probleme

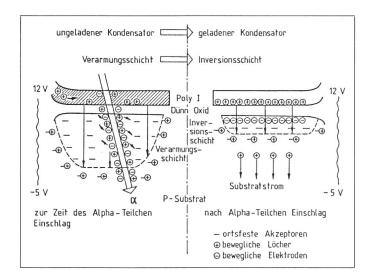

Die Softfehler durch Alpha-Teilchen sind ein Beispiel dafür, was an neuen Problemen durch die Verringerung der Abmessungen auftreten kann. Ein Alpha-Teilchen kann in Silizium auf einer Strecke von etwa 30 µm mehr als 1 Mio Elektronen-/Defekt-

elektronenpaare erzeugen (Fig. 6). Tritt dies in der Verarmungsschicht eines pn-Überganges auf, so entsteht ein kurzer Stromimpuls, der bei kleinflächigen Bauelementen zu einem Fehlsignal führen kann. Die Einführung der 16-kbit-Speicher ist durch diesen Effekt lange Zeit verzögert worden. Heute beherrscht man dieses Problem einigermassen durch sorgfältige Materialauswahl und durch schirmmassnahmen. Bei weiterer Verringerung der Abmessungen muss man jedoch auch damit rechnen, dass Mesonen und Elektronen, die sich nicht mehr abschirmen lassen, Softfehler erzeugen. Dagegen hilft nur noch die Verwendung redundanter Schaltun-

#### 2.7 Strukturelle Lösungen

Die Probleme bei der Weiterentwicklung der integrierten Schaltungen werden sich also in Zukunft immer mehr von der Technologie auf die Struktur verlagern. Man wird in immer stärkerem Masse die komplexen grossintegrierten Schaltungen strukturieren. Man wird damit diese Komplexe übersichtlicher machen und die Wiederverwendbarkeit bereits entwikkelter Strukturen erhöhen. Anderseits bedeutet Strukturierung natürlich auch Einschränkung in der Flexibilität und damit höheren Aufwand. Ansätze

für eine solche Strukturierung gibt es schon bei Gate Arrays und bei Zellenbibliotheken. Es gibt heute grossintegrierte Schaltungen, die ganze Mikroprozessoren als Makrozellen enthalten. Die Einführung von Makrozellen wird ferner eine geregelte Kommunikation über Busstrukturen erforderlich machen, und man wird in Zukunft Technologien. Grundschaltungen. Zellen, Makrozellen, Busstrukturen und Übertragungsprotokolle in der Schaltung standardisieren müssen, wenn die Weiterentwicklung der Integration nicht wegen exponentiell ansteigender Entwicklungsaufwendungen steckenbleiben soll.

Die Probleme bei Strukturentwicklung und Prüfung sind eine Konsequenz der Tatsache, dass integrierten Schaltungen im Gegensatz zu biologischen Systemen jede Fähigkeit der Selbstreparatur fehlt. Der Schaltungsentwicklung sind ferner durch die Tatsache Grenzen gesetzt, dass integrierte Schaltungen im Prinzip zweidimensionale Strukturen sind. Die Ein- und Ausgänge sind fast immer eindimensional am Rand der Schaltungen angeordnet. Dies führt zu schwerwiegenden Einschränkungen hinsichtlich der zu realisierenden Aufgaben. Dagegen erleichtern diese technologischen Beschränkungen die Konzipierung solcher Schaltungen.

#### 2.8 Ausblick

Die Technologie der grossintegrierten Schaltungen hat ihre rasche Entwicklung der glücklichen Kombination des fast idealen Halbleitermaterials Silizium mit dem idealen Schutzüberzug SiO2 und geeigneten Donatoren und Akzeptoren zu verdanken. Dieser Glücksfall, den uns die Natur beschert hat, hat es ermöglicht, dass die Entwicklung der Grossintegration so atemberaubend schnell verlaufen ist. Er wird es auch ermöglichen, dass für die nächsten Jahre die Grossintegration der Motor der Innovation in weiten Bereichen unseres Lebens bleiben und werden wird.