**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 75 (1984)

Heft: 1

Artikel: Génération automatique de layout orienté métal pour circuits CMOS

**Autor:** Piguet, C. / Bertarionne, M.

**DOI:** https://doi.org/10.5169/seals-904331

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

# **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

# Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 01.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Génération automatique de layout orienté métal pour circuits CMOS

C. Piguet, M. Bertarionne

Le dessin des plans de masques ou layout de circuits intégrés est un travail long, fastidieux et non exempt d'erreurs. De manière à augmenter la productivité des opérateurs, nous proposons ici une nouvelle technique de dessin basée sur une description symbolique du circuit. En outre, ce layout symbolique est orienté métal, basé sur un croisement systématique des conducteurs métalliques et diffusions. Il est décomposable en microcellules: le concepteur doit donc utiliser un répertoire très limité de microcellules avec leurs règles d'assemblage pour obtenir un layout symbolique. Le layout géométrique est obtenu par traduction automatique assurée par un programme. Quelques exemples permettent de chiffrer les productivités obtenues par cette technique, ainsi que les densités en transistors par mm² atteintes pour ces circuits

Das Zeichnen der Maskenpläne oder der Entwurf von integrierten Schaltungen ist eine langwierige und mühsame Arbeit, bei der Fehler kaum zu vermeiden sind. Um die Produktivität des Entwerfers zu erhöhen, wird eine neue Zeichentechnik vorgeschlagen, die auf einer symbolischen Beschreibung der Schaltung beruht. Der symbolische Entwurf ist ferner metallorientiert, auf der systematischen Kreuzung von metallischen Leitern und Diffusionsleitern aufgebaut. Er kann in Mikrozellen unterteilt werden: Der Entwerfer muss ein sehr beschränktes Verzeichnis derartiger Zellen mit ihren Montagevorschriften verwenden, um damit den symbolischen Entwurf aufzubauen. Der geometrische Entwurf folgt automatisch mittels eines Programms. Verschiedene Beispiele ermöglichen es, die auf diese Weise erzielte Produktivität zu beziffern sowie die Transistordichte der resultierenden Schaltungen anzugeben.

Ce travail est partiellement financé par la Commission pour l'Encouragement des recherches scientifiques en Suisse, Crédits 1085 et 1085.1.

# Adresse des auteurs

Dr C. Piguet, M. Bertarionne, Centre électronique horloger SA., Maladière 71, 2000 Neuchâtel 7.

# 1. Introduction

L'objectif de la technique de layout proposée est l'obtention d'une meilleure productivité au niveau graphique qui est actuellement de l'ordre de 4 à 6 MOS/jour par opérateur pour des circuits complexes. Néanmoins, il est indispensable d'obtenir des circuits présentant une densité comparable à celle des layouts dessinés à la main, le rendement de fabrication des circuits décroissant fortement avec l'augmentation de surface de la puce.

La technique de layout consistant à dessiner symboliquement les éléments du circuit sur une grille est appelée Layout Symbolique Statique [1]. Cette technique a été utilisée par plusieurs fabricants de circuits intégrés [2; 3; 4]. La référence [4] propose une structure de layout où ce sont les conducteurs en silicium polycristallin (poly) qui croisent systématiquement des conducteurs en métal ou en diffusion. Dans ce dernier cas, un transistor MOS est créé. Dans ce type d'orientation, ni les conducteurs poly ni les conducteurs métal ne sont placés à distance minimum. Il en résulte que la densité est inférieure à celle des layouts dessinés à la main.

# 2. Layout symbolique orienté métal

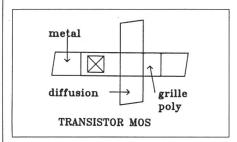

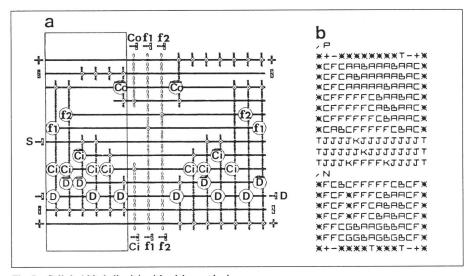

Dans la technique de layout proposée [5], une autre orientation est choisie: ce sont les conducteurs métalliques qui croisent systématiquement les conducteurs diffusion. Le transistor MOS étant créé par le croisement

Fig. 1 Transistor MOS

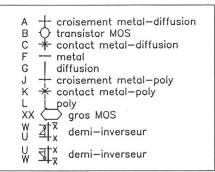

poly-diffusion, il est nécessaire de contacter une grille poly à un conducteur métallique lorsque ce dernier croise une diffusion pour obtenir le transistor MOS (fig. 1). Les conducteurs métalliques sont placés aux distances minimum. Il est également possible d'implanter des conducteurs poly verticaux. La conception d'un layout symbolique doit s'effectuer à partir des 11 microcellules symboliques de la figure 2. Les conducteurs horizontaux sont toujours métalliques. Les conducteurs verticaux sont soit des diffusions (traits épais), soit des poly (traitillés). Le transistor de dimension minimum est symbolisé par un cercle, le contact par une croix, le transistor plus gros occupant deux microcellules par un hexagone et un demi-inverseur par le symbole correspondant. Ces derniers sont associés par paire pour la réalisation d'un inverseur.

Le concepteur d'un layout symbolique dispose d'une grille dans laquelle il place les microcellules représentées à la figure 2, de manière à obtenir la fonction logique désirée. L'assemblage des microcellules dans une grille doit obéir à un certain nombre de règles. Ces règles sont résumées dans des matrices d'assemblage indiquant les juxtapositions interdites de deux microcellules dans une ligne ou une colonne. Par exemple, il est interdit de juxtaposer dans une colonne deux microcellules A et J, une diffusion ne pouvant être connectée à un poly.

Fig. 2 Ensemble des microcellules symboliques

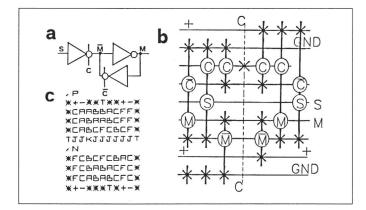

Fig. 3 Registre C<sup>2</sup>MOS

- a Schéma logique

- b Layout symbolique

- c Fichier alphabétique

placer certaines colonnes diffusion en préservant le fonctionnement logique. Par exemple, les zones N entourées par le caisson peuvent être alignées à travers des tranches différentes, par exemple pour la tranche d'un compteur de programme et la logique du pointeur de pile associée (fig.

- La méthode de synthèse est très simple et convient bien à une organisation verticale de l'équipe de développement où chaque concepteur est responsable d'une partie d'un circuit jusqu'au layout.

La méthode de synthèse de circuits logiques CMOS [6] consiste à générer les équations logiques simplifiées par la méthode de Karnaugh sous forme de somme de produits, ceci séparément pour les réseaux de transistors N et P. Pour une cellule de registre, on obtient:

$$N(\bar{M}) = C \cdot S + \bar{C} \cdot M \quad P(\bar{M}) = \bar{C} \cdot S + C \cdot M$$

$N(M) = \bar{M} \quad P(M) = \bar{M}$

$N(\bar{C}) = C \quad P(\bar{C}) = C$

La figure 3 représente le layout symbolique obtenu avec les deux blocs N et P placés sous les lignes métal horizontales. Une variable de contrôle C est implémentée en poly vertical. Ce layout symbolique doit être traduit en fichier alphabétique. Il est tourné d'un quart de tour (la dernière colonne devient la première ligne). Les ordres, N et P, définissent les régions N et P. Les symboles terminaux +, - et T définissent les points d'entrée/sortie pour  $V_{\rm DD}$ ,  $V_{\rm SS}$  et les variables logiques.

Le layout orienté métal procure un certain nombre d'avantages:

- Les variables internes du circuit sont disponibles sur les deux côtés du circuit. Elles sont au pas minimum métal: les cellules logiques peuvent ainsi être mélangées à des structures de bus métal [7].

- Les variables de contrôle en poly sont placées entre les blocs Net P(écartés par les règles de layout diffusion-caisson), ce qui augmente la densité.

- Les lignes métal sont toujours perpendiculaires aux lignes diffusion et poly; il est ainsi toujours possible d'ajouter des lignes métal ou poly pour un niveau d'interconnexions de plus haut niveau.

- Une telle technique de layout convient bien à une méthodologie basée sur le plan directeur [8]. Par exemple, le registre C2MOS a été redessiné pour s'adapter à une tranche d'un compteur de programme avec pointeur de pile (fig. 4).

- Comme toutes les variables internes sont implémentées par des lignes métal allant horizontalement d'un côté à l'autre du circuit, il est possible d'échanger ou de dé-

Fig. 4 Registre C2MOS redessiné

# 3. Programme de traduction

L'objectif du programme est la traduction automatique du layout symbolique en un layout géométrique. L'entrée du programme est constituée par un layout symbolique dessiné sur une installation graphique ou par un fichier alphabétique (fig. 3) si l'on ne dispose que d'une console alphanumérique. C'est dire que dans le premier cas, la première tâche du programme sera de traduire le layout symbolique en un fichier alphabétique.

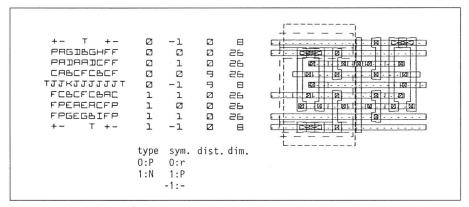

La figure 5a représente le layout symbolique d'une cellule 1 bit d'une unité arithmétique et logique assurant la transparence, la décrémentation, l'incrémentation et l'inversion en fonction des 4 combinaisons des variables  $f_1f_2$ . Les variables D et S sont respectivement l'entrée et la sortie du circuit, tandis que C est le report de l'étage précédent et C<sub>0</sub> celui généré pour l'étage suivant. La figure 5b représente le fichier alphabétique correspondant, tourné d'un quart de tour (les conducteurs métal sont verticaux).

Fig. 5 Cellule 1 bit de l'unité arithmétique et logique a Layout symbolique b Fichier alphabétique

| а               | b        |          |           |    |  |

|-----------------|----------|----------|-----------|----|--|

| *MATA           | *MATE    |          |           |    |  |

| +- T-+          | Ø        | -1       | •         | В  |  |

| CFHGGJGGGJAAC   |          | <b>3</b> |           | 25 |  |

| CFCGIAGGGA&AC   |          | 1        | <b>2</b>  | 26 |  |

| CFCGAAGG JAAAC  | <b>3</b> | Ø        | <b>23</b> | 26 |  |

| CFF FFHIARBAC   | Ø        | ı        | <b>2</b>  | 26 |  |

| CFF FFCABBAAC   | Ø        | 0        | Ø         | 26 |  |

| CFF FFFCBARAC   |          | 1        |           | 26 |  |

| CARHEFFFFCBAC   | Ø        | Ø        | (2)       | 26 |  |

| TJJJJKJJJJJJJJT | Ø        | -1       |           | 8  |  |

| TJJJJJKJJJJJJJ  | (2)      | -1       | Ø         | 8  |  |

| TJJJMFFFFNJJJJT |          | -1       | 0         | 8  |  |

| FCBIFFFFCBCF    | 1        | Ø        | (2)       | 26 |  |

| FCF FFFCBAACF   | 1        | 1        | Ø         | 26 |  |

| FCF FFCABABCF   | 1        | Ø        | Ø         | 26 |  |

| FCF FFCERBACE   | 1        | 1        | Ø         | 26 |  |

| FFCGERAGBERCF   | 1        | Ø        | Ø         | 26 |  |

| FFIGGERGEGACE   | 1        | 1        | Ø         | 26 |  |

| +- T T-+        | * 1      | -1       | Ø         | B  |  |

|                 |          |          |           |    |  |

Fig. 6 Fichier du layout de la figure 5 après prétraitement complété des indications de la hauteur

#### 3.1 Prétraitement

L'objectif du prétraitement est la suppression de segments inutiles de métal et l'introduction de microcellules de bord dans lesquelles le conducteur métallique est arrêté. Par exemple, dans la partie droite de la figure 5a, les lignes métalliques ont été dessinées jusqu'au bord de la cellule, alors que certains de ces segments sont inutiles. Le prétraitement fera disparaître ces segments comme cela a été fait par le concepteur pour la partie gauche de la figure 5a. Il est évident que s'il existe un symbole terminal T, la ligne métallique est conservée jusqu'au bord. Le prétraitement assure également la suppression des lignes et colonnes vides après avoir introduit les microcellules de bord. La figure 6a représente le fichier obtenu après prétraitement à partir de celui de la figure 5a. On constate que le répertoire de microcellules est étendu: par exemple, les microcellules de bord D et E remplacent B et les microcellules de bord Het I remplacent Cselon que c'est un point de départ ou d'arrivée du conducteur métallique.

#### 3.2 Symétrie

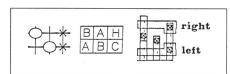

Pour améliorer la densité, les microcellules comportant des diffusions sont géométriquement asymétriques. Les diffusions sont écartées vers la droite pour la symétrie droite et vers la gauche pour la symétrie gauche, de manière à pouvoir placer les contacts des grilles entre les diffusions sans perte de surface (fig. 7). On attribue la

Fig. 7 Principe de la symétrie

Fig. 8 Fichier du layout (a) de la figure 5a avec ancrages et indication des distances (b)

même symétrie à toutes les microcellules d'une même colonne.

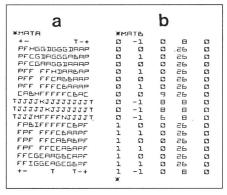

De manière à calculer les dimensions finales du layout géométrique, le programme attribue à chaque colonne une hauteur qui peut différer selon le type de microcellules. Ces informations sont stockées par le programme dans une matrice associée au fichier, comme le représente la figure 6b. La première colonne indique le type (Ø pour le type P et 1 pour le type N), la deuxième colonne indique la symétrie (∅ pour droite, 1 pour gauche et -1 pour aucune symétrie) et la quatrième colonne indique la hauteur des microcellules (une unité correspond à 0,5 um pour la technologie 4 um).

# 3.3 Matrice d'assemblage

Les microcellules sont généralement assemblées par simple collage. Par exemple, l'assemblage de plusieurs lignes métal est effectué toujours à distance minimum, et les microcellules correspondantes sont toujours assemblées par collage. Par contre, entre deux colonnes comportant des lignes poly ou des diffusions, il peut être nécessaire d'introduire une distance due aux règles de layout de la technologie choisie. C'est le cas par exemple entre une microcellule *B* (transistor) et *C* (contact) où, selon la symétrie, le poly de la grille du transistor est trop près de la diffusion du contact.

La figure 8b représente la matrice associée au fichier de la cellule de l'unité arithmétique et logique, où la troisième colonne indique les distances à placer entre les lignes du fichier alphabétique de la figure 8a.

### 3.4 Régions N et ancrages

Certains masques (comme le caisson) distinguent les régions des MOS N de celles des MOS P. Le programme calcule les emplacements de ces rectangles en tenant compte des règles de layout adéquates:

La figure 8a représente le fichier alphabétique de la cellule unité arithmétique et logique après avoir remplacé les microcellules C placées sur les alimentations + et - en microcellules P dites ancrages, permettant de fixer les potentiels des caissons et du substrat. Un ancrage est réalisé pour chaque paire de microcellules P de symétrie droite-gauche.

#### 3.5 Traduction

Le programme dispose de la représentation en layout géométrique des différentes microcellules. Celles-ci sont assemblées géométriquement sans la couche métal, en tenant compte des distances calculées. Les conducteurs métalliques sont ensuite placés, certaines microcellules étant les points de départ et d'autres les points d'arri-

Fig. 9 Layout géométrique de la cellule unité arithmétique et logique

Fig. 10 Traduction et layout géométrique du registre C<sup>2</sup>MOS

vée des segments de métal. Une procédure géométrique permet également de joindre en un seul segment tous les tronçons de diffusion et de poly. Enfin, dans certains cas, à la suite de la procédure de calcul des distances, certaines grilles de transistors contactées au même conducteur métallique ne se touchent plus, et ainsi ne respectent plus les règles de layout. Ceci peut également se produire entre deux contacts. Une procédure joint ces grilles et supprime un des deux contacts trop proches.

La figure 9 représente le layout géométrique de la cellule unité arithmétique et logique en technologie CEH 4 μm. La densité est de 1200 MOS/mm² en technologie 4 μm.

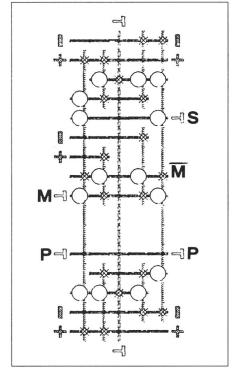

La figure 10 représente le fichier alphabétique, la matrice associée ainsi que le layout géométrique du registre C<sup>2</sup>MOS de la figure 3. La densité est de 1600 MOS/mm<sup>2</sup> en technologie 4 µm.

# 4. Résultats

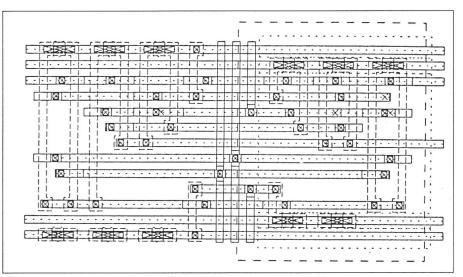

L'assemblage des différentes cellules doit s'effectuer au niveau symbolique, ce qui permet d'être indépendant de la technologie pour de très gros modules.

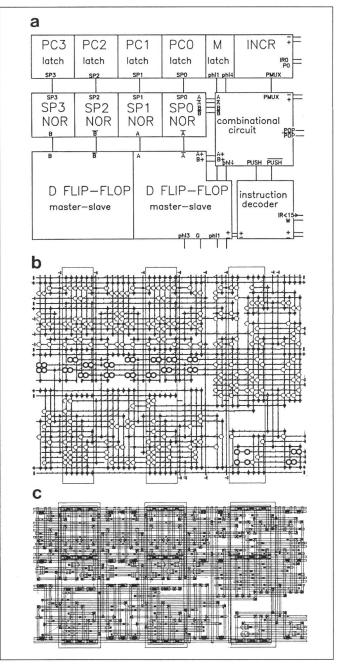

La figure 11a représente le plan directeur d'une première tranche d'un compteur de programme, ainsi que le pointeur de pile associé. La figure 11b représente le layout symbolique obtenu à partir du fichier alphabétique, ce qui permet la vérification au niveau symbolique. La figure 11c représente le layout géométrique correspondant. La densité de ce module est de 1200 MOS/mm² en technologie 4 µm, correspondant à 450 MOS/mm² en technologie 6 µm. D'autres exemples présentent des densités tout à fait comparables.

La productivité au niveau du dessin symbolique est très inégale selon les blocs. Néanmoins, en faisant une

moyenne sur des modules en logique câblée d'un micro-ordinateur totalisant 2700 MOS dont 700 ont été dessinés, la productivité au niveau dessin a été de 19 MOS/jour, compte tenu de l'assemblage et des vérifications. Si l'on tient compte d'une régularité de la logique câblée voisine de R = 5, on obtient le chiffre de 100 MOS/jour pour la productivité réelle. Il y a donc un accroissement de la productivité au niveau graphique d'un facteur 3 à 5 comparé aux 4-6 MOS dessinés par jour, tout en obtenant des densités tout à fait comparables sinon meilleures que pour les layouts manuels non orientés. Cette technique de layout a été utilisée pour un gros module de 3000 MOS en logique câblée, destiné à un circuit in-

Fig. 11

Plan directeur (a),

layout symbolique (b) et

layout géométrique (c)

d'un extrait d'un

compteur de

programme

Fig. 12 Microphotographies

- a Détail obtenu par un microscope électronique

- b Deux tranches d'un compteur de programme

- c Module de 3000 MOS en logique câblée

dustriel. La productivité s'est élevée à 25 MOS/jour par opérateur pour une densité de 1000 MOS/mm<sup>2</sup> en technologie 4 µm (fig. 12c).

Les microphotographies de la figure 12 représentent des parties de circuits intégrés selon la technique de layout proposée en technologie CEH CMOS

#### 5. Conclusion

La technique de layout proposée permet une augmentation non négli-

geable de la productivité au niveau graphique, tout en présentant des densités comparables aux conceptions manuelles non orientées. En outre, elle constitue une excellente base pour la synthèse automatique de circuits inté-

# Bibliographie

- 167...170.

- [6] J. Zahnd and A. Stauffer: Basic design methods for CMOS logic circuits with ordered layout. Ninth Eu-ropean Solid-State Circuits Conference, Lausanne (ESSCIRC '83). Digest of technical papers p. 171 174 p. 171...174.

- p. 171...174.

[7] D. Aubert a. o.: Computer-aided layout of distributed CMOS static descoders. Eighth European Solid-State Circuits Conference, Brussel 1982 (ESSCIRC '82). Digest of technical papers p. 90...93.

[8] F. Anceau and R. A. Reis: Complex integrated circuit design strategy. IEEE Journal of Solid-State Circuits 17(1982)3, p. 459...464.