**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 75 (1984)

Heft: 1

Artikel: Méthodes de synthèse des systèmes séquentiels asynchrones CMOS

**Autor:** Stauffer, A. / Zahnd, J.

**DOI:** https://doi.org/10.5169/seals-904330

## Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

## **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

## Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 01.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Méthodes de synthèse des systèmes séquentiels asynchrones CMOS

A. Stauffer, J. Zahnd

Tout système séquentiel asynchrone, défini par sa table d'états, admet des méthodes de synthèse directe de schémas à transistors CMOS. Ces méthodes, qui évitent l'usage intermédiaire de schémas logiques, permettent de concevoir des circuits statiques, des circuits dynamiques et des circuits semidynamiques. Les schémas logiques obtenus ultérieurement ne servent qu'à faciliter la compréhension du fonctionnement des circuits

Für jedes asynchrone sequentielle System, das durch seine Zustandstabelle definiert ist, gibt es Methoden zum direkten Entwerfen der Schaltungen mit CMOS-Transistoren, unter Umgehung des logischen Schemas. Diese Methoden gestatten es, statische, dynamische und halbdynamische Schaltungen zu entwerfen. Das nachträglich erhaltene logische Schema hat nur den Zweck, die Verständlichkeit der Funktionsweise der Schaltkreise zu erleichtern.

## 1. Circuit statique

1.1 Principe de synthèse

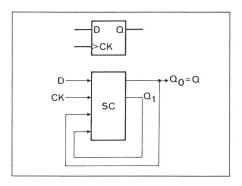

Rappelons qu'un système logique séquentiel asynchrone est par définition un système qui est formé en connectant une ou plusieurs sorties d'un système combinatoire à certaines de ses propres entrées, de façon à créer une ou plusieurs boucles de rétroaction. Aussi part-on, pour la synthèse d'un tel système, du modèle de la figure 1, où le système appelé SC est un système combinatoire supposé sans retard, et où les éléments formellement introduits sur les boucles de rétroaction sont des éléments de retard (ou délais) supposés tous égaux. La valeur des variables  $q_i$  à un instant t constitue l'état du système à cet instant, et la valeur des variables  $q_i^+$  constitue l'état futur. Ce dernier terme est justifié par l'hypothèse d'une même valeur △ pour tous les délais du modèle, en vertu de laquelle on aura, de façon générale:

$$q_{\mathbf{i}}(t+\triangle)=q_{\mathbf{i}}^{+}(t).$$

Il faut rappeler qu'il s'agit là d'un modèle très grossier, utilisé seulement comme modèle de départ d'un système qu'on se propose de réaliser. Lorsqu'on passe à la réalisation, les retards sur les boucles ne sont plus égaux, et d'autres retards apparaissent en général à l'intérieur du système combina-

$x_1$   $x_m$   $z_p$   $z_p$   $z_p$   $z_p$   $z_p$   $z_p$   $z_p$

Fig. 1

toire SC. On ne connaît guère de méthode de réalisation simple et directe, qui garantisse pour le système réalisé un fonctionnement logique conforme à celui du modèle de départ. On est obligé en général d'analyser le système construit et de le modifier au besoin. Nous nous bornerons ici à des exemples très simples, où nous obtiendrons des circuits connus qu'il ne sera pas nécessaire d'analyser.

La table de vérité du système combinatoire SC (fig. 1) est appelée la table d'états du système séquentiel asynchrone. Elle détermine l'état futur  $q^+$  =  $(q^+_1, ..., q^+_n)$  et la sortie  $z = (z_1, ..., z_p)$  en fonction de l'état présent  $q = (q_1, ..., q_n)$  et de l'entrée  $x = (x_1, ..., x_m)$ . Il arrive souvent qu'il n'y ait pas de variables de sortie  $z_i$  et que ce soient les variables  $q_i$  (ou certaines d'entre elles) qui soient prises comme variables de sortie du système.

Pratiquement, pour la phase de synthèse, il n'y a pas lieu d'introduire deux jeux de variables distincts  $q_i$  et  $q_i^+$ . On identifiera  $q_i$  et  $q_i^+$ , de sorte qu'à partir de la table d'états (table de vérité de SC) on obtiendra des équations de la forme

$$q_i = F_i(x_1, ..., x_m, q_{1,..., q_n})$$

qui par cette forme même impliquent des boucles de rétroaction.

Ces équations seront tirées de la table d'états en appliquant à celle-ci les méthodes propres aux systèmes combinatoires. On obtiendra pour chacune des variables  $q_i$  les expressions  $n(q_i)$  et  $p(q_i)$  des réseaux n et p correspondants. Toutefois, il faut imposer ici une contrainte qui découle de façon évidente de la structure des circuits CMOS, à savoir que

- 1. les variables  $q_j$  (j = 1,..., n) ne doivent pas figurer dans les expressions  $n(q_i)$  et  $p(q_i)$  sous forme complémentée  $(\bar{q}_i)$ , mais seulement sous forme vraie  $(q_i)$ , et

- 2. la variable  $q_i$  ne doit pas figurer du tout, ni sous forme vraie ni sous for-

Ce travail est partiellement financé par la Commission pour l'encouragement de la recherche scientifique, crédit 1085.1.

## Adresse des auteurs

A. Stauffer et J. Zahnd, Laboratoire de systèmes logiques, EPFL, 16, chemin de Bellerive, 1007 Lausanne.

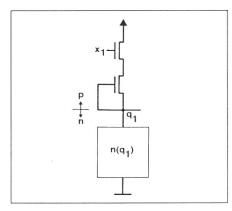

Fig. 2

me complémentée, dans les expressions  $n(q_i)$  et  $p(q_i)$ .

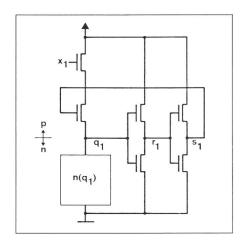

La raison de ces interdictions est simple. Supposons que l'on ait obtenu par exemple pour  $p(q_1)$  une expression de la forme  $x_1q_1 + ...$  Une telle expression se traduirait par le schéma «douteux» de la figure 2. Pour respecter l'interdiction, il faut introduire une variable  $r_1 = \bar{q}_1$  et une variable  $s_1 = \bar{r}_1$ , ce qui revient à remplacer le schéma de la figure 2 par celui de la figure 3.

L'interdiction d'utiliser des variables complémentées implique seulement qu'on doit écrire explicitement les équations de réseaux des inverseurs qui seraient implicites autrement. Ainsi, au lieu d'écrire  $n(q_2) = x\bar{q}_3$ , on doit écrire  $n(q_2) = xr_3$ , et ajouter les expressions  $p(r_3) = q_3$ ,  $n(r_3) = q_3$  de l'inverseur qui réalisera  $r_3 = \bar{q}_3$ .

On voit qu'en général, la structure bouclée illustrée par la figure 1 imposera pour la plupart des fonctions  $q_i$  la réalisation d'une fonction complémentaire  $r_i$ . Il y aura lieu dans ce cas d'examiner si l'une des deux fonctions est plus avantageuse à réaliser à partir de la table d'états, l'autre étant réalisée par inversion. La méthode qui découle de ces considérations est énoncée au paragraphe suivant.

Fig. 3

00 01 11 00.1 0 0 00,0 01,0 10,1 01 01.1 01,0 11,0 00,1 01,1 100 0,00 10,1 10 9192

Fig. 4

### 1.2 Méthode

A partir de la table d'état d'un système séquentiel asynchrone tel que celui de la figure 1:

- Ecrire des équations de réseaux n et p pour chacune des fonctions q<sub>1</sub>, ..., q<sub>n</sub>, z<sub>1</sub>, ..., z<sub>p</sub> en appliquant (sans restriction) les méthodes vues pour les systèmes combinatoires [1].

- Eliminer dans ces équations les variables complémentées q

i, en remplaçant q

i par n

i et en ajoutant les équations d'inverseur n(n) = q

i et p(n) = q

i.

- Si une variable q<sub>i</sub> figure encore (sous forme vraie) dans les expressions n(q<sub>i</sub>), p(q<sub>i</sub>), éliminer q<sub>i</sub> dans ces expressions en remplaçant q<sub>i</sub> par s<sub>i</sub>, et ajouter

- les équations d'inverseur  $n(r_i) = q_i$ ,  $p(r_i) = q_i$  si elles ne sont pas déjà dans la liste;

- les équations d'inverseur  $n(s_i) = r_i$  et  $p(s_i) = r_i$ .

- 4. (facultatif) Pour chaque paire  $q_i$ ,  $r_i$  examiner s'il peut être avantageux du point de vue du nombre de transistors (ou du critère d'optimisation «surface du schéma d'implantation» qui sera introduit plus loin) de remplacer les équations de  $q_i$  et les équations d'inverseur  $n(r_i) = q_i$ ,  $p(r_i) = q_i$  par des équations de réseaux tirées de la table d'états pour  $r_i$  (réalisation de la fonction inverse de  $q_i$  à partir de la table d'états) et par les équations d'inverseur  $n(q_i) = r_i$ ,  $p(q_i) = r_i$ .

- 5. Pour les variables d'entrée  $x_i$  qui figurent sous forme complémentée dans les équations obtenues, et dont on ne dispose pas sous cette forme, ajouter les équations d'inverseur  $n(\bar{x_i}) = x_i$  et  $p(\bar{x_i}) = x_i$ .

#### 1.3 Exemple:

discriminateur du sens de rotation

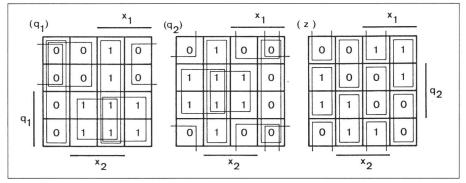

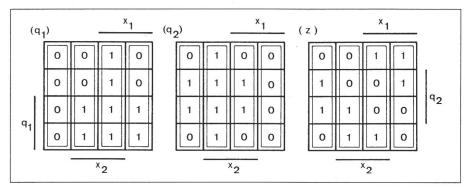

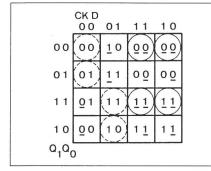

La table d'états de la figure 4 définit l'état futur  $q_1^+$   $q_2^+$  et la sortie z d'un discriminateur du sens de rotation [2, pp. 166...171]. Une première solution est choisie dans la figure 5, où l'on a séparé les tables de Karnaugh relatives à  $q_1$ ,  $q_2$  et z. Cette solution se traduit par les équations

$$q_{1} = [\bar{x}_{1}\bar{x}_{2} + \bar{x}_{1}\bar{q}_{1} + \bar{x}_{2}\bar{q}_{1}]0 + [x_{1}x_{2} + x_{1}q_{1} + x_{2}q_{1}]1$$

(1)

$$q_2 = [x_1 \bar{x}_2 + x_1 \bar{q}_2 + \bar{x}_2 \bar{q}_2] 0 + [\bar{x}_1 x_2 + \bar{x}_1 q_2 + x_2 q_2] 1$$

(2)

$$z = [\bar{x}_1 \bar{x}_2 \bar{q}_2 + \bar{x}_1 x_2 \bar{q}_1 + x_1 \bar{x}_2 q_1 + x_1 x_2 q_2] 0 + [\bar{x}_1 \bar{x}_2 q_2 + \bar{x}_1 x_2 q_1 + x_1 \bar{x}_2 \bar{q}_1 + x_1 x_2 \bar{q}_2] 1$$

(3)

dont on tire les équations des réseaux:

$$n(q_1) = p(q_1) = \bar{x}_1 \bar{x}_2 + \bar{x}_1 \bar{q}_1 + \bar{x}_2 \bar{q}_1 \tag{4}$$

$$n(q_2) = p(q_2) = x_1 \bar{x}_2 + x_1 \bar{q}_2 + \bar{x}_2 \bar{q}_2$$

(5)

$$n(z) = \bar{x}_1 \bar{x}_2 \bar{q}_2 + \bar{x}_1 x_2 \bar{q}_1 + x_1 \bar{x}_2 q_1 + x_1 x_2 q_2$$

(6)

$$p(z) = x_1 x_2 \bar{q}_2 + x_1 \bar{x}_2 \bar{q}_1 + \bar{x}_1 x_2 q_1 + \bar{x}_1 \bar{x}_2 q_2$$

(7)

Nous avons ainsi exécuté la première étape de la méthode décrite au paragraphe précédent. On peut effectuer les étapes 2 et 3 d'un seul coup, ce qui donne:

$$n(q_1) = p(q_1) = \bar{x}_1 \bar{x}_2 + \bar{x}_1 r_1 + \bar{x}_2 r_1 \tag{8}$$

$$n(q_2) = p(q_2) = x_1 \bar{x}_2 + x_1 r_2 + \bar{x}_2 r_2 \tag{9}$$

$$n(z) = \bar{x}_1 \bar{x}_2 r_2 + \bar{x}_1 x_2 r_1 + x_1 \bar{x}_2 q_1 + x_1 x_2 q_2$$

(10)

$$p(z) = x_1 x_2 r_2 + x_1 \tilde{x}_2 r_1 + \tilde{x}_1 x_2 q_1 + \tilde{x}_1 \tilde{x}_2 q_2$$

(11)

$n(r_1) = p(r_1) = q_1$

(12)

$$n(r_2) = p(r_2) = q_2$$

(13)

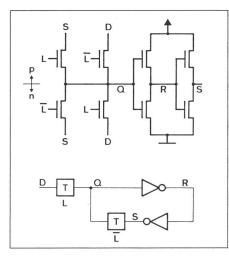

Fig. 5

Fig. 6

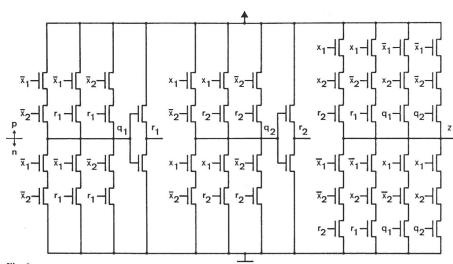

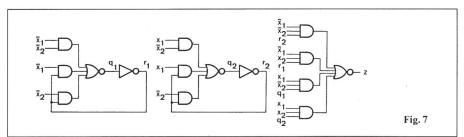

Ces équations se traduisent par le schéma électronique de la figure 6. Pour obtenir le schéma logique de la figure 7, il suffit de partir des relations (8) à (13) et de reconstituer les équations du discriminateur:

$$n(q_2) = p(q_2) = [\bar{x}_1 \bar{x}_2 + x_1 x_2] q_2 + x_1 \bar{x}_2$$

(23)

$$n(z) = [\bar{x}_1 \bar{x}_2]^{\dagger} q_2 + [\bar{x}_1 x_2] q_1 + [x_1 \bar{x}_2] \bar{q}_1 + [x_1 x_2] \bar{q}_2$$

(24)

$$p(z) = [x_1 x_2] q_2 + [x_1 \bar{x}_2] q_1$$

+  $[\bar{x}_1 x_2] \bar{q}_1 + [\bar{x}_1 \bar{x}_2] \bar{q}_2$  (25)

Selon les étapes 2 et 3 de la méthode, on transforme ce système d'équations en

$$n(q_1) = p(q_1) = [\bar{x}_1 x_2 + x_1 \,\bar{x}_2] \, s_1 + \bar{x}_1 \bar{x}_2 \qquad (26)$$

$$n(q_2) = p(q_2) = [\bar{x}_1\bar{x}_2 + x_1 x_2] s_2 + x_1\bar{x}_2$$

(27)

$$n(z) = [\bar{x}_1 \bar{x}_2] q_2 + [\bar{x}_1 x_2] q_1 + [x_1 \bar{x}_2] r_1 + [x_1 x_2] r_2$$

(28)

$$p(z) = [x_1 x_2] q_2 + [x_1 \bar{x}_2] q_1 + [\bar{x}_1 x_2] r_1 + [\bar{x}_1 \bar{x}_2] r_2$$

(29)

$$n(r_1) = p(r_1) = q_1$$

(30)

$$n(s_1) = p(s_1) = r_1$$

(31)

$$n(r_2) = p(r_2) = q_2$$

(32)

$$n(s_2) = p(s_2) = r_2$$

(33)

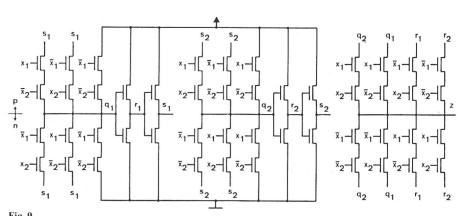

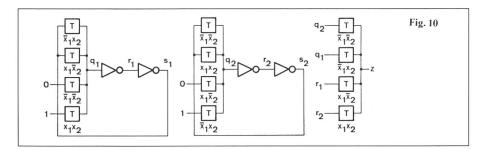

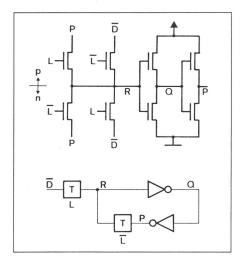

La matérialisation de ces équations conduit au schéma électronique de la figure 9. Le schéma logique du discri-

$$q_{1} = [\bar{x}_{1}\bar{x}_{2} + \bar{x}_{1} r_{1} + \bar{x}_{2}r_{1}] 0 + [x_{1}x_{2} + x_{1}\bar{r}_{1} + x_{2}\bar{r}_{1}] 1$$

(14)

$$q_2 = [x_1 \bar{x}_2 + x_1 r_2 + \bar{x}_2 r_2] 0 + [\bar{x}_1 x_2 + \bar{x}_1 \bar{r}_2 + x_2 \bar{r}_2] 1$$

(15)

$$z = [\bar{x}_1 \bar{x}_2 r_2 + \bar{x}_1 x_2 r_1 + x_1 \bar{x}_2 q_1 + x_1 x_2 q_2] 0 + [\bar{x}_1 \bar{x}_2 \bar{r}_2 + \bar{x}_1 x_2 \bar{r}_1 + x_1 \bar{x}_2 \bar{q}_1 + x_1 x_2 \bar{q}_2] 1$$

(16)

$$r_1 = [q_1] \, 0 + [\bar{q}_1] \, 1$$

(17)

$$r_2 = [q_2] 0 + [\bar{q}_2] 1$$

(18)

Une deuxième solution est présentée dans la figure 8. Elle donne d'abord les équations

$$q_1 = [\bar{x}_1 x_2 + x_1 \bar{x}_2] q_1 + [\bar{x}_1 \bar{x}_2] 0 + [x_1 x_2] 1$$

(19)

$$q_2 = [\bar{x}_1 \bar{x}_2 + x_1 x_2] q_2 + [x_1 \bar{x}_2] 0 + [\bar{x}_1 x_2] 1$$

(20)

$$z = [\bar{x}_1 \bar{x}_2] q_2 + [\bar{x}_1 x_2] q_1 + [x_1 \bar{x}_2] \bar{q}_1 + [x_1 x_2] \bar{q}_2$$

(21)

puis les équations des réseaux:

$$n(q_1) = p(q_1) = [\bar{x}_1 x_2 + x_1 \bar{x}_2] q_1 + \bar{x}_1 \bar{x}_2$$

(22)

Fig. 8

(36)

re de Q:

n(R) = p(R) = Q

minateur (fig. 10) découle des équations reconstituées:

$$q_1 = [\bar{x}_1 x_2 + x_1 \bar{x}_2] s_1 + [\bar{x}_1 \bar{x}_2] 0 + [x_1 x_2] 1$$

(34)

$$q_2 = [\bar{x}_1 \bar{x}_2 + x_1 x_2] s_2 + [x_1 \bar{x}_2] 0 + [\bar{x}_1 x_2] 1$$

(35)

$$z = [\bar{x}_1 \bar{x}_2] \ q_2 + [\bar{x}_1 x_2] \ q_1$$

$$+ [x_1 \bar{x}_2] \ r_1 + [x_1 x_2] \ r_2$$

$$r_1 = [q_1] \ 0 + [\bar{q}_1] \ 1 \tag{37}$$

$$s_1 = [r_1] \ 0 + [\bar{r}_1] \ 1$$

(38)

$$r_2 = [q_2] \, 0 + [\bar{q}_2] \, 1 \tag{39}$$

$$s_2 = [r_2] 0 + [\bar{r}_2] 1$$

(40)

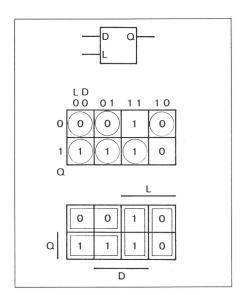

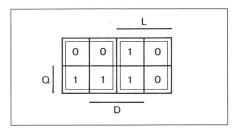

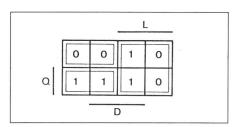

## 1.4 Application: élément de mémoire D

L'élément de mémoire *D* (en anglais: latch) est défini par sa table d'états (fig. 11). Opérée dans la table de Karnaugh, la simplification de la fonction réalisée par cet élément conduit à l'équation

$$Q = [L\bar{D} + \bar{L}\bar{Q}]0 + [LD + \bar{L}Q]1$$

(41)

Celle-ci entraîne les équations des réseaux suivantes, où l'on a d'emblée

Fig. 11

$n(Q) = L \bar{D} + \bar{L} R \tag{42}$   $p(Q) = \bar{L} \bar{D} + L R \tag{43}$

introduit la variable R complémentai-

$$p(Q) - LD + LR \tag{43}$$

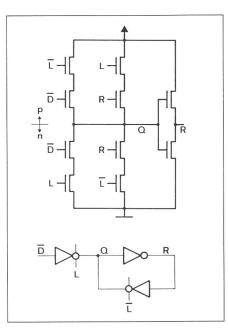

Les relations (42) à (44) correspondent au schéma électronique de la figure 12. Pour obtenir le schéma logique de la figure 12, on reconstitue les équations de l'élément de mémoire:

$$Q = [L \bar{D} + \bar{L} R] 0 + [L D + \bar{L} \bar{R}] 1$$

(45)

=  $[L] ([\bar{D}] 0 + [D] 1) + [\bar{L}] ([R] 0 + [\bar{R}] 1)$

$$R = [Q] 0 + [\bar{Q}] 1 \tag{46}$$

Comme il est suggéré au point 4 de la méthode (§ 1.2), on peut, à partir de la table de Karnaugh (fig. 11), former d'abord des équations de réseaux pour la variable R, à savoir:

$$R = [L D + \bar{L} \bar{R}] 0 + [L \bar{D} + \bar{L} R] 1$$

(47)

Fig. 12

Fig. 13

(44)

d'où

$$n(R) = LD + \bar{L}Q \tag{48}$$

$$p(R) = \bar{L}D + LQ \tag{49}$$

$$n(Q) = p(Q) = R \tag{50}$$

Le schéma électronique de la figure 13 matérialise ces relations. Le schéma logique de l'élément de mémoire découle des équations reconstituées:

$$R = [L D + \bar{L} Q] 0 + [L \bar{D} + \bar{L} \bar{Q}] 1$$

(51)

=  $[L]([D] 0 + [\bar{D}] 1) + [\bar{L}]([Q] 0 + [\bar{Q}] 1)$

$$Q = [R] 0 + [\tilde{R}] 1 \tag{52}$$

Ces schémas présentent un avantage par rapport aux schémas précédents (fig. 12) si l'on ne dispose pas de la variable  $\bar{D}$ . On constate qu'il s'agit en fait du même circuit, utilisé de manière différente.

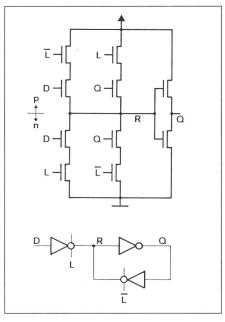

Une autre solution est déterminée par la figure 14. Elle entraîne soit les

Fig. 14

Fig. 15

équations (53) à (60) puis la figure 15, soit les équations (61) à (68) liées à la figure 16. Ici encore, on aboutit à un même circuit utilisé de deux manières différentes.

$$Q = [L] D + [\bar{L}] Q \tag{53}$$

$$n(Q) = [L]D + [\bar{L}]S \tag{54}$$

$$p(Q) = [\bar{L}] D + [L] S \tag{55}$$

$$n(R) = p(R) = Q \tag{56}$$

$$n(S) = p(S) = R \tag{57}$$

$$Q = [L] D + [\bar{L}] S \tag{58}$$

$$R = [Q] 0 + [\bar{Q}] 1 \tag{59}$$

$$S = [R] 0 + [\bar{R}] 1 \tag{60}$$

$$R = [L] \bar{D} + [\bar{L}] R \tag{61}$$

Fig. 16

$$n(R) = [L] \bar{D} + [\bar{L}] P \tag{62}$$

$$p(R) = [\bar{L}] D + [L] P \tag{63}$$

$$n(Q) = p(Q) = R \tag{64}$$

$$n(P) = p(P) = Q \tag{65}$$

$$R = [L] \bar{D} + [\bar{L}] P \tag{66}$$

$$Q = [R] 0 + [\bar{R}] 1 \tag{67}$$

$$P = [Q] 0 + [\bar{Q}] 1 \tag{68}$$

Fig. 17

Fig. 18

Enfin, une troisième solution est choisie dans la figure 17. Elle donne lieu aux équations (69) à (74) puis aux schémas de la figure 18. Si l'on compare ces schémas avec ceux de la figure 15, on retrouve l'équivalence fonctionnelle qui existe entre un inverseur suivi d'une porte de transmission et un inverseur à sortie 3-états.

$$Q = [L] D + [\bar{L} \bar{Q}] 0 + [\bar{L} Q] 1$$

(69)

Fig. 19

Fig. 20

$$n(Q) = [L] D + \bar{L} R \tag{70}$$

$$p(Q) = [\bar{L}] D + L R \tag{71}$$

$$n(R) = p(R) = Q \tag{72}$$

$$Q = [L] D + [\bar{L} R] 0 + [\bar{L} \bar{R}] 1$$

$$= [L] D + [\bar{L}] ([R] 0 + [\bar{R}] 1)$$

(73)

$$R = [Q] 0 + [\bar{Q}] 1 \tag{74}$$

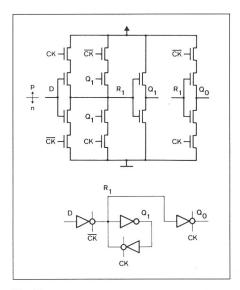

## 1.5 Application: bascule bistable D

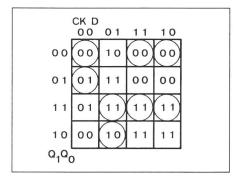

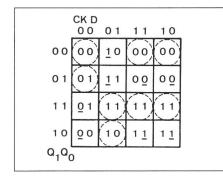

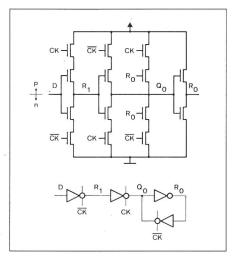

La bascule bistable D (en anglais: D flip-flop) de la figure 19 correspond à un système combinatoire SC muni de deux boucles de rétroaction. La table d'états de la figure 20 définit l'état futur  $Q^+_1 Q^+_0$  de cette bascule. Si l'on choisit la solution proposée dans les tables de Karnaugh de la figure 21 pour déterminer les fonctions  $R_1$  et  $R_0$  inverses de  $Q_1$  et  $Q_0$ , on obtient les équations

$$R_{1} = [\overline{CK} D + CK \overline{R}_{1}] 0 + [\overline{CK} \overline{D} + CK R_{1}] 1$$

(75)

$$R_{0} = [CK \ \bar{R}_{1} + \overline{CK} \ \bar{R}_{0}] \ 0$$

$$+ [CK \ R_{1} + \overline{CK} R_{0}] \ 1$$

(76)

puis les équations des réseaux:

Fig. 21

$$n(R_1) = \overline{CK} D + CK Q_1 \tag{77}$$

$$p(R_1) = CKD + \overline{CK}Q_1 \tag{78}$$

$$n(Q_1) = p(Q_1) = R_1$$

(79)

$$n(R_0) = CK Q_1 + \overline{CK} Q_0 \tag{80}$$

$$p(R_0) = \overline{CK} Q_1 + CK Q_0 \tag{81}$$

$$n(Q_0) = p(Q_0) = R_0$$

(82)

et les équations reconstituées:

$$R_{1} = [\overline{CK}]([D]0 + [\overline{D}]1) + [CK]([Q_{1}]0 + [\overline{Q}_{1}]1)$$

(83)

$$Q_1 = [R_1] 0 + [\bar{R}_1] 1 \tag{84}$$

$$R_0 = [CK]([Q_1]0 + [\bar{Q}_1]1) + [\bar{C}K]([Q_0]0 + [\bar{Q}_0]1)$$

(85)

$$Q_0 = [R_0] 0 + [\bar{R}_0] 1 \tag{86}$$

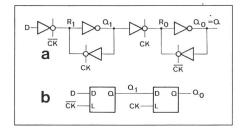

La matérialisation des relations (83) à (86) conduit au schéma logique du circuit (fig. 22a), dans lequel on reconnaît deux éléments de mémoire *D* interconnectés conformément à la figure 22b. En réalisant ces éléments sous l'une ou l'autre des formes étudiées au paragraphe précédent, on obtient un ensemble de bascules bistables *D* dont le fonctionnement obéit à la table d'états de la figure 20.

## 2. Circuit dynamique

### 2.1 Principe de fonctionnement

Un circuit séquentiel dynamique [3] est un système séquentiel asynchrone

Fig. 22

Fig. 23

dont le fonctionnement repose sur l'emploi d'un signal de référence périodique. La fréquence de ce signal doit être suffisante pour permettre aux capacités du circuit d'assurer la conservation temporaire de l'état logique 0 ou de l'état logique 1 de certaines variables lors du blocage de leurs réseaux n et p. Les transitions de 1 à 0 ou de 0 à 1 des variables sont réalisées par conduction de leurs réseaux n ou de leurs réseaux p.

## 2.2 Méthode

A partir de la table d'états du système séquentiel, la simplification des fonctions du circuit dynamique correspondant s'effectue de la manière suivante:

- 1. souligner les variables instables de la table;

- appliquer la méthode propre aux circuits séquentiels statiques en considérant que

- chacun des 0 et des 1 non soulignés peut également correspondre à un état à haute impédance  $\nabla$ ;

- 3. vérifier que pour toute paire d'états stables vis-à-vis du signal de référence, chacune des variables appartient au moins à un bloc de 0, à un bloc de 1 ou à un bloc qui dépend d'une variable; modifier au besoin la synthèse pour satisfaire cette condition.

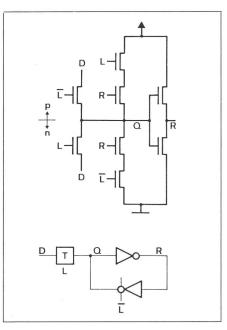

## 2.3 Application: bascule bistable D

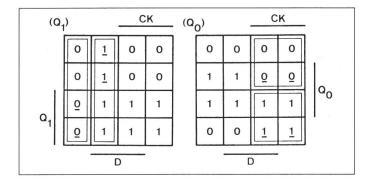

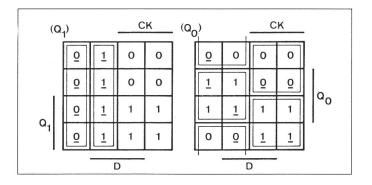

La table d'états de la figure 23 définit l'état futur  $Q_1^+ Q_0^+$  de la bascule bistable D dynamique. Dans cette table, on a souligné les variables instables et symbolisé le caractère dynamique de la bascule en regard du signal de référence CK par l'encerclement discontinu des états stables.

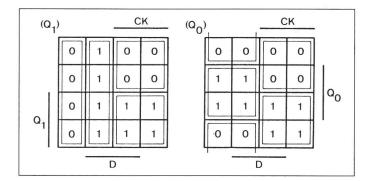

Opérée dans les tables de Karnaugh de la figure 24, la simplification des fonctions  $R_1$  (inverse de  $Q_1$ ) et  $Q_0$  conduit aux équations

$$R_1 = [\overline{CK} D] 0 + [\overline{CK}\overline{D}] 1 \tag{87}$$

$$Q_0 = [CK R_1] 0 + [CK \bar{R}_1] 1$$

(88)

puis aux équations des réseaux:

$$n(R_1) = \overline{CK} D \tag{89}$$

$$p(R_1) = CKD (90)$$

$$n(Q_0) = CK R_1 (91)$$

$$p(Q_0) = \overline{CK} R_1 \tag{92}$$

Les relations (89) à (92) correspondent au schéma électronique de la figure 25. Pour obtenir le schéma logique de la figure 25, on reconstitue les équations de la bascule bistable *D* dynamique:

$$R_1 = [\overline{CK}]([D]0 + [\overline{D}]1) \tag{93}$$

$$Q_0 = [CK]([R_1]0 + [\bar{R}_1]1)$$

(94)

Fig. 24

Fig. 25

## 3. Circuit semi-dynamique

## 3.1 Principe de fonctionnement

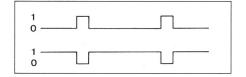

Un circuit séquentiel semi-dynamique est un système séquentiel asynchrone dont le fonctionnement repose sur l'emploi d'un signal de référence impulsionnel. Les impulsions positives  $(0 \rightarrow 1 \rightarrow 0)$  ou négatives  $(1 \rightarrow 0 \rightarrow 1)$  de ce signal (fig. 26) doivent être suffisamment brèves pour permettre aux capacités du circuit d'assurer la conservation temporaire de l'état logique 0 ou 1 de certaines variables lors du blocage de leurs réseaux n et p. Les transitions sont réalisées par conduction de leurs réseaux n ou de leurs réseaux p.

Fig. 26

### 3.2 Méthode

Le signal de référence divise la table d'états du système séquentiel en deux parties: une partie statique et une partie dynamique qui correspondent respectivement à l'absence et à la présence d'une impulsion. La simplification des fonctions du circuit semi-dynamique s'opère à partir de cette table ainsi divisée:

- 1. souligner les variables instables de la table;

- 2. souligner les variables des états stables de la partie statique de la table;

- 3. appliquer la méthode propre aux circuits séquentiels statiques en considérant que chacun des 0 ou des 1 non soulignés de la

Fig. 27

Fig. 28

table peut également correspondre à un état à haute impédance  $\nabla$ .

## 3.3 Application: bascule bistable D

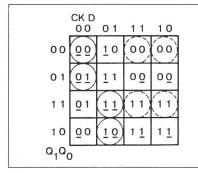

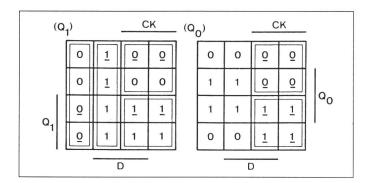

La bascule bistable *D* admet deux tables d'états distinctes (fig. 27 et 28) selon que le signal de référence *CK* présente des impulsions positives ou négatives. Dans ces tables, caractérisées par l'encerclement discontinu des états stables de la partie dynamique, on a souligné l'ensemble des variables instables et les variables des états stables de la partie statique.

La simplification des fonctions  $R_1$  (inverse de  $Q_1$ ) et  $Q_0$  de la bascule D dont le signal CK présente des impulsions positives (fig. 27), passe par les tables de Karnaugh de la figure 29 et conduit aux équations

$$R_1 = [\overline{CK} D] 0 + [\overline{CK}\overline{D}] 1 \tag{95}$$

Fig. 30

$$Q_0 = [\overline{CK} \ \overline{Q}_0 + CK R_1] 0 + [\overline{CK} \ Q_0 + CK \overline{R}_1] 1$$

(96)

puis aux équations des réseaux:

$$n(R_1) = \overline{CK} D \tag{97}$$

$$p(R_1) = CK D (98)$$

$$n(Q_0) \overline{CK} R_0 + CK R_1 \tag{99}$$

$$p(Q_0) = CK R_0 + \overline{CK} R_1 \tag{100}$$

$$n(R_0) = p(R_0) = Q_0 (101)$$

où l'on a d'emblée introduit la variable  $R_0$  complémentaire de  $Q_0$ . Le schéma électronique de la figure 30 matérialise les relations (97) à (101). Le schéma logique (fig. 30) découle des équations reconstituées:

$$R_1 = [\overline{CK}]([D]0 + [\overline{D}]1) \tag{102}$$

$$Q_0 = [CK]([R_1]0 + [\bar{R}_1]1) + [CK]([R_0]0 + [\bar{R}_0]1)$$

(103)

Pour la bascule *D* dont le signal *CK* présente des impulsions négatives (fig.

Fig. 29

Fig. 31

28), la simplification des fonctions  $R_1$  et  $Q_0$  (fig. 31) détermine les équations

$$p(Q_0) = \overline{CK} R_1 \tag{110}$$

$$R_1 = [\overline{CK} D + CK \bar{R}_1] 0 + [\overline{CK} \bar{D} + CK R_1] 1$$

(104)

$$R_{1} = [\overline{CK}]([D]0 + [\bar{D}]1) + [CK]([Q_{1}]0 + [\bar{Q}_{1}]1)$$

(111)

$$Q_0 = [CK R_1] 0 + [CK \bar{R}_1] 1$$

(105)

$$Q_1 = [R_1] 0 + [\bar{R}_1] 1$$

(112)

$$Q_0 = [CK]([R_1]0 + [\bar{R}_1]1)$$

(113)

$$n(R_1) = \overline{CK} D + CK Q_1$$

(109)

$$p(R_1) = CKD + \overline{CK}Q_1 \qquad (107)$$

$$n(Q_1) = p(Q_1) = R_1$$

(108)

$$n(Q_0) = CK R_1$$

puis les schémas électronique et logique de la figure 32.

Si l'on compare les schémas logiques des bascules *D* semi-dynamiques (fig. 30 et 32) avec ceux des bascules statique (fig. 22) et dynamique (fig. 25), on reconnaît, dans les deux cas, une

Fig. 32

demi-bascule statique précédée ou suivie d'une demi-bascule dynamique.

## Bibliographie

- [1] A. Stauffer: Méthodes de synthèse des systèmes combinatoires CMOS. Bull. ASE/UCS 75(1984)1, p. 000...000.

- [2] D. Mange: Analyse et synthèse des systèmes logiques. Traité d'électricité de l'EPFL. Vol. V. St-Saphorin, Editions Georgi, 1978.

- [3] E. Vittoz and H. Oguey: Complementary dynamic M.O.S. logic circuits. Electronics Letters 9(1973)4, p. 77...78.