|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 74 (1983)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 5                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Synthèse automatique de circuits CMOS                                                                                                                                                                                     |

| <b>Autor:</b>       | Martin, J. C. / Zinszner, R. / Aubert, D.                                                                                                                                                                                 |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-904770">https://doi.org/10.5169/seals-904770</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Synthèse automatique de circuits CMOS

J. C. Martin, R. Zinszner, D. Aubert, C. Piguet

Présentation de deux méthodes de conception de circuits CMOS et des premiers résultats obtenus avec les programmes de génération automatique du layout. La première méthode est basée sur une description symbolique et sans dimensions du circuit alors que la deuxième utilise une structure ordonnée (matricielle et orientée) du layout.

Es werden zwei Methoden für den Entwurf von CMOS-Schaltungen vorgestellt und erste Resultate der Programme für die automatische Auslegung gezeigt. Die erste Methode beruht auf einer symbolischen Beschreibung der Schaltung, ohne Dimensionen, während die zweite eine geordnete Struktur der Anordnung (orientierte Matrix) verwendet.

## 1. Introduction

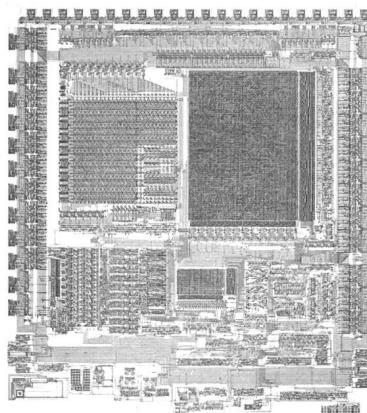

Concevoir un circuit intégré, c'est créer un ensemble de plans de masques ou layout. La description physique de ce layout contient principalement des rectangles et permet la fabrication automatique des masques. Cette base de données physique est volumineuse pour des circuits complexes comme le montre l'exemple de layout de la figure 1. Une hiérarchie permet de traiter un nombre limité d'éléments lors de la conception et de réaliser des programmes efficaces même pour des circuits complexes. Le tableau I montre un exemple de hiérarchie pour la conception de circuits.

Hiérarchie pour la conception de circuits complexes

Tableau I

| Niveau        | Elements    | Ensemble |

|---------------|-------------|----------|

| 1 Physique    | Rectangles  | Layout   |

| 2 Symbolique  | Transistors | Circuit  |

| 3 Fonctionnel | Modules     | Système  |

La première génération des outils de conception assistée par ordinateur (C.A.O.) correspond au niveau physique du tableau: un système graphique permet de manipuler les rectangles du layout. Nous présentons ci-

Fig. 1 Exemple d'un layout d'un microprocesseur

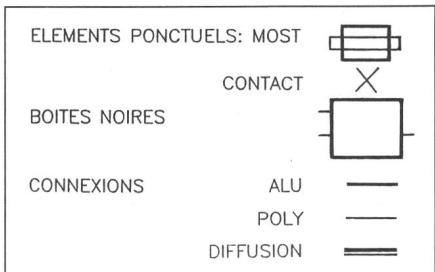

Fig. 2 Exemple de symboles

Il faut noter que ces symboles sont, en réalité, présents en différentes couleurs.

Poly = Silicium polycristallin

dessous les deuxième et troisième générations correspondant aux niveaux symbolique et fonctionnel. Tous les programmes et principes présentés sont adaptés à une technologie CMOS.

## 2. Layout symbolique et sans dimensions

LA CAO 2<sup>e</sup> génération simplifie le travail interactif de conception du circuit sur un écran graphique. D'abord une représentation symbolique des éléments remplace les rectangles du layout physique. Ensuite un dessin sans dimensions est généré: les éléments sont placés et connectés sans souci de métrique. Un programme transforme automatiquement les symboles en rectangles et effectue un déplacement des éléments connectés (tassement ou expansion) jusqu'à ce que les règles dimensionnelles minimum soient respectées.

La figure 2 montre quelques exemples de symboles, pour des éléments ponctuels (sans dimensions lors de l'édition), un élément prédéfini (boîte noire ou cellule) et des connexions qui sont des lignes extensibles.

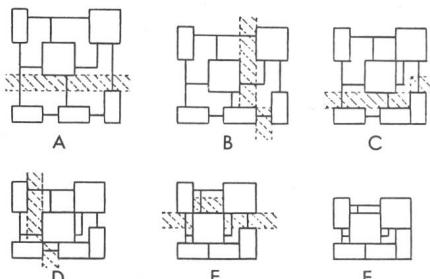

Un exemple d'un tel programme est CABBAGE [1], provenant de l'Université de Californie. La figure 3 est un exemple de traitement par CABBAGE de six boîtes noires connectées. Les différentes étapes de la compaction, de

Conférence présentée lors du «Meeting 1982 on Computer Aided Design (CAD)» organisé par IEEE Swiss Section, Chapter on Solid State Devices and Circuits, le 19 octobre 1982, à Berne.

Ce travail est partiellement financé d'une part par la Commission pour l'Encouragement des Recherches Scientifiques en Suisse, Crédit 1119, et d'autre part par le Centre Electronique Horloger à Neuchâtel, LGZ Landis & Gyr Zug AG à Zug et la Fondation Suisse pour la Recherche en Microtechnique à Neuchâtel.

### Adresse des auteurs

J. C. Martin, R. Zinszner, D. Aubert, C. Piguet, Centre Electronique Horloger S.A., 2000 Neuchâtel 7.

Fig. 3 Exemple de traitement d'un circuit par CABBAGE[1]

A à F, montrent que l'algorithme ne traite qu'une seule dimension à la fois et que par passes successives horizontales et verticales, on obtient un layout de surface réduite.

Un programme semblable est en cours de réalisation pour une technologie CMOS<sup>1)</sup>. En plus des éléments définis à figure 2, la notion de surface a été ajoutée pour représenter le caisson spécifique à la technologie CMOS. Une telle surface contient d'autres éléments et a une forme extensible. Les étapes successives de la conception d'un petit circuit et de la conversion de

la forme symbolique au layout sont données à la figure 4. Le schéma logique (4a) est traduit manuellement avec des MOST complémentaires (4b), puis dessiné symboliquement sur un écran graphique interactif (4c) grâce à un éditeur. Toutes les opérations suivantes sont exécutées automatiquement, la transformation en rectangles des éléments symboliques (4d) puis l'introduction des règles de plans de masques spécifiques à un fabricant, horizontalement et verticalement (4e et 4f). Le résultat final est le layout physique (fig. 4g) composé de rectangles et

Fig. 4 Exemple de layout symbolique et de compaction

- a Schéma logique

- b Schéma électrique, technologie CMOS

- c Schéma symbolique

- d Traduction automatique en layout

- e, f Introduction des règles de layout horizontales et verticales

- g Layout final

| ELEMENT | CROISEMENT | MOST | CONTACT |

|---------|------------|------|---------|

| SYBOLLE | +          | ○    | *       |

| LAYOUT  |            |      |         |

| CONTACT | CROISEMENT | LIAISON | ANCRAGE |

|---------|------------|---------|---------|

| SYBOLLE | *          | +       | -       |

| LAYOUT  |            |         |         |

| ELEMENT | CONTACT | LIAISON | LIAISON |

|---------|---------|---------|---------|

| SYBOLLE | *       | -       |         |

| LAYOUT  |         |         |         |

| ELEMENT | ANCRAGE | MOST | CONTACT |

|---------|---------|------|---------|

| SYBOLLE | *       | ○    | *       |

| LAYOUT  |         |      |         |

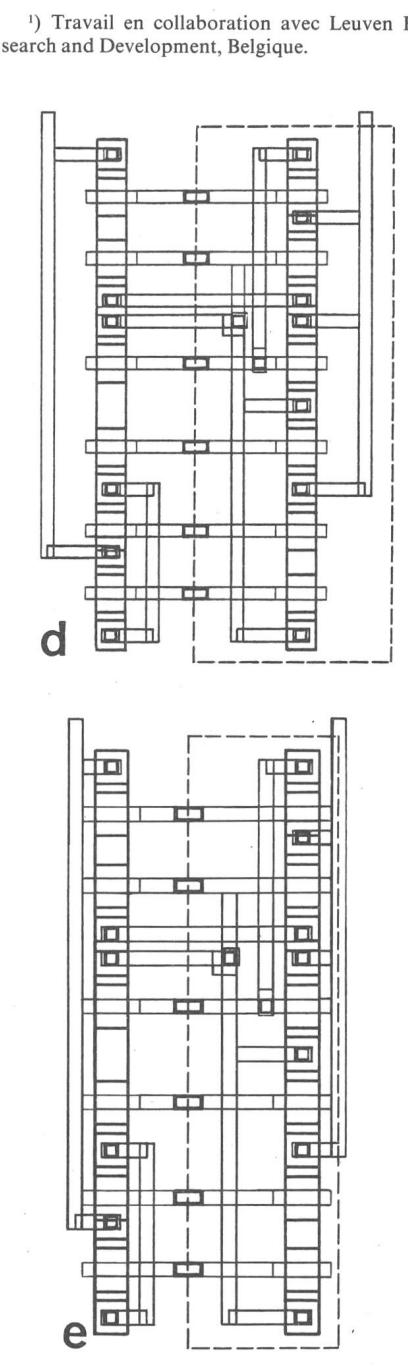

Fig. 5 Ensemble de microcellules

MOST Metal oxide semiconductor transistor

Connexion par diffusion

Connexion métallique

Connexion en silicium polycristallin

conforme aux règles technologiques d'un fabricant.

Plusieurs améliorations de l'algorithme de traitement ont été apportées en vue d'accélérer le calcul et d'améliorer le résultat. Citons en particulier la notion de porte, qui permet au point de connexion d'une liaison sur une boîte noire de se déplacer, et la notion d'équilibrage, qui évite que tous les éléments se tassent sur un bord.

### 3. Layout ordonné

La 3<sup>e</sup> génération des outils de synthèse vise à une génération entièrement automatique du layout physique à partir d'une description fonctionnelle. A l'image des mémoires, des structures régulières permettront une conception sûre et rapide grâce à un algorithme de construction simple.

On recherche des structures matricielles permettant de réaliser des fonctions logiques diverses sans perte de place par rapport à ce que l'on fait aujourd'hui avec un système CAO de 1<sup>re</sup> génération. La notion de layout ordonné implique d'abord qu'il est composé de cellules simples (microcel-

lules), arrangées en matrice(s) rectangulaire(s), ensuite que le layout est orienté, c'est-à-dire qu'un niveau d'interconnexions n'est utilisé que dans une direction.

Un premier exemple de layout ordonné pour une technologie CMOS a été proposé: le «gate matrix» [2]. Un second exemple pour une structure particulière de décodeur a été étudié [3], où le programme PLASCAL permet une génération automatique du layout à partir d'une description logique.

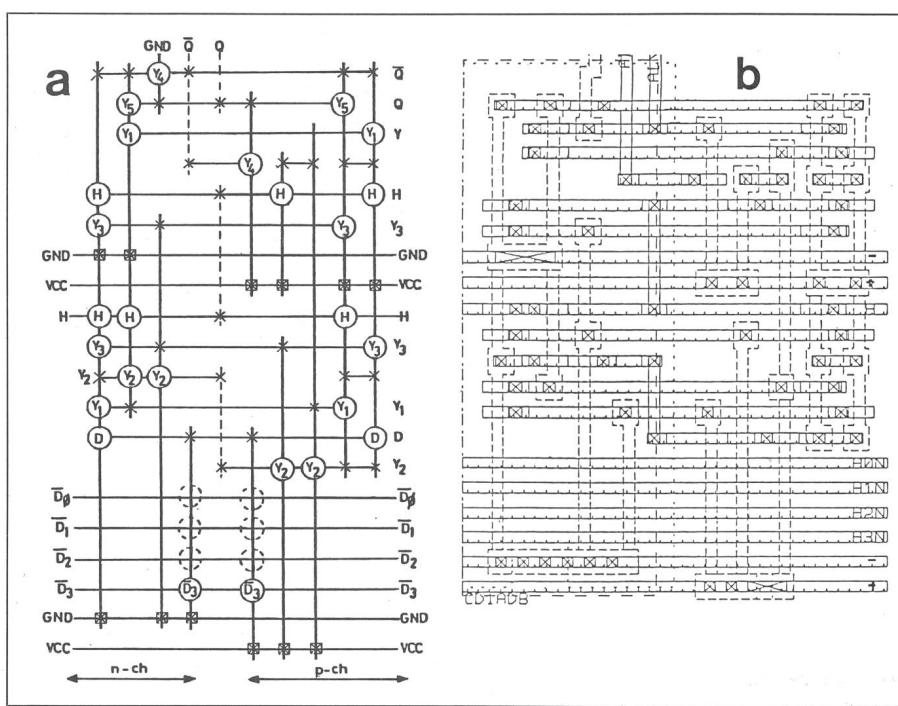

Une structure particulière et les programmes correspondants de génération automatique sont en cours de développement. L'orientation est donnée par les lignes d'aluminium. Un ensemble de microcellules est donné à la figure 5 et un circuit réalisé selon cette structure est montré à la figure 6. Ce circuit de 1087 transistors contient, sur la moitié de sa surface, une ROM dynamique formée par deux grands tableaux réguliers [4]. Quelques détails de la figure 6 sont agrandis à la figure 7. Une bascule D (fig. 7) montre comment la plupart des circuits logiques peuvent être conçus avec un layout ordonné et que la densité d'intégration est excellente.

### 4. Conclusions

Les méthodes proposées accélèrent le temps de développement et limitent

Fig. 6 Automate programmable en layout ordonné CMOS

Moitié supérieure: décodeur et mémoire

Moitié inférieure: différents circuits logiques dont une bascule D répétée sept fois et détaillée à la figure 7

le risque d'erreurs. Elles seront indispensables à la réalisation de circuits complexes (plus de 10 000 MOSTs). De plus, une base de donnée sous forme symbolique ou fonctionnelle est indépendante des détails technologiques. On peut donc envisager une transformation automatique d'un circuit lors d'un changement de technologie ou de fabricant.

### Bibliographie

- [1] M. Y. Hsueh: Symbolic layout compaction. In: P. Antonetti, D. O. Pederson and H. De Man: Computer design aids for VLSI circuits. Alphen aan der Rijn and Rockville /Md., Sijhoff and Nordhoff, 1981.

- [2] A. D. Lopez and H.-F. S. Law: A dense gate matrix layout method for MOS VLSI. IEEE J. of Solid-State Circuits 15(1980)4, p. 736...740.

- [3] D. Aubert a. o.: Computer aided layout of distributed CMOS static decoders. European Solid-State Circuits Conference 1982, p. 90.

- [4] J. C. Martin: Random and programmable logic in watches. In: From electronics to microelectronics. Fourth European Conference on Electrotechnics - EUROCON '80. Amsterdam/New York/Oxford, North-Holland, 1980; p. 708...714.

Fig. 7 Bascule D statique

a Description symbolique

b Layout