|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 73 (1982)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 3                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Analoge Schaltungsteile in einem 4-kbit-CMOS-RAM                                                                                                                                                                          |

| <b>Autor:</b>       | Feller, E.                                                                                                                                                                                                                |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-904927">https://doi.org/10.5169/seals-904927</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 18.02.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Analoge Schaltungsteile in einem 4-kbit-CMOS-RAM

E. Feller

621.3.049.774.2; 621.3.049.037.33;

Die hohe Speicherdichte in einem RAM erfordert eine analoge Schaltungstechnik für die Speicherzelle, Y-Selektion und den Leseverstärker. Diese Teile und ihre Arbeitsweise werden am Beispiel eines 1 k × 4-bit-RAM vorgestellt. Ein Kriterium für die richtige Dimensionierung der Speicherzelle wird skizziert. Die Schaltung des sehr schnellen Leseverstärkers wird kurz besprochen.

La grande capacité d'une RAM nécessite une technique de couplage analogique pour ses cellules, la sélection Y et l'amplificateur de lecture. Ces parties et leur fonctionnement sont décrites en prenant comme exemple une RAM de 1 k × 4 bits. Un critère pour le dimensionnement correct des cellules est indiqué et le circuit de l'amplificateur de lecture très rapide brièvement traité.

## 1. Einleitung

Moderne Digitalrechner, Prozessrechner und Mikroprozessoren benötigen als Arbeitsspeicher schnelle, leistungsarme und platzsparende Halbleiterspeicher. Solche Speicher sind aus einer Vielzahl von integrierten Schaltungen zusammengebaut. Sie enthalten als wichtigste Bauteile sog. Random Access Memories (RAM), das sind Lese/Schreib-Speicher mit direktem Zugriff zu allen Speicherplätzen. Je nach Speicherorganisation bestehen die Speicherplätze aus einzelnen Bit, Byte oder aus längeren Binärworten.

Es existieren viele verschiedene Arten von RAM. Sie unterscheiden sich in der verwendeten Technologie, der internen Schaltungstechnik, welche eng mit der Technologie verknüpft ist, und den äußeren Eigenschaften ganz beträchtlich. Eine Darstellung dieser Vielfalt würde den Rahmen des Themas wohl sprengen. Alle RAM haben aber folgendes gemeinsam: Die geforderte hohe Speicherdichte verlangt eine spezielle platzsparende Schaltungstechnik, welche nicht nur digitale Elemente, sondern auch analoge Schaltungsteile einsetzt.

Dieser Aufsatz beschränkt sich im folgenden auf die Betrachtung solcher analoger Schaltungsteile in einem statischen 4096-bit-RAM in CMOS-Technologie, welches vom Verfasser entwickelt worden ist.

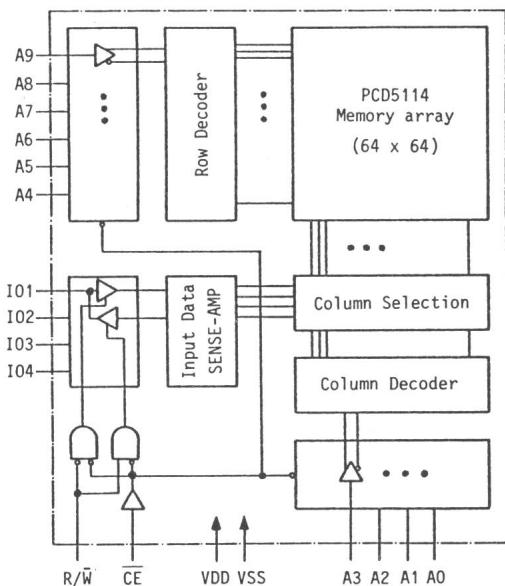

Fig. 1 Blockdiagramm

|             |                       |

|-------------|-----------------------|

| A9, ...A0   | Adresseingänge        |

| R/W         | Read/Write Eingang    |

| CE          | Chip enable Eingang   |

| IO1, ...IO4 | Daten-Ein-/Ausgänge   |

| VDD         | Speisung + 5 V        |

| VSS         | Speisung 0 V (ground) |

## 2. Aufbau und Funktion eines statischen RAM

### 2.1 Blockdiagramm

Ein statisches 4-k-RAM mit der Organisation 1 k × 4 bit umfasst folgende Funktionsblöcke (Fig. 1):

- Adresseingänge A9, ...A0

- Adressbuffer

- Zeilen-Decoder (Row- oder X-Decoder)

- Speichermatrix (Memory array)

- Spaltenselektion (Column- oder Y-Selektion)

- Spalten-Decoder (Column- oder Y-Decoder)

- Leseverstärker (Sense-Amplifier)

- Daten-Ein-/Ausgänge IO1, ...IO4

- Schreiblogik

- Steuerlogik

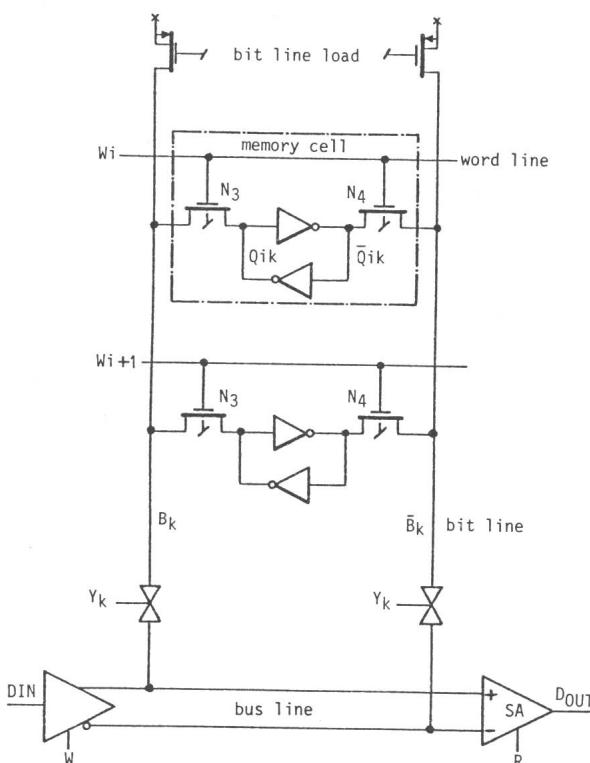

Die Speichermatrix setzt sich aus den einzelnen Speicherzellen zusammen. Sie ist in horizontaler Richtung von sog. Wortleitungen durchzogen. Eine vom X-Decoder aktivierte Wortleitung selektiert die entsprechende Zeile (Row) der Speichermatrix. In vertikaler Richtung sind alle Zellen einer Spalte (Column) mit sog. Bitleitungen verbunden. Pro Spalte werden zwei benötigt. Die Bitleitungen übertragen die gespeicherte Information der ganzen selektierten Matrixzeile von den einzelnen Zellen zur Spaltenselektion, wo ein ausgewähltes Bitleitungspaar zum Leseverstärker durchgeschaltet wird. Die Selektionsschalter sind bidirektionale Schalter, welche vom Y-Decoder angesteuert werden.

Der Leseverstärker regeneriert das schwache, symmetrische Signal und steuert damit die kräftigen Ausgangsstufen.

Zu speichernde Daten werden via Spaltenselektion in die gewünschte Spalte eingewiesen und in diejenige Zelle abgelegt, welche im Kreuzungspunkt von aktiver Wortleitung und selektiertem Bitleitungspaar liegt.

Eine Steuerlogik liefert die notwendigen Steuersignale für die einzelnen Funktionsblöcke.

Die Speicherzelle, Spaltenselektion und der Leseverstärker sind von der Arbeitsweise und Schaltungstechnik her gesehen analoge Schaltungsteile. Sie sollen näher betrachtet werden.

### 2.2 Funktion

Ein statisches 4-k-RAM (1 k × 4 bit) kennt im wesentlichen drei Betriebsarten: Lesen, Schreiben und Ruhebetrieb (stand-by).

#### Lesevorgang:

An die Adresseingänge A9 bis A0 wird eine Binärzahl (Adresse) angelegt. Die höherwertigen Bit A9 bis A4 (X-Adresse) werden im X-Decoder in einen  $(^4)$ -Code umgewandelt und aktivieren so eine der 64 Wortleitungen. Die Bit A3 bis A0 (Y-Adresse) wählen via Y-Decoder und Y-Selektion vier Spalten aus. Die vier selektierten Zellen können jetzt ge-

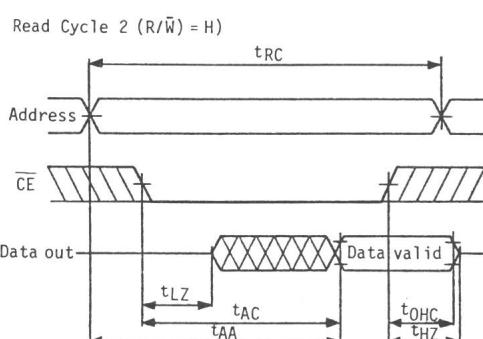

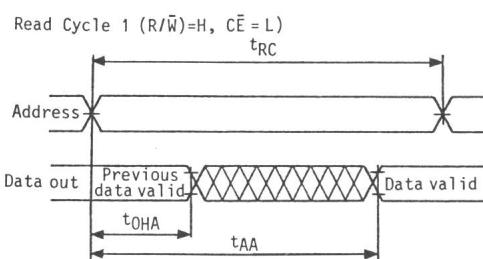

lesen werden. Der eigentliche Lesezyklus wird aber erst durch die korrekte Ansteuerung der Steuereingänge  $\overline{R/W}$  und  $\overline{CE}$  gemäss Figur 2 ausgelöst, worauf die Leseverstärker eingeschaltet werden. Nach der Adress-Zugriffszeit (Address Access Time  $t_{AA}$ ) erscheinen die vier Datenbit am Ausgang.

#### Schreibvorgang:

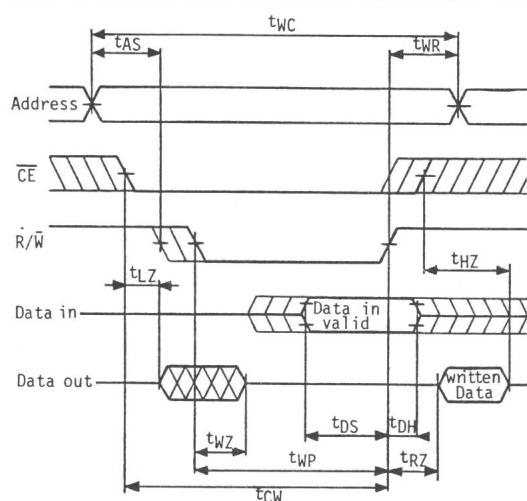

In gleicher Weise wie beim Lesen des RAM wird eine Adresse angelegt, worauf die entsprechenden vier Zellen selektiert werden. Durch die Ansteuerung gemäss Figur 3 wird ein Schreibzyklus ausgelöst. Zunächst werden die Ausgangs-Treiber in den hochohmigen Zustand geschaltet. Anschliessend kann das zu schreibende 4-Bit-Wort an die Daten-Ein-/Ausgänge angelegt werden. Es wird sofort auf die entsprechenden Bitleitungen geschaltet und so in die Zellen eingeschrieben.

#### Ruhebetrieb:

Beim Ruhebetrieb ( $\overline{CE} = H$ ) werden alle internen Arbeitsströme abgeschaltet. Es fliessen nur noch verschwindend kleine Leckströme ( $I_{DDS} \approx 10 \text{ nA}$ ).

Diese Eigenschaft macht CMOS-RAM besonders attraktiv; bei einem Ausfall der Speisespannung kann eine Batterie den Ruhestrom liefern und so den drohenden Datenverlust abwenden.

### 3. Die Speicherzelle

#### 3.1 Prinzip

Die Speicherzelle ist das häufigste Element in einem RAM. Sie muss deshalb möglichst klein sein. Das kann nur erreicht werden, wenn die Anzahl der verwendeten MOS-Transistoren auf das absolut Notwendige reduziert wird. In Figur 4 ist das Schaltungsprinzip einer Speicherzelle dargestellt. Im wesentlichen werden zwei Inverter benötigt, welche so geschaltet sind, dass zwei stabile Arbeitspunkte existieren. Dies entspricht den beiden logischen Zuständen eines Bit. Mit zwei Selektions-

Fig. 2 Lesezyklus

R/W Read/Write Eingang

$\overline{CE}$  Chip enable Eingang

L Logische 0 (low)

H Logische 1 (high)

Fig. 3 Schreibzyklus

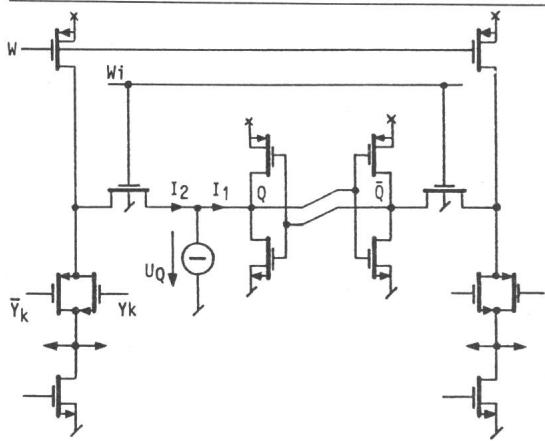

Fig. 4 Prinzip Y-Selection

$B_k$  Bitleitung (Spalte k)

$\overline{B}_k$  Inverse Bitleitung

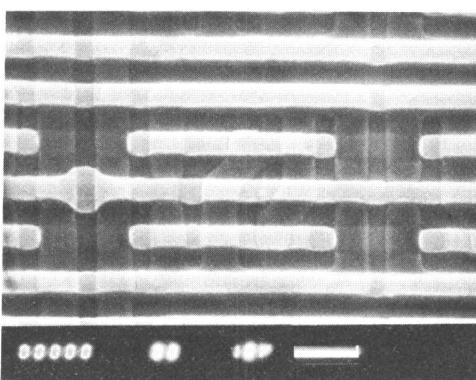

Fig. 5 Elektronenmikroskop-Aufnahme der RAM-Zelle

Transistoren (N3, N4) kann das Inverterpaar an die vertikalen Bitleitungen angeschaltet werden. Um eine möglichst kleine Zelle zu erhalten, wird der Herstellungsprozess bis an die Grenze des Möglichen getrieben (Fig. 5). Häufig wird ein Prozess auch nur für die Herstellung von RAM entwickelt.

Einige der heute angewendeten Zellentypen sind in Figur 6 dargestellt. Für ein RAM mit sehr niedrigem Ruhestrom kommt nur eine Sechs-Transistor-Zelle in Frage.

Die Überlegungen, welche im nächsten Abschnitt über das Lese/Schreib-Prinzip angestellt werden, gelten für diese Sechs-Transistor-Zelle. Sie können aber ohne weiteres sinngemäß auf die andern Typen übertragen werden.

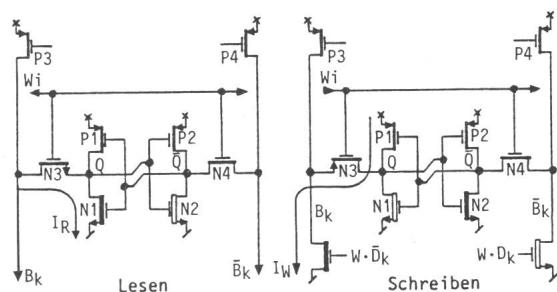

### 3.2 Lese/Schreib-Prinzip

Zuerst sollen der Lese- und Schreibvorgang qualitativ beschrieben werden. In Figur 7 sind beide Fälle skizziert. Die Dicke der gezeichneten Transistorsymbole soll ein Mass für den Leitwert  $G_{ON}$  im eingeschalteten Zustand sein. Ein schwarz ausgefülltes Symbol bedeutet zudem, dass der betreffende Transistor gerade eingeschaltet ist; weiss bedeutet ausgeschaltet.

#### Lesevorgang

Am Anfang sei der Knoten Q auf Erdpotential, d.h., die Zelle hat eine logische Null gespeichert. Wird sie nun selektiert, indem die Transistoren N3 und N4 mit der Wortleitung  $W_i$  eingeschaltet werden, so fliesst ein Lesestrom  $I_R$  vom Lastwiderstand P3 am Ende der Bitleitung  $B_K$  durch den Selektionstransistor N3 in die Zelle hinein. Der grösste Spannungsabfall tritt dabei über dem Transistor N3 auf. Nachdem der Lesestrom die Bitleitungskapazität (nicht gezeichnet) umgeladen hat, entsteht am Lastwiderstand ein verwertbarer Spannungsabfall von ca. 300 mV.

Im Interesse eines kleinen Betriebsstromes wählt man einen möglichst kleinen Lesestrom, da alle Zellen der selektierten Zeile diesen Strom statisch konsumieren. Andererseits sollte die Bitleitungskapazität (ca. 1,5 pF) möglichst schnell umgeladen werden, damit der Lesevorgang nicht unnötig lange dauert. Dies erfordert aber einen hohen Lesestrom. Das vorliegende statische Arbeitsprinzip entschärft den Konflikt, indem ein kleiner Lesestrom zusammen mit einem kleinen Spannungshub an der Bitleitung ein genügend rasches Signal liefert. Es kostet gesamthaft weniger Strom, das schwache Signal nach der Spaltenselektion zu verstärken, als alle Leseströme zu erhöhen.

Das einfache statische Arbeitsprinzip benötigt zudem keine Lese-Erholzeit (Read Recovery Time), da die Lesespannung an der Bitleitung nie einen so niedrigen Wert erreicht, dass die nächste gelesene Zelle versehentlich überschrieben wird. Bei vollem Spannungshub müssten die Bitleitungen vor jedem Lesevorgang auf eine ungefährliche Spannung aufgeladen werden (precharge). Einige RAM-Hersteller verwenden das Precharge-Prinzip. Sie nehmen in Kauf, dass ihr RAM nicht voll statisch gelesen werden kann (ohne  $\overline{CE}$ -Takt), was bei RAM mit 'Address Latches' sowieso nicht möglich ist, ausser man leite den Precharge-Impuls in einer aufwendigen Schaltung von den Adress-Übergängen ab (Address Activated).

#### Schreibvorgang

Vor dem Schreiben sei in der betrachteten Zelle eine '1' gespeichert, eine '0' soll eingeschrieben werden. Der Knoten Q

befindet sich also vorerst auf  $V_{DD}$ -Potential. Beim Schreibvorgang wird die Bitleitung  $B_K$  auf Erdpotential geschaltet. In der Folge fliesst ein Schreibstrom  $I_W$  aus der Zelle heraus via Selektions-Transistor N3 in den Bitleitungs-Treiber hinein. Als Ersatz für die ganze Schaltung (Fig. 4) ist in Figur 7 ein einzelner N-Kanal-Transistor ( $W\bar{D}_K$ ) eingezeichnet.

Der grösste Spannungsabfall tritt über dem Transistor P1 auf; mit andern Worten, die Speicherzelle kippt und hat fortan eine logische '0' gespeichert. Eine logische '1' wird geschrieben, indem die zweite Bitleitung  $\bar{B}_K$  an Erdpotential geschaltet wird.

Die qualitative Beschreibung des Lese/Schreib-Vorgangs gibt schon einige Hinweise, wie die Zelle zu dimensionieren ist. Ein quantitatives Kriterium, das auch die grossen Streuungen im Prozess berücksichtigt, wird im nächsten Abschnitt besprochen.

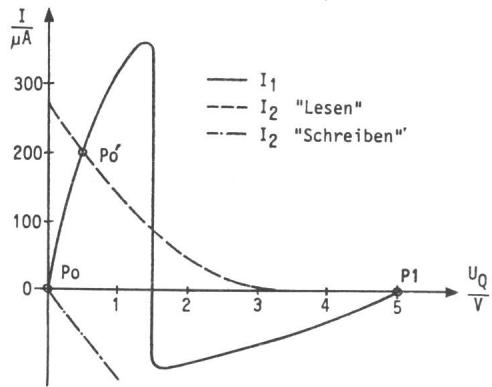

### 3.3 Die I-U-Charakteristik der Zelle

Die Transistoren der RAM-Zelle sind so zu dimensionieren, dass folgende zwei Bedingungen erfüllt sind: Beim Lesen darf die Zelle nicht versehentlich überschrieben werden; beim Schreiben muss die Zelle sicher kippen.

Ein übersichtliches Hilfsmittel zur Beurteilung dieser Bedingungen ist eine I-U-Charakteristik gemäss Figur 8.

In Gedanken wird eine Spannungsquelle  $U_Q$  in die Zelle geschaltet. Ihre eingeprägte Spannung wird von 0 bis  $V_{DD}$  variiert. Die beiden Ströme  $I_1$  und  $I_2$  sind in Funktion der Spannung  $U_Q$  graphisch aufzutragen. Praktisch kann dies der Kleinheit der Zelle wegen nicht durchgeführt werden. Eine experimentelle Bestimmung der Kurven kann man sich auch gar nicht leisten. Die Entwicklungs-, Masken- und Herstellungskosten einer Versuchsserie sind viel zu hoch. Es bleibt nur die Simulation mit einem guten Netzwerk-Analyse-Pro-

| Typ                             | CMOS 6 Transistoren | Enhancement Enhancement | Enhancement Depletion | Poly load | JFET/ Poly load |

|---------------------------------|---------------------|-------------------------|-----------------------|-----------|-----------------|

| Zelle                           |                     |                         |                       |           |                 |

| Fläche (relativ)                | 1,5                 | 1,4                     | 1,0                   | 0,5       | 0,4             |

| $I_{DD5}/\text{Stand by Strom}$ | pA                  | $10 \mu\text{A}$        | $1 \mu\text{A}$       | nA        | nA              |

| Technologie                     | CMOS                | NMOS/CMOS               | NMOS                  | NMOS/CMOS | CMOS            |

Fig. 6 RAM-Zellen

CMOS Complementary Metal Oxide Semiconductor

NMOS n-Channel Metal Oxide Semiconductor

JFET Junction Field Effect Transistor

Fig. 7 Lese-/Schreib-Vorgang

$I_R$  Lesestrom

$I_W$  Schreibstrom

Fig. 8  $I-U$ -Charakteristik

Fig. 9 Leseverstärker-Prinzip

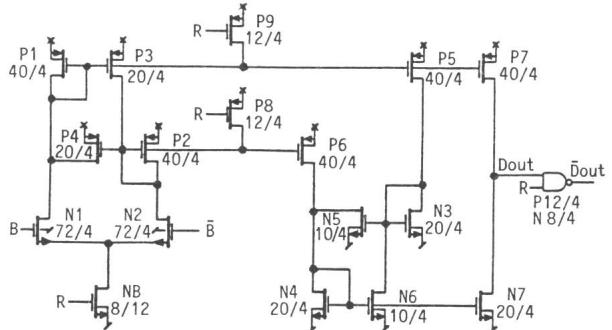

Fig. 10 Leseverstärker

gramm wie SPICE, PHILPAC, DOMOS usw., wo die Berechnung von  $I-U$ -Kennlinien sehr leicht möglich ist.

In den Kennlinien treten die obigen Bedingungen anschaulich hervor:

– Beim Lesen schneiden sich die Zellenkennlinie  $I_1 (U_Q)$  und die Kennlinie  $I_2 (U_Q)$  der Außenwelt in zwei Punkten  $P_0$  und  $P_1$ . Der Schnittpunkt  $P_1$  entspricht einer logischen Eins. Der zweite Punkt  $P_0'$  entspricht dem Lesen einer logischen Null, wobei der Lesestrom fließt. Die erste Bedingung ist erfüllt, wenn der Schnittpunkt um einen genügend hohen Sicherheitsabstand unter dem Scheitel der Zellenkennlinie liegt und die Spannung einen Schwellwert nicht überschreitet.

– Beim Schreiben wird die Kennlinie  $I_2 (U_Q)$  nach unten verschoben, so dass nur noch der Schnittpunkt  $P_0$  existiert.  $P_0$  entspricht der geschriebenen Null. Die zweite Bedingung ist erfüllt, wenn der Abstand zwischen der Senke von  $I_1 (U_Q)$  und der Kurve  $I_2 (U_Q)$  genügend gross ist.

Im Rahmen dieser Bedingungen kann die Geometrie der Transistoren der Zelle frei variiert werden, um weitere Bedingungen wie die Höhe des Lesestromes sowie die Funktion der Zelle über einen grossen Speisespannungs- und Temperaturbereich zu garantieren, und das bei möglichst kleiner Zellfläche.

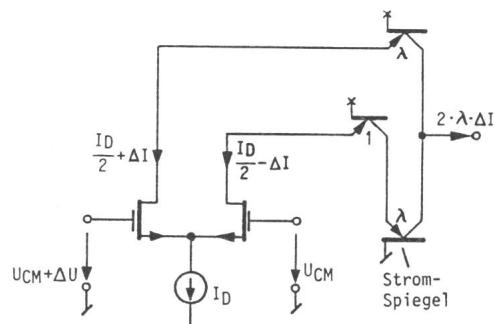

#### 4. Der Leseverstärker

##### 4.1 Prinzip

Der Leseverstärker soll bei hoher Gleichtaktspannung und kleinem differentiellem Eingangssignal ein Ausgangssignal mit dem vollen CMOS-Pegel liefern. Eine Schaltung, welche den geforderten Bedingungen entspricht, ist in Fig. 9 dargestellt.

Der Leseverstärker besteht aus einer differentiellen Eingangsstufe und einigen Stromspiegeln, welche dafür sorgen, dass am Ausgang der volle Hub erreicht werden kann. Er reagiert sehr unempfindlich auf Streuungen der Prozessparameter.

Die üblichen Stromspiegel haben den Nachteil, dass sie zwar schnell auf eine Stromzunahme ansprechen, aber leider nicht auf eine Stromabnahme. Durch kreuzgekoppelte Stromspiegel kann dieser Nachteil behoben werden.

##### 4.2 Die optimierte Schaltung

Die mittels SPICE-Simulation optimierte Schaltung ist in Figur 10 dargestellt. Eine erstaunlich kurze Reaktionszeit von max. 14 ns bei einem 100-mV-Eingangssignal wird von SPICE

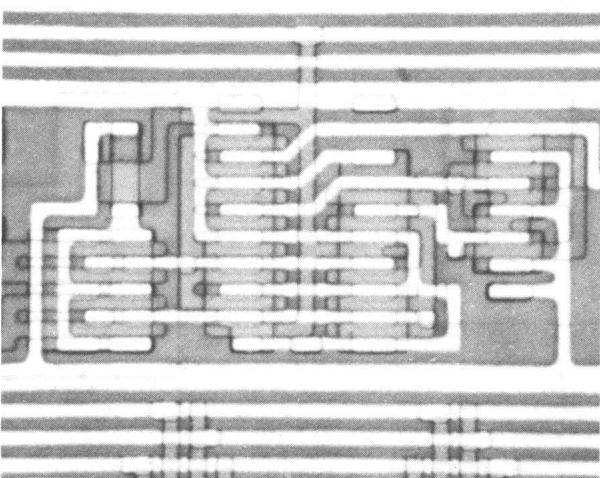

Fig. 11 Leseverstärker (Vergrösserung 500:1)

errechnet. Leider kann dieses Ergebnis nicht direkt messtechnisch verifiziert werden, jede Sonde würde den Verstärker kapazitiv überlasten.

Eine indirekte Bestätigung ist aber möglich: Die gemessene Address Access Time des RAM (typisch 90 ns) stimmt recht gut mit dem berechneten Wert überein, so dass der Simulation einigermaßen vertraut werden darf.

In Figur 11 ist der realisierte Leseverstärker in 500facher Vergrößerung abgebildet. Die Aluminiumverbindungen haben

eine minimale Breite von 4  $\mu\text{m}$ , der Rasterabstand beträgt 8  $\mu\text{m}$ . Für die Herstellung des 4-k-RAM wird der CMOS-Prozess mit 4- $\mu\text{m}$ -Geometrie und selbstjustierenden Kontakten verwendet, welcher von *J. Solo* bei Faselec AG, Zürich, entwickelt worden ist.

#### Adresse des Autors

E. Feller, Faselec AG, Räffelstrasse 29, 8045 Zürich.

## Literatur – Bibliographie

DK: 621.38.049.037.33

SEV-Nr. A 913

**Electronique des signaux analogiques.** Par *J. Auvray*. Paris, Dunod, 1980; bro., 8°, X/350 p., fig., tab. Collection Dunod Université

Cet ouvrage traite des principes de base de l'électronique analogique. L'auteur décrit et analyse les circuits électroniques simples dont la compréhension permet d'aborder l'étude des systèmes plus complexes.

La première partie contient des rappels des notions fondamentales de traitement des signaux (séries de Fourier, fonctions de transfert, distorsions), ainsi que la description et les caractéristiques des composants passifs et actifs utilisés actuellement. La deuxième partie est consacrée aux filtres et aux amplificateurs de faible puissance. Elle débute par un résumé des méthodes d'analyse et de synthèse des filtres passifs. Suit un chapitre important consacré aux techniques de l'amplification: amplificateurs opérationnels et ses applications, amplificateurs pour signaux alternatifs (basse fréquence, vidéo fréquence, haute fréquence, sélectif, ...), contre-réaction et stabilité, bruit. Une étude des filtres actifs termine cette seconde partie. Dans la troisième partie sont rassemblées les études de quelques circuits classiques en électronique comme les redresseurs, les stabilisateurs, les amplificateurs de puissance, les amplificateurs non linéaires, les oscillateurs et bascules, les modulateurs et démodulateurs.

Ce livre passe en revue les principales techniques de l'électronique analogique. Pour chacune, l'auteur définit les buts recherchés, décrit les circuits habituellement utilisés et analyse leur comportement souvent de façon détaillée et agrémentée d'exemples numériques. Par sa forme, son niveau technique, par l'étendue de la matière traitée et malgré une présentation moyenne (surtout pour les figures), cet ouvrage s'adresse principalement aux étudiants des écoles techniques et universitaires.

*A. Decurnex*

SEV-Nr. A 912

DK: 621.313 : 621.314

**An introduction to electrical machines and transformers.** By *George McPherson*. New York a.o. John Wiley and Sons, 1981; 8°, XVIII/557 p., fig. Price: cloth £ 14.30

Das vorliegende Lehrbuch vermittelt die wesentlichen Grundlagen über die Theorie, die Wirkungsweise sowie das Betriebsverhalten elektrischer Maschinen und Transformatoren.

Nach einem allgemeinen Teil werden die Synchronmaschine, der Transformator, die Asynchronmaschine, die Gleichstrommaschine und die Einphasenmaschine behandelt. In drei Anhängen wird eine Übersicht über die Berechnung des magnetischen Kreises elektrischer Maschinen gegeben, über die Zusammenhänge zwischen den elektrischen Größen in symmetrischen, dreiphasigen Netzen sowie über die Beschreibung der Schenkelpolmaschine in der Zweiachsen-theorie.

Zu jeder der beschriebenen Maschinenarten folgt nach einer kurzen Einführung über ihren Aufbau die Ableitung und Anwendung des Ersatzschaltbildes, die Beschreibung der experimentellen Bestimmung der Maschinenkenngroßen sowie des Regulierverhaltens. Auf Sonderbauarten wie Autotransformator, PAM (pole-amplitude-modulation)-Motoren, Permanenterregung bei Gleichstrommaschinen usw. wird ebenfalls eingegangen. Die Synchronmaschine ausgenommen, werden Übergangsvorgänge nicht behandelt.

Das Buch ist gut gegliedert und mit modernem Bildmaterial und anschaulichen Skizzen versehen. An mathematischen Hilfsmitteln sind Kenntnisse in einfacher Differential- und Integralrechnung sowie in der Zeigerdarstellung erforderlich. Das Buch wendet sich an Studenten der Ingenieurwissenschaften, der Elektrotechnik und des Maschinenbaus. Es ist aber auch für den in der Praxis stehenden Ingenieur, z.B. in der Projektierung, wertvoll.

*A. Meyer*