|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 72 (1981)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 23                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | Bus normalisés pour microprocesseurs                                                                                                                                                                                      |

| <b>Autor:</b>       | Nicoud, J.-D.                                                                                                                                                                                                             |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-905175">https://doi.org/10.5169/seals-905175</a>                                                                                                                                   |

### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Bus normalisés pour microprocesseurs

Par J.-D. Nicoud

681.325-181.48;

*Les bus pour microprocesseurs existent depuis 7 ans et ont subi une évolution assez importante. Des bus commerciaux ont été acceptés comme norme «de facto», le démarrage d'une norme indépendante d'un fabricant étant très difficile. Les fonctions demandées à un bus sont toujours plus évoluées, mais l'intelligence des interfaces et une plus grande régularité de la conception permettent en fait de simplifier la réalisation. Aussi l'évolution se fait de bus monoprocesseurs 8 bits avec beaucoup de lignes de contrôle vers des bus multiprocesseurs 32 bits avec relativement peu de lignes de commande bien définies.*

*In den 7 Jahren ihrer Existenz haben die Mikroprozessorkomplexe eine recht bedeutende Entwicklung durchgemacht. Kommerzielle Busse sind de facto als Norm angenommen worden, während die Festlegung einer von Herstellern unabhängigen Norm sehr schwierig ist. Die von einem Bus verlangten Funktionen werden immer komplexer, doch ermöglicht die Intelligenz der Interface sowie eine grössere Regelmässigkeit in der Auslegung auch Vereinfachungen in der Herstellung. So erfolgt die Entwicklung von den 8-Bit-Monoprozessorkomplexen mit vielen Steuerleitungen zu 32-Bit-Multiprozessorkomplexen mit relativ wenigen, genau definierten Steuerleitungen.*

## 1. Introduction

Pour communiquer avec ses périphériques et mémoires, un processeur utilise un groupe de lignes appelées bus. Les contraintes électriques et mécaniques au niveau des circuits intégrés microprocesseurs, des cartes circuits imprimés sous-systèmes, et des systèmes complets, ont conduit à une très grande diversité de bus, pour lesquels une normalisation satisfaisante est loin d'être atteinte. En effet, l'évolution de la technologie et la complexité croissante des processeurs et modules modifient sans cesse les critères de choix. Les mécanismes importants des systèmes multiprocesseurs sont encore mal compris. Les fabricants visent leur profit à court terme en proposant des solutions optimisées pour leur dernier processeur, et doivent modifier ces solutions à chaque nouvelle génération de processeur.

Un effort important (mais insuffisant) est toutefois entrepris par des organisations internationales pour définir et accepter des normes dont l'industrie a besoin.

## 2. Topologie des systèmes informatiques

Les communications dans un système informatique peuvent se grouper selon trois niveaux :

1. Au premier niveau, le processeur a des communications intenses avec ses mémoires et circuits interfaces. Un bus parallèle (backplane bus) assure ce trafic avec une vitesse de plusieurs dizaines de Mbit/s.

2. Au deuxième niveau, le 1<sup>er</sup> niveau communique avec les périphériques, branchés en étoile ou selon un bus de communication série ou parallèle, avec un débit de quelques Mbit/s.

3. Au dernier niveau, les systèmes sont reliés entre eux par des lignes directes à relativement faible vitesse, quelques dizaines de kbit/s. Une interconnexion en réseau offrant plusieurs chemins, permet d'augmenter la fiabilité et la distribution des charges.

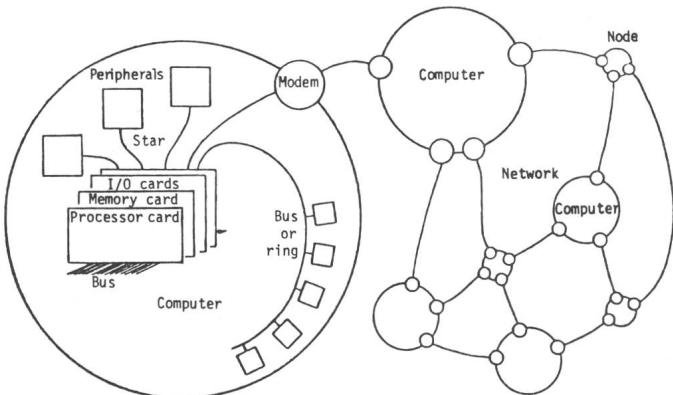

La figure 1 illustre ces trois niveaux. Cet article ne s'occupe que du premier niveau, les bus de microprocesseurs.

## 3. Les systèmes de microprocesseurs

### 3.1 Système monoprocesseur

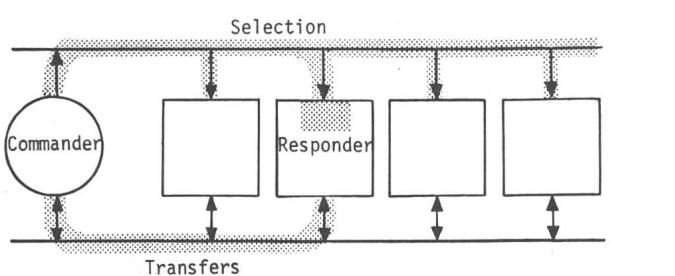

Si un processeur maître doit transférer de l'information avec plusieurs unités esclaves, une liaison en étoile n'est pas réaliste. Maîtres et esclaves sont branchés en parallèle sur un bus permettant le transfert d'information avec un seul esclave à la fois. Chaque transfert est précédé de la sélection de l'esclave (fig. 2). Pour cette sélection, à chaque esclave est assignée une adresse, avec généralement une sous-adresse correspondant à l'information précise à l'intérieur de l'esclave, comme c'est le cas pour les mémoires et registres de périphériques. Des blocs d'information peuvent être associés à une première sélection; cette notion de transfert du bloc, de canal, prend une importance croissante avec les nouveaux microprocesseurs.

Etant donné que le transfert suit logiquement la sélection, l'adresse de sélection et les données peuvent être multiplexées sur les mêmes figures sans perte significative de performance. Les signaux de synchronisation peuvent être conçus soit dans l'optique d'une optimisation d'un transfert adresse-donnée combinée, comme c'est le cas avec la plupart des microprocesseurs actuels, soit en séparant et en mettant sur un même niveau le transfert des adresses et des données. Cette dernière approche convient bien pour les processeurs 16 et 32 bits et est proposée pour le bus P896.

Les systèmes monoprocesseurs ont presque tous un mécanisme d'interruption qui permet à un esclave d'attirer l'atten-

Fig. 1 Topologie d'un système informatique

Fig. 2 Sélection et transfert maître-esclave

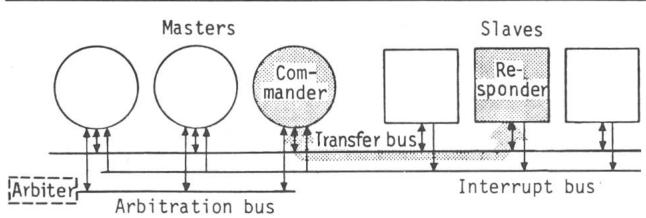

**Fig. 3** Système multiprocesseur

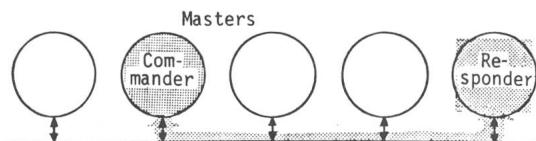

**Fig. 4** Système homogène

tion du maître. Les demandes d'interruption peuvent se faire en étoile sur le processeur ou un contrôleur d'interruption, ou utiliser un bus d'interruption associé au bus de données pour la transmission d'un mot ou vecteur d'identification.

### 3.2 Systèmes multiprocesseurs

La présence de plusieurs maîtres (processeurs) sur un même bus implique un mécanisme d'arbitration qui peut être centralisé ou distribué (fig. 3). Dans la plupart des systèmes actuels, un maître principal (le processeur) prête le contrôle à des sous-maîtres (unités d'accès direct en mémoire).

Le problème d'accès et de priorité en cas de demande simultanée est délicat à résoudre. Dans un système multiprocesseur, le problème des interruptions prend une dimension différente selon que chaque processeur est associé à une tâche et un groupe de périphérique donné, ou que chaque processeur est banalisé pour permettre le transfert des tâches d'un processeur à l'autre.

### 3.3 Système homogène

Les systèmes microprocesseurs tendent à ne contenir que des maîtres, ayant leur mémoire locale et leurs périphériques propres (fig. 4). Un bus commun est nécessaire pour les échanges d'information et la synchronisation des processus. L'un des maîtres demande alors le contrôle du bus, sélectionne un autre maître qui joue alors le rôle d'esclave et effectue le transfert. Ce mécanisme est utilisé pour les demandes d'interruption, qui peuvent être dirigées avec précision et complétées d'une information de priorité.

#### **4. Les Fonctions des bus microprocesseurs**

#### *4.1 Bus de transfert d'information*

Le bus d'information transporte l'adresse de sélection et les données associées, en parallèle sur deux bus parallèles ou en série (bus multiplexé). Dans le cas de transferts de données consécutives, l'adresse n'a pas besoin d'être répétée (transferts de blocs).

Un cycle de transfert peut être purement synchrone (l'escalier doit être plus rapide que le maître). La plupart des micro-processeurs permettent la synchronisation des échanges au niveau des données. P896 permet la synchronisation tant du point de vue de l'adresse que des données, car il est clair qu'avec l'évolution de la technologie, le temps de sélection

d'une carte est du même ordre de grandeur que le temps d'accès d'une mémoire par exemple.

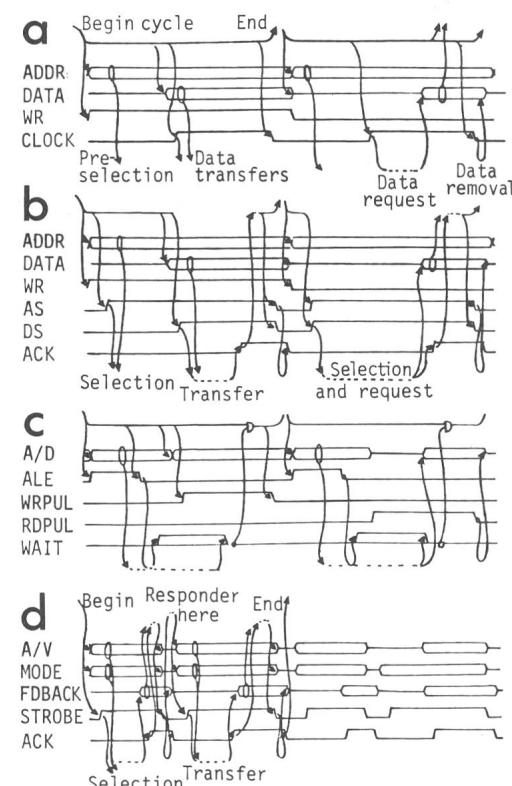

La figure 5 donne quelques exemples de protocoles de transfert en écriture et lecture. Ces quelques exemples évoquent la multiplicité des variantes, étant donné que chaque action élémentaire peut être explicitement mise en évidence et synchronisée avec une paire de signaux, ou au contraire considérée implicitement comme survenant à l'instant spécifié. Une synchronisation explicite ralentit pour une technologie donnée, mais a l'avantage d'être indépendante de cette technologie.

L'information de commande associée à un transfert d'information (lecture/écriture, mémoire/périphérique, octet/mot de 16 bits) est, selon les cas, transportée par les signaux de synchronisation des échanges ou encodée.

## 4.2 Bus d'arbitration

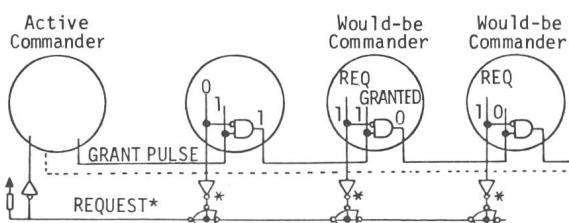

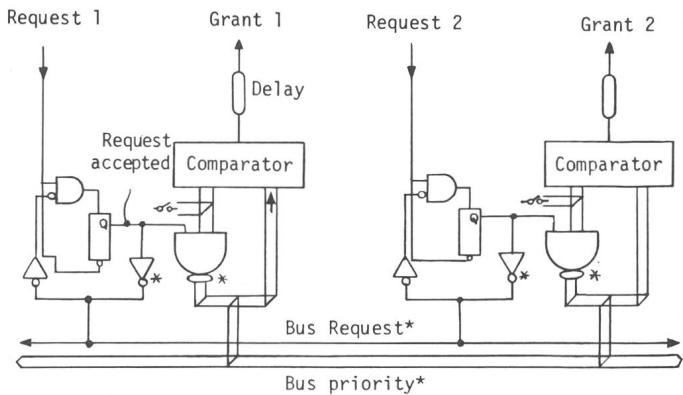

Pour arbitrer entre les demandes de simulation, qui peuvent être d'accès au bus ou d'interruption, une chaîne de priorité (fig. 6) est très fréquemment utilisée, malgré ses limitations. Une arbitration parallèle (fig. 7) tend à se généraliser dans des bus récents (P696, Fastbus, P896), mais est plus lente qu'un arbitre centralisé.

### 4.3 Bus d'interruption

Le bus d'interruption transmet les demandes au processeur en action par une ligne et/ou cablé. Le processeur répond par une impulsion qui permet à l'esclave le plus prioritaire de placer un vecteur d'identification sur le bus de donnée (libre à ce moment-là étant donné l'optique monoprocesseur). L'arbitrage des demandes d'interruption se fait en général par une chaîne de priorité comme dans le cas de l'arbitrage.

**Fig. 5** Diagramme des temps typiques pour un cycle d'écriture et de lecture

- pour un cycle d'écriture et de lecture

- a Transfert synchrone, bus non multiplexé (6800)

- b Transfert asynchrone, bus non multiplexé (68000)

- c Transfert asynchrone, bus multiplexé (8085)

- d Transfert avec synchronisation complète (P896)

#### 4.4 Bus d'alimentation

Les cartes branchées sur le bus doivent être alimentées en puissance, et le courant de retour des signaux actif doit être absorbé avec une chute de tension minimale. Le bus d'alimentation joue un rôle important dans la fiabilité du système, mais le coût des broches de connecteur ne permet en général pas la multiplicité souhaitable des lignes de masse et d'alimentation.

#### 5. Caractéristiques électriques et mécaniques d'un bus

Le bus court (10 cm) qui relie le processeur lui-même n'a pas besoin d'être adapté du point de vue de son impédance électrique. Par contre le bus arrière (backplane bus) doit être adapté, ce qui entraîne une puissance dissipée importante. Le bus peut être collecteur ouvert où à trois états. Pratiquement tous les bus utilisent la technologie TTL, mais l'utilisation de circuits ECL ou de portes à caractéristique trapézoïdale est très intéressante.

La taille des cartes d'un système microprocesseur et le choix du connecteur a beaucoup fluctué dans le temps. Le format européen avec connecteur indirect rallie actuellement le plus d'intérêt, mais ses contraintes apparaissent encore souvent inacceptables aux fabricants US.

#### 6. Bus importants actuels

La plupart des bus actuels ont été développés pour un processeur donné et sont fortement influencés par les caractéristiques de ce processeur. Une analyse récente relativement complète peut se trouver dans les références [1; 2; 3]. La norme Mibus [5] a été une première proposition de bus indépendante d'un fabricant. Elle est venue trop tôt, et ne correspondait plus aux besoins 4 ans plus tard, lorsque la nécessité de bus universels s'est réellement fait sentir pour l'industrie: Mibus aurait dû avoir un connecteur DIN à 64 broches et 20 lignes d'adresses au moins. Les bus les plus largement utilisés, S100 et Multibus® ont été normalisés par l'IEEE (696 [2] et 796 [3]). D'autres bus industriels sont largement utilisés: STD-bus [6], SMP-80 et AMS-85 de Siemens. Pour les nouveaux processeurs 16 et 32 bits, les fabricants proposent le ZBI [3], le Versabus [9]; des groupes de standardisation proposent Eurobus-E35 [10], Fastbus [11] et P896 [12].

Les bus de miniordinateurs (Unibus, Q-bus, mass-bus [4]) ont souvent inspiré les concepteurs de bus universels pour microprocesseurs.

Microbus n'a pas été mentionné car, comme le Motel bus, il ne s'agit en fait pas d'un bus, mais d'un ensemble de signaux assez mal spécifiés, redondants et locaux à la carte processeur.

##### 6.1 Bus IEEE-696 (S100)

Très mal conçu au départ, mais accepté comme norme de facto, le S100 a été un peu amélioré par le groupe de travail de l'IEEE. La seule valeur du S100 est sa relative normalisation, mais la compatibilité des cartes de différents fabricants disponibles doit être soigneusement testée dans chaque cas.

##### 6.2 Bus IEEE-796 (Multibus R)

Le bus d'Intel est en cours d'acceptation par l'IEEE sans modifications majeures. C'est un bon bus multiprocesseur, assez souple d'emploi de par les possibilités d'interruption et d'arbitrage parallèles ou par bus. Le format des cartes est un handicap majeur en Europe.

#### 6.3 Bus IEEE-896 (Backplane bus)

Le bus P896 (P proposition) est encore en cours de définition. Des options importantes doivent se voter prochainement. La contrainte d'un nombre de lignes égal à 64 pour un bus multiplexé de 32 bits a forcé une optimisation très grande des lignes de contrôle, avec pour résultat un schéma très simple, de structure régulière et extensible. Le niveau 1 comporte 8 lignes pour le bus d'arbitrage, 8 lignes pour la synchronisation et le mode de transfert, 2 lignes pour un bus série, et 14 lignes pour l'alimentation 5 V et la masse. Le niveau 2 prévoit d'utiliser la rangée médiane du connecteur DIN, avec adjonction de détection et correction d'erreurs, et de nouvelles fonctions de transfert. P896 ne prévoit pas d'interruption. Un espace de contrôle (CSR) existe à la place et joue le rôle de boîte aux lettres pour les demandes réciproques. Un deuxième niveau d'échange est prévu pour la gestion des tâches au niveau du système, le transfert des charges, le test du système et la reconfiguration en cas de panne d'un processeur. Ce niveau utilise un bus série.

#### 6.4 Tableau comparatif

Le tableau de la figure 8 résume les caractéristiques importantes des bus les plus largement utilisés, ou présentant un intérêt historique ou potentiel. La diversité des solutions concernant le nombre de lignes et la taille des cartes est frappante, d'autant plus que les fonctions réalisées au niveau de l'utilisateur ne sont pas si différentes. L'utilisation des circuits intégrés plus complexes permet (et force à cause du nombre limité de broches autour d'un circuit) des signaux au codage plus complexe, et permet une plus grande richesse de fonctions avec peu de lignes. Une autre raison de l'évolution des bus est le transfert de la fonction d'accès et d'exécution d'instructions au niveau de la carte elle-même. Le bus n'est à la limite plus utilisé que pour des transferts de blocs d'information assez

Fig. 6 Chaîne de priorité (daisy-chain)

Fig. 7 Bus de priorité parallèle, par comparaison de vecteurs (bus en collecteur ouvert)

| Bus                       | Introduction year | A          | D           | Status Timing | Handshake | Supervisor | Error checking | Arbitration | Interrupt | Reset | Clock | Miscellaneous | Unspecified | Power | GND   | Total |

|---------------------------|-------------------|------------|-------------|---------------|-----------|------------|----------------|-------------|-----------|-------|-------|---------------|-------------|-------|-------|-------|

| S100                      | 1975              | 24         | 16          | 14            | 1         |            |                | 7           | 10        | 1     | 2     | 5             | 7           | 4     | 5     | 100   |

|                           | 1979              |            |             |               |           |            |                |             |           |       |       |               |             |       |       |       |

| Mubus                     | 1975              | 16         | 16          | 1 3           | 1         |            |                | 5           | 5         | 1     | 1     | 2+2           |             | 9     | 8     | 74    |

| STD                       | 1977              | 16         | 8           | 2 5           |           |            |                | 4           | 3         | 2     | 2     | 3             |             | 6     | 4     | 56    |

| Multibus                  | 1977              | 20         | 16          | 1 5           | 2         |            |                | 5           | 9         | 1     | 2     | 1             | 4           | 12    | 8     | 86    |

|                           | 1979              |            |             |               |           |            |                |             |           |       |       |               |             |       |       |       |

| Eurobus 18                | 1979              |            | 18          |               | 5 3       |            |                |             | 3         | 1     | 1     | 1             | 23          | 3     | 7     |       |

| E3S                       | 1981              |            | 2           |               | 5 3       |            |                |             | 3         | 1     | 1     | 1             | 12          | 4     | 9     | 64    |

| Versabus                  | 1980              | 23<br>(+8) | 16<br>(+16) | 3+8           | 4         |            |                | 3           | 18        | 11    | 2     | 2             | 11          | 14    | 24    | 140   |

| Versabus E                | 1981              | 23         | 16          | 4/9           | 4/5       |            |                | 0/15        | 2/10      | 1     | 1     | 3             |             | 5     | 8     | 64/96 |

| Fastbus                   | 1979              |            | 32          |               | 4 6       | 1          |                | 2           | 11        | 1     |       | 2+3           | 24          | 20    | 17    | 130   |

| P896 level 1<br>(level 2) | 1982              |            | 32          |               | 5 2       | (+1)       | (+10)          | (+4)        |           |       |       | 2             |             | 4     | 10    | 64    |

|                           |                   |            |             |               |           |            |                |             |           |       |       |               |             | (+2)  | (+10) | (96)  |

Fig. 8 Tableau comparatif des principaux bus actuels

longs, et de messages courts pour boîte aux lettres. Le bus P896 est pour l'instant le seul à pleinement refléter cette tendance.

#### Bibliographie

- [1] C. Warren: Understanding bus basics helps resolve design conflicts. EDN 26(1981)11, p. 159...173.

- [2] C. Warren: Compare μC-bus specs to find the bus you need. EDN 26(1981)12, p. 141...153.

- [3] C. Warren: High-performance buses clear a path for future μCs. EDN 26(1981)13, p. 157...158.

- [4] C.G. Bell, J.C. Mudge and J.E. McNamara: Computer engineering: A DEC view of hardware systems design. Bedford/Mass., Digital Press, 1978.

- [5] J.D. Nicoud and D. del Corso: Mubus standard. Microscope 1(1977)8, p. 1...44.

- [6] K. Britton: The STD bus: A critical look at a proposed new standard. Dr. Dobb's Journal of Computer Calisthenics and Orthodontia 3(1978)11, p. 34 to 39.

- [7] K.A. Elmquist a.o.: Standard specification for S-100 bus interfaces devices. IEEE Task 696.1/D2. Computer 12(1979)7, p. 28...52.

- [8] R.W. Boberg: Proposed microcomputer system 796 bus standard. IEEE Task P 796/D2. Computer 13(1980)10, p. 89...105.

- [9] T. Balph and J. Kister: Microprocessor bus gears up to a 32-bit future. Electronic Design 28(1980)13, p. 97...103.

- [10] E3S, Proposal for a small system standard. ESONE. Bruxelles, CEE, 1981.

- [11] Fastbus, modular high speed data acquisition system for high energy physics and other applications. Washington, USA Department of Commerce, National Bureau of Standards, 1981.

- [12] A.A. Allison: Status report on the P 896 backplane bus. IEEE Micro 1(1981)1, p. 67...82.

#### Adresse de l'auteur

Prof. J.-D. Nicoud, LAMI EPFL, 16, chemin de Bellerive, 1007 Lausanne.