|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 72 (1981)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 15                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | Vorbehandlung von integrierten Schaltungen                                                                                                                                                                                |

| <b>Autor:</b>       | Lombardini, R.                                                                                                                                                                                                            |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-905135">https://doi.org/10.5169/seals-905135</a>                                                                                                                                   |

### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Vorbehandlung von integrierten Schaltungen

Von R. Lombardini

621.3.049.77;

*Die Vorbehandlung ist eine notwendige Voraussetzung zur Sicherstellung der Zuverlässigkeit von integrierten Schaltungen und Geräten. Die Schwierigkeit besteht darin, aus der Vielzahl der möglichen Vorbehandlungsmethoden die kostenwirksamste Sequenz für das jeweilige Bauteil bzw. Modul oder Gerät auszuwählen. Massgebend für die Festlegung einer Vorbehandlungssequenz ist die Kenntnis der Ausfallmechanismen, die den sogenannten Frühausfällen zugrunde liegen.*

*Un déverminage est une condition indispensable pour assurer la fiabilité des circuits intégrés et des équipements. La difficulté consiste dans le choix de la séquence assurant le déverminage le plus efficace au meilleur prix. Afin d'effectuer ce choix, il est nécessaire de connaître les mécanismes de défaillance qui sont à l'origine des défaillances précoces.*

## 1. Einleitung

Unter Vorbehandlung (engl. screening) versteht man eine Folge von Beanspruchungen, denen eine elektronische Einheit (Bauteil, bestückte Leiterplatte, Gerät, Anlage usw.) unterworfen wird, um die Fehlermechanismen der Frühausfälle zu aktivieren. Mit einer Vorbehandlung soll auch die Ausfallrate einer reparierfähigen Einheit oder einer Menge von nicht reparierbaren Einheiten in der Nutzungsphase verkleinert werden. Dabei soll die Vorbehandlung die Gebrauchsduer der Einheiten nicht wesentlich verkürzen, also nicht zerstörend wirken.

Der zunehmend grösser werdende Anteil der Elektronik in Systemen jeglicher Art sowie die rasante Entwicklung auf dem Bauteilsektor insbesondere der digitalen Elektronik hat das Problem der Qualitäts- und Zuverlässigkeitssicherung der Elektronik in den Vordergrund rücken lassen. Dabei wird über Erfolg oder Misserfolg von Massnahmen in noch stärkerem Masse als bisher nur mittels Statistik und Wahrscheinlichkeitsrechnung entschieden.

Bei vielen Firmen, die sich erst seit relativ kurzer Zeit intensiv mit der Fertigung von mittleren und grösseren Serien elektronischer Baugruppen oder Geräten befassen, tut man sich schwer bei der Wahl von qualitätssichernden Massnahmen. Beispiele sind:

1. Wahl und Qualifikation von Lieferanten und Herstellern.

2. Festlegung der Integrationsstufe (Bauteil, bestückte Leiterplatte, Baugruppe, Anlage), auf welcher die Vorbehandlung durchzuführen ist.

3. Entscheid, welche Bauteile einer Eingangsprüfung zu unterwerfen sind (Art der Messungen, 100prozentige oder Stichprobenprüfung).

Andere Firmen konnten sich im Laufe der Jahre ein eigenliches Know-how auf dem Qualitätssicherungsgebiet aufbauen und verfügen auch über ein ausreichendes Budget, um die hohen Kosten für die Einrichtungen und Fachleute zu decken. Oft braucht es jedoch verschiedene schlechte Erfahrungen, bis die Bedeutung eines durchdachten Qualitätssicherungskonzeptes anerkannt wird. Es fällt manchen Leuten schwer einzusehen, dass selbst eine Eingangsprüfung keine Gewähr für ein gutes Funktionieren über eine gewisse Zeitspanne ist.

Trotz allen guten Willens und aller Erfahrung gibt es, abgesehen von einigen Grundregeln, keine Patentlösung auf dem Gebiet der Vorbehandlung. Jede Einheit muss in sich betrachtet werden. Massnahmen, die in einem Fall erfolgreich waren, können in einem anderen Falle ein gravierendes Problem nicht verhindern. Die Vorbehandlung ist keine exakte Wissenschaft; es geht darum, die dominanten Ausfallmechanismen zu aktivieren bzw. zu beschleunigen, damit die Frühausfälle während der Vorbehandlung, also vor dem eigentlichen Einsatz, auftreten. Eine Vorbehandlung kann dann als optimal bezeichnet

werden, wenn mit dem geringsten Aufwand alle wichtigen Ausfallmechanismen abgedeckt sind.

Bei Bauteilen, insbesondere integrierten Schaltungen (IC), kann eine vernünftige Vorbehandlung aufgrund allgemeiner Erkenntnisse und Erfahrungen noch relativ leicht festgelegt werden. Bei höheren Integrationsstufen, wie z. B. ganzen Baugruppen, bestehend aus mehreren bestückten Leiterplatten, wird das Problem komplizierter; hier muss vermehrt Rücksicht genommen werden auf die späteren Einsatzbedingungen und auf die Zusammensetzung der Einheit (Stecker, Schalter, analoger oder digitaler Charakter, Abgleiche, Überwach- und Prüfbarkeit der Einheit usw.). Das aktive Betreiben der Einheiten unter wechselnder Temperatur (meistens thermische Zyklen), oftmals mit Aus- und Einschaltvorgängen, hat sich auf höherer Integrationsstufe bestens bewährt. Anderseits sind einzelne Firmen dazu übergegangen, bei rein digitalen Leiterplatten nur noch die Bauteile einzeln zu prüfen und vorzubehandeln. Dies hat den Vorteil, dass die IC bei der Vorbehandlung stärker belastet (z. B. Burn-in bei 125 °C) und damit Bauteilausfälle sicherer vermieden werden können, im Gegensatz zu einer Vorbehandlung, die lediglich auf Leiterplattenebene geschiehe. Dieses Vorgehen bedingt aber, dass der Fertigungsprozess gut beherrscht wird, d. h. dass die Qualitätsverminde rung durch Lagerung, Handhabung, Bestückung, Löten usw. unbedeutend ist<sup>1)</sup>.

## 2. Ausfallarten von IC und Vorbehandlungsmethoden

Leider herrscht in der Literatur keine Einigkeit bei der Verwendung und Einteilung der Begriffe für die verschiedenen Ausfallarten von IC. Oftmals wird nicht klar zwischen Ausfallmechanismus, Ausfallart (Erscheinungsform) und der Ursache des Ausfalls unterschieden. Dass die verschiedenen Hersteller für ähnliche Ausfallmechanismen z. T. stark unterschiedliche Aktivierungsenergien angeben, ist eher verständlich, da diese durch den Entwurf, das Ausgangsmaterial, den Herstellungsprozess usw. beeinflusst werden. Tabelle I fasst die typischen Ausfallmechanismen, Ausfallarten und Vorbehandlungsmethoden für IC zusammen. Nicht alle aufgezählten Ausfallarten können immer durch die angegebenen Vorbehandlungsschritte zum Verschwinden bzw. zum Ausbrechen gebracht werden. Oft haben Ausfallmechanismen nicht den Charakter von Früh ausfällen (z. B. Elektromigration). Die Liste in Tabelle I ist ferner nicht vollständig. Besonders bei LSI/VLSI-IC (kleinere Dimensionen) und neuen Technologien können weitere bzw.

<sup>1)</sup> Die Vorbehandlung ist meist nicht das beste Mittel, Entwicklung fehler auf die Spur zu kommen. Dies ist eindeutig die Aufgabe der viel ausgedehnteren Qualifikations- und Zuverlässigkeitstests.

| Ausfallart (Ausfallmechanismen)                                        | Symptome                                                                                 | Empfohlene Methode                     |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------|

| <i>Technologie bzw. Chip bezogen</i>                                   |                                                                                          |                                        |

| Ursprüngliches Silikonmaterial (engl. bulk), z. B. Gitterfehler, Risse | Beeinträchtigung der elektrischen Eigenschaften                                          | Hochtemperaturlagerung                 |

| Oberfläche (z. B. Contamination, Ionenwanderung)                       | Hohe Leckströme, logische Fehler                                                         | Burn-in, Zentrifuge                    |

| Oxyd, Passivierung (z. B. Pinholes)                                    | Hohe Leckströme, Kurzschluss                                                             | Hochtemperaturlagerung, Burn-in        |

| Diffusion (z. B. Maskenfehler)                                         | IC-Charakteristik leicht bis stark verändert                                             | Temperaturzyklen, Burn-in              |

| Metallisierung (z. B. Korrosion, Risse)                                | Kurzschluss oder Unterbruch zwischen Schaltungselementen auf Chip                        | Burn-in, Temperaturzyklen              |

| Weitere, wie z. B. Alpha-Partikel                                      | Softerrs                                                                                 | Überwachtes Burn-in                    |

| <i>Gehäuse- bzw. verpackungsbezogen</i>                                |                                                                                          |                                        |

| Kontaktierung (Bonding; z. B. keine Haftung des Anschlusses)           | Kein elektrischer Kontakt über betreffenden Anschluss                                    | Temperaturzyklen, Zentrifuge, Burn-in  |

| Chiphaltung                                                            | Intermittierende Kurzschlüsse, Totalausfall durch überhitzten Chip (zuwenig Wärmeabfuhr) | Temperaturzyklen, Zentrifuge, Burn-in  |

| Anschlussdrähte (Bonds, z. B. gebrochener Anschlussdraht)              | Elektrischer Unterbruch am betreffenden Anschluss                                        | Temperaturzyklen, Zentrifuge, Burn-in  |

| Gehäuse (z. B. Undichtigkeit)                                          | Oberflächenkorrosion des Chips                                                           | Thermische Zyklen, Dichtigkeitsprüfung |

| Anschlüsse extern                                                      | Matte, korrodierte Anschlüsse                                                            | Lötbarkeitsprüfung                     |

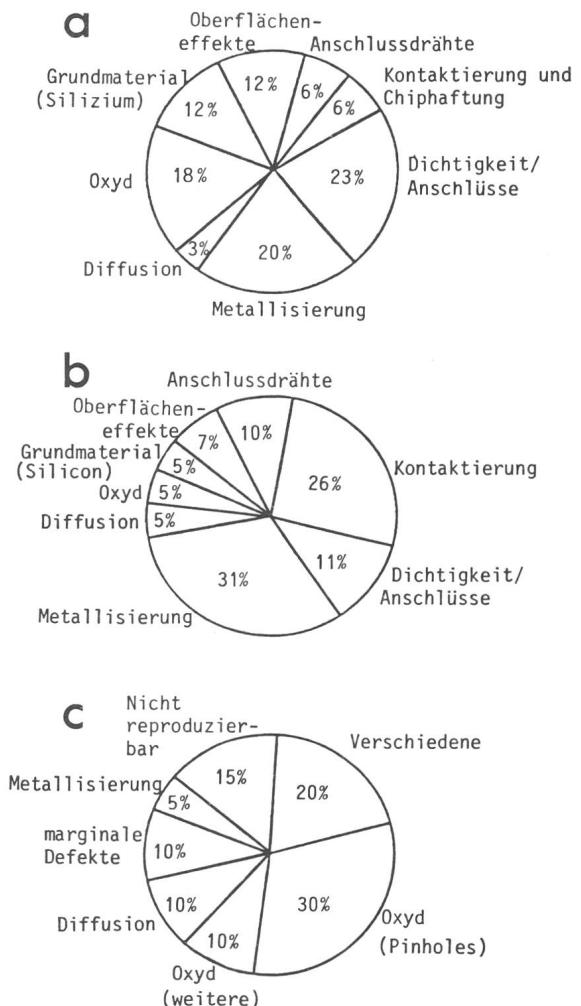

neue Ausfallmechanismen auftreten. Die Verteilung der Ausfallmechanismen für einige digitale IC ist in Figur 1 gegeben.

Die Periode der Frühausfälle dauert bei den IC zwischen 100 und 2000 Betriebsstunden. Eine Vorbehandlung bei Raumtemperatur ist deshalb wirtschaftlich nicht möglich. Eine selektive Auswahl der Vorbehandlungssequenz und die Tatsache, dass viele wichtige Ausfallmechanismen (chemisch-physikalische Abläufe) sich durch eine oder mehrere Einflussgrößen beschleunigen lassen, erlauben es, in kürzerer Zeit auf eine äquivalente Betriebsdauer zu kommen. Neben der Temperatur (Junction Temperatur) gibt es je nach Ausfallmechanismus noch weitere beschleunigende Faktoren, wie z. B. das elektrische Feld, die Stromdichte, der Temperaturgradient und die Feuchtigkeit, die jedoch zum Teil nur indirekt beeinflusst werden können.

Der Beschleunigungsfaktor  $F$ , den man für einen gegebenen Fehlermechanismus durch Erhöhung der Temperatur erreicht, kann nach dem Modell von *Arrhenius* wie folgt berechnet werden:

$$F = \lambda_1 / \lambda_2 = \exp [EA/k \cdot (1/T_2 - 1/T_1)]$$

$\lambda_1, \lambda_2$  Ausfallrate für die betrachtete Ausfallart bei  $T_1$  bzw.  $T_2$ .

EA Aktivierungsenergie des betreffenden Ausfallmechanismus. Ist diese bekannt oder kann sie geschützt werden, so kann  $F$  berechnet werden. Je grösser EA ist (Tab. II), desto grösser ist die Temperaturempfindlichkeit des jeweiligen Ausfallmechanismus.

$k$  Boltzmannkonstante ( $8.617 \times 10^{-5}$  eV/K)

$T_1, T_2$  Junction Temperatur in  $^{\circ}$ K, dabei ist  $T_J = T_A + P_D \times \theta_{JA}$ ,  $T_J$  die Junction Temperatur,  $T_A$  die Umgebungstemperatur,  $P_D$  die Verlustleistung und  $\theta_{JA}$  der thermische Widerstand des Gehäuses (typisch  $100^{\circ}$ K/W ohne Luftstrom,  $60-70^{\circ}$ K/W bei Luftstrom von ca. 2,5 m/S).

Der Anwender wird kaum an der Ausfallrate  $\lambda$  von einzelnen Ausfallarten interessiert sein; er benötigt meistens die Ausfallrate des ganzen IC. Daher ist es üblich, mit der mittleren

Beschleunigungsfaktoren für verschiedene Aktivierungsenergien (Arrhenius-Modell), normiert auf 55 °C [5]

Tabelle II

| Testtemperatur | 0,3 eV | 0,4 eV | 0,5 eV | 0,6 eV | 0,7 eV   | 0,8 eV    | 0,9 eV    | 1,0 eV      |

|----------------|--------|--------|--------|--------|----------|-----------|-----------|-------------|

| 0 °C           | 0,12   | 0,058  | 0,028  | 0,014  | 0,007    | 0,003     | 0,0016    | 0,00081     |

| 25 °C          | 0,34   | 0,24   | 0,169  | 0,118  | 0,083    | 0,058     | 0,041     | 0,0285      |

| 35 °C          | 0,50   | 0,40   | 0,317  | 0,25   | 0,20     | 0,16      | 0,127     | 0,1007      |

| 55 °C          | 1,0    | 1,0    | 1,0    | 1,0    | 1,0      | 1,0       | 1,0       | 1,0         |

| 70 °C          | 1,59   | 1,85   | 2,17   | 2,53   | 2,95     | 3,44      | 4,02      | 4,69        |

| 85 °C          | 2,43   | 3,27   | 4,4    | 5,91   | 7,93     | 10,7      | 14,4      | 19,3        |

| 100 °C         | 3,59   | 5,50   | 8,43   | 12,9   | 19,7     | 30,3      | 46,4      | 71,1        |

| 125 °C         | 6,46   | 11,99  | 22,4   | 41,7   | 77,3     | 145,0     | 269,0     | 501,0       |

| 150 °C         | 10,8   | 23,86  | 52,0   | 117,1  | 257,5    | 573,0     | 1 267,0   | 2 804,0     |

| 175 °C         | 17,1   | 44,0   | 113,8  | 293,0  | 750,5    | 1 948,0   | 5 021,0   | 12 942,0    |

| 200 °C         | 25,8   | 75,9   | 225,4  | 666,0  | 1 954,0  | 5 818,0   | 17 197,0  | 50 824,0    |

| 250 °C         | 52,1   | 193,6  | 728,0  | 2718,0 | 10 062,0 | 37 928,0  | 141 712,0 | 529 415,0   |

| 300 °C         | 93,1   | 419,8  | 1914,0 | 8676,0 | 38 935,0 | 178 254,0 | 808 013,8 | 3 663 626,0 |

Beispiel: Bei einem EPROM 2732 mit einer Temperaturhochlagerung von 24 h bei 125 °C kann die «data retention» von über 1000 h bei 55 °C simuliert werden.

Aktivierungsenergie zu operieren (Tab. III). Um die Grenzen des Modells von *Arrhenius* anzudeuten, sei noch erwähnt, dass die Korrosion der Chipoberfläche in gewissen Fällen bei tieferen Temperaturen beschleunigt wird, oder dass bei Oxyddefekten das angelegte elektrische Feld ( $V_{CC!}$ ) eine ungleich höhere Beschleunigung bewirkt. In [2] wird z. B. ein Beschleunigungsfaktor von  $10^7$  je MV/cm erwähnt. Je höher EA ist, um so wirkungsvoller sind die Vorbehandlungsprozeduren bei erhöhter Temperatur (Tab. II).

### 3. Vorbehandlung von integrierten Schaltungen nach MIL-STD 883

Es wurde eingangs erwähnt, dass eine Vorbehandlung in erster Linie darauf ausgerichtet sein muss, die möglichen und dominanten Fehlermechanismen abzudecken, was jedoch nicht immer wirtschaftlich realisierbar ist, da die Fehlermechanismen in Art und Intensität von Los zu Los, von Technologie zu Technologie und von Hersteller zu Hersteller starken Schwankungen unterworfen sind. Es ist trotz dieser Tatsache mit der MIL-STD 883 (Test Methods and Procedures for Microelectronics) gelungen, eine Vorbehandlungsnorm aufzustellen, die gleichermaßen von Herstellern und Anwendern anerkannt und befolgt wird. Auch wenn der Nutzen einiger in dieser Norm beschriebener Methoden nicht überall anerkannt ist, hat diese dazu beigetragen, die verwirrende Vielzahl von Methoden und Bedingungen besser zu definieren und

Die Vorbehandlungsklassen und dazugehörigen Operationen nach MIL-STD 883 Method 5004

Tabelle IV

| Operationen                                 | S <sup>a)</sup> | B | C | Methode nach MIL-STD 883          |

|---------------------------------------------|-----------------|---|---|-----------------------------------|

| Visuelle Kontrolle (intern)                 | ×               | × | × | 2010                              |

| Hochtemperaturlagerung                      | ×               | × | × | 1008                              |

| Temperaturzyklen                            |                 |   |   |                                   |

| Gas-Gas                                     | ×               | × | × | 1010                              |

| Zentrifuge                                  | ×               | × | × | 2001                              |

| Visuelle Kontrolle (extern)                 | ×               | × | × | 2009                              |

| Dichtigkeit<br>(fine und gross leak)        | ×               | × | × | 1014                              |

| Reduzierte elektr. Prüfung<br>(Pre-burn-in) | ×               | × |   | gemäss Hersteller-spezifikationen |

| Burn-in                                     | ×               | × |   | 1015                              |

| Elektrische Endprüfung                      | ×               | × | × | gemäss Hersteller-spezifikationen |

| Röntgen                                     | ×               |   |   | 2012                              |

<sup>a)</sup> Bei der Klasse S werden gewisse Operationen wiederholt oder gegenüber Klasse B und C in verschärfter Form durchgeführt. «Serialisation» und «Particle impact noise detection» kommen bei der S-Klasse noch hinzu.

zu ordnen. Ebenfalls ist den Herstellern von Prüfanlagen damit eine klare Leitlinie für die Konzeption ihrer Anlagen gegeben worden. Die darin enthaltene Methode 5004 (Screening Procedures) unterscheidet folgende drei Vorbehandlungssequenzen, die ihrer Schärfe entsprechend in drei Zuverlässigkeitssklassen eingeteilt werden: S = Raumfahrt; B = Militär, für Anwendungen, wo extreme Umweltbedingungen herrschen oder hohe Folgekosten anfallen; C: Militär, für Bodenstationen.

Die zu den drei Vorbehandlungsklassen gehörenden Vorbehandlungsschritte sind in Tabelle IV angegeben. Nach MIL-HDBK 217 (Reliability Prediction of Electronic Equipment) wären dabei die Fehlerraten der Klasse B um Größenordnungen kleiner als die für gewöhnliche Komponenten ohne jede Vorbehandlung (Commercial grade).

Die in den Vorbehandlungsklassen nach Methode 5004 aufgeführten Vorbehandlungsschritte sind in der MIL-STD 883 genau beschrieben. Zuerst wird der Zweck der jeweiligen Vorbehandlung angegeben, dann werden die zur Durchführung notwendigen Apparaturen aufgelistet, anschliessend folgt eine detaillierte Beschreibung der Prozedur unter Angabe der verschiedenen Prüfschärfen, der durchzuführenden Messungen,

Aktivierungsenergien [2...5]

Tabelle III

|                       |                      |                                  |           |

|-----------------------|----------------------|----------------------------------|-----------|

| Für Fehlermechanismen | MOS                  | Oxyd                             | 0,3 eV    |

|                       |                      | Silikondefekte                   | 0,3 eV    |

|                       | MOS                  | Kontamination                    | 1,4 eV    |

|                       | NMOS                 | (Plastik) Korrosion<br>(Feuchte) | 0,54 eV   |

|                       | NMOS                 | Mobile Ionen                     | 1-1,35 eV |

|                       | EPROM                | Bitänderung<br>(data retention)  | 0,6 eV    |

| Mittlere EA für IC    | CMOS                 |                                  | 1,1 eV    |

|                       | Linear und MOS       |                                  | 0,7 eV    |

|                       | TTL (Plastik)        |                                  | 0,6 eV    |

|                       | 16 k RAM (Keramik)   |                                  | 0,5 eV    |

|                       | 16 k EPROM (Keramik) |                                  | 0,5 eV    |

der Fehlerkriterien usw. Beispiel: Die Methode 1008.1 (die Ziffer nach dem Punkt gibt den Revisionsstand an) beschreibt die Hochtemperaturlagerung. Es werden dabei 8 verschiedene Prüfschärfen unterschieden: A (75 °C), B (125 °C), C (175 °C), ... H (400 °C). Die minimale Verweilzeit im Ofen soll 24 h betragen.

Hersteller und Anwender sind nun dazu übergegangen, eigene von der Methode 5004 abweichende Vorbehandlungsabläufe durchzuführen. Es gibt gute Gründe, dies zu tun, da die MIL-STD 883 auf hermetische Gehäuse und Militäranwendung ausgerichtet ist. Es ist jedoch von Vorteil, wenn man sich auf die einzelnen Vorbehandlungsschritte (Methoden) der MIL-STD 883 bezieht oder Abweichungen davon klar festhält. Beispielsweise kann die Dichtigkeit und die konstante Beschleunigung (Zentrifuge) nur für Keramikgehäuse angewendet werden. Ein weiteres Problem bildet die interne visuelle Kontrolle, die im nachhinein vom Anwender nicht mehr durchgeführt werden kann. Für spezielle IC (z.B. EPROM, EA-ROM) wäre die Anwendung der Abläufe nach Tabelle IV grundsätzlich nicht angebracht.

Aus Gründen der Verfügbarkeit, des Terms und oft auch wegen günstigeren Preisen, lassen Anwender ihre IC in externen Testinstituten vorbehandeln. Darüber hinaus ist es für den europäischen Anwender kleiner und mittlerer Stückmengen fast unmöglich, Zertifikate bzw. Prüfprotokolle je Los über die vom Hersteller durchgeführte Vorbehandlung zu erhalten. Die Zusammenarbeit mit einem Testinstitut bringt den Vorteil, dass die Verantwortlichen der Qualitäts- und Entwicklungsabteilungen Einfluss auf den Vorbehandlungsablauf, die Schärfegrade und sogar die elektrischen Prüfprogramme haben können. Dadurch kann sich eine Firma das für die Qualitäts- und Zuverlässigkeitssicherung von LSI/VLSI-IC notwendige Know-how erarbeiten, ohne dass hohe eigene Investitionen vorgenommen werden müssen. Findet der Anwender die Zeit gekommen, um die notwendigen Anlagen selbst zu beschaffen, so kann er aufgrund der gewonnenen Erfahrung und mit der Beratung eines Unabhängigen leichter die richtige Wahl treffen.

#### Vorbehandlungsablauf für IC in Militärgeräten und Anlagen in extremen Umweltbedingungen

Tabelle V

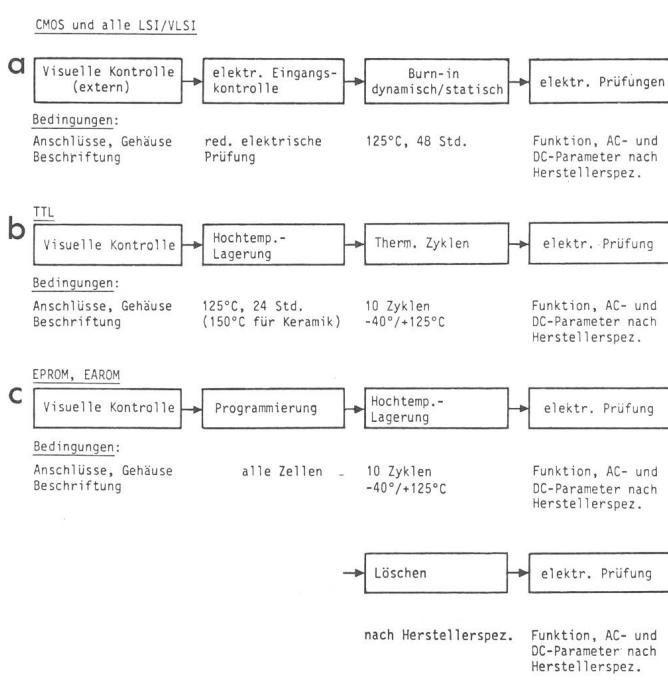

- A. CMOS und alle LSI/VLSI wie Figur 2, jedoch mit einer Hochtemperaturlagerung und therm. Zyklen vor dem Burn-in. Bei Verwendung von hermetisch verpackten IC ist eine Dichtigkeitsprüfung (mind. Stichprobe) zu empfehlen.

- B. TTL wie CMOS, jedoch Burn-in nur statisch.

- C. EPROM, EA-ROM wie Figur 2, jedoch ausgedehntere Sequenz mit zweimaligem Programmieren, Lagern bei 150 °C, Prüfen und Löschen. Dichtigkeitsprüfungen sehr empfehlenswert.

#### 4. Vorschläge für Vorbehandlungsabläufe

Bei der Festlegung einer Vorbehandlungssequenz sind folgende Punkte zu beachten:

1. Technologie

2. Komplexität des IC

3. Besonderheiten der Anwendung (Umgebungsbedingungen)

4. Gehäuse, Verpackung

5. Stellenwert der Zuverlässigkeit und Qualität

6. Preis der Komponente, Preis der Vorbehandlung

7. Erfahrungen, Hersteller und eigene

8. Erkenntnisse aus Fehleranalysen

Diese Kriterien berücksichtigend, wurden am Centre Suisse d'Essais des Composants Electroniques (CSEE) in Zusammenarbeit mit Schweizerkunden Vorbehandlungssequenzen für verschiedene Technologien festgelegt und mit Erfolg angewandt (Fig. 2 und Tab. V). Es werden jedoch auch andere Sequenzen laufend erprobt und die Resultate verglichen. Untersuchungen haben z.B. gezeigt, dass die Reihenfolge, in der die einzelnen Vorbehandlungsschritte durchgeführt werden, einen Einfluss auf die Wirksamkeit der Vorbehandlung hat.

Bei der Beurteilung der Wirksamkeit der einzelnen Vorbehandlungsschritte sind vor allem die in den IC latent vorhandenen Ausfälle entscheidend. Weiterhin muss der Erfolg an der Anzahl der entdeckten bzw. zum Ausbruch gebrachten Ausfälle im Verhältnis zum Preis der jeweiligen Schritte gemessen werden. Die billigen Operationen (Hochtemperaturlagerung und thermische Zyklen, beide ohne Anlegen der Speisespannung) können die teureren (Burn-in, Zentrifuge, Dichtigkeit) nur in Ausnahmefällen ersetzen. Das Burn-in kommt dem wirklichen Einsatz der Komponenten am nächsten (Temperatur, elektrisches Feld und Stromdichte bewirken hier Frühausfälle) und ist deshalb ein sehr wirkungsvolles Mittel zur Vorbehandlung. Die Art der Durchführung (Temperaturwahl, Konfiguration der Beschaltung, anzulegende Spannungen bzw. Signale beim dynamischen Burn-in usw.) verlangt jedoch einiges an Erfahrung und Wissen. Falls bei einem Los von IC in Keramikgehäusen wirklich Dichtigkeitsprobleme bestehen, so ist die Dichtigkeitsprüfung das einzige Mittel, dies im Rahmen einer Vorbehandlung herauszufinden. Deshalb ist es besonders bei IC, die in Außenanlagen oder in Anlagen mit längeren Arbeitsunterbrüchen eingesetzt werden, angebracht, die etwas teurere Dichtigkeitsprüfung 100prozentig durchzuführen.

Oft wird die Frage gestellt, in welcher Tiefe die IC im Verhältnis zu diskreten Halbleitern und passiven Elementen vorzubehandeln bzw. zu prüfen seien. Auf diese Frage kann aufgrund der Komplexität, der intrinsischen Zuverlässigkeit und

Fig. 2 Vorbehandlungsablauf für IC, die in Industriegeräten eingesetzt werden

|                        | SSI/MSI | LSI  |

|------------------------|---------|------|

| Elektrische Prüfung    | -20     | 1.—  |

| Visuelle Kontrolle     | -05     | -07  |

| Hochtemperaturlagerung | -03     | -05  |

| Temperaturzyklen       | -08     | -10  |

| Dichtigkeit            | -30     | -50  |

| Zentrifuge             | -25     | -40  |

| Burn-in (48 h)         | -50     | 1.50 |

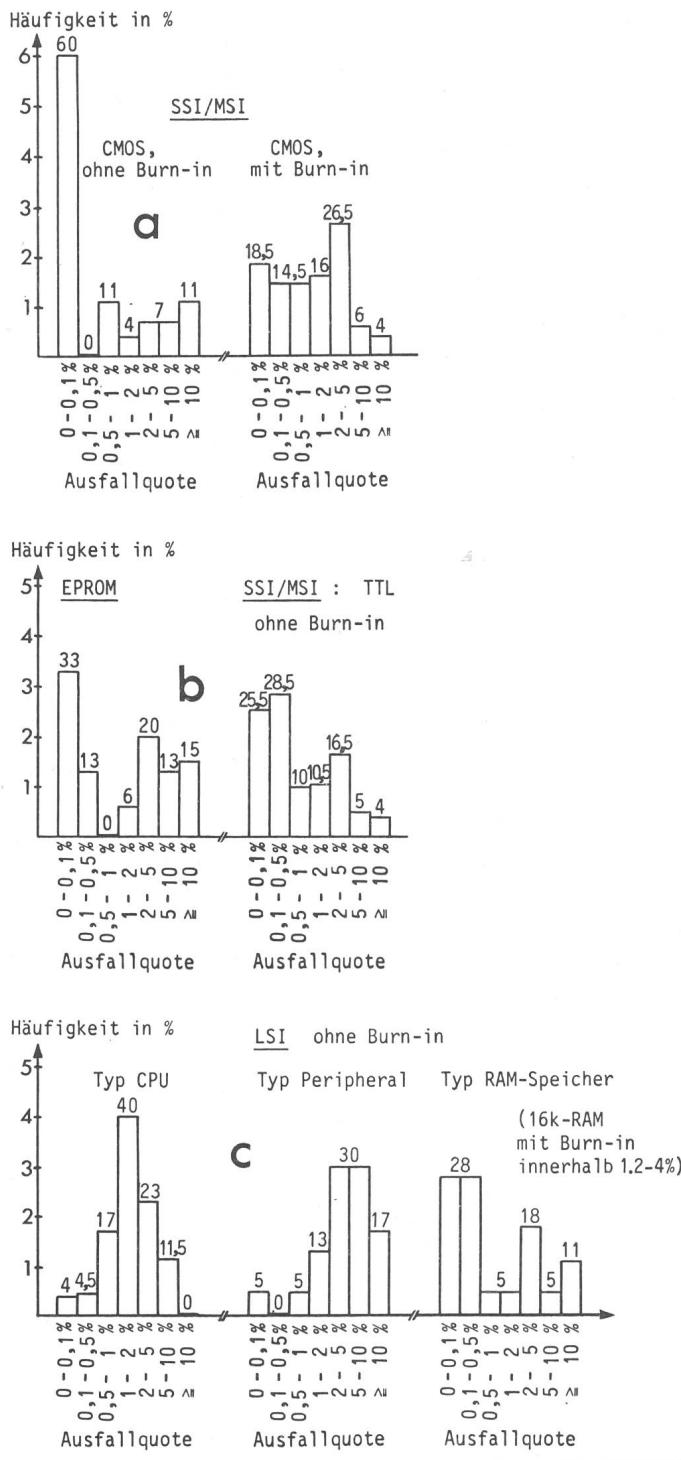

Fig. 3 Am CSEE ermittelte Ausfälle im 2. Semester 1980 und 1. Semester 1981 (Einteilung der Lose nach Fehlerquote)

basierend auf Erfahrungen folgende Faustregel angegeben werden: der Aufwand sollte sich etwa wie 3 : 2 : 1 für die in der obigen Reihenfolge erwähnten Bauteile verhalten. Dabei sind kritische Bauteile, z.B. optoelektronische Bauteile und Leistungsbauteile je nach Anwendung ebenfalls zur höheren Klasse zu zählen.

Vielfach wird der Einwand erhoben, dass mit zu rigoroser Vorbehandlung und Prüfung viele Bauteile zum Ausfall gebracht würden, die sonst ohne weiteres jahrelang gut in ihrer Anwendung funktioniert hätten (overkill). Dieser Vorwurf kann nicht mit mathematisch exakten Beweisen entkräftet werden, jedoch sprechen folgende Argumente gegen diese Befürchtung: durch eine grosse Erfahrung entwickelt der Spezialist ein Gespür für «normale» Ausfallquoten; wird bei einem Los nach einer Vorbehandlung eine überdurchschnittliche Anzahl von Ausfällen registriert, so wird jeder seriöse Prüfer eine Untersuchung der Ursache veranlassen. Mit einer Ausfallanalyse [7] und einem Vergleich mit noch nicht vorbehandelten Bauteilen des gleichen Loses kann die Ursache mit grosser Sicherheit aufgedeckt werden. Weiterhin sind die angewandten Methoden durch Hunderte von Losen verschiedenster Herkunft und Technologie erprobt und verifiziert worden, und durch die Markierung der vorbehandelten Bauteile wird sogar der Feedback vom Einsatz her sichergestellt.

## 5. Aufwand und Nutzen

Die Durchführung der Vorbehandlung für LSI/VLSI-IC inklusive elektrische Prüfung im Hause ist schon für eine Firma mittlerer Grösse ein finanzielles Problem (Gesamtinvestitionen ca. sFr. 3 Mio., jährliche Kosten ca. sFr. 1 Mio.). Dies ist auch ein Grund, weshalb sich Anwender und Hersteller mehr und mehr an Testinstitute wenden. Die Preise, die man dort für eine Vorbehandlung bezahlt, können je nach Losgrösse, Schärfegrade und IC schwanken. Tabelle VI gibt einige Richtpreise an.

Die Prüfsequenz von Punkt C in Figur 2 kommt auf ca. Fr. 2.50 und von Punkt C in Tabelle V auf ca. Fr. 5.- zu stehen. Es gibt einfache und aufwendige Methoden, die möglichen Einsparungen durch eine Vorbehandlung von IC zu berechnen (siehe z.B. [1; 3; 8]). Da diese Berechnungen jedoch alle auf statistischen Werten beruhen, ist ein praxisbezogener Beweis im nachhinein sehr schwierig zu führen. Weitere Gründe, eine 100prozentige Vorbehandlung der IC durchzuführen, bestehen im Bedürfnis, eine mögliche Fehlerquelle auszuschalten, um Fabrikations- und Entwicklungsfehlern gezielter auf die Spur zu kommen, hohe Garantie- und Servicekosten zu verhindern oder den Wünschen bzw. Vorschriften des Kunden zu entsprechen.

## 6. Erfahrungen am CSEE

Wie im ersten Abschnitt erwähnt, wurde auch am CSEE festgestellt, dass Verhalten bzw. Fehlerquote von Los zu Los stark abweichen. Das Burn-in hat sich mit Ausnahme der reifen und stabilen PMOS- und z.T. TTL-Technologie als sehr effizient erwiesen. Wird bei einzelnen Produkten eine sehr kleine Ausfallquote (einige Promille) festgestellt, so wird dem jeweiligen Kunden empfohlen, die Vorbehandlung bei der nächsten Lieferung nur noch als Stichprobe (etwa 10 bis 20 %) durchzuführen. Bei CMOS und LSI/VLSI ist ein Burn-in trotz der Kosten notwendig. EPROM, die über Jahre in Systemen eingebaut bleiben, sollten rigoros geprüft werden, da bei die-

sem Element die «data retention» (Beibehaltung der Information) und die Programmierbarkeit ein Problem bilden können. Custom-IC können besonders bei den ersten Losen eine grosse Fehlerquote aufweisen; eine 100prozentige Prüfung und Vorbehandlung sollte Bestandteil der Beschaffung sein. Bei allen IC sollte die Prüfung bei der wahrscheinlichen Einsatztemperatur durchgeführt werden.

Oft beklagen sich Kunden als Anwender von IC, dass das Prüfen und die Vorbehandlung im Verhältnis zu den IC-Stückpreisen zu teuer seien. Diesem Einwand kann entgegnet werden, dass ein IC von Fr. -70 deshalb so billig ist, weil er nicht vorbehandelt wurde. Es ist klar, dass auch die Hersteller sich den Gesetzen des Marktes beugen müssen; die Qualität hat auch hier ihren Preis. So bietet jeder Hersteller auch vorbehandelte IC an, in Europa ist allerdings meist mit längeren Lieferfristen und hohen Preisen zu rechnen.

Abschliessend fasst Figur 3 einige summarische Ausfallstatistiken zusammen. Ausgewertet wurden ca. 280 Lose. Massgebend als Ausfallkriterium waren jeweils die Herstellerspezifikationen. Besonders interessant ist der Unterschied zwischen CMOS mit und ohne Burn-in. Immer häufiger wünschen Kunden des CSEE gerade für kritische Anwendungen CMOS-Komponenten mit Burn-in einzusetzen. Die Darstellungen in Figur 3a zeigen, dass dadurch offenbar vermehrt Frühhausfälle gefunden werden. Zu den CMOS- und TTL-Auswertungen ist zu bemerken, dass einige Kunden dem CSEE nur die sog. Problemkomponenten zur Prüfung zustellen, also IC-Typen, bei denen sie erfahrungsgemäss Schwierigkeiten hatten. Die Auswertung der EPROM (Fig. 3b) beschränkt sich auf folgende Typen: 1702, 2708, 2716 und 2732; die Streuungen der Ausfallquoten sind bei diesen Bauteiltypen besonders ausge-

prägt. LSI-Bauteile (CPU, Peripherals, RAM) wurden fast ausschliesslich bei erhöhter Temperatur (+ 70 °C) geprüft, da eine stärkere Temperaturabhängigkeit festgestellt wurde (Fig. 3c). Die Darstellung über die RAM beinhaltet alle Speicherarten; bei den 16-K ist eine erhebliche Zunahme der Ausfallquote nach dem Burn-in zu verzeichnen.

## Literatur

- [1] *A. Birolini*: Bedeutung der Prüfung und Vorbehandlung elektronischer Bauteile und Geräte. Bull. SEV/VSE 72(1981)15, S. 805...811.

- [2] *R. Reininger*: HMOS II reliability report. RR-26. Santa Clara/California, Intel Corporation, 1980.

- [3a] *The reliability handbook*. Santa Clara/California, National Semiconductor Corporation, 1979.

- [3b] *P. Naumchick and R. A. Kramer*: Reliability of N-channel silicon-gate memory and microprocessor components (Reliability of NMOS ICs PR-1). Santa Clara/California, National Semiconductor Corporation, 1978.

- [4] *Results of the reliability studies and of the improvements made by SGS-ATES to its COS/MOS family*. Agrate/Milano, Società Generali Semiconduttori (SGS-ATES), 1978.

- [5] Qualität und Zuverlässigkeit. Qualitätskontrolle. Freising, Texas Instruments Deutschland GmbH, 1978.

- [6] '80 Semiconductor data book. Hitachi IC memories. Tokyo, Hitachi Ltd., 1980.

- [7] *J.S. Smith*: Electrical overstress failure analysis in microcircuits. IEEE Proceedings of the Annual Reliability Physics Symposium 16(1978), p. 41...46.

- [8] *R. Lombardini*: Le contrôle de la fiabilité et l'accroissement de la complexité des dispositifs électroniques. Second colloque international sur la fiabilité et la maintenabilité, Perros-Guirec – Trégastel/France, 8...12 septembre 1980. Lannion, Centre National d'Etudes des Télécommunications (CNET), Centre de Fiabilité, 1980, p. 195...199.

- [9] *D. Ströhle*: Feuchteprobleme bei LSI-S. NTG-Fachberichte 77(1981), S. 106.

- [10] *R.T. Anderson*: Reliability design handbook. RDH-376. New York, Reliability Analysis Center/Griffiss Air Force Base, 1976.

- [11] *Microcircuit screening effectiveness*. Technical reliability study TRS-1. New York, Reliability Analysis Center/Griffiss Air Force Base, 1978.

- [12] *R.A. Evans*: Engineers or witch doctors? IEEE Trans. R 28(1975)5, p. 337.

## Adresse des Autors

*R. Lombardini*, dipl. El.-Ing. ETH, ASE-CSEE (Association Suisse des Electriciens – Centre Suisse d'Essais des Composants Electroniques), ruele Vaucher 22, 2000 Neuchâtel.