|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 72 (1981)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 15                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | Bedeutung der Prüfung und Vorbehandlung elektronischer Bauteile und Geräte                                                                                                                                                |

| <b>Autor:</b>       | Birolini, A.                                                                                                                                                                                                              |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-905132">https://doi.org/10.5169/seals-905132</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

## Elektrotechnik und Elektronik Electrotechnique et électronique

### Bedeutung der Prüfung und Vorbehandlung elektronischer Bauteile und Geräte

Von A. Birolini

621.38;

*Prüfungen und Vorbehandlungen sind unerlässlich, um die für eine vorgesehene Anwendung relevanten Fehler zu entdecken und möglichst alle Frühaußfälle noch vor Beginn der Nutzungsphase zu eliminieren. Kosten- und Terminbetrachtungen zwingen aber zu einer Koordination und Einschränkung. Nach einer kurzen Einführung werden die wichtigsten Aspekte der Prüfung, insbesondere der Eingangsprüfung, Umweltprüfung und Zuverlässigkeitssprüfung sowie der Vorbehandlung elektronischer Bauteile und Geräte dargelegt.*

*Les essais et le déverminage sont indispensables pour faire ressortir tous les défauts importants pour une application donnée et éliminer le plus possible de défaillances précoces avant le début de la phase d'utilisation. Des considérations économiques ou de délais imposent toutefois certaines restrictions et une coordination des essais. Après une courte introduction, les aspects principaux concernant les essais et le déverminage de composants et équipements électroniques sont discutés, en particulier les essais de réception, d'environnement et de fiabilité.*

#### 1. Einleitung

Inwieweit ein gegebener Bauteil oder ein Gerät die gestellten Anforderungen, z.B. in bezug auf Leistungsparameter oder Zuverlässigkeit, erfüllt, kann nur mit Hilfe einer geeigneten Prüfung festgestellt werden. Eine solche Prüfung wird in der Regel an verschiedenen Projektphasen oder Integrationsniveaus durchgeführt und deshalb als Eingangsprüfung, Zwischenprüfung, Endprüfung oder Abnahmeprüfung bezeichnet. Je nach Art und Tiefe der Prüfung wird ferner zwischen Parameterprüfung, Funktionsprüfung, Charakterisierung, Qualifikationsprüfung, Zuverlässigkeitssprüfung usw. unterschieden.

Im Zusammenhang mit elektronischen Geräten und Anlagen war die Prüfung auf Bauteile- und Leiterplattenebene bis zur Einführung der komplexen integrierten Schaltungen (LSI- und VLSI-IC) noch leicht überblickbar. Insbesondere konnte man praktisch alle Parameter, Zustände und Zustandsfolgen überprüfen. Durch den Einsatz von Mikroprozessoren und Speichern sind aber auch diese Prüfungen problematisch geworden. Einerseits, weil solche Bauteile sehr leistungsfähig und extrem vielseitig sind und andererseits, weil sie die Zuverlässigkeit von ganzen Modulen oder sogar Geräten empfindlich beeinflussen können.

Die Frage *was, wie und wo* geprüft werden soll, um die Prüfkosten so tief wie möglich zu halten und trotzdem alle für die vorgesehene Anwendung relevanten Fehler entdecken zu können, ist damit auch auf dem Niveau Bauteile und Leiterplatten aktuell geworden.

Überlagert zu den Prüfschwierigkeiten kommt noch das Problem der Festlegung der optimalen Vorbehandlung hinzu, die es erlauben soll, vor Beginn der Nutzungsphase möglichst

alle Frühaußfälle zu eliminieren. Die Optimierung wird dabei in bezug auf die Kosten, für eine vorgegebene Verbesserung der Zuverlässigkeit, oder in bezug auf die Wirksamkeit der Vorbehandlung, für gegebene feste Kosten vorgenommen.

Aus diesen Überlegungen ergibt sich im Zusammenhang mit der Entwicklung und Herstellung komplexer Geräte und Anlagen folgende prinzipielle Frage:

*Auf welchem Integrationsniveau soll was, wie und wo geprüft und vorbehandelt werden, um kostenoptimal die für eine vorgesehene Anwendung relevanten Fehler zu entdecken und möglichst alle Frühaußfälle zu eliminieren?*

Die Antwort auf diese Frage ist schwierig, weil sowohl über die Fehlerentdeckungswahrscheinlichkeit einer bestimmten Prüfung wie auch über die Ausfallmechanismen, die durch eine gegebene Vorbehandlung aktiviert werden sollen, oft zuwenig genaue Kenntnisse vorliegen. Ganz allgemein sind jedoch im Hinblick auf eine Optimierung von Prüfungen und Vorbehandlungen stets folgende Grundregeln zu beachten:

1. Bei Kostenbetrachtungen ist immer die ganze Kette bis zu den Garantieleistungen zu berücksichtigen.

2. Mit Prüfungen und Vorbehandlungen soll man beim möglichst tiefsten Integrationsniveau beginnen und selektiv operieren.

3. Qualifikationsprüfungen sollen nicht aus Kosten- oder Termingründen übersprungen werden.

4. Die verschiedenen Prüfungen sollen soweit wie möglich koordiniert werden.

5. Die Prüfungen und Vorbehandlungen sind sorgfältig zu planen und durchzuführen, damit die Reproduzierbarkeit und eine lückenlose Interpretation der Prüfresultate sichergestellt sind.

6. Prüfungen und Vorbehandlungen sind stets durch ein effizientes Qualitätsdatensystem zu unterstützen.

7. Die Probleme betreffend Prüfungen und Vorbehandlungen müssen möglichst früh, schon in der Entwicklungs- und Konstruktionsphase, diskutiert werden (Design Reviews).

Im folgenden soll auf die wichtigsten Aspekte der Prüfung und Vorbehandlung elektronischer Bauteile und Geräte näher eingegangen werden. Für eine allgemeine Darlegung der Aufgaben und Methoden zur Sicherstellung der Qualität und der Zuverlässigkeit sei auf [1...7] verwiesen.

## 2. Prüfungen

### 2.1 Eingangsprüfungen

Mit der Eingangsprüfung wird festgestellt, ob eine angelieferte Betrachtungseinheit (Stoff, Bauteil, Leiterplatte usw.) fehlerfrei ist. Je nach der Bedeutung der Betrachtungseinheit für die Zuverlässigkeit oder die Sicherheit des ganzen Gerätes, sowie der zu erwartenden Fehlerquote, wird eine Stichproben- oder eine hundertprozentige Prüfung durchgeführt. Im Falle komplexer integrierter Schaltungen zeigt die Erfahrung, dass die Fehlerquote im Bereich von 0,5 bis 5 % liegt und damit die Kosten für eine hundertprozentige Eingangsprüfung sehr oft tiefer sind als die Summe der Kosten für eine Stichprobenprüfung und den späteren Ersatz der defekten IC. Folgendes Beispiel soll dies verdeutlichen:

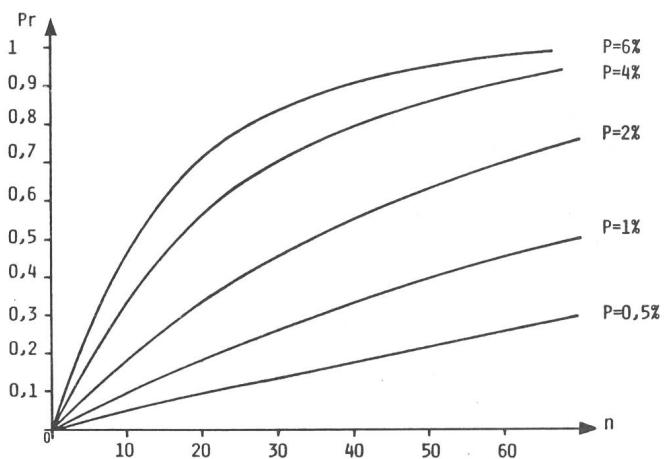

Werden eine Anzahl Leiterplatten mit je 25 IC mit Fehlerquote 2 % bestückt, so sind ohne Eingangsprüfung nach Figur 1 40 % der Leiterplatten defekt. Nimmt man an, dass die Reparatur einer Leiterplatte Fr. 100.– kostet, bedeutet dies, dass eine hundertprozentige Eingangsprüfung bis zu Prüfkosten von Fr. 1.60 je IC billiger ist.

In der Praxis kann der Vorteil der hundertprozentigen Eingangsprüfung aus folgenden Gründen noch höher liegen:

1. Die Fehlerquote ist bei LSI- und vor allem bei VLSI-IC oft grösser als 2 %. Dadurch steigt auch die Anzahl der defekten Leiterplatten. Die Eingangsprüfung von LSI/VLSI-IC liegt im Bereich von Fr. 1.– bis 2.–.

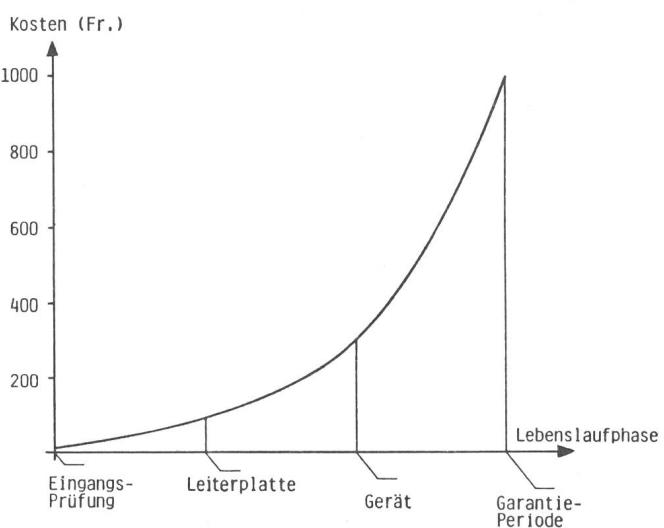

2. Die Entdeckung und der Ersatz eines defekten IC kann wesentlich höher als Fr. 100.– zu stehen kommen; vor allem, wenn es um LSI- oder VLSI-IC oder um eine Reparatur in der Garantieperiode geht (Fig. 2).

3. Im Falle einer hundertprozentigen Eingangsprüfung kann man in der Regel fordern, dass die defekten IC ersetzt werden.

Fig. 2 Typische Kosten für den Ersatz eines defekten LSI-IC während des Lebenslaufes eines Gerätes (Industrieprodukte)

4. Dank einer hundertprozentigen Eingangsprüfung kann die Prüfung auf Leiterplatten- und Modulebene vereinfacht werden.

5. Durch eine hundertprozentige Eingangsprüfung ist man den Schwankungen der Fehlerquote von Los zu Los nicht mehr ausgesetzt.

Auch eine hundertprozentige Eingangsprüfung kann jedoch nicht gewährleisten, dass alle auf einer bestückten Leiterplatte befestigten IC fehlerfrei sind. Defekte IC können durch falsche Handhabung, transiente Vorgänge, Montagefehler usw. eingeführt werden. Dank der Eingangsprüfung weiss man aber, dass die IC fehlerfrei waren, so dass die Fehlerursachen in der Fertigung oder in der Konstruktion gesucht und behoben werden müssen.

Wie in der Einleitung schon erwähnt wurde, müssen bei der Funktionsprüfung von LSI- und VLSI-IC grosse Einschränkungen gemacht werden. Dies, weil es einfach nicht möglich ist, alle Zustände und Zustandsfolgen zu prüfen. Für einen Speicher mit  $n$  Zellen sind z.B. bis zu  $2^n$  Zustände und  $n!$  Zustandsfolgen möglich, was für einen Speicher mit  $n = 50$  Zellen insgesamt schon etwa  $10^{80}$  Prüfmöglichkeiten geben würde.

Zur Durchführung der Eingangsprüfung elektronischer Bauteile werden auf dem Markt zahlreiche Prüfautomaten und Prüfanlagen angeboten. Während Prüfautomaten für einfache Bauteile etwa 20000 bis 60000 Fr. kosten, liegen Prüfanlagen für LSI/VLSI-IC im Bereich von 0,5 bis 1,5 Mio Fr. Das grosse Problem bei der Prüfung der LSI/VLSI-IC liegt aber nicht nur in den sehr hohen Investitionskosten für die Prüfanlage, sondern vielmehr in den Anschaffungs- und Wartungskosten der Prüfprogramme (Tabelle I). Es ist deshalb üblich, dass auch grosse Benutzer und sogar Hersteller ihre LSI/VLSI-IC durch spezialisierte Prüfzentren prüfen lassen. In den USA existieren etwa 80 derartige Prüfzentren, in Europa 9, wovon 1 in der Schweiz [8; 9].

### 2.2 Zwischen- und Endprüfungen

Zwischenprüfungen werden während der Fertigungsphase laufend durchgeführt, in der Regel am Ende jedes Integrationsschrittes. Ihr Zweck ist es, vor allem die Nahtstellen sowie die Parameter und die Funktion der fertiggestellten Betrach-

Fig. 1 Wahrscheinlichkeit (Pr), mindestens einen defekten Bauteil auf einer Printplatte, bestehend aus  $n$  Bauteilen mit Fehlerquote  $p$ , zu finden

$$Pr = 1 - (1 - p)^n$$

*Anschaffungs- und jährliche Betriebskosten für die Eingangsprüfung (elektrische Prüfung) integrierter Schaltungen, in 1000 Fr.*

Tabelle I

|                         | Prüfautomat für SSI/MSI-IC | Prüfanlage für LSI/VLSI-IC |

|-------------------------|----------------------------|----------------------------|

| Anschaffungskosten      | 50 bis 150                 | 500 bis 1500               |

| Betriebskosten pro Jahr | 80 bis 120                 | 500 bis 900                |

| – Personalkosten        | 1 Person                   | 3–4 Personen               |

| – Instandhaltung        | 5 bis 15                   | 50 bis 150                 |

| – Prüfprogramme         | –                          | 80 bis 100 <sup>1)</sup>   |

| – Abschreibung          | 10 bis 40                  | 150 bis 350                |

| – Übrige Kosten         | 5 bis 10                   | 10 bis 20                  |

<sup>1)</sup> ca. 10000...20000 Fr. pro Programm

tungseinheit (Leiterplatte, Modul, Baugruppe usw.) als Ganzes zu prüfen. Die Zwischenprüfung auf einem bestimmten Integrationsniveau kann die Prüfungen an tieferen Niveaus nicht ersetzen. Bei der Prüfung bestückter Leiterplatten können z.B. die komplexen IC trotz Anwendung einer leistungsfähigen und sehr teuren Leiterplattenprüf-anlage nur bedingt geprüft werden. Der Grund dafür ist, dass mit solchen Anlagen praktisch keine dynamische und nur eine beschränkte Anzahl statischer Prüfungen durchgeführt werden können. Ein IC, der auf der Leiterplatte gerade noch für die vorgesehene Anwendung funktioniert, kann trotzdem wichtige Spezifikationen nicht erfüllen und damit potentielle Frühhausfälle enthalten. Mit einer hundertprozentigen Eingangsprüfung werden hingegen alle defekten IC von Anfang an eliminiert. Dadurch können die Prüfungen auf Leiterplattenebene umfangmäßig und kostenmäßig reduziert werden. Man darf auch nicht vergessen, dass, ähnlich wie beim Prüfen von LSI/VLSI-IC, das Problem der Prüfung der Leiterplatten in der Erstellung und Wartung der Prüfprogramme liegt.

Die Endprüfung wird am fertigen Gerät durchgeführt. Geprüft werden die Parameter und die Funktionen auf Geräteebene. Für solche Prüfungen spielen dann die Aspekte der Instandhaltbarkeit und insbesondere der Prüfbarkeit und Zugänglichkeit eine wichtige Rolle. Diese Aspekte sind in der Entwicklungs- und Konstruktionsphase durch die Realisierung eines Instandhaltungskonzeptes zu berücksichtigen.

### 2.3 Abnahmeprüfung

Eine Abnahmeprüfung ist eine Prüfung, die in Anwesenheit des Kunden durchgeführt wird. Sie umfasst in der Regel eine reduzierte Endprüfung, kombiniert mit einer Zuverlässigkeit-, Sicherheits- und Instandhaltbarkeitsprüfung. Die erfolgreiche Abnahmeprüfung ist eine Voraussetzung für die offizielle Abnahme des Gerätes durch den Kunden.

### 2.4 Qualifikationsprüfungen

Eine Qualifikationsprüfung wird in der Regel als Teil eines Freigabeverfahrens durchgeführt. Dabei kann es sich um die Freigabe eines Bauteils, eines Moduls, einer Baugruppe oder sogar des Prototyps eines ganzen Gerätes handeln. Bei Prototypen komplexer Geräte muss die Qualifikationsprüfung gründlich und umfassend sein. Sie bezweckt die Überprüfung der Eignung des Prototyps für die vorgesehene Anwendung und soll enthalten:

1. Parameter- und Funktionsprüfung bei verschärften Beanspruchungen,

2. Umweltprüfungen,

3. Zuverlässigkeitssprüfungen,

4. Instandhaltbarkeitsprüfungen,

5. Sicherheitsprüfungen.

Bei den Parameter- und Funktionsprüfungen werden die spezifizierten und die extremen Werte aller relevanten Parameter gemessen und wenn möglich registriert (Stabilität der Parameter). Die Art der Umweltprüfungen, die durchgeführt werden müssen, hängt stark vom Gerät und vom vorgesehenen Einsatz ab. Übliche Umweltprüfungen für Geräte im Militärbereich sind: trockene Wärme, feuchte Wärme, Sonnenbestrahlung, Kälte, Zentrifuge, mechanische Schocks, Vibrationen, Regen, Salznebel, Schimmelwachstum, Sand, Unterdruck und elektromagnetische Verträglichkeit. Als Nachschlagewerke für die Prüfverfahren können die IEC 68, MIL-STD-810 und DIN 40046 für Geräte, die MIL-STD-883 für IC und die MIL-STD-202 für diskrete Bauteile verwendet werden. Die Schärfegrade sind selektiv zu wählen.

Die Hauptschritte bei der Freigabe elektronischer Bauteile sind:

1. Festlegung der vorgesehenen Anwendung, in bezug auf geforderte Funktion, Arbeitsbedingungen (intern/extern) und Auswirkung eines Ausfalls,

2. Qualifikation des Bauteils, insbesondere in bezug auf Verhalten unter normalen und verschärften Beanspruchungen sowie Stabilität der Parameter,

3. Qualifikation des Herstellers und des Lieferanten,

4. Betrachtungen über Kosten, Termine und Zweitlieferanten.

Bereits bei komplexen IC kostet eine Qualifikationsprüfung in der Regel mehr als 20000 Fr. Sie hat zudem wegen Masken- oder Prozessänderungen beim Hersteller nur eine beschränkte Gültigkeit. Es besteht deshalb ein grosses Interesse in der Aufteilung der Qualifikationskosten oder im Austausch von Resultaten über Qualifikationsprüfungen zwischen mehreren Anwendern, z.B. im Rahmen von Exact- oder Gidep-Berichten<sup>1)</sup>.

### 2.5 Zuverlässigkeitssprüfungen

Zuverlässigkeitssprüfungen sind notwendig, um die in der Praxis erreichte Zuverlässigkeit beurteilen zu können. Es wird grundsätzlich zwischen Ermittlung und Nachweis der Zuverlässigkeit unterschieden. Bei der Ermittlung wird eine Punkt- oder Intervallschätzung der «wahren» Zuverlässigkeit gesucht. Beim Nachweis sucht man eine Regel zur Prüfung von Hypothesen der Form: die Zuverlässigkeit  $R$  ist grösser als ein gegebener Wert  $R_0$ . Je früher man mit Zuverlässigkeitssprüfungen beginnt, desto schneller können Schwachstellen, die in den Zuverlässigkeitssanalysen nicht beachtet wurden, entdeckt und oft mit geringem Aufwand behoben werden. Dadurch entsteht ein Lernprozess, der zu einer gezielten Verbesserung der Zuverlässigkeit führt (reliability growth [10]). Zuverlässigkeitssprüfungen müssen wenn möglich zusammen mit Qualifikationsprüfungen durchgeführt werden. Die Prüfbedingungen sollen möglichst nahe den reellen Einsatzbedingungen gewählt werden. Als Beispiel sei die Ermittlung und der Nachweis einer MTBF<sup>2)</sup> näher beschrieben.

<sup>1)</sup> Exact: Exchange of Authenticated Electronic Component Performance Test Data. Gidep: Government-Industry Data Exchange Program (USA).

<sup>2)</sup> MTBF: Mean Time Between Failures.

Die MTBF ist der Erwartungswert (Mittelwert) der ausfallfreien Arbeitszeiten einer Betrachtungseinheit mit konstanter Ausfallrate  $\lambda = 1/\text{MTBF}$ . Für eine solche Betrachtungseinheit ist die Zuverlässigkeitssfunktion durch den Ausdruck  $R(t) = e^{-\lambda t}$  gegeben. Die Wahrscheinlichkeit  $Pr$ , dass in einer Zeitspanne  $T$  höchstens  $c$  Ausfälle eintreten, lässt sich berechnen aus

$$Pr \{ \text{Anzahl Ausfälle in } (0, T) \leq c \} = \sum_{i=0}^c \frac{(\lambda T)^i}{i!} e^{-\lambda T}$$

Es seien nun  $T$  die kumulative Betriebszeit und  $k$  die Anzahl Ausfälle während  $T$ . Die Punktschätzung für die MTBF ist gegeben durch

$$\hat{\text{MTBF}} = T/k$$

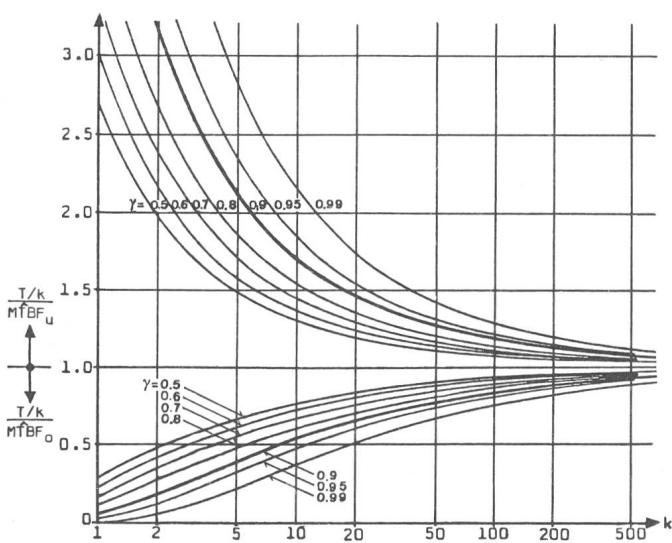

Für die Intervallschätzung liefert Fig. 3 die obere ( $\hat{\text{MTBF}}_u$ ) und die untere ( $\hat{\text{MTBF}}_u$ ) Vertrauensgrenze der MTBF mit einer Aussagewahrscheinlichkeit  $\gamma$  [7]. Der Nachweis einer MTBF stützt sich in der Regel auf folgende Abmachung zwischen Lieferant und Abnehmer: die Betrachtungseinheit soll mit einer Wahrscheinlichkeit  $\geq 1 - \alpha$  angenommen werden, falls die «wahre» MTBF grösser als der spezifizierte Wert  $\text{MTBF}_0$  ist, und sie soll mit einer Wahrscheinlichkeit  $\geq 1 - \beta$  zurückgewiesen werden, falls die «wahre» MTBF kleiner als der minimal akzeptierbare Wert  $\text{MTBF}_1$  ist. Die Bestimmung der Prüfzeit  $T$  (kumulative Betriebszeit) und der zugelassenen Anzahl Ausfälle  $c$  während  $T$  erfolgt mit Hilfe folgender Gleichungen:

$$\sum_{i=0}^c \frac{(T/\text{MTBF}_1)^i}{i!} e^{-T/\text{MTBF}_1} \approx \beta$$

$$\sum_{i=0}^c \frac{(T/\text{MTBF}_0)^i}{i!} e^{-T/\text{MTBF}_0} \approx 1 - \alpha$$

Die Kurven der Poisson-Verteilung erlauben eine graphische Lösung dieses Gleichungssystems.

Fig. 3 Vertrauensgrenzen  $\hat{\text{MTBF}}_u$  und  $\hat{\text{MTBF}}_l$  für eine unbekannte MTBF

$T$  kumulative Betriebszeit

$k$  Anzahl Ausfälle während  $T$

$\gamma$  Aussagewahrscheinlichkeit

Für  $k = 0$  setze  $\hat{\text{MTBF}}_0 = \infty$  und  $\hat{\text{MTBF}}_u = T/\ln[2/(1 - \gamma)]$ ;

die Aussagewahrscheinlichkeit ist in diesem Fall  $1 - (1 - \gamma)/2 = (1 + \gamma)/2$

Die genannte Prüfung wird zweiseitiger Einfach-Prüfplan genannt. Daneben werden oft auch der einseitige Einfach-Prüfplan (nur  $\alpha$  und  $\text{MTBF}_0$  oder  $\beta$  und  $\text{MTBF}_1$  sind gegeben) oder der Folge-Prüfplan (Sequentialtest) verwendet. Für den Nachweis der MTBF sind folgende Angaben wichtig:

1. Geforderte Funktion (ggf. Anforderungsprofil),

2. Arbeitsbedingungen,

3.  $\alpha$  und  $\text{MTBF}_0$  und/oder  $\beta$  und  $\text{MTBF}_1$ ,

4. Welche Parameter müssen während der Prüfung überwacht werden und für welche Abweichungen tritt ein Ausfall ein?

5. Klare Hinweise betreffend die Wartung und die Instandsetzung während der Prüfung,

6. Bestimmungen für den Fall eines negativen Prüfergebnisses.

Die Ausfallrate  $\lambda$  der elektronischen Bauteile liegt zwischen  $10^{-6}$  und  $10^{-9} \text{ h}^{-1}$ . Dies bedeutet, dass durchschnittlich ein Ausfall pro  $10^6$  bis  $10^9$  kumulierte Arbeitsstunden auftreten wird. Fig. 3 zeigt aber, dass für eine kleine Anzahl Ausfälle ( $k$ ) das Vertrauensintervall für  $\lambda = 1/\text{MTBF}$  sehr breit ist. Aus diesem Grunde werden oft zeitraffende Prüfungen durchgeführt. Die Extrapolation der Daten für normale Arbeitsbedingungen ist auch heute noch schwierig, weil die Ausfallmechanismen und die entsprechenden Aktivierungsenergien zuwenig bekannt sind.

## 2.6 Instandhaltbarkeitsprüfungen

Die Instandhaltung wird grundsätzlich in Wartung und Instandsetzung (Reparatur) eingeteilt. Dementsprechend werden auch die Prüfungen für die Wartbarkeit und Instandsetzbarkeit getrennt ausgewertet.

Bei den Wartbarkeitsprüfungen geht man davon aus, dass sich die Dauer einer Wartung aus folgenden Komponenten zusammensetzt:

1. Zeit für die Durchführung der Funktionsprüfung,

2. Zeit für die Arbeiten zur Verhinderung von Drift- oder Ver schleissausfällen,

3. Zeit für die Lokalisierung (Diagnostik) und Behebung allfälliger vorhandener verborgener Ausfälle,

4. Zeit für die Kalibration und Justierung,

5. Zeit, die durch die logistische Unterstützung oder andere Umstände, z.B. menschliche Einflüsse, bestimmt wird.

In ähnlicher Weise werden die Instandsetzungszeiten unterteilt in

1. Zeit für die Ausfalllokalisierung,

2. Zeit für die Ausfallbehebung,

3. Zeit für Justierungsarbeiten,

4. Zeit für die Funktionsprüfung,

5. Zeit, die durch die logistische Unterstützung oder andere Umstände, z.B. menschliche Einflüsse, bestimmt wird.

Für die Bestimmung oder den Nachweis der Wartbarkeit und insbesondere der Instandsetzbarkeit wird in der Regel eine repräsentative Anzahl relevanter Ausfälle simuliert und dann die notwendigen Reparaturzeiten aufgenommen und ausgewertet. Dabei werden definierte und gleichbleibende materielle (logistische) und personelle Bedingungen vorausgesetzt. Oft begnügt man sich mit der Bestimmung oder mit dem Nachweis des Mittelwertes der Reparaturzeiten (MTTR) oder der Wartungszeiten (MTTPM). In solchen Fällen muss man berücksichtigen, dass die Wartungs- und Instandsetzungszeiten nicht exponentiell, sondern oft nach einer lognormalen Verteilung verteilt sind. Typische Prüfpläne für die Instandsetzung sind in [11] aufgeführt. Diese Prüfpläne weichen prinzipiell von den Prüfplänen für die MTBF [12] ab.

Instandhaltbarkeitsprüfungen sollten schon auf Printplatten- oder Modulebene durchgeführt werden. Dies würde die Möglichkeit ergeben, den Mittelwert der Instandsetzungszeiten und der Wartungszeiten für ein höheres Integrationsniveau rechnerisch zu ermitteln.

Um eine gute Instandhaltbarkeit zu erreichen, muss man während der Entwicklungs- und Konstruktionsphase ein Instandhaltungskonzept aufstellen und konsequent auf allen Integrationsniveaus realisieren. Dazu gehören insbesondere die Aspekte der Ausfallerkennung und der Ausfalllokalisierung bis zum Niveau Ersatzteile, der ersatzteilkonformen Strukturierung des Gerätes und der Sicherstellung einer einfachen Zugänglichkeit und Prüfbarkeit.

### 3. Vorbehandlungen

Unter Vorbehandlung (screening) versteht man eine Folge von Beanspruchungen, denen ein Bauteil, ein Modul, eine Baugruppe usw. unterworfen wird, mit der Absicht, möglichst alle Frühhausfälle zu provozieren und den Wert der konstanten Ausfallrate ( $\lambda$ ) zu senken. Ohne geeignete Vorbehandlung

würden die meisten Frühhausfälle erst bei der Endprüfung oder während der Garantieperiode auftreten und hohe Reparaturkosten verursachen (Fig. 2). Im Hinblick auf eine Optimierung zwischen Wirksamkeit und Kosten muss die Vorbehandlung selektiv und gezielt auf den verschiedenen Integrationsniveaus durchgeführt werden.

Auf dem Niveau Bauteile müssen vor allem die IC, die Optoelemente und die diskreten Leistungsbauteile einer Vorbehandlung unterzogen werden. Solche Bauteile weisen oft zwischen 2 und 10% Frühhausfälle auf (Tabelle II). Für die Vorbehandlung der diskreten Bauteile kann man sich auf die MIL-STD-202 bzw. MIL-STD-750 und für die IC auf die MIL-STD-883 stützen. Eine Vorbehandlungssequenz, welche der Klasse B der MIL-STD-883B nahekommt, ist in Figur 4 angegeben. Die Klasse B entspricht den Anforderungen, die an die hochwertigen und zuverlässigen Industriegeräte gestellt werden, und verbessert gegenüber den ungeprüften IC die Ausfallrate ( $\lambda$ ) um einen Faktor 5 bis 10 [14]. Eine entsprechende Vorbehandlung (inkl. Prüfung) kostet etwa Fr. -50 bis Fr. 1.50 für SSI/MSI-IC und Fr. 2.- bis Fr. 4.- für LSI/

| ASE - CSEE<br>Rue de Vaudier 22<br>CH-2000 Neuchâtel<br>038 24 18 00 |                                                           | Protocole d'essai/Prüfprotokoll No. 465<br>(Fiche suivieuse/Laufkarte) |                                  | Centre Suisse d'Essais des Composants Electroniques                      |                                                     |

|----------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------|

| Client<br>Kunden No.                                                 | 18                                                        | Commande<br>Auftrag No.                                                | 934'220                          | Quantité<br>Anzahl                                                       | 3'000                                               |

| Composant<br>Komponente                                              | 8085A                                                     | Fabricant<br>Hersteller                                                | Intel                            | Date de fabrication<br>Herstellungsdatum                                 | 26                                                  |

| Remarques<br>Bemerkungen                                             | Portier plastique, essai sur Penky VIII                   |                                                                        |                                  |                                                                          | Date<br>Termin 3.8.81                               |

| No.                                                                  | Désignation de l'essai<br>Beschreibung der Prüfung        | Nombre de composants<br>Anzahl Komponenten                             |                                  | Date<br>Datum                                                            | Remarques<br>Bemerkungen                            |

| 01 X                                                                 | Contrôle visuel<br>Sichtkontrolle                         | 3'000                                                                  | Bon<br>Gut                       | CONT                                                                     | Visa<br>Visum                                       |

| 20                                                                   | Soudabilité (échantillon)<br>Lötbarkeit (Stichprobe)      |                                                                        |                                  | FCT                                                                      |                                                     |

| 10 X                                                                 | Essai électrique réduit<br>Red. elektrische Prüfung       | 25°C                                                                   |                                  | DCT                                                                      | Load Board 314<br>Programme 0 ASA (Reter 31)        |

| 02 X                                                                 | Stockage à haute température<br>Hochtemperaturlagerung    | 24 h, 125 °C, N <sub>2</sub> □                                         |                                  |                                                                          |                                                     |

| 03 X                                                                 | Cycles thermiques<br>Thermische Zyklen                    | 10 cycles, -40 °C + 125 °C                                             |                                  |                                                                          |                                                     |

| 05                                                                   | Accélération const.<br>Konst. Beschleunigung              | g                                                                      |                                  |                                                                          |                                                     |

| 06                                                                   | Etanchéité (Fine Leak)                                    | Atm cm <sup>3</sup> /s                                                 |                                  |                                                                          |                                                     |

| 07                                                                   | Etanchéité (Gross Leak)                                   | Atm cm <sup>3</sup> /s                                                 |                                  |                                                                          |                                                     |

| 10 X                                                                 | Essai électrique réduit<br>Red. elektrische Prüfung       | 25°C                                                                   |                                  | CONT<br>FCT<br>DCT                                                       | Load Board 314<br>Programme 0 ASA (Reter 31)        |

| 08 X                                                                 | Burn-in<br>48 h, 125 °C, N <sub>2</sub> □<br>dyn. stat. □ |                                                                        |                                  |                                                                          | Oven Criteria IV<br>Board 60863<br>Driver 818 8085A |

| 20                                                                   | Soudabilité (échantillon)<br>Lötbarkeit (Stichprobe)      |                                                                        |                                  |                                                                          |                                                     |

| 11 X                                                                 | Essai électrique à<br>Elektrische Prüfung bei             | 70 °C                                                                  |                                  | CONT<br>FCT<br>DCT                                                       | Load Board 314<br>Programme 0 ASA                   |

| 30 X                                                                 | Marquage<br>Markierung                                    |                                                                        | Encre/Tinte<br>jaune □<br>bleu □ | Collant/Kleber<br>VIS (orange)<br>CONT (brun)<br>FCT (rot)<br>DCT (grün) |                                                     |

Conditions générales contractuelles au verso / Allgemeine Vertragsbestimmungen auf der Rückseite

Fig. 4

Prüfprotokoll/Laufkarte des CSEE,

wie sie vor Beginn einer Prüfung vorliegt

Typische Anzahl Frühausfälle nach einer Vorbehandlung

gemäss MIL-STD-883/Klasse B [13]

Tabelle II

| Familie | Komplexität | % Frühausfälle |

|---------|-------------|----------------|

| TTL     | SSI/MSI     | 1,3            |

|         | LSI         | 3,7            |

| ECL     | SSI/MSI     | 2,4            |

|         | LSI         | 2,5            |

| CMOS    | SSI/MSI     | 6,2            |

|         | LSI         | 3,2            |

| NMOS    | LSI         | 3,1            |

| lineare | -           | 4,5            |

VLSI-IC. Eine grundsätzliche Frage ist, ob man sie beim Hersteller, intern oder in einem externen Prüfzentrum durchführen lässt. Für kleine bis mittelgroße Unternehmen lautet die Antwort eindeutig zugunsten eines externen Prüfzentrums, und zwar aus folgenden Gründen:

1. Die Investitionskosten für die Prüfeinrichtungen (ohne die elektrischen Prüfungen) liegen zwischen 0,5 und 1,5 Mio Fr.

2. Beim Hersteller hat man keinen direkten Zugang zu den Vorbehandlungs- und Prüfverfahren. Damit können diese Verfahren die vorgesehene Anwendung der IC nicht berücksichtigen.

3. Bei einem externen Prüfzentrum liegen die Kosten und Termine oft günstiger. Darüber hinaus kann man die Vorbehandlung (insbesondere das Burn-in) und die elektrische Prüfung am Schluss (die als Eingangsprüfung zu betrachten ist) der vorgesehenen IC-Anwendung anpassen.

Auf dem Niveau Leiterplatten hat sich folgendes Vorbehandlungsverfahren herauskristallisiert [15]:

1. Visuelle Kontrolle und grobe elektrische Prüfung.

2. Thermische Zyklen; typisch: 10 Zyklen zwischen  $-40^{\circ}$  und  $+80^{\circ}$  C mit 2...10 °C/min und Anhaltszeit kleiner als 10 min; die Speisung soll während der Heizung eingeschaltet und während der Kühlung ausgeschaltet werden.

3. Vibrationen (falls die Einsatzbedingungen dies erfordern); typisch: random, 5 bis 30 Zyklen von 15 min bei 1...6 g.

4. Einbrennung (debugging); typisch: 60 Zyklen von 15 min mit periodischem Ein- und Ausschalten.

5. Gezielte elektrische Prüfung.

Dieses Verfahren ist für hochwertige und zuverlässige Industriegeräte anzuwenden und setzt voraus, dass auf Bauteilebene die nötigen Vorbehandlungen und Prüfungen schon vorgenommen worden sind. Auch für die Prüfung und Vorbehandlung von Leiterplatten besteht ein Interesse für eine Gruppierung der kleinen und mittelgroßen Unternehmen.

Auf höherem Integrationsniveau werden die Vibrationen nur in Spezialfällen durchgeführt. Anstelle der thermischen Zyklen wird oft eine Hochtemperaturlagerung von 100 bis 300 h vorgenommen.

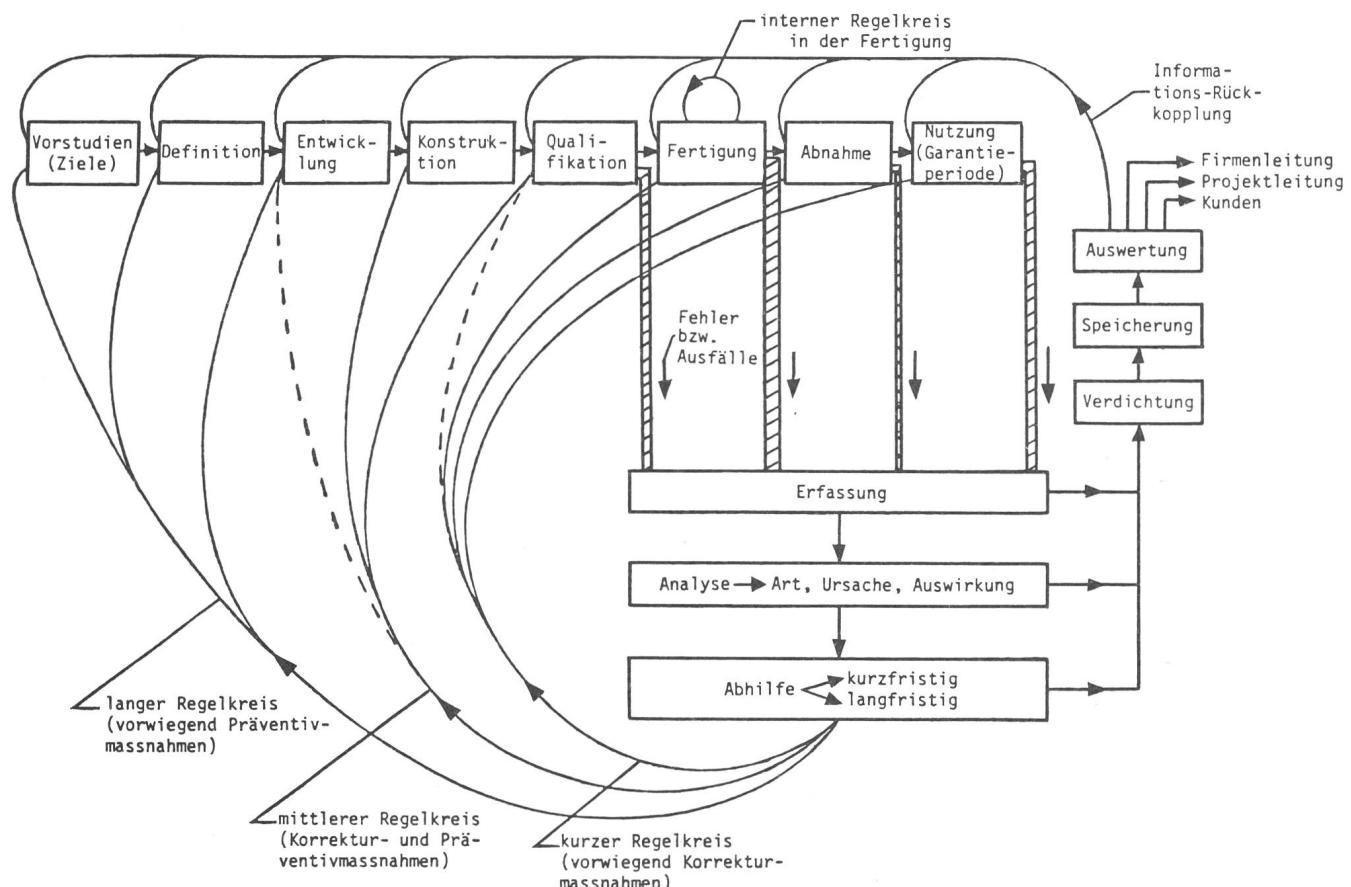

#### 4. Qualitätsdatensystem

Das Qualitätsdatensystem ist ein wichtiges Hilfsmittel zur raschen und wirksamen Erfassung und Korrektur aller Nicht-übereinstimmungen (Fehler und Ausfälle), die während den Prüfungen oder Vorbehandlungen festgestellt werden. Seine Hauptziele sind:

1. Rechtzeitige Erfassung aller Nichtübereinstimmungen (Fehler und Ausfälle).

2. Unverzügliche Bestimmung der Ursachen und koordinierte Durchführung der notwendigen Korrekturmassnahmen, nicht nur

Fig. 5 Prinzip des Qualitätsdatensystems

zur Behebung, sondern wenn möglich auch zur Vermeidung des Wiederauftretens des gleichen Fehlers oder Ausfalles.

3. Speicherung, Verdichtung, Auswertung und Verteilung von Informationen und Daten, die als Entscheidungsgrundlagen für die Erfreigung von Präventivmassnahmen dienen sollen.

4. Erfassung und Optimierung der Folgekosten (Reparatur, Nacharbeit, Garantie usw.).

Das Qualitätsdatensystem wird von der Erprobung des Prototyps (Qualifikationsprüfung) bis zum Ende der Garantieperiode eingesetzt, siehe Fig. 5 [2]. Wenn möglich, sollte es aber auch während der Nutzungsphase wirksam bleiben, denn in dieser Phase fallen die wichtigsten Zuverlässigkeitss- und Instandhaltbarkeitsdaten an. Bei Grossprojekten sollte das Qualitätsdatensystem computerunterstützt ausgelegt werden.

## Literatur

- [1] *J. M. Juran, F. M. Gryna and R. S. Bingham*: Quality control handbook. Third edition, New York, McGraw-Hill, 1974.

- [2a] *A. Birolini*: Zusammenhang zwischen Qualitätssicherung und Zuverlässigkeit. In: Informationstagung: Qualitätskontrolle und Zuverlässigkeit, 21. September 1978, Fribourg, Zürich, SEV, 1978, S. 1...22.

- [2b] *A. Birolini*: Qualitäts- und Zuverlässigkeitssicherung komplexer Systeme. Teil 1 und 2. Bull. SEV/VSE 70(1979)3, S. 142...148 + Nr. 5, S. 237...243.

- [3] *M. L. Shooman*: Probabilistic reliability: An engineering approach. New York, McGraw-Hill, 1968.

- [4] *P. Bitter u.a.*: Technische Zuverlässigkeit. Problematik, mathematische Grundlagen, Untersuchungsmethoden, Anwendungen. 2. Auflage, Berlin u.a., Springer-Verlag, 1977.

- [5] *R. T. Anderson*: Reliability design handbook. RDH-376. New York, Reliability Analysis Center/Griffiss Air Force Base, 1976.

- [6] Development guide for reliability. Part 1 to 6. AMC Pamphlet 706-195...706-200. Alexandria/Va, Headquarters, US Army Material Command, 1975/1976.

- [7a] *A. Birolini*: Zuverlässigkeit von Schaltungen und Systemen. Autographie zur Vorlesung an der ETH Zürich. 3. Auflage, Zürich, Selbstverlag, 1978.

- [7b] *A. Birolini*: Zuverlässigkeitstechnik. Autographie zum Fortbildungskurs an der Universität Neuchâtel. Zürich, Selbstverlag, 1979.

- [8] *E. R. Goodridge*: Independent test houses, Circuits Manufacturing 20(1980)12, p. 28...32.

- [9] Prüfinstitute testen alles. Markt und Technik -(1981)7, S. 81.

- [10a] *P. H. Mead*: Reliability growth of electronic equipment. Microelectronics and Reliability 14(1975)-, S. 439...443.

- [10b] *D. M. Keith*: A report on a survey of the specification and attainment of reliability in communications equipment. Proceedings of the IEEE Reliability and Maintainability Symposium (1975), p. 579...593.

- [10c] *T. Jayachandran*: A Comparison of reliability growth models. IEEE Trans. Reliability 25(1976)I, S. 49...52.

- [10d] *G. Gironi* a.o.: A burn-in program for wear out unaffected equipments. Microelectronics and Reliability 15(1976)-, p. 227...232.

- [10e] *A. J. Bonis*: Reliability growth curves for one shot devices. Proceeding of the IEEE Reliability and Maintainability Symposium (1977), p. 181...185.

- [10f] *K. W. Fertig and V. K. Murthy*: Models for reliability growth during burn-in: Theory and applications. Proceedings of the IEEE Reliability and Maintainability Symposium (1978), p. 504...509.

- [10g] *L. A. Weaver* a.o.: Comparison of burn-in and life test growth models. Transactions of the Technical Conference of the American Society of Quality Control, Chicago (1978), p. 53...57.

- [11] Maintainability demonstration. MILStandard 471.

- [12] Reliability design qualification and production acceptance tests: Exponential distribution. MIL-Standard 781.

- [13] Microcircuit screening effectiveness. TRS-1. New York, Reliability Analysis Center/Griffiss Air Force Base, 1978.

- [14] Reliability prediction of electronic equipment. MIL Handbook 217c.

- [15] *R. E. Schafer* a.o.: Electronic equipment screening and debugging techniques. ADA 053561. National Technical Information Service, U.S. Department of Commerce, Springfield/VA, 1978.

## Adresse des Autors

Dr. *A. Birolini*, ASE-CSEE (Association Suisse des Electriciens – Centre Suisse d'Essais des Composants Electroniques), ruelle Vaucher 22, 2000 Neuchâtel.