|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 72 (1981)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 7                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | CEH et FSRM : fabrication en petite série de circuits intégrés CMOS                                                                                                                                                       |

| <b>Autor:</b>       | Gerber, B. / Forrer, M.                                                                                                                                                                                                   |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-905091">https://doi.org/10.5169/seals-905091</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 26.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

## CEH et FSRM : Fabrication en petite série de circuits intégrés CMOS

Par B. Gerber et M. Forrer

### 1. Introduction

Le Centre Electronique Horloger (CEH) établira en 1981 en collaboration avec la Fondation Suisse pour la Recherche en Microtechnique (FSRM), une ligne de fabrication pour l'intégration en petites séries (5000 à 20000 par an) de circuits intégrés à transistors MOS complémentaires. Une telle activité permettra de faire face à un besoin de plus en plus important qui se manifeste non seulement dans le domaine horloger mais également dans les autres domaines de la microélectronique.

La force de l'industrie suisse reste, à l'heure actuelle, le produit spécialisé de pointe et de haute qualité. Cela exige au sein des entreprises une activité créatrice, imaginative et dynamique, activité que l'on retrouve dans un laboratoire de recherche tel que le CEH. Le lien étroit qu'aura la ligne de fabrication avec les départements des recherches et développements sera un élément essentiel pour l'application rapide de nouvelles idées. Ce sont surtout les moyennes et petites entreprises, qui ne peuvent pas se doter d'une compétence microélectronique en plus de leur spécialité particulière, qui devraient y trouver un intérêt vital. La ligne de fabrication sera épaulée par un département de développement offrant une possibilité de consultation ou de mandats de conception de circuits afin de résoudre les problèmes particuliers des clients avec un maximum de flexibilité.

Malgré la présence de circuits «semi-custom», une fabrication de circuits en petites séries garde toute son actualité. En effet, l'utilisation de petits circuits logiques et analogiques optimisés en performance (vitesse et consommation) ou de circuits à grande échelle (VLSI) reste du domaine de la conception à la base. Il est évident qu'un circuit intégré spécialisé aura un prix plus élevé qu'un circuit standard fabriqué en grande série. Il couvrira cependant les besoins spécifiques du client. La technologie CMOS silicon gate répond à ces besoins.

### 2. La technologie CMOS silicon gate

La technologie CMOS silicon gate permet l'intégration de transistors MOS complémentaires, c'est-à-dire à canal p et n sur une même plaque de silicium. Elle utilise une couche en silicium polycristallin pour former les grilles des transistors contrairement à la technologie metal gate utilisant des grilles en aluminium. Son avantage principal est la possibilité de réaliser des transistors à très faible tension de seuil ( $V_T \approx 0,5$  V), plus performants grâce à leur structure auto-alignée et qui peuvent être reliés entre eux à l'aide d'un niveau d'interconnexions supplémentaires facilitant la topologie de circuits complexes. La technologie CMOS silicon gate, pratiquée au CEH depuis dix ans, nécessite huit étapes de masquage photolithographique si l'on inclut une couche de passivation pour protéger les circuits.

<sup>1)</sup> Les articles qui suivent correspondent à des exposés présentés lors de la journée d'information de même nom organisée par le Solid State Devices & Circuits Chapter (IEEE Switzerland Section), le 23 octobre 1980 à Berne et soutenue également par l'ASE (p. 326 à 338).

621.38(494);

La technologie CMOS est caractérisée par une très faible consommation de puissance (proportionnelle à la fréquence de fonctionnement du circuit) et une grande immunité au bruit. Le CEH est connu pour ses réalisations de circuits horlogers alimentés à 1,5 V, fonctionnant à des fréquences de plusieurs MHz et ne consommant que quelques  $\mu$ A. Des circuits basses fréquences (32 kHz) peuvent avoir des consommations inférieures à 0,2  $\mu$ A.

La technologie CMOS est donc particulièrement bien adaptée aux applications exigeant une très faible consommation, par exemple pour des instruments fonctionnant sur pile, des applications bio-médicales, des circuits de surveillance et de télécommunication.

Toutefois, il faut tenir compte de certaines limitations quant à la tension d'alimentation: Une technologie optimisée pour des tensions d'alimentation de 1,5 V ne fonctionnera plus au-delà de 5 V. Ceci est dû à l'apparition de transistors «parasites» qui court-circuitent les éléments entre eux. De plus, en alimentant un circuit pouvant fonctionner à 1,5 V sous une tension d'alimentation de 5 V, on augmentera sa consommation d'un facteur 10.

Afin de satisfaire un plus grand nombre d'utilisateurs potentiels, le CEH mettra à disposition une technologie 1,5 V et une technologie 5 V, le choix à faire dépendant des applications envisagées.

### 3. Éléments disponibles

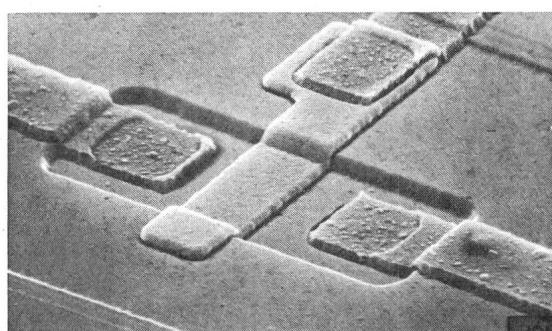

La figure 1 montre une microphotographie d'un transistor typique (p ou n-ch) utilisé dans les circuits logiques. En régime de saturation et pour une tension d'alimentation de 1,5 V, un transistor à canal n conduira un courant de l'ordre de 30  $\mu$ A. En réduisant la tension appliquée sur la grille jusqu'à l'obtention d'un courant de 10 à 100 nA, le transistor entre alors dans le régime de faible inversion où il se comporte de manière comparable à un transistor bipolaire. Cette propriété trouve de nombreuses applications dans la réalisation de circuits analogiques.

Une limitation de la technologie CMOS basse tension (1,5 V) se présente lorsque des courants élevés (quelques mA)

Fig. 1 Microphotographie d'un transistor MOS

doivent être délivrés. Cette condition conduit à des transistors en forme de serpentin dont la largeur de canal peut dépasser plusieurs mm. Une réduction possible de la surface consiste à alimenter la grille du transistor à tension plus élevée, tension qui peut être générée par un multiplicateur de tension intégré.

Si l'on désire réaliser des circuits analogiques, la possibilité de pouvoir disposer de résistances et de capacités devient très importante. Contrairement à la technologie à grille métallique, la technologie silicon gate ne possède pas de capacités de valeur élevée ( $300$  à  $500$  pF/mm $^2$ ) qui sont indépendantes de la tension. Grâce aux deux niveaux d'interconnexions (aluminium et silicium polycristallin), il est possible de réaliser des capacités indépendantes de la tension et en plus totalement flottantes ayant des valeurs de l'ordre de  $100$  pF/mm $^2$ .

Des résistances de quelques k $\Omega$  peuvent être obtenues en utilisant la diffusion p- du caisson. Mais pour la plupart des applications, elles sont souvent beaucoup trop faibles. Pour remédier à cet inconvénient, le CEH contrôle et utilise les courants de fuites des jonctions latérales qui se forment dans le silicium polycristallin à l'intersection des dopages p+ et n+, ce qui permet de réaliser des résistances de haute valeur (entre  $1$  et  $100$  G $\Omega$ ) sans augmenter la complexité du procédé de fabrication. Ces diodes trouvent également une application très importante dans la réalisation de multiplicateurs de tension intégrés.

#### 4. Circuits réalisables

Depuis le développement de la technologie silicon gate, le CEH s'est toujours efforcé de tirer le parti maximum des éléments à disposition pour réaliser des circuits logiques et analogiques.

La combinaison de portes logiques élémentaires permet la réalisation de circuits diviseurs de fréquence statiques. Les performances de ces diviseurs peuvent être améliorées en réalisant des circuits diviseurs dynamiques qui atteignent les performances suivantes: fréquence maximale  $5$  MHz; consommation  $0,4$   $\mu$ A/MHz à  $V_{ce} = -1,5$  V.

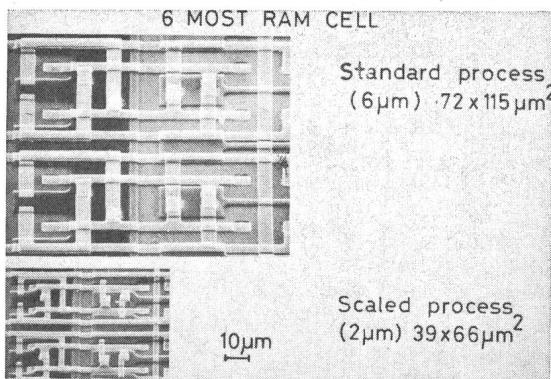

A l'heure actuelle, on observe que le nombre de fonctions demandées à un circuit digital est de plus en plus élevé. Ceci conduit à des circuits intégrés à grande échelle structurés en architecture de micro-ordinateurs. Par exemple, la seconde génération des processeurs comporte une mémoire RAM (Random-Access Memory) pour le stockage des données et une mémoire morte ROM (Read-Only Memory) pour le stockage du programme. Ce dernier est constitué par une séquence d'instructions exécutée par le microprocesseur. Seule la technologie CMOS permet de réaliser de tels circuits ayant une consommation de puissance inférieure à  $10$   $\mu$ W. Aujourd'hui, on peut estimer que  $10$  kbits de mémoire ROM occupent une surface de  $10$  mm $^2$  avec une consommation totale de  $1$   $\mu$ A à une fréquence de lecture de  $1$  kHz. Les mémoires RAM statiques, quant à elles, utilisent des cellules CMOS à  $6$  transistors.  $1$  kbit de mémoire utilise  $10$  mm $^2$ , la consommation de courant étant de  $1$   $\mu$ A pour un taux de lecture et d'écriture de  $5$  mots/s.

Les nouvelles générations de circuits intégrés analogiques comportent de plus en plus de circuits dans lesquels le CEH jouit d'une grande compétence notamment dans les circuits à micropuissance. L'un des premiers circuits analogiques développés dans le cadre des applications horlogères fut l'oscillateur à quartz. L'application judicieuse des éléments décrits

Fig. 2 Mémoire RAM à 6 transistors en technologie standard et MiniMOS

tels que les capacités flottantes, les diodes réalisées dans le silicium polycristallin, l'utilisation de transistors dans le régime de faible inversion, a permis de réaliser un circuit oscillateur  $32$  kHz qui ne consomme que  $0,05$   $\mu$ A.

Un autre exemple est un circuit de référence de tension basé sur une paire de transistors de même type mais dont les grilles sont dopées de type inverse. Il permet d'obtenir des tensions stabilisées ayant une dérive thermique de seulement  $\pm 1$  mV entre  $-20$  °C et  $+80$  °C avec une consommation totale de courant inférieure à  $0,1$   $\mu$ A.

Comme autre exemple réalisé, citons les filtres à capacité commutée, les amplificateurs opérationnels ainsi que les amplificateurs à faible bruit qui sont utilisés pour traiter des signaux analogiques délivrés par des senseurs.

Dans le domaine des hautes fréquences, le CEH a développé un circuit horloger de  $4,2$  MHz ne consommant que  $2$   $\mu$ A.

#### 5. Technologies en développement

Deux technologies sont actuellement en développement au CEH.

Tout en conservant l'acquis de la technologie conventionnelle, la *technologie double poly* offre, au prix d'un masque supplémentaire, un certain nombre d'éléments nouveaux: transistors à oxyde de grille d'épaisseurs différentes, structures de type tétrode, ainsi que des capacités flottantes de valeur élevée indépendantes de la tension. Elle permet en outre de réaliser des mémoires non volatiles reprogrammables électriquement à partir de  $1,5$  V. Les tensions élevées nécessaires à leur programmation sont générées à l'aide de multiplicateurs de tensions complètement intégrés. Une mémoire de  $16 \times 4$  bits a déjà été réalisée. L'effacement global demande  $250$  ms alors que l'inscription s'effectue en  $50$  ms par bit. Le nombre de cycles de programmation est de l'ordre de  $10^4$ . La rétention de l'information est supérieure à  $10$  ans à  $60$  °C.

Le but fixé à la *technologie MiniMOS* est la réalisation de transistors de très faibles dimensions (géométries minimales de  $2$   $\mu$ m). De nouveaux procédés de gravure (dry etching processes) et la modélisation mathématique de ces structures sont étudiés conjointement avec l'EPFL. La figure 2 illustre le gain en surface obtenu sur une cellule de mémoire RAM à  $6$  transistors.

#### 6. Organisation de la ligne de fabrication

La ligne de fabrication sera une unité distincte. Le service d'intégration actuel du CEH formera son noyau. Il bénéficiera des équipements microélectroniques qui sont au service de la

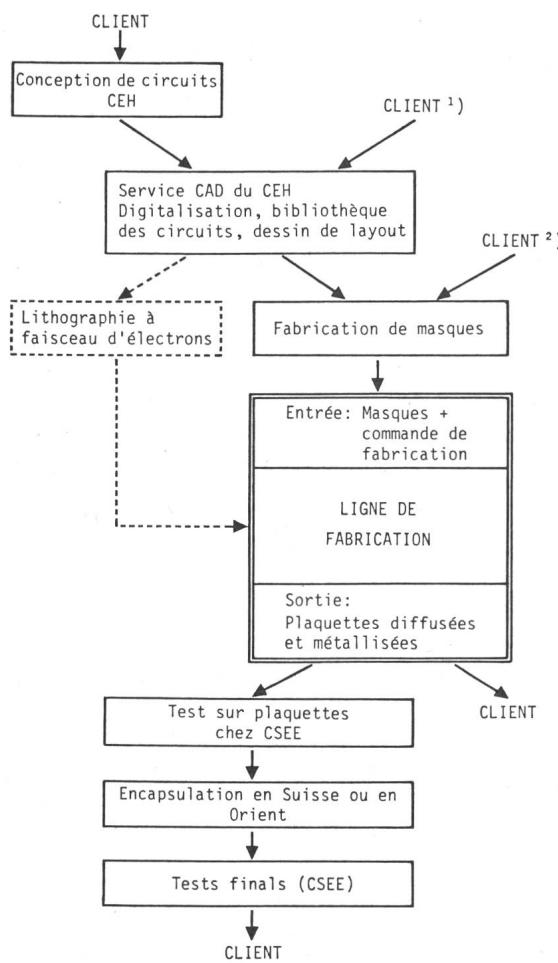

**Fig. 3 Possibilités d'accès à la ligne de fabrication**

Client<sup>1)</sup>: industrie, haute école disposant de sa propre conception de circuits

Client<sup>2)</sup>: industrie, haute école disposant de sa propre conception de circuits *et* des moyens de dessins (CAD) des layouts

CAD Computer aided design

CSEE Centre Suisse d'Essais des Composants Electroniques de l'ASE

recherche. Le CEH assurera la gestion technique de la ligne de fabrication.

La figure 3 indique les possibilités d'accès à la ligne de fabrication à différents niveaux, selon les possibilités des clients.

Etant donné que le centre d'évaluation et de contrôle des composants électroniques de l'ASE (CSEE) s'installe actuellement à Neuchâtel avec un équipement puissant, nous suggérons d'utiliser ses services pour les tests sur plaquette ainsi que pour les tests finals.

Une activité d'encapsulation n'est pas prévue actuellement. Il est coutume de faire faire des encapsulations en Extrême-Orient (prix: 40 ct. par circuit). Certains fabricants suisses offrent également un service d'encapsulation, mais à un prix sensiblement plus élevé.

Le temps de conception, soit l'établissement d'un schéma et le dessin des plans de masques, dépendra fortement de la complexité du circuit à réaliser. Grâce à l'utilisation de circuits standards mis en bibliothèque, les temps de digitalisation et les coûts de développement devraient pouvoir être minimisés. Les estimations pour les autres phases de la fabrication sont les suivantes: 2 à 6 semaines pour la digitalisation, 2 à 4 semaines pour la fabrication des masques et environ 3 semaines pour la fabrication proprement dite d'une série de 24 plalettes de 3 pouces de diamètre.

Une capacité de production annuelle de 1000 plalettes pour clients externes est prévue pour 1981. Elle pourra être augmentée par la suite selon besoins. Le prix d'une plaquette est estimé à fr. 600.-. L'évolution des prix dépendra de multiples paramètres (investissements, nombre de plalettes fabriquées, etc.).

Le prix d'un circuit dépendra directement de sa surface et de son rendement de fabrication qui lui-même sera fonction des particularités du circuit (circuit entièrement logique, purement analogique, etc.). Pour fixer les idées, un circuit de 16 mm<sup>2</sup> avec un rendement de 20 % coûtera environ fr. 15.-. A ce prix, il convient d'ajouter le coût des tests et de l'encapsulation.

#### Adresse des auteurs

Dr M. Forrer et B. Gerber, Centre Electronique Horloger S.A., Maladière 71, 2000 Neuchâtel 7.