**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 70 (1979)

**Heft:** 21

**Artikel:** Das Zentrum des SEV für die Evaluation und Kontrolle elektronischer

Komponenten: Aufgaben und Aufbau

**Autor:** Birolini, A.

**DOI:** https://doi.org/10.5169/seals-905440

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

# **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

# Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 01.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Das Zentrum des SEV für die Evaluation und Kontrolle elektronischer Komponenten – Aufgaben und Aufbau

Von A. Birolini

621.38:658.56

Ausgehend von der raschen Entwicklung und Verbreitung der integrierten Schaltungen werden eingangs die Probleme dargelegt, denen sich heute viele Hersteller elektronischer Module oder Geräte gegenübergestellt sehen. Insbesondere werden die Aspekte der Qualifikation, der Prüfung und der Vorbehandlung von hochintegrierten Schaltungen besprochen. Die Lösung dieser Probleme im Rahmen des Impulsprogrammes des Bundesamtes für Konjunkturfragen wird dann vorgestellt. Auf die Aufgaben und auf den vorgesehenen Aufbau des Zentrums für die Evaluation und Kontrolle elektronischer Komponenten (CECCE) in Neuenburg wird speziell eingegangen.

En partant du développement et de la diffusion très rapide des circuits intégrés, on expose tout d'abord les problèmes qui en resultent pour un grand nombre de fabricants de modules ou d'équipements électroniques. Il s'agit surtout des aspects de la qualification, du contrôle et du déverminage des composants électroniques à haut degré d'intégration. La solution de ces problèmes dans le cadre du programme d'impulsion de l'Office fédéral pour les Questions Conjoncturelles, est ensuite présentée. En particulier on décrit les tâches et le programme de création du Centre d'Evaluation et de Contrôle des Composants Electroniques (CECCE) de Neuchâtel.

#### 1. Einleitung

Es gibt kaum einen andern Zweig der Technik, der sich so rasch wie die Elektronik entwickelt und durchgesetzt hat. Elektronische Komponenten werden in der Schweiz jährlich zu Hunderttausenden in der Steuer-, Überwachungs-, Übermittlungs-, Computer- und Unterhaltungstechnik verwendet. Viele dieser Komponenten können praktisch problemlos eingesetzt werden. Andere, wie die integrierten Schaltungen (IC) sind derart komplex geworden, dass sie einer umfassenden Prüfung und Vorbehandlung unterzogen werden müssen, um die Prüfkosten in der Fertigungsphase und die Zahl der Frühausfälle ganzer Baugruppen und Apparate kleinzuhalten.

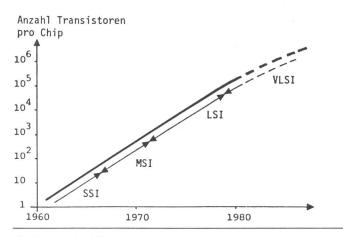

Die rasche Entwicklung der IC ist der Planartechnik (1959) zu verdanken. Durch diese Technik wurde es möglich, eine grosse Anzahl von Transistoren gleichzeitig auf einem einzigen Silizium-Substrat wirtschaftlich herzustellen (batch-processing). Ein Rückblick auf die letzten fünfzehn Jahre zeigt, dass sich die Anzahl der Transistoren pro Chip jedes Jahr annäherungsweise verdoppelt hat (Fig. 1). Zu dieser Steigerung haben vor allem die Verkleinerung der Abmessungen der einzelnen Transistoren auf dem Chip (von 50...100 µm im Jahre 1960 auf 2...4 µm im Jahre 1979), die Vergrösserung der Chipfläche (von 3...6 mm<sup>2</sup> im Jahre 1960 auf 20...40 mm<sup>2</sup> im Jahre 1979) und die Entwicklung integrationsgerechter Schaltungsstrukturen, insbesondere für die Speicherzellen, beigetragen [2; 3; 4]. Wie in Fig. 1 angedeutet, ist jedoch aus verschiedenen Gründen in den achtziger Jahren eine Sättigung vorauszusehen [4; 5]. Wahrscheinlich wird die Schwelle der 106 Transistoren pro Chip nur noch von den Speichern und von anwendungsorientierten Schaltungen überschritten werden [4; 5; 6]. Die Abgrenzung zwischen SSI, MSI, LSI und VLSI ist nicht genau definiert; sie bezieht sich oft auch auf die Anzahl der Tore pro Chip oder auf die Abmessungen der einzelnen Transistoren (Linienbreite).

Zusammen mit der Anzahl Transistoren pro Chip ist auch die Komplexität der IC stark angestiegen. 64-kbit-Speicher und 16-bit-Mikroprozessoren werden schon heute kommerziell angeboten. Grössere Speicher sind angekündigt und Mikroprozessoren mit 32 bit werden entwickelt [7; 8; 9]. Es ist zu erwarten, dass auch die Anzahl der externen Verbindungen über die heute erreichten 64 Pin steigen wird [4; 10].

Die wachsende Komplexität der IC sowie die grosse Vielfalt des Angebotes und der Anwendungsmöglichkeiten solcher

Dieser Aufsatz ist eine überarbeitete Fassung des Vortrages anlässlich der SEV-Generalversammlung vom 1. September 1979.

Komponenten stellen viele Anwender vor komplexe Probleme. Betroffen sind vor allem die kleineren und mittleren Unternehmen, welche – von anderen Techniken herkommend – in das für sie neue Gebiet der modernen Elektronik einsteigen müssen. Neben den Aspekten der Kosten, der Liefertermine, der Wahl und des Einsatzes der IC sowie der Prüfung von bestückten Printplatten von Modulen oder von Geräten, stellen sich bezüglich der angelieferten IC auch prinzipielle Qualitätsund Zuverlässigkeitsfragen. Zu diesen gehören insbesondere die anwendungsspezifische *Qualifikation*, die *Prüfung* und die *Vorbehandlung* der IC.

# 2. Qualifikation, Prüfung und Vorbehandlung integrierter Schaltungen

#### 2.1 Qualifikation

Die Qualifikation dient dazu, die Eignung eines gegebenen IC für eine bestimmte Anwendung festzustellen. Sie besteht in der Regel in einer Folge von Prüfungen, die nach einem definierten Verfahren durchgeführt werden Dazu gehören:

- Umweltprüfungen, z.B. Verhalten bei Lagerung auf hoher Temperatur, bei Temperaturzyklen und bei Temperaturschocks; Messung der Dichtigkeit, der Widerstandsfähigkeit in korrosiver Umgebung usw.

- Mechanische Prüfungen, z.B. Verhalten bei Beschleunigung, Vibration und Schocks; Messung der Festigkeit der Verbindungen, der Lötbarkeit usw.

- Elektrische Prüfungen, z.B. Messung von Speisestrom, Reststrom, logischer Niveaus, Störabstand, Schaltzeiten usw. für digitale

Fig. 1 Komplexitätszunahme der integrierten Schaltungen SSI, MSI, LSI, VSLI: small, medium, large, very large scale integration

Kostenvergleich zwischen einer 100%igen Eingangsprüfung und einer Stichprobenprüfung unter Berücksichtigung der Kosten für den Ersatz der defekten IC auf den bestückten Printplatten Tabelle I

| angelieferte IC                                                          | 1000  |

|--------------------------------------------------------------------------|-------|

| defekte IC (im Mittel)                                                   | 20    |

| bestückte Printplatten                                                   | 40    |

| Printplatten mit mindestens<br>einem defekten IC (im Mittel)             | 16    |

| Kosten für eine 100 %ige Eingangsprüfung Fr.                             | 100   |

| Kosten für eine Stichprobenprüfung (Stichprobeumfang n = 80) Fr.         | 8.–   |

| Kosten für die Reparatur der defekten Printplatten (im Mittel 16×30) Fr. | 480.– |

IC; ferner von Offset, Bias, Frequenzgang, Slew Rate, Rauschfaktor usw. für analoge IC.

- Zuverlässigkeitsprüfungen, wie Langzeitverhalten (Driftmessung), Lebensdauermessung (unter normalen oder erschwerten Bedingungen) und Ausfallanalysen.

Umfang und Tiefe einer Qualifikationsprüfung wird durch die vorgesehene Anwendung bestimmt. Neben den Leistungsparametern und den Umweltbedingungen sollte auch die Auswirkung eines Ausfalles des betrachteten IC auf die Zuverlässigkeit und auf die Sicherheit des ganzen Gerätes berücksichtigt werden (criticality). Aus Gründen der Standardisierung wird die Qualifikation oft für eine ganze Klasse von Anwendungen durchgeführt [11; 12]. Einschränkend ist festzuhalten, dass eine Qualifikation in der Regel nur für einen bestimmten Hersteller und für begrenzte Zeit Gültigkeit hat.

# 2.2 Eingangsprüfung

Mit der Eingangsprüfung wird festgestellt, ob ein angelieferter IC fehlerfrei ist. Dadurch wird vermieden, dass defekte IC erst bei der Prüfung der bestückten Printplatten oder noch später entdeckt werden. Die Eingangsprüfung kann stichprobenweise oder vollumfänglich (100 %ig) durchgeführt werden. Der Vorteil der Stichprobenprüfung besteht im geringeren Prüfaufwand. Bei kleineren Stichproben (z.B. n = 20) besteht jedoch die Gefahr, dass Lose mit 1% bis 3% defekten IC mit über 50% Wahrscheinlichkeit angenommen werden (siehe Anhang A). Man kann sich nun fragen, ob z.B. 2% defekte IC nicht tolerierbar wären. Um diese Frage zu beantworten, sollen die Konsequenzen auf z.B. eine mit 25 IC bestückte Printplatte betrachtet werden:

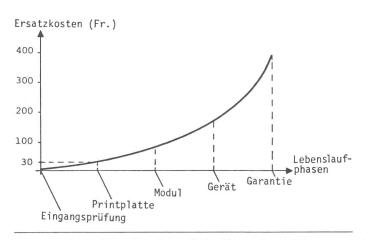

Wenn die Wahrscheinlichkeit eines defekten IC gleich 2% ist und alle IC als statistisch unabhängig angesehen werden können, dann besteht eine Wahrscheinlichkeit von  $1-0.98^{25}\approx 0.40$ , dass die bestückte Printplatte mindestens einen defekten IC enthält 1). Nun betrachte man dazu die Kosten für den Ersatz der defekten IC auf der bestückten Printplatte (Fig. 2). Für SSI- und MSI-IC liegen diese Kosten zwischen Fr. 20.– und Fr. 40.– [13; 15; 25]. Anhand dieser Angaben lässt sich ein konkreter Kostenvergleich anstellen. Das Beispiel von Tabelle I zeigt, dass eine 100 %ige Eingangsprüfung nur ca. 25 % der Kosten für die Stichprobenprüfung und für den Ersatz der defekten integrierten Schaltungen auf den bestückten Printplatten ausmacht. Der hier gefundene Wert von 25 % ist ein Mittelwert, der in zahlreichen praktischen Untersuchungen bestätigt wurde [13; 15]. Er setzt voraus, dass die Eingangsprüfung mit Hilfe geeigneter Prüfanlagen durchgeführt wird.

1) Mit 60 IC würden 70 % und mit 200 IC 98 % der bestückten Printplatten defekt sein.

Aus den obigen Darlegungen geht hervor, dass eine 100-prozentige Eingangsprüfung bei IC beträchtliche wirtschaftliche Vorteile mit sich bringen kann. Daneben gibt es aber auch technische Gründe: Es ist z.B. praktisch unmöglich, auf einer bestückten Printplatte jeden IC ausreichend zu prüfen, da einerseits der Zugang zu den Ein- und Ausgängen beschränkt ist und anderseits die Prüfung einer bestückten Printplatte in der Regel mit tiefen Frequenzen erfolgt. Es besteht damit eine latente Gefahr für intermittierende Ausfälle. Diese Überlegungen sollen jedoch nicht den Eindruck erwecken, dass eine 100%ige Eingangsprüfung die Prüfung der bestückten Printplatten überflüssig macht; beide Prüfungsarten sind notwendig und ergänzen sich gegenseitig.

Die einfachste Eingangsprüfung ist die statische Prüfung bei Raumtemperatur. Sie erlaubt eine grobe Siebung und kann mit geringem Zusatzaufwand auch bei einer höheren oder tieferen Temperatur durchgeführt werden. Wesentlich aufwendiger sind hingegen die dynamischen und parametrischen Prüfungen. Die Aufstellung der Prüfkriterien ist einfach für SSI- und MSI-IC, kann aber für LSI-IC sehr komplex werden [16; 17]. Bei Speichern und vor allem bei Mikroprozessoren zeigt sich deshalb die Notwendigkeit einer anwendungsorientierten Prüfung, nicht zuletzt um die Prüfprogrammkosten zu reduzieren.

# 2.3 Vorbehandlung

Die im Abschnitt 2.2 beschriebene Eingangsprüfung dauert in der Regel zwischen 0,3 s (für SSI-IC) und 30 s (für LSI- und VLSI-IC). Sie erlaubt deshalb lediglich die Feststellung der momentanen Funktionstüchtigkeit des betreffenden IC. Wegen des komplexen Aufbaus benötigen aber viele IC 100...2000 Betriebsstunden, um ihren thermodynamischen Gleichgewichtszustand zu erreichen. Während dieser Periode treten die sog. Frühausfälle auf. Diese Periode ist in der Zuverlässig-

Fig. 2 Typischer Verlauf der Kosten für den Ersatz einer defekten integrierten Schaltung (SSI bis MSI)

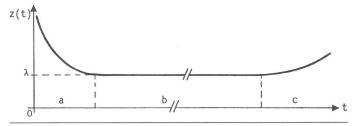

Fig. 3 Typischer Verlauf der Ausfallrate a, b und c sind die Perioden der Frühausfälle, der Ausfälle mit konstanter Ausfallrate und der Verschleissausfälle

| Vorbehandlung                                 | Zuverlässigkeitsklasse |                |                |

|-----------------------------------------------|------------------------|----------------|----------------|

|                                               | S                      | В              | С              |

| Visuelle Prüfung (intern)                     | Bedingung A            | Bedingung B    | Bedingung B    |

| Stabilisierungsofen                           | 24 h                   | 24 h           | 24 h           |

| Thermische Schocks                            | 15 Zyklen und          | 15 Zyklen oder | 15 Zyklen oder |

| Temperaturzyklen                              | 10 Zyklen              | 10 Zyklen      | 10 Zyklen      |

| Mechanische Schocks                           | 1 500 g                | nein           | nein           |

| Beschleunigungsprüfung                        | 30 000 g               | 30 000 g       | 30 000 g       |

| Dichtigkeitsprüfung                           | ja                     | ja             | ja             |

| Messung der kritischen elektrischen Parameter | ja                     | nein           | nein           |

| Burn-in                                       | 168 + 72  h            | 168 h          | nein           |

| Elektrische Prüfung                           | ja                     | ja             | ja             |

| Röntgenaufnahme                               | ja                     | nein           | nein           |

| Visuelle Prüfung (extern)                     | ja                     | ja             | ja             |

keitstheorie wohl bekannt und ist durch eine monoton fallende Ausfallrate gekennzeichnet (Fig. 3). Man rechnet, dass 1..3 % der SSI- und MSI-IC und 4...8 % der LSI-IC Frühausfälle erleiden [13; 14; 15; 18]. Frühausfälle sind besonders unerwünscht, weil sie in der Regel während den Endprüfungen oder während der Garantiezeit auftreten und hohe Zusatzkosten verursachen (Fig. 2).

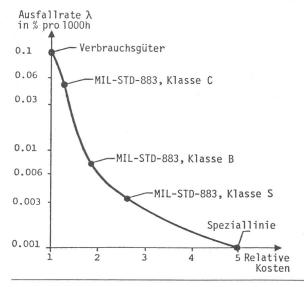

Eine effiziente Methode, um die Frühausfälle zu provozieren, ist die Vorbehandlung (screening). Darunter versteht man eine Folge von Beanspruchungen, denen die IC mit der Absicht unterworfen werden, Frühausfälle am einzelnen IC hervorzurufen. Dadurch wird die mittlere Lebensdauer der IC, welche die Vorbehandlung bestanden haben, wesentlich vergrössert. Wie aus Fig. 4 hervorgeht, kann sich dadurch eine hundertfache Verbesserung ergeben [19]²). Die Buchstaben S, B und C in Fig. 4 bezeichnen die drei Zuverlässigkeitshauptklassen der IC gemäss MIL-Normen [11]. Tabelle II gibt eine Übersicht über die entsprechenden Beanspruchungen [11; 19]. Die Festlegung der optimalen Vorbehandlungsbeanspruchungen in bezug auf Art, Umfang und Reihenfolge ist ein komplexes Problem, da die Ausfälle von der Technologie und von den Herstellungsprozessen abhängen [20...25].

Für viele Anwendungen gehen die Vorbehandlungen nach Tab. II zu weit. Untersuchungen haben gezeigt, dass man sich oft auf die thermischen Schocks, auf das Burn-in und auf eine 100 %ige Prüfung beschränken kann (siehe Anhang B).

#### 3. Die Lösung auf schweizerischer Ebene

Die vorhergehenden Ausführungen zeigen, dass die Herstellung moderner elektronicher Module oder Geräte hoher, Qualität und Zuverlässigkeit eine eingehende Qualifikation, Prüfung und Vorbehandlung der verwendeten IC erfordert. Erfahrungsgemäss kommen aber die technischen und wirtschaftlichen Vorteile der Qualifikation, Prüfung und Vorbehandlung der IC erst dann zum Ausdruck, wenn man über geeignete und leistungsfähige Prüfeinrichtungen verfügt.

Bei den Eingangsprüfungen besteht zum Beispiel die Wahl zwischen mehr oder weniger stark komponentenorientierten Prüfautomaten und universellen, computergesteuerten Prüfanlagen. Prüfautomaten werden für Fr. 50000.– bis 200000.–

2) Es wird hier angenommen, dass die Ausfallrate konstant ist, eine Annahme, die in den Zuverlässigkeitsanalysen elektronischer Geräte und Systeme oft getroffen wird [19; 27]. Der Verbesserungsfaktor hängt von der Beherrschung der Technologie und der Fertigung ab. Er kann von Hersteller zu Hersteller sehr stark variieren.

angeboten [16]. Sie benötigen für den Betrieb nur wenig Personal mit einer Spezialausbildung. Sie sind aber oft sehr beschränkt in der Leistung und in der Geschwindigkeit. Computergesteuerte Prüfanlagen sind anderseits sehr teuer (Fr. 400000.– bis 1500000.–) und benötigen für die Bedienung 2 bis 4 hochqualifizierte Spezialisten und jährlich ca. 10% des Anschaffungspreises für die Instandhaltung. Sie bieten dafür eine grosse Flexibilität bei hoher Prüfgeschwindigkeit. (Bei einfachen Funktionsprüfungen kann mit Hilfe eines «Handlers» ein Durchsatz von bis zu 8000 IC pro Stunde erreicht werden.) Prüfautomaten wie auch Prüfanlagen müssen in der Regel in 3 bis 6 Jahren amortisiert werden.

Für die umfassende und wirtschaftlich sinnvolle Qualifikation, Prüfung und Vorbehandlung einer grossen Anzahl verschiedener IC empfiehlt sich deshalb eine Lösung auf schweizerischer Ebene. Diese würde vor allem für die mittleren und kleineren Unternehmen folgende Vorteile bringen:

- Zugang zu modernen und leistungsfähigen Prüfanlagen;

- Abbau der Abhängigkeit von den Herstellern integrierter Schaltungen;

- Steigerung der Qualität und Zuverlässigkeit der Produkte und damit Reduktion der Herstellungskosten und der Garantiekosten.

Fig. 4 Wirksamkeit und Kosten der Vorbehandlung von integrierten Schaltungen Der Punkt 0.001 auf der Ordinate entspricht dem Wert  $\lambda = 10^{-8} \ h^{-1}$

Im Hinblick auf diese Vorteile wurde im Zusammenhang mit dem Impulsprogramm von den eidgenössischen Räten in ihrer Dezembersession 1978 ein Kredit von 8 Mio Fr. für die Einrichtung eines Zentrums für die Evaluation und Kontrolle elektronischer Komponenten (CECCE: Centre d'Evaluation et de Contrôle de Composants Electroniques), speziell hochintegrierter Schaltungen, in Neuenburg beschlossen. Der Kredit ist als finanzielle Starthilfe für die Jahre 1979 bis 1982 gedacht. Nach Ablauf dieser Periode, d.h. ab 1983, muss das Zentrum selbsttragend werden. Dies entspricht der Zielsetzung des Impulsprogramms des Bundes, welches als Anstoss zur Selbsthilfe konzipiert ist.

Diese Lösung kommt der ganzen Schweizerindustrie zugute. Sie soll vermeiden, dass jedes Unternehmen eigene Prüfeinrichtungen anschaffen muss, die dann möglicherweise unzweckmässig (weil zu klein) oder unwirtschaftlich (weil zu gross und damit nicht ausgelastet) sind. Vor der Anschaffung einer Prüfeinrichtung sollten die Unternehmen zukünftig auch die Möglichkeit berücksichtigen, die Qualifikation, Prüfung und Vorbehandlung der IC an das CECCE zu vergeben.

Mit dem Aufbau und dem Betrieb des CECCE wurde der Schweizerische Elektrotechnische Verein (SEV) anfangs April 1979 beauftragt. Für den SEV bedeutet dies den Aufbau einer neuen Institution [1]. Als beratende und überwachende Instanz wurde vom Vorstand des SEV ein Ausschuss bestehend aus Vertretern des Bundes, des Schweizerischen Schulrates, des Kantons Neuenburg sowie der Hersteller und der Anwender von IC gebildet.

#### 4. Aufgaben des CECCE

Kurz zusammengefasst sind die Aufgaben des CECCE:

- Stück- und Serienprüfungen für Anwender und Hersteller von IC (dazu gehören, je nach Bedarf, Eingangs- und Ausgangsprüfung, Qualifikation und Vorbehandlung von SSI- bis VLSI-IC);

- Beratung und Information über Wahl, Einsatz und Prüfung sowie über weitere Qualitäts- und Zuverlässigkeitsfragen elektronischer Komponenten, insbesondere integrierter Schaltungen;

- Förderung der Zusammenarbeit mit den Prüfstellen in der Schweizerindustrie, mit den ausländischen Testinstituten und mit den Hochschulen:

- Auf bau einer möglichst umfassenden Prüfprogrammbibliothek;

- Untersuchung von Ausfällen und Ausfallmechanismen elektronischer Komponenten;

- Aus- und Weiterbildung von Prüfspezialisten.

Sowohl die digitalen, wie auch die analogen und die hybriden IC sollen berücksichtigt werden. Wegen ihrer grossen Bedeutung und Verbreitung werden aber die digitalen, vor allem die hochintegrierten, digitalen Schaltungen im Vordergrund stehen. Eine Erweiterung des Tätigkeitsbereiches auf die bestückten Printplatten oder auf diskrete elektronische Komponenten ist denkbar, soll aber erst später gründlich überprüft werden<sup>3</sup>)

Zur Lösung dieser vielseitigen und komplexen Aufgaben wird das Zentrum über moderne, sehr leistungsfähige Einrichtungen für die Qualifikation, die Prüfung und die Vorbehandlung von SSI- bis VLSI-IC sowie über einen kleinen Stab hochqualifizierter Spezialisten verfügen. Damit soll es vor allem für die mittleren und die kleineren Unternehmen möglich werden, die Dienstleistungen des CECCE in das eigene Qualitätssicherungssystem einzubeziehen.

3) Verschiedene diskrete elektronische und elektromechanische Komponenten werden zurzeit schon beim SEV in Zürich geprüft.

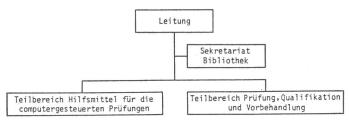

#### 5. Aufbau des CECCE

Damit das Zentrum seine Tätigkeit rasch aufnehmen kann, wurde entschieden, den Aufbau in zwei Phasen vorzunehmen. In der ersten Phase wird das Schwergewicht auf Eingangsprüfungen für Anwender von IC gelegt. In der zweiten Phase werden die Qualifikation und die Vorbehandlung dazukommen.

Zurzeit sind die Beschaffung von Prüfeinrichtungen, die baulichen Anpassungen der vom Kanton Neuenburg zur Verfügung gestellten Räumlichkeiten (ca. 400 m²) und die Einführung der Mitarbeiter im vollen Gange. Ab Anfang 1980 wird das Zentrum über 4 bis 5 Mitarbeiter und über eine sehr leistungsfähige, computergesteuerte Prüfanlage verfügen. VLSI-IC bis zu 120 Pin können dann geprüft werden. Bei der Wahl der Anlage wurden folgende Aspekte besonders berücksichtigt:

- 1. Prüfungen sowohl für Anwender wie auch für Hersteller von IC und folglich grösstmögliche Flexibilität und einfache Anpassung des «Handlers» und der Einrichtungen für Messungen an Wafers.

- 2. Kleinstmögliche Einschränkungen in bezug auf statische, dynamische und parametrische Prüfungen; möglichst viele unabhängige Pin.

- 3. Möglichkeit, sich auf vorhandene Prüfprogramme stützen zu können.

- 4. Modularer Aufbau; gute Zuverlässigkeit und Instandhaltbarkeit; guter Kundendienst.

- 5. Zusammenarbeit mit den Prüfstellen in der Schweizerindustrie und, wenn möglich, Ergänzung der dort schon vorhandenen Prüfanlagen.

Die vorgesehene prinzipielle Struktur des CECCE ist in Fig. 5 gezeigt. Beide Teilbereiche ergänzen sich gegenseitig und müssen eng zusammenarbeiten.

Dank der finanziellen Starthilfe durch den Bund wird es für das CECCE von Anfang an möglich sein, Preise und Bearbeitungszeiten im Rahmen anderer Testinstitute anzubieten.

Die Kontakte mit potentiellen Kunden werden gegen Ende 1979 aufgenommen. Mit Prüfungen für Anwender von IC soll im Frühling 1980 begonnen werden. Qualifikationen und Vorbehandlungen sollen erst ab Herbst 1980 durchgeführt werden.

- -Software für Prüfprogramme und Auswertungen

- Entwurf und Realisierung automatisierter Prüfabläufe

- Lösung von Interface-Problemen

- Beratung über Wahl, Prüfung und Einsatz von IC

- Aufbau einer Prüfprogrammbibliothek

- Kontakte, Zusammenarbeit mit ähnlich gelagerten Organisationen und mit der Software-Schule

- Aus- und Weiterbildung von Prüfspezialisten

- -Stück- und Serienprüfungen für Anwender und Hersteller von IC (statisch,dynamisch,parametrisch)

- -Qualifikation von IC

- -Vorbehandlung von IC

- -Langzeit-und Lebensdauerprüfungen

- Ausfallanalysen

- -Beratung in Zuverlässigkeits- und Qualitätsfragen elektronischer Komponenten

- Kontakte, Zusammenarbeit mit ähnlich gelagerten Organisationen

- Aus- und Weiterbildung von Prüfspezialisten

Fig. 5 Vorgesehene prinzipielle Struktur des CECCE

#### Anhang A:

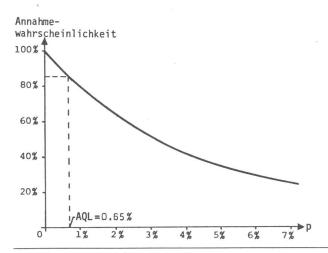

# Annahmewahrscheinlichkeit im Falle kleiner Stichproben

Bei der Durchführung einer Stichprobenprüfung stellt sich die Frage nach der Prüfschärfe, d.h. nach dem Absinken der Annahmewahrscheinlichkeit, wenn der prozentuale Anteil der defekten Betrachtungseinheiten im Los zunimmt. Folgendes Beispiel soll zeigen, dass im Falle kleiner Stichproben, Lose mit hohem prozentualem Anteil defekter Betrachtungseinheiten mit einer grossen Wahrscheinlichkeit angenommen werden können.

Es sei ein Los von 100 IC eines bestimmten Typs gekauft worden. Die Eingangsprüfung soll nach einem Einfach-Stichprobenplan für normale Prüfung mit AQL = 0,65% durchgeführt werden. Nach CEI 410 oder MIL-STD-105 findet man folgende Stichprobenvorschrift: man nehme eine Stichprobe von n = 20 IC, führe die Prüfung durch und nehme das Los an, falls kein defekter IC gefunden wird (c = 0); sonst weise man das Los zurück. Wenn man mit p die Wahrscheinlichkeit bezeichnet, dass ein IC defekt ist (Ausschusswahrscheinlichkeit), so kann man die Wahrscheinlichkeit berechnen, dass in einer Stichprobe von 20 IC kein defekter IC gefunden wird. Unter der Annahme statistischer Unabhängigkeit folgt dann für die gesuchte Wahrscheinlichkeit der Ausdruck  $(1-p)^{20}$ , siehe z.B. [26]. Fig. 6 stellt das Resultat graphisch dar. Für den Wert p = AQL = 0,65% findet man eine Annahmewahrscheinlichkeit von 0,88, dass in der Stichprobe von 20 IC kein defekter IC gefunden wird. Diese Wahrscheinlichkeit fällt aber wegen des kleinen Stichprobenumfanges nur allmählich ab, wenn p zunimmt. Für  $p = 10 \cdot AQL$ 6,5% hat man immer noch den Wert 0,26. Im Zusammenhang mit kleinen Stichproben besteht damit für den Anwender das Risiko, dass er Lose mit grosser Ausschusswahrscheinlichkeit annimmt.

### Anhang B: Preiswerte und wirksame kombinierte Eingangsprüfung und Vorbehandlung der IC

Eine Vorbehandlung der IC nach den MIL-Normen [11] ist umfangreich und kann für übliche Industrieanwendungen zu teuer sein (Fig. 4, Tabelle II). Die Praxis hat gezeigt, dass eine Vorbehandlung bestehend aus thermischen Schocks und Burn-in wirksam und gleichzeitig preisgünstig ist [13; 14; 15; 18]. Der thermische Schock simuliert die mechanischen Beanspruchungen, welche durch den Temperaturgradienten zwischen Chip und Gehäuse gegeben werden. Ein Schock besteht in der Regel aus einem raschen Übergang von + 100 °C auf 0 °C und von 0 °C auf + 100 °C mit Anhaltsdauer an den Grenzwerten  $\geq$  5 min und Transferzeiten  $\leq$  10 s. (Für den Militärbereich hätte man + 150 °C und - 65 °C.) Während dem Burn-in wird der IC auf einer konstanten, erhöhten Temperatur betrieben (statisch oder dynamisch). Die Temperatur muss so hoch wie möglich eingestellt werden, jedoch ohne die Temperatur auf dem Chip über 150 °C steigen zu lassen. Die Dauer des Burn-in muss der Dauer der Periode der Frühausfälle entsprechen (Fig. 3). Die Erfahrung zeigt, dass in der Regel 96 h für SSI- und MSI-IC

Annahmekennlinie für eine Stichprobe mit Umfang n = 20 Fig. 6 und Annahmezahl c = 0(Die Kurve geht auf Null für p = 100 %)

und 168 h für LSI-IC ausreichen: 168 h bei 150 °C Chiptemperatur entsprechen 2000 bis 3000 h bei 25 °C Raumtemperatur.

Eine Vorbehandlung bestehend aus 10 bis 15 thermischen Schocks und einem Burn-in, gefolgt von einer 100 %igen Eingangsprüfung bietet eine wirksame und preisgünstige Lösung der Probleme der Frühausfälle (und damit auch der defekten IC). Sie ist in den USA weit verbreitet. Die Preise sind wegen den grossen Serien entsprechend niedrig; man rechnet Fr. -. 20 bis -. 30 für SSI- und MSI-IC [13; 14; 15].

#### Literatur

- [1a] Eine neue Institution des SEV. Das Zentrum für die Evaluation und Kontrolle Elektronischer Komponenten (EKEK-Zentrum) in Neuenburg. Bull. SEV/ VSE 70(1979)15, S. 789...790.

- [1b] Une nouvelle institution de l'ASE. Le Centre d'Evaluation et de Contrôle des Composants Electroniques (CECCE) à Neuchâtel. Bull. ASE/UCS 70(1979)15, p. 791...792.

- R. Allan: Semiconductors: toeing the (microfine)line. IEEE Spectrum 14(1977)12, p. 34...40.

- Joint special issue on very large-scale integration. IEEE Trans. ED 26(1979)4, p. 257...732.

- R. W. Kepes: The evolution of digital electronics towards VLSI. IEEE Trans. ED 26(1979)4, p. 271...279. [4]

- G. Moore: VLSI: some fundamental challenges. IEEE Spectrum 16(1979)4,

- R. Allan: VLSI: scoping its future. IEEE Spectrum 16(1979)4, p. 30...37.

- R.N. Gossen: The 64-kbit RAM: a prelude to VLSI. IEEE Spectrum 16 (1979)3, p. 42...45.

- D. Queyssac: Projecting VLSI's impact on microprocessors. IEEE Spectrum 16(1979)5, p. 38...41. [8]

- E.A. Torrero: VSLI and other solid-state devices. IEEE Spectrum 16(1979)1, p. 43...47.

- R.H. Cushman: Microprocessor directory. EDN 23(1978)21, p. 87...190.

- Test methods and procedures for microelectronics. MIL-STD-883. Lists of standard microcircuits. MIL-STD-1562.

- E. Rubinstein: Independent test labs: caveat emptor. IEEE Spectrum 14(1977)6, [13] p. 44...50

- W. T. Greenwood: Reliability testing for industrial use. Computer 10(1977)7, p. 26...30.

- B. Coker: Device testing vs. circuit board testing. Anaheim/California 92807, Electronic Test Center, 1976.

- [16a] M. Marshall: Logic in testingland a tale of measurement techniques. EDN 21(1976)2.

- [16b] M. Marshall: Through the memory cells further explorations of IC's in testingland. EDN 21(1976)4. [16c] M. Marshall: Microprocessors in testingland – the jury receives its instruc-tions. EDN 21(1976)6.

- [17] A. Bluestone: Logical environment comparison testing handles complex LSI

- devices. Computer Design 18(1979)4, p. 95...102.

A. Stadler: Relative IC failure rates summary. Houston/Texas, Reliability [18] Inc., 1979. [19] R.T. Anderson: Reliability design handbook, RDH-376, New York, Relia-

- bility Analysis Center/Griffis Air Force Base, 1976. J.T. Henderson: IC screening, reliability or ripoff. Proceedings of the IEEE Reliability and Maintainability Symposium (1976), p. 452...455.

- R.C. Forster: Why consider screening, burn-in, and 100-percent testing for commercial devices. IEEE Trans, MFT 5(1976)3, p. 52...58.

J.D. Ekings and R.L. Sweetland: Burn-in forever? There must be a better way, Proceedings of the IEEE Reliability and Maintainability Symposium

- (1978), p. 286...293.

D.S. Peck: New concerns about integrated circuit reliability. Reliability [23] Physics. Annual Proceedings 16(1978), 1...6

- E.R. Hnatek: High-reliability semiconductors: paying more doesn't always pay off. Electronics 50(1977)3, p. 101...105.

- F. Danner and J. J. Lombardi: Setting up a cost-effective screening program for ICs. Electronics 44(1971)18, p. 44...47.

- [26a] A. Birolini: Zuverlässigkeit von Schaltungen und Systemen. Autographie zur Vorlesung an der ETH Zürich. 3. Auflage. Zürich, Selbstverlag, 1978.

- [26b] A. Birolini: Zuverlässigkeitstechnik. Autographie zum Fortbildungskurs an der Universität Neuenburg. Zürich, Selbstverlag, 1979.

[27] A. Birolini: Qualitäts- und Zuverlässigkeitssicherung komplexer Systeme –

- Teil 1: Aufgaben und organisatorische Voraussetzungen. Bull. SEV/VSE 70(1979)3, S. 142...148. Teil 2: Methoden. Bull. SEV/VSE 70(1979)5, S. 237 bis 243.

#### Adresse des Autors

Dr. A. Birolini, Association Suisse des Electriciens, CECCE, Ruelle Vaucher 22, 2000 Neuchâtel