|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 68 (1977)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 17                                                                                                                                                                                                                        |

| <b>Artikel:</b>     | Le Microsystème 8 CEI                                                                                                                                                                                                     |

| <b>Autor:</b>       | Nguyen, H.                                                                                                                                                                                                                |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-915064">https://doi.org/10.5169/seals-915064</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 27.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Le Microsystème 8 CEI<sup>1)</sup>

Par H. Nguyen

681.3.066 : 681.325-181.48

On décrit la structure générale d'un système composé d'un microprocesseur et de périphériques spécialisés, conçu et réalisé pour l'application au réglage digital de machines électriques. Afin de réduire le temps de calcul, on a développé en particulier un multiplicateur et un diviseur rapides câblés qui sont appelés par l'unité centrale comme des périphériques.

Die allgemeine Struktur eines Systems bestehend aus einem Mikroprozessor und speziellen Peripheriegeräten wird beschrieben, das insbesondere für die digitale Regelung von elektrischen Maschinen entworfen wurde. Um die Rechenzeiten zu verkürzen, wurden ein spezieller verdrahteter schneller Multiplikator und eine Divisionsschaltung entwickelt, die von der Zentraleinheit wie Peripheriegeräte aufgerufen werden können.

## 1. Introduction

L'asservissement échantillonné a déjà fait l'objet d'études depuis la deuxième guerre mondiale. Les applications sont devenues de plus en plus nombreuses surtout ces dernières années, grâce aux progrès réalisés dans le domaine de l'informatique industrielle. La baisse du coût a permis l'introduction des mini-ordinateurs dans les chaînes d'automatisme. Quant aux petites installations, un nouvel outil de travail vient d'être mis à disposition de l'automaticien: le microprocesseur, modeste en format mais vaste en possibilités.

Avec l'évolution actuelle de la technologie, la décomposition d'un système à microprocesseur en modules fonctionnels devient une nécessité: c'est un bus «universel» qui dicte les lois de communication aux différents dispositifs (processeur central, mémoires, périphériques ...) gravitant autour. Ainsi développés, les périphériques restent indépendants du microprocesseur utilisé. Un effort de standardisation devient avantageux tant au niveau du software qu'à celui du hardware: l'ensemble de signaux de contrôle restant le même, l'utilisation des nouveaux composants intégrés ne peut être que profitable pour réduire la consommation et le nombre de circuits et augmenter les performances sans devoir modifier les programmes et le système.

## 2. Description du système de base

### 2.1 Structure générale

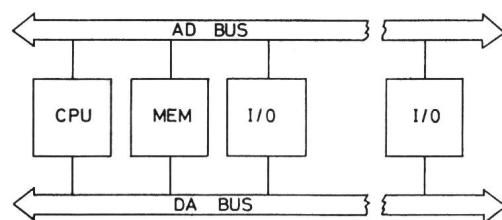

Le schéma bloc de la fig. 1 donne une description de l'architecture du microsystème. On y distingue l'unité centrale CPU, les mémoires (vives et mortes) MEM et les interfaces d'entrée-sortie I/O; le tout est relié par un unibus (AD et DA BUS) qui véhicule les informations et les signaux de contrôle d'une manière bidirectionnelle: la situation géographique des différentes cartes ne joue aucun rôle.

Le bus a été choisi surtout pour les microprocesseurs du type n-MOS<sup>2)</sup>. Il se subdivise en trois groupes: le groupe DA (DATA), le groupe AD (ADDRESS) et un troisième laissé à disposition de l'utilisateur, chacun comportant 16 lignes. Pour la définition des deux premiers groupes, on se réfère à [1]<sup>3)</sup>.

<sup>1)</sup> Récemment, la Chaire d'Electronique Industrielle de l'EPFL sous la direction du professeur H. Bühler a pu fêter ses cinq ans d'activité. A cette occasion, un bulletin contenant des articles sur des travaux exécutés à cette Chaire a été édité et distribué à un cercle d'intéressés restreint. Pour faire connaître ces travaux à un public plus large, nous publierons successivement trois des articles en question.

Le travail «Microsystème 8 CEI» a pu être réalisé grâce à un subside de la Commission pour l'encouragement des recherches scientifiques. Il faut bien noter que dans cet article CEI signifie «Chaire d'Electronique Industrielle» et non «Commission Electrotechnique Internationale».

<sup>2)</sup> n-channel metal-oxide semiconductor.

<sup>3)</sup> Voir la bibliographie à la fin de l'article.

L'unité centrale qui contrôle actuellement notre système se base sur le processeur Motorola M6800B. Celui-ci possède une longueur de mot égale à 8 bits et s'adapte assez facilement au bus mentionné. Son choix a été dicté par le fait qu'il se trouve parmi les plus rapides dans sa catégorie, et sa mise en œuvre est relativement simple.

La mémoire possède une capacité maximale égale à 8K. Cette option se motive par le domaine des applications prévues; une plus grande taille n'augmente qu'inutilement le nombre de lignes d'adresse à prendre en considération. Tant pour les RAM (random access memory) que pour les ROM (read only memory), les mémoires s'organisent en blocs de 1K chacun. Dans le cas particulier du processeur 6800B, où la page zéro (les 256 premières positions) se trouve favorisée par un court temps d'accès, la première moitié de cette dernière est réservée aux périphériques, tandis que l'autre moitié sert de support à des informations auxquelles on se réfère souvent. En même temps les adresses d'interruption, de TRAP, de NMI (Non maskable interrupt) et de RESTART sont codées sur 2 bytes chacune et mémorisées

Fig. 1 Schéma bloc du microsystème 8 CEI

dans une ROM, successivement de la position 17770<sub>8</sub> à 17777<sub>8</sub> (en octal).

Les interfaces d'entrée-sortie ont une structure parallèle ou série selon les périphériques mis en jeu. Pour des applications au réglage automatique, l'exigence d'une grande vitesse de réponse impose la configuration parallèle. Au contraire, les périphériques servant de support au développement des programmes (par exemple: télétype, lecteur de bande), se contentent en général de la solution série certes lente, mais plus simple [2].

### 2.2 Software de support

L'existence d'un cross-assembleur implanté sous RT-11 du mini ordinateur PDP 11/40 et développé par le laboratoire de calculatrices digitales (LCD) de l'EPFL possède l'avantage de décharger le microsystème du travail de traduction et met à disposition un langage symbolique plus explicite que celui proposé par le fabricant [3].

Une fois le programme traduit, il faut pouvoir le tester dans l'environnement réel où il sera implanté définitivement.

L'existence d'un programme ODT (Octal debugging tool) résident donne une grande souplesse à cette phase de test et évite ainsi le recours à la procédure «start and execute» qui ne permet qu'une conclusion très sommaire (réussite ou échec). Développé initialement par le LCD, ce programme est assisté par un display (ou télétype) et un lecteur de bandes; des compléments ont été apportés pour commander un programmateur de PROM et pour mettre au point et tester certains des périphériques spécialisés.

### 2.3 Caractéristiques mécaniques et électriques

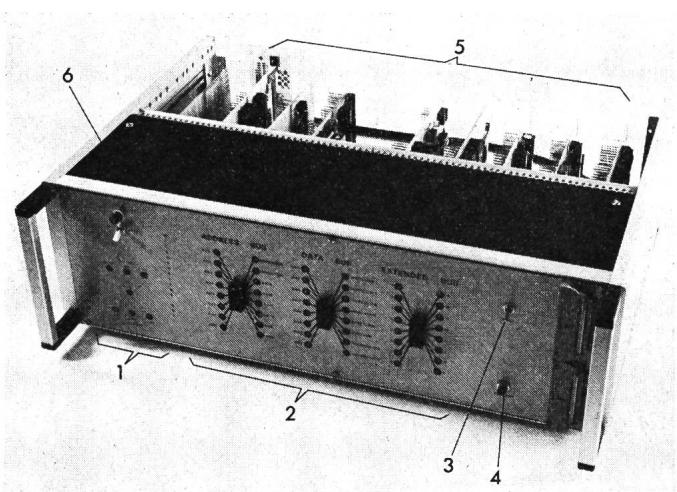

La fig. 2 illustre l'organisation mécanique du microsystème. Le rack 19" abrite d'une part les blocs d'alimentation; d'autre part de la place est prévue pour loger dix cartes de format européen. Un panneau avant donne des facilités d'accès au bus (3 socles à 16 pins à circuit intégré en parallèle avec des douilles de 1 mm de diamètre), de commande d'arrêt (HALT) et de démarrage (RESTART) et d'utilisation des tensions d'alimentation depuis l'extérieur.

Le microsystème est alimenté par le réseau 220 V, 50 Hz. Des blocs d'alimentation fournissent les tensions nécessaires:  $\pm 15$  V pour les circuits analogiques,  $\pm 15$  V et  $+5$  V pour le digital (de ces  $\pm 15$  V on dérive individuellement sur les cartes les autres tensions intermédiaires nécessaires). Pour des questions d'immunité aux bruits, deux terres sont prévues pour l'analogique et le digital et reliées uniquement au niveau du réseau.

### 3. Les périphériques spécialisés

Un certain nombre de périphériques a été développé à la CEI pour des applications dans le domaine du réglage des machines.

#### 3.1 Multiplicateur rapide

L'opération de multiplication se retrouve assez fréquemment dans les programmes. La solution par software conduit à des temps de calcul parfois inacceptables. L'existence de

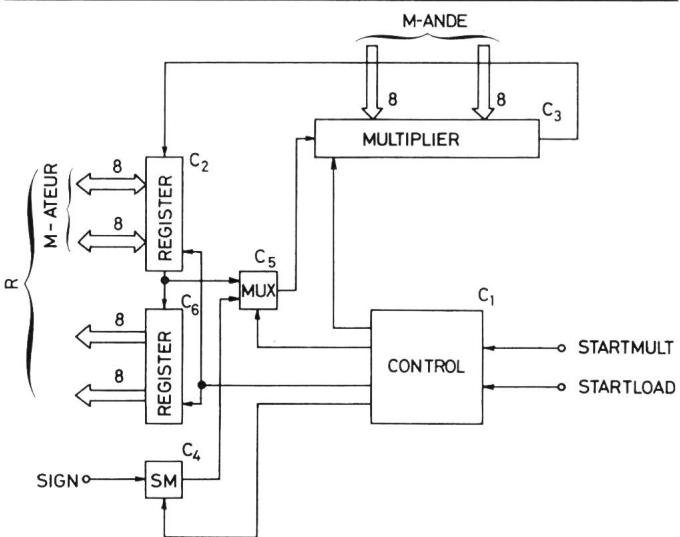

Fig. 3 Schéma bloc du multiplicateur 16/16 bits

circuits intégrés multiplicateurs du type série-parallèle incite à développer un périphérique pour cette opération (fig. 3):

L'impulsion STARTLOAD indique au bloc de contrôle  $c_1$  de charger l'opérande multiplicateur M-ATEUR dans le registre  $c_2$  et le multiplicande M-ANDE dans le buffer du multiplicateur  $c_3$ ; en même temps on mémorise le signe de M-ATEUR dans  $c_4$ . Le signal STARTMULT démarre le calcul en fournissant les impulsions nécessaires: de la première à la 16e impulsion, le multiplexeur  $c_5$  laisse passer la sortie du registre  $c_2$  dans  $c_3$ ; de la 16e impulsion jusqu'à la fin (32 en tout), c'est la sortie de la bascule  $c_4$  de mémorisation du signe qui est prise en considération. Pendant tout ce temps le résultat sort à la même cadence de  $c_3$  et se trouve décalé dans les registres  $c_2$  et  $c_6$ .

Bien qu'il soit construit pour une opération de 16 bits  $\times$  16 bits (en complément à 2) le périphérique peut être utilisé également pour des multiplications 16 bits  $\times$  8 bits et 8 bits  $\times$  8 bits. Notons que ce multiplicateur travaille en complément à 2 et suivant le principe de l'algorithme de Booth, et le temps de calcul (durée depuis l'impulsion de STARTMULT jusqu'à l'obtention du résultat complet dans  $c_2$  et  $c_6$ ) s'élève à 3,5  $\mu$ s.

#### 3.2 Diviseur rapide

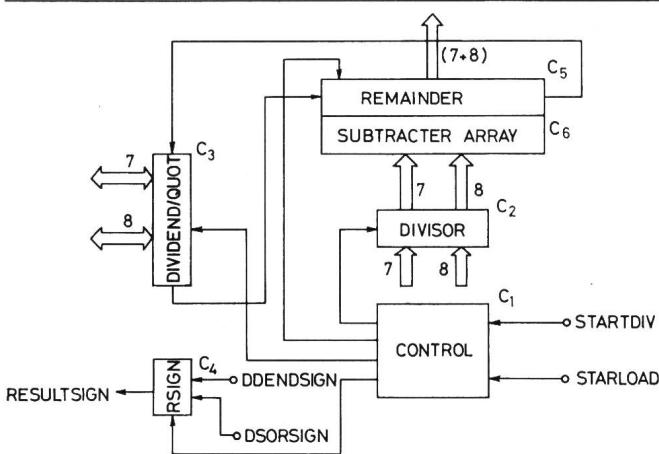

Une autre opération arithmétique utilisée dans de nombreux cas (par exemple dans l'approximation de certaines fonctions arithmétiques comme arc cosinus ...) est la division. Là aussi le compromis vitesse-nombre de composants mène à une structure du type série-parallèle (fig. 4):

L'impulsion STARTLOAD demande au bloc de contrôle  $c_1$  de charger le diviseur dans le registre  $c_2$ , le dividende dans  $c_3$  et leurs signes DDENDSIGN et DSORSIGN dans  $c_4$ . Le signal STARTDIV démarre le calcul en générant les impulsions nécessaires pour décaler le dividende dans le buffer  $c_5$  où il se trouve combiné avec le diviseur grâce au système logique combinatoire  $c_6$ ; en même temps le résultat sortant de  $c_5$  entre à la même cadence dans le registre  $c_3$ . A la fin de la division on obtient le quotient dans  $c_3$ , le reste dans  $c_5$  (le diviseur reste inchangé), alors que le signe RESULTSIGN est déjà disponible au moment du chargement des opérandes.

Fig. 2 Vue d'ensemble du microsystème 8 CEI

- 1 Power on/off - ( $\pm 15$  V, 0 V) analogique - ( $\pm 15$  V, 5 V, 0 V) digital

- 2 Accès au bus

- 3 Halte

- 4 Restart

- 5 Place pour 10 eurocartes

- 6 Bloc d'alimentation

Fig. 4 Périphérique diviseur 16/16 bits

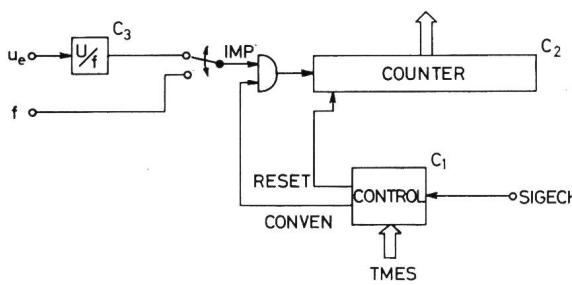

Fig. 5 Dispositif de mesure digitale de vitesse

Les longueurs des opérandes sont les mêmes que pour le multiplicateur. Par contre, on travaille ici avec «bit de signe + valeur absolue», et le temps s'élève à 5 µs.

### 3.3 Mesure digitale de la vitesse

Une manière relativement simple de mesurer numériquement la vitesse d'une machine tournante est représentée sur la fig. 5. Lors de l'impulsion d'échantillonnage SIGECH, avec un petit retard pendant lequel le processeur vient lire le résultat dans  $c_2$ , le signal RESET remet  $c_2$  à zéro, puis CONVEN passe à «1» pour laisser passer les impulsions IMP qui sont comptées dans  $c_2$ . Ces impulsions proviennent soit du convertisseur  $U/f$   $c_3$  qui donne une fréquence proportionnelle à la tension d'entrée  $u_e$  (qui est l'image de la vitesse si l'on utilise pour les essais un simulateur de machine), soit d'un dispositif à disque strié fixé à l'arbre de la machine qui fournit un train d'impulsions avec une fréquence  $f$  proportionnelle à la vitesse. La durée pendant laquelle CONVEN = 1 découle de la valeur TMES qui peut être programmée selon les besoins. On obtient à la sortie du compteur  $c_2$  une représentation digitale de la vitesse:

$$MES = f_{IMP} \cdot TMES$$

où  $f_{IMP}$  est la fréquence des impulsions IMP.

Il est entendu que la période d'échantillonnage doit être légèrement supérieure à TMES pour assurer le bon fonctionnement du montage.

### 3.4 Convertisseur A/D et D/A

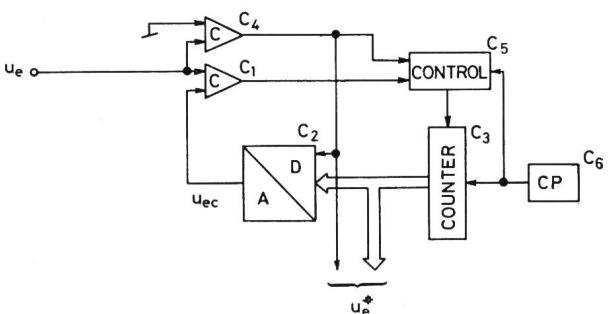

Le convertisseur A/D suivant classique représenté à la fig. 6 permet la digitalisation permanente d'une grandeur analogique  $u_e$ . Cette dernière est comparée ( $c_1$ ) à la sortie  $u_{ec}$

du convertisseur D/A ( $c_2$ ) dont l'entrée digitale provient du compteur  $c_3$  et du comparateur de signe  $c_4$ . Le sens du comptage UP/DOWN se détermine par le signe de  $(u_{ec} - u_e)$  et de celui de  $u_e$  au niveau du bloc de contrôle  $c_5$  qui assure en même temps la synchronisation avec l'horloge CP ( $c_6$ ) afin d'éviter de changer UP/DOWN pendant CP = 0. Le résultat  $u_e^*$  s'obtient sous la forme «bit de signe + valeur absolue»; pour les applications, 7 bits pour coder cette valeur absolue sont prévus.

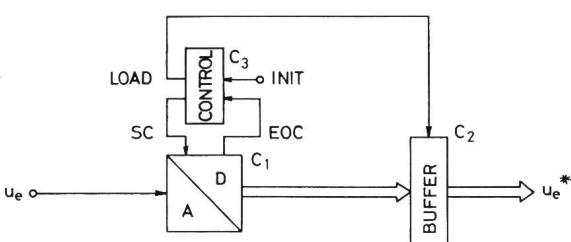

Tout en gardant l'exigence de la présence permanente de la grandeur digitale, on peut mettre en œuvre un convertisseur intégré rapide A/D à approximations successives (fig. 7), la fin de chaque conversion indiquée par le signal EOC (End of convert) sauve la sortie de  $c_1$  dans le buffer  $c_2$ , puis génère la conversion suivante par l'impulsion SC (Start convert). Le signal INIT permet le démarrage du dispositif. Avec l'utilisation d'un A/D du type ADC82 (Burr Brown), on obtient la valeur digitale sous forme de complément à 2.

Quant à la conversion inverse par un convertisseur D/A, l'existence de circuits intégrés (p. ex. mono DAC 02; DAC 70) facilite beaucoup la tâche.

### 3.5 Synchronisateur programmable

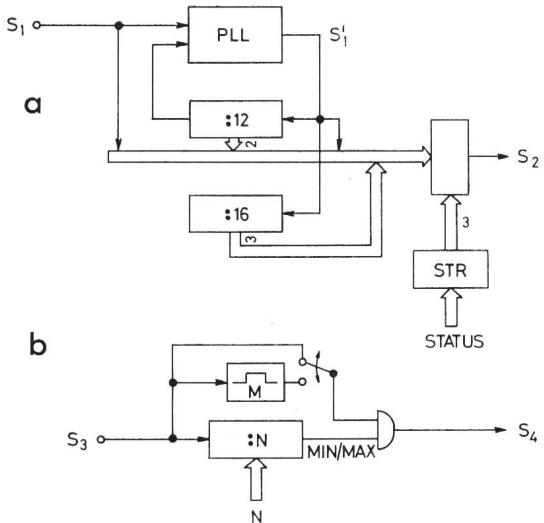

Le schéma de la fig. 8a a été conçu spécialement pour les cas où l'on travaille avec des convertisseurs de courant: A cause de l'ondulation, il faut une synchronisation des instants d'échantillonnage pour s'assurer d'une mesure constante au cas où la valeur moyenne du courant ne varie pas. Le PLL (Phase locked loop), contre-réactionné par un diviseur par 12, fournit à sa sortie  $s_1$  une fréquence 12 fois plus élevée et synchronisée sur l'entrée  $s_1$ . Grâce encore à un compteur par 16, on a à disposition à l'entrée du multiplexeur des fréquences 12 fois (convertisseur de courant en pont hexaphasé), 6 fois (montage en pont triphasé), 4 fois, 3 fois (étoile triphasée), 2 fois (redresseur à 2 alternances) et 1,5 fois celle de  $s_1$ . Le mot d'état STATUS à 3 bits du registre

Fig. 6 Convertisseur A/D suivant utilisant un convertisseur D/A en contre-réaction

Fig. 7 Convertisseur A/D suivant utilisant un convertisseur A/D rapide à approximations successives

**Fig. 8** Synchroniseur programmable

a Multiplicateur en fréquence

b Diviseur en fréquence

**Fig. 9** Horloge à temps réel programmable

STR choisit l'une de ces fréquences. Ainsi, quel que soit le type de convertisseur de la liste citée, on arrive à une mesure «uniforme» du courant malgré son ondulation en branchant le réseau d'alimentation en  $s_1$  (par l'intermédiaire p. ex. d'un transformateur).

Quant au circuit de la fig. 8b, il génère un signal  $s_4$  de fréquence  $N$  fois moins élevée que l'entrée  $s_3$  et de largeur (durée où  $s_4 = 1$ ) égale soit à celle de  $s_3$ , soit à celle de la sortie de la monostable M. Il faut noter que la durée de l'impulsion de M doit être au moins égale à celle de  $s_3$ . Ce dispositif trouve son utilité p. ex. quand on désire surveiller le courant plus souvent que la vitesse tout en gardant le synchronisme.

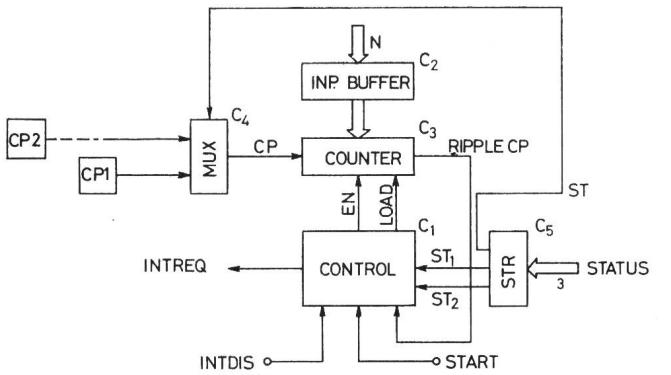

### 3.6 Horloge programmable

Le schéma de la fig. 9 fournit une horloge programmable offrant plusieurs modes de fonctionnement. Le signal START, par l'intermédiaire du bloc de contrôle  $c_1$ , charge le contenu du buffer  $c_2$  dans le décompteur  $c_3$ , puis met EN à «1» pour commencer le décomptage à la cadence de CP, ce dernier provenant du multiplexeur  $c_4$  commandé par le bit ST<sub>0</sub> du registre d'état  $c_5$  et dont les deux entrées sont reliées respectivement à une horloge locale CP<sub>1</sub> et à une source externe CP<sub>2</sub>. A la fin de la période indiquée par le signal RIPPLECP, si le bit ST<sub>1</sub> est à «1», la ligne INTREQ se met

**Fig. 10** Tables de codage et lecture digitales

a Table de codage et lecture de base

b Table de transformation en sortie à collecteur ouvert

à l'état actif et ne sera désactivée que par le signal INTDIS. En même temps la même séquence se répète si le bit ST<sub>2</sub> est à «1», tandis que ST<sub>2</sub> = 0 correspond à une seule séquence de décomptage.

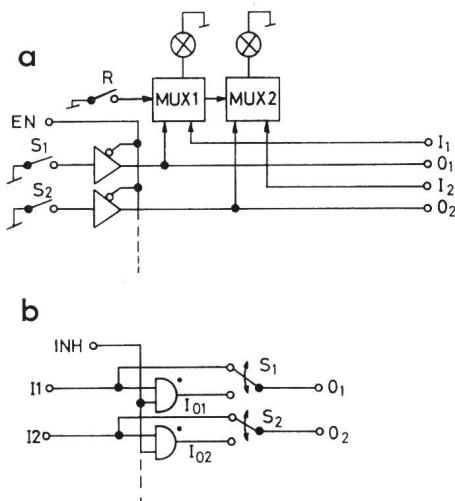

### 3.7 Tables de codage et lecture digitales

Dans les phases de mise au point ou de dépannage, on est souvent appelé à imposer ou examiner des niveaux logiques d'une manière statique. Le schéma de la fig. 10a permet de lire l'état de O (OUTPUT) ou I (INPUT) suivant la position de l'interrupteur R. Les signaux O peuvent provenir soit de l'extérieur (EN = 1), soit des interrupteurs S. La table comprend 16 bits de codage. On possède deux commandes EN séparées pour le byte «haut» et pour le byte «bas». Quant à l'alimentation et le niveau logique, le choix s'étend de 0 à 18 V.

La deuxième table (fig. 10b) joue un rôle complémentaire. Elle transforme les 16 entrées I TTL (transistor-transistor logic) en signaux à collecteur ouvert I<sub>O</sub>; les sorties O sont branchées par l'intermédiaire des interrupteurs S, soit à I, soit à I<sub>O</sub>. La commande INH permet de mettre à zéro I<sub>O</sub>. Notons que cette table doit être alimentée en +5 V.

### Bibliographie

- [1] J.-D. Nicoud: Mubus standard. *Microscope* 1(1976)2, p. 7...8.

- [2] J.-D. Nicoud: Interfacing. Proceedings of the International Symposium and Course on Mini- and Microcomputers and their applications, Zurich, June 2...5, 1975 (MIMI'75). Calgary, Alberta, Canada, Acta Press, 1976; p. 22...27.

- [3] J.-D. Nicoud: Microprocessor 6800: software. *Microscope* 1(1976)2, p. 9...18.

### Adresse de l'auteur

Ha Nguyen, Chaire d'électronique industrielle, EPFL, 16, chemin de Bellerive, 1007 Lausanne.