|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 68 (1977)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 2                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Ladungsverschiebeelemente                                                                                                                                                                                                 |

| <b>Autor:</b>       | Guggenbühl, W.                                                                                                                                                                                                            |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-914982">https://doi.org/10.5169/seals-914982</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 27.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Ladungsverschiebeelemente<sup>1)</sup>

Von W. Guggenbühl

## 1. Einleitung

Unter Ladungsverschiebe- oder Ladungstransport-Elementen versteht man heute meistens schieberegisterartige Strukturen, die vom Prinzip her für den Betrieb mit amplitudentkontinuierlichen (analogen) Signalen geeignet sind. Die rapide Entwicklung der modernen Halbleitertechnologie hat auf dem Gebiet dieser als «Charge Transfer Devices» (CTD)<sup>2)</sup> bezeichneten Elementen in den letzten Jahren grosse Fortschritte gebracht und ermöglicht hochintegrierbare Strukturen, die auf den Gebieten der Verzögerung und Verarbeitung abgetasteter Analogsignale, der Digitalspeicher und der Photosensoren grosse Bedeutung erlangen können.

Die Idee des analogen Schieberegisters ist schon alt. Bereits 1943 erscheint sie in der Patentliteratur [1]<sup>3)</sup> in der Form einer Kette von Kondensatoren, die durch schaltbare Verstärker getrennt sind und auf denen die Abtastwerte eines kontinuierlichen Signals temporär gespeichert werden. Diese Schaltung hat aber keine breite Verwendung gefunden. Erst die in den letzten Jahren bekanntgewordenen, zur Grossintegration geeigneten Konzepte der Ladungsverschiebung längs Kristalloberflächen [2; 3] versprechen eine praktisch erfolgreiche Realisierung dieses für viele Anwendungen interessanten Schaltungskonzeptes.

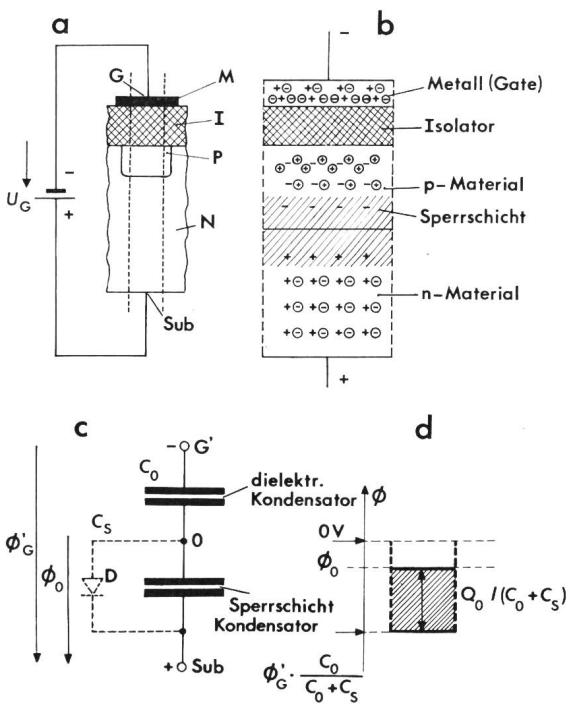

Fig. 1 Schichtfolge Metall-Isolator-p-Halbleiter-n-Halbleiter als Oberflächenspeicher Typ A

- a Schichtstruktur

G = Gate-Anschluss, Sub = Substrat-Anschluss

- b Ladungsverteilung

+ - fixe Atomrest-Ladungen

⊕ ⊖ bewegliche Ladungen

- c Vereinfachtes Kondensatormodell

$C_0$  Oberflächenkondensator

$C_s$  Sperrsichtkondensator (auf Flächeneinheit bezogen)

- d Oberflächenpotential  $\phi_0$  als Füllniveau einer Potentialwanne.

$Q_0$  gespeicherte Ladung (auf Flächeneinheit bezogen)

621.377.622.12

## 2. Wirkungsweise von Ladungsverschiebeelementen

### 2.1 Ladungsspeichervorgänge an Halbleiteroberflächen

Die modernen Ladungsverschiebeelemente basieren auf zwei Typen von Halbleiter-Oberflächenkondensatoren. Bei der in Fig. 1 skizzierten Form verwendet man eine dielektrisch isolierte Metallelektrode über einer p-n-Diode, deren p-leitende Schicht potentialmäßig schwiebt (floating). Die andere in Frage stehende Struktur (Fig. 2) ist der klassische MOS-Kondensator. Es soll nun zunächst ein Modell für das Verhalten solcher Kondensatorstrukturen bei Variation der angelegten Spannung entwickelt und nachfolgend auf Ladungsspeicherketten angewendet werden.

Die Ladungsverteilung in der als Oberflächenkondensator benutzten Schichtstruktur Fig. 1a ist in Fig. 1b schematisch aufgezeichnet. Man erkennt aus dieser Darstellung, dass bei Einbezug des sog. Sperrsichtspeicherbegriffs aus der Halbleitertechnik die Anordnung als Serieschaltung zweier Kondensatoren, nämlich einer normalen, dielektrisch isolierten Dreischichtstruktur und eines p-n-Sperrsichtkondensators, aufgefasst werden kann (Fig. 1c). Die gestrichelt angedeutete p-n-Diode ist bei der gewählten Spannungsrichtung gesperrt. Vereinfachend soll nun angenommen werden, dass die in Frage stehenden Kondensatoren lineare Schaltelemente seien. Der Oberflächenkondensator wird dadurch gut, der Sperrsichtkondensator nur näherungsweise beschrieben. Man kann im derart linearisierten Modell das Potential  $\Phi_0$  am Punkt 0 zwischen den beiden Kondensatoren Fig. 1c relativ zum Klemmenpunkt Sub leicht berechnen. Es entspricht in der Anordnung Fig. 1a dem Potential an der Halbleiteroberfläche bezogen auf die n-leitende Substratzone.

$\Phi_0$  ist gemäss

$$\Phi_0 = \Phi_{G'} \frac{C_0}{C_0 + C_s} + \frac{Q_0}{C_0 + C_s} \quad (1)$$

von dem über den beiden Kondensatoren wirksamen Potentialgefälle  $\Phi_{G'}$  und der auf der «Oberfläche» befindlichen «freien» Ladung  $Q_0$  abhängig. Das Oberflächenpotential gemäss Gl. (1) lässt sich als oberes Niveau einer mit Ladung bzw. Flüssigkeit gefüllten Potentialwanne (potential well) gemäss Fig. 1d interpretieren, deren Boden durch die zwischen dem Gate und Substrat wirksame Potentialdifferenz  $\Phi_{G'}$  angehoben und abgesenkt werden kann. Die seitliche Begrenzung des so erzeugten Potentialtopfs ist durch die laterale Ausdehnung der Metallelektrode bzw. des p-n-Übergangs gegeben; die «Höhen» dieser seitlichen Wände sind durch die Potentiale der Nachbarzonen definiert.

Zur exakten Behandlung des Zusammenhangs zwischen Ladung und Potential der Kondensatorstruktur Fig. 1 wäre eine genauere Modellierung der Speicherphänomene an Halbleiteroberflächen erforderlich, die jedoch detaillierte Kenntnisse der Halbleiterphysik nichthomogener Strukturen voraussetzt. So weicht die Halbleiteranordnung Fig. 1a beispiels-

<sup>1)</sup> Vortrag, gehalten an der SEV-Informationstagung über «Moderne Technologien in der Elektronik» am 11. November 1976 in Biel.

<sup>2)</sup> Die verwendeten Abkürzungen sind auf S. 70 zusammengestellt.

<sup>3)</sup> Siehe Literatur am Schluss des Aufsatzes.

weise in folgenden Punkten wesentlich vom vereinfachten Modell Fig. 1c ab:

- Der Sperrsichtkondensator  $C_s$  ist nicht konstant, d.h.  $C_s = f(\phi_0)$ .

- Die geometrischen Abmessungen der Sperrsicht sind vom Potential  $\phi_s$  abhängig; damit ist auch die örtliche Verteilung der freien Ladungen eine Funktion von  $\phi_0$ .

- Im vereinfachten Modell wird die innere Diffusionsspannung der p-n-Diode vernachlässigt. Diese Spannung von einigen Zehntel Volt sorgt dafür, dass Elektronen und Löcher sich nicht per Diffusion vermischen.

Die erwähnten Unterschiede zwischen der wirklichen Anordnung und dem Modell verändern das qualitative Verhalten als Oberflächen Speicher nicht wesentlich, jedenfalls soweit es für ein grobes Verständnis der Ladungsverschiebungsvorgänge notwendig ist.

Die folgenden Eigenschaften des wirklichen Oberflächen-Speichers Fig. 1a lassen sich jedoch aus dem vereinfachten Doppel-Kondensator-Modell nicht ableiten:

– Es erscheint nicht die ganze Spannung  $U_G$  als Potentialdifferenz  $\phi'_G$  über der Ersatz-Kondensatorordnung Fig. 1c. Die Potentialdefinition ist nämlich, nachdem ein Nullpunkt festgelegt ist, nur innerhalb eines Stoffes mit gleicher Kristallstruktur (z.B. innerhalb eines einkristallinen Halbleiters) sinnvoll. Bei der Betrachtung der «Spannungsverteilung» über einer Serieschaltung verschiedener Stoffe (wie etwa der Anordnung Fig. 1a) sind an den Kontaktstellen die Unterschiede der Träger-Austrittsarbeiten sowie allfällige fixe Ladungen an den Grenzflächen zu berücksichtigen. Mit guter Näherung kann jedoch der Unterschied zwischen  $U_G$  und  $\phi'_G$  gemäss

$$\phi'_G \approx U_G - U_T \quad (2)$$

konstant gesetzt werden, wobei  $U_T$  von den kontaktierten Stoffen und der Struktur der Grenzflächen, insbesondere derjenigen zwischen Halbleiter und Isolator, abhängt.

– Das Kondensator-Ersatzmodell gilt nur für einen beschränkten Betriebsbereich, nämlich  $\phi_0 \leq 0$  (da sonst die p-n-Diode leitend ist) und  $Q_0 \geq 0$  (Oberflächenladung positiv).

– Die Potentialdifferenz  $\phi_0$  über dem Sperrsichtspeicher  $C_s$  tendiert langfristig zu Null, da der Sperrstrom der parallelgeschalteten p-n-Diode den Speicher  $C_s$  entsprechend auflädt, indem er dessen negative Ladung abbaut. Im Sinne der Fig. 1d könnte dies mit einem «Beregnen» des Behälters verglichen werden, wobei das obere Niveau allmählich auf  $\phi_0 = 0$  ansteigt. Alle anderen  $\phi_0$ -Werte ( $\phi_0 < 0$ ) können nur temporär, d.h. über beschränkte Zeit, eingenommen werden.

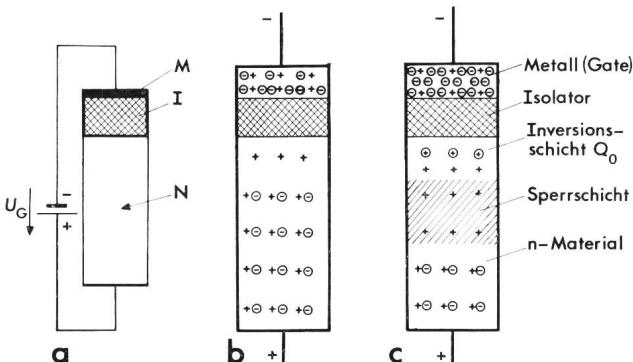

Fig. 2 Schichtfolge Metall–Isolator–n-Halbleiter als Oberflächen Speicher Typ B (MOS-Struktur)

a Struktur

b Ladungsverteilung (schematisch, verzerrte Dichteverhältnisse) bei kleiner Spannung  $U_G$ ; ( $|U_G| < |U_T|$ ). Symbole wie in Fig. 1b

c Ladungsverteilung (schematisch) bei grossem  $U_G$ ; ( $|U_G| > |U_T|$ ). Es entsteht eine Inversionsschicht mit beweglichen, positiven Ladungsträgern

Fig. 3 Vergleich zwischen dem Oberflächenpotential  $\phi_0$  einer CCD-Zelle in Funktion der Gatespannung und des Modells nach Fig. 1c in Funktion der wirksamen Kondensatorspannung  $\phi'_G$

a n-Kanal Oberflächen CCD-Zelle (Speichertyp B)

Akzeptorendichte  $N_A = 10^{14} \text{ cm}^{-3}$ , Oxyddicke 1800 Å

$Q_{0m}$  = Sättigungsladung bei  $U_G - U_T = 5 \text{ V}$  [4]

b Modell nach Fig. 1c. Interessanter Betriebsbereich

$Q_0 > 0$ ,  $\phi_0 < 0$  (schraffiert). Weil es sich hier um positive Ladungen handelt, sind die Vorzeichen von  $\phi'_G$  und  $\phi_0$  gegenüber a) umgekehrt.

Der zweite in Frage stehende Oberflächenkondensator, mit der Schichtfolge Metall–Isolator–Halbleiter (MIS oder MOS), Fig. 2, zeigt ähnliche Speichereigenschaften. Die Doppelkondensatorstruktur ist in diesem Fall vielleicht etwas weniger leicht erkennbar als in Fig. 1. Fig. 2b illustriert schematisch die Trägerdichteverteilung in einer MIS-Struktur des Anreicherungstyps bei kleinen Spannungen  $U_G$ . Die auf Grund der negativen Klemmenspannung  $U_G$  erzwungene positive Ladung an der Halbleiteroberfläche wird durch entsprechende Evakuierung der beweglichen Träger (Elektronen) erzeugt. Bei grösserer Klemmenspannung wird jedoch die nach dem Influenzgesetz auf der Halbleiterseite benötigte positive Ladung teilweise durch (bewegliche) Löcher aufgebracht; dies entspricht der aus der Theorie der MOS-Transistoren bekannten Oberflächen-Inversion. Fig. 2c zeigt die entsprechende Ladungsverteilungssituation. Sie legt als Ersatzmodell wieder die Serieschaltung zweier Kondensatoren analog Fig. 1c nahe, da die bewegliche Oberflächenladung auf der einen Seite durch den Isolator I von der Gate-Klemme, auf der andern Seite durch eine Sperrsicht (von beweglichen Trägern entblößte Zone) vom Substrat getrennt ist. Das Modell Fig. 1c bzw. die Potentialwannen-Darstellung Fig. 1d lassen sich demnach auch auf die Situation Fig. 2c übertragen. Die zur Gültigkeit dieser Modelle gemachten Bemerkungen gelten sinngemäss auch für den MIS-Kondensator. Der durch Gl. (2) formulierte Unterschied zwischen Klemmenspannung und «Kondensatorpotential» entspricht in unserer Näherung der bekannten Schwellspannung einer MOS-Struktur. Das Doppelkondensatormodell gilt nur für den Betriebsbereich jenseits des Oberflächeninversionspunktes, also für  $\phi'_G = U_G - U_T < 0$  und für positive Oberflächenladung  $Q_0 > 0$ .

Der Aufladung von  $C_s$  durch den Sperrstrom mit dem Endzustand  $\phi_0 \approx 0$  entspricht beim MOS-Kondensator die ther-

mische Neuerzeugung von Elektron-Lochpaaren im Sperrschichtbereich. Auch hier strebt die Anordnung zum Gleichgewichtszustand bei  $\Phi \rightarrow 0$ , andere Oberflächenpotentiale sind nur transient möglich. Fig. 3 illustriert die qualitativ gute Übereinstimmung zwischen dem berechneten Oberflächenpotential in einer realen MIS-Anordnung und dem Kondensatormodell Fig. 1c. Die Krümmung der Kurven in Fig. 3a ist durch die Nichtlinearität der Sperrsichtkapazität bedingt. Die in Fig. 1 besprochene Kondensatorstruktur unterscheidet sich qualitativ vom MIS- bzw. MOS-Kondensator durch die Grösse der Schwellspannung  $U_T$ , die im Fall der Fig. 1 positiv, im Fall der Fig. 2 negativ ist. In der Sprache der MOS-Transistoren ist die Struktur Fig. 1 ein Depletion- (Verarmungs-) und Fig. 2 ein Enhancement- (Anreicherungs-) Kondensator.

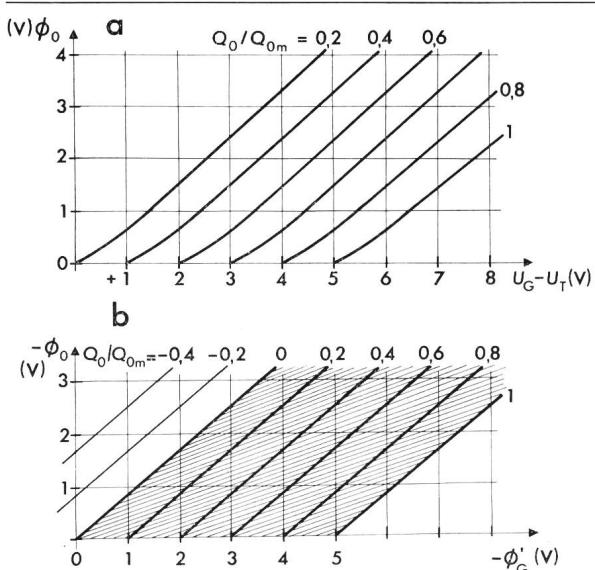

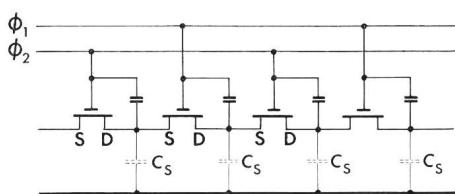

## 2.2 Der Eimerketten-Speicher

Der Aufbau eines «analogen» Schieberegisters nach dem Eimerketten-Speicherprinzip (Bucket-Brigade-Device BBD) ist in Fig. 4a gezeichnet. Man kann die Anordnung als abwechselnde Folge von Kondensatoren des Typs A (Fig. 1) und des Typs B (Fig. 2) auffassen. Fig. 4b und 4c zeigen die dieser Vorstellung entsprechende Aneinanderreihung von Potentialtöpfen, deren oberes Füllniveau gemäss Fig. 1c das Oberflächenpotential  $\Phi_0$  darstellt. Nach dieser Modellvorstellung können die Töpfe (Wannen) durch die Spannungen an den Deckplatten der Kondensatoren auf und ab bewegt werden. Die Gleichungen (1) und (2) ergeben für das Oberflächenpotential

Fig. 4 Eimerketten-Schaltung (BBD)

- a Struktur (p-Kanal-Variante)

- b Oberflächenpotential und Ladungsfluss für die aktive Taktphase  $\Phi_1$  ( $t = t_1$ )

- c Oberflächenpotential und Ladungsfluss für die darauf folgende Taktphase  $\Phi_2$  ( $t = t_2$ )

- d Zeitlicher Verlauf der Taktspannungen

$$\begin{aligned} \Phi_0 &= \frac{C_0}{C_0 + C_{sj}} (U_{\Phi i} - U_{Tj}) + \frac{Q_0}{C_0 + C_{sj}} = \\ &= K_j (U_{\Phi i} - U_{Tj}) + \frac{Q_0}{C_t} \end{aligned} \quad (3)$$

wenn als Klemmspannung  $U_G$  die jeweilige Taktspannung  $U_{\Phi i}$  und für  $C_s$  die Sperrsichtkondensatoren  $C_{sj}$  der betreffenden Kondensatorstrukturen eingesetzt werden. Dabei bedeutet der erste Summand der Gl. (3) das Potential des «Topfbodens». Gemäss Abschnitt 2.1 ist das Schwellpotential  $U_{Tj}$  in Gl. (3) beim Kondensatortyp A (Depletion) grösser als beim Kondensatortyp B (Enhancement), d.h.  $U_{TA} > U_{TB}$ . Zusammen mit dem Taktspannungswechsel  $U_{\Phi 1}$  und  $U_{\Phi 2}$  ergibt sich somit als Funktion der Längskoordinate  $x$  ein 4phasiges Spannungsprofil der «Topfböden» z.B. gemäss Fig. 4b. Die Erhöhung des Oberflächenpotentials  $\Phi_0$  durch bewegliche Oberflächenladung  $Q_0$  wird durch den zweiten Summanden in Gl. (3) erfasst. Diese Oberflächenladung läuft, als «Flüssigkeit» aufgefasst, nach der tiefsten Potentialstelle, die für das betrachtete Ladungspaket erreichbar ist. Während der aktiven Clockphase  $\Phi_1$  ( $U_{\Phi 1} < 0$ ) leeren sich demnach die beiden Töpfe R und T in die jeweils rechts liegenden Nachbarwannen S bzw. V bis auf die durch die Schwellen zurückgehaltenen Restladungen  $Q_B$  (Fig. 4b). Damit wandern bei jeder Takt-Halbphase die Ladungspakete um eine Stelle nach rechts, z.B. die Ladung  $\Delta Q_1$  vom Speicher R in den Speicher S. In der nächsten Takt-Halbwelle ( $\Phi_2$  aktiv,  $U_{\Phi 2} < 0$ ) verschiebt sich dieses Ladungspaket um eine weitere Stelle nach rechts, (Fig. 4c) usw. Pro gespeicherten Abtastwert sind zwei Potentialtöpfe notwendig, denn ein Topf darf ja nicht gleichzeitig gefüllt und geleert werden. Die Eimerkettenschaltung wird in der Literatur oft als Kaskade von MOS-Transistoren mit vergrösserten Gate-Drain-Kapazitäten beschrieben. Im betreffenden Ersatzschema Fig. 5 sind diese durch Überlappung der Gate-Elektroden über die Drainzonen gebildeten Speicher als diskrete Kondensatoren eingezeichnet.

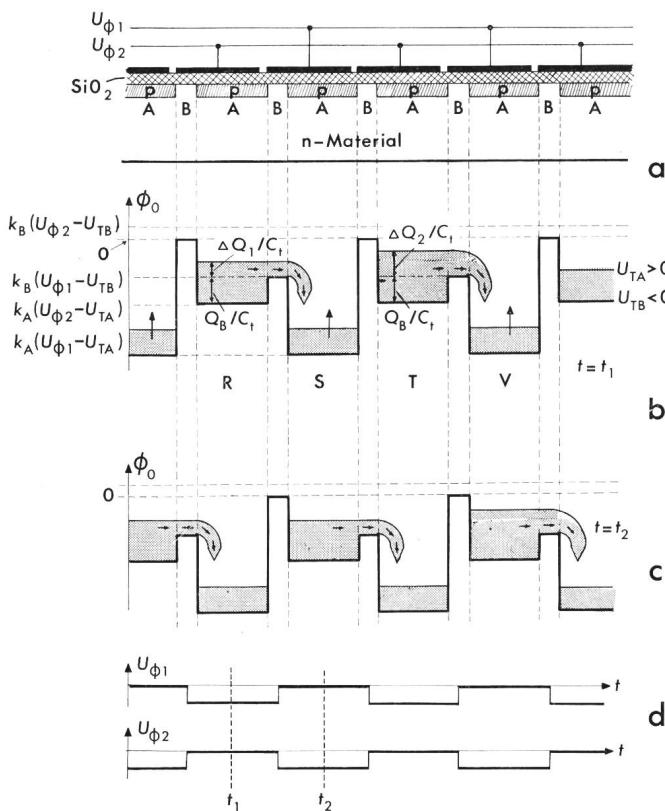

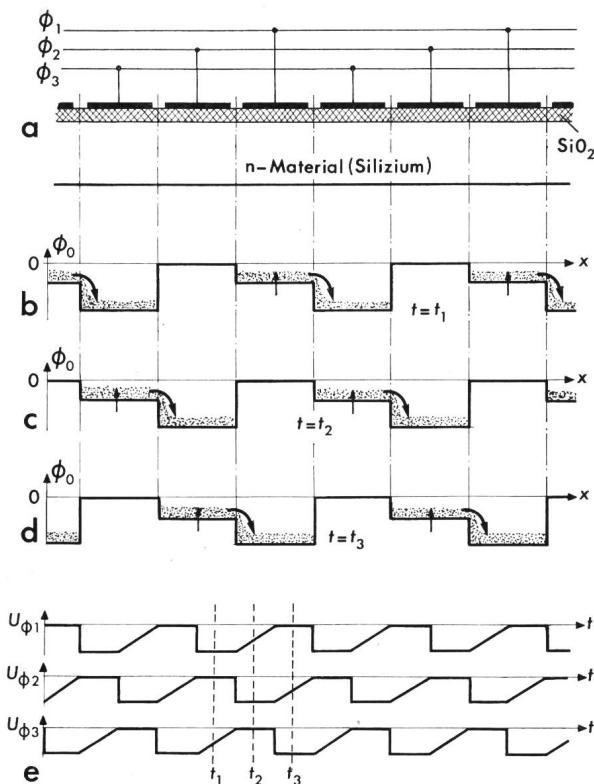

## 2.3 Die ladungsgekoppelte Kette (Charge Coupled Device, CCD)

Das Prinzip der ladungsgekoppelten Kette (CCD) wird im folgenden anhand der dreiphasigen Speicherkette illustriert. Es handelt sich dabei um eine Aneinanderreihung von MOS-Oberflächenkondensatoren des Typs B (Fig. 6a). Diese werden alternierend mit 3 Taktspannungen gemäss Fig. 6e angesteuert. Die Fig. 6b, c, d zeigen drei Momentaufnahmen des Oberflächenspannungsverlaufes zu den in Fig. 6e eingetragenen Zeiten  $t_1, t_2, t_3$ . Durch die besondere Wahl der Taktspannungsformen Fig. 6e wird die Fortleitung der in den Töpfen gespei-

Fig. 5 Eimerketten-Register nach Fig. 4a als Kette von MOS-Transistoren und Kondensatoren

(S = Source, D = Drain). Die Substratkondensatoren  $C_s$  werden in den meisten Schematas nicht eingezeichnet

cherten Ladungen nach rechts gewährleistet, indem im Dreierrhythmus einer der Töpfe allmählich angehoben wird, während die beiden Nachbarn in den Extremstellungen stehen. Im Unterschied zum in Fig. 4 dargestellten BBD-Register werden dabei die Wannen jeweils komplett entleert.

Damit zwischen den einzelnen Wannen keine Potentialwelle entstehen, müssen die Spalte zwischen den Kondensatorplatten ausserordentlich schmal gehalten werden (1...3  $\mu\text{m}$ ), was technologisch grosse Anforderungen stellt. Um das korrekte Fliessen der Ladung in einer Richtung zu gewährleisten, sind pro gespeichertem Ladungspaket drei Wannen notwendig.

Anstelle der Dreiphasenanordnung sind auch zweiphasige Ketten mit besonders strukturierten Elektroden (verschiedene Dielektrikumsdicken) entwickelt worden.

Schwierigkeiten mit den Haftstellen an der Kristalloberfläche und den relativ geringen lateralen Transportgeschwindigkeiten der Träger führten auf die Idee, den Ladungstransport von der Oberfläche ins Innere des Kristalls zu verlegen. Dazu muss das Potentialminimum (in der Richtung senkrecht zur Oberfläche betrachtet) von der Oberfläche, wo es sich bei der gewöhnlichen MOS-Struktur Fig. 2 befindet, ins Innere des Kristalls verlegt werden, was durch besondere leitfähigkeitsspezifische Strukturierung der Oberflächenschicht erreicht werden kann. Man spricht dann von sog. «buried channel CCD's» (BCCCD) im Gegensatz zu den «surface channel CCD's» (SCCCD). Man erkauft sich die Freiheit von Oberflächeneffekten sowie das bessere Frequenzverhalten beim BCCCD mit einem viel kleineren Maximalwert des transportierbaren Ladungspakets und einer dadurch bedingten schwierigeren Schaltungstechnik.

Fig. 6 3phasige, ladungsgekoppelte Speicherkette (CCD)

a Struktur (p-Kanal)

b, c, d Oberflächenpotentialprofile und Ladungsfluss in den Zeitmomenten  $t_1$ ,  $t_2$ ,  $t_3$  nach Fig. 6e

e Zeitlicher Verlauf der Taktspannungen

## 2.4 Ein- und Auskopplung der Ladungen

### Ladungs-Einspeisung

Normalerweise wird die Ladung in eine Verschiebekette via eine spezielle p-n-Diode injiziert. Dies ist bei der Eimerketten schaltung beinahe eine Selbstverständlichkeit; im MOS-Transistor Ersatzbild dieser Schaltung (Fig. 5) ist dies einfach die erste Source-Diode (S) der Kette, die galvanisch mit der Signalquelle plus einer allfälligen Vorspannung verbunden betrieben wird. Diese Spannung wird durch den ersten MOS-Transistor schalter auf einen Kondensator übertragen, der als Ladungsquelle der Kette dient.

Die Injektion von Trägern aus einer p-n-Diode kann auch beim ladungsgekoppelten Element (CCD) verwendet werden. Diese Diode wird dabei als Source eines MOS-Transistors auf gefasst. Das Potential eines anschliessenden Steuergates bestimmt, wieviel Ladung zur ersten Potentialwanne der Schiebekette, die wie eine MOS-Drainzone wirkt, gelangen kann.

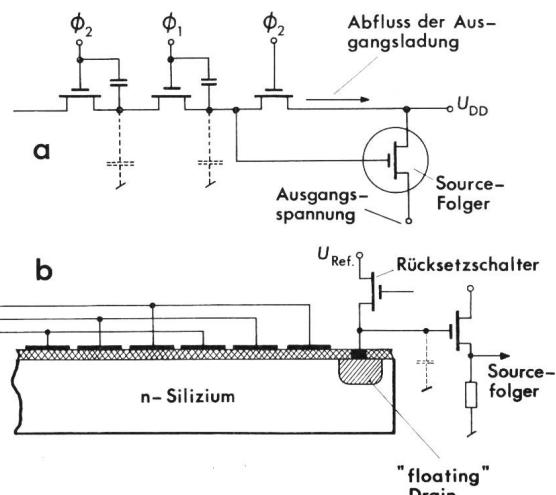

### Ladungsdetektion

Im Fall der BBD-Ketten ist die Ausgangsschaltung, d. h. die Umwandlung der Ladungspakete in eine proportionale Spannung, relativ einfach. Die Ladung des letzten Kettengliedes wird nach einer Senke  $U_{DD}$  abgesogen und am letzten Kettenglied ein MOS-Source-Folger angeschlossen (Fig. 7a). Solche Ausgangsstufen werden meistens als Gegentaktpaar eingesetzt, um die Taktspannungsanteile im Ausgangssignal zu eliminieren.

Bei der CCD-Kette wird die am Ausgang ankommende Ladung meist zunächst auf einer potentialmäßig schwelbenden (floating) p-Zone gespeichert, bevor sie einer Senke zugeführt

Fig. 7 a) Ausgangsschaltung eines BBD-Registers (Eintaktvariante) und b) CCD-Ausgangsstufe (ladungszerstörend) für die Umwandlung der Ladungspakete in eine Spannung

wird (Fig. 7b). Die an diesem sog. «floating drain» entstehende Spannung wird z. B. über einen Source-Folger ausgekoppelt. Da jedoch das Potential dieser Zone entgegen der Schaltung Fig. 7a nicht definiert ist (fehlende kapazitive Überdeckung), muss die «floatende» p-Zone vor jedem neu ankommenden Ladungspaket mit einem Schalttransistor auf ein Referenzpotential zurückgesetzt werden.

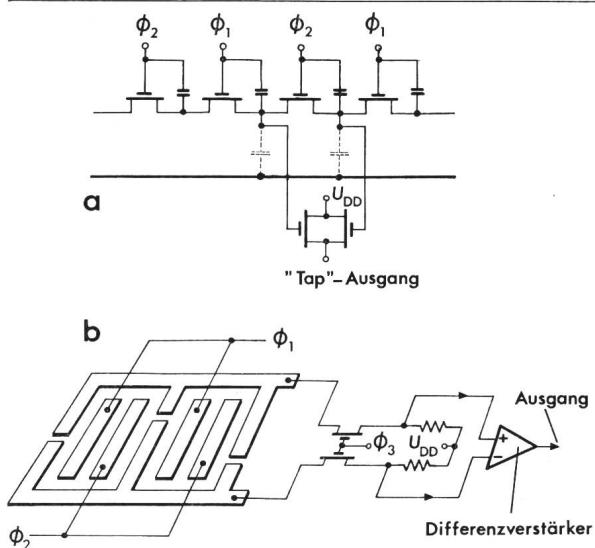

Bei den durch Fig. 7 illustrierten Auskopplungsmethoden wird die detektierte Ladung zerstört. Bei zahlreichen Anwen-

dungen ist jedoch das «Auslesen» einer zur Ladung proportionalen Spannung von einem «Abgriff» in der Kette erwünscht, ohne dabei die Weiterverschiebung der Ladung zu den nachfolgenden Gliedern zu verschlechtern. Wieder ist dieses Problem beim BBD-Register etwas einfacher zu lösen als bei der CCD-Variante. An die bei jeder BBD-Zelle vorhandene p-Zone kann gleich wie bei der Ausgangsstufe ein «Source-Folger» angeschlossen werden, ohne dabei den Ladungstransfer zum nächsten Eimer wesentlich zu verschlechtern. Fig. 8a zeigt eine solche Anzapfschaltung, die das Signal zur Unterdrückung der Taktspannung von zwei aufeinanderfolgenden Elementarzellen bezieht.

Bei der CCD-Kette ist die zerstörungsfreie Auskopplung bedeutend umständlicher. Man benutzt dabei die Tatsache, dass das Spiegelbild der unter den Elektroden verschobenen Ladung in den Taktzuführungsleitungen fließt und dort durch geeignete Schaltungen detektiert werden kann. Diese Technik wird in Fig. 8b am Beispiel der sog. «Split-Elektroden» demonstriert [5; 6]. Solche Anordnungen werden gebraucht, wenn das Signal längs der Verzögerungskette an verschiedenen Stellen abgegriffen und gewichtet addiert werden soll. Wie aus Fig. 8b ersichtlich, sind hier die zur Taktpause  $\phi_3$  gehörenden Elektroden zweigeteilt, wobei das Teilverhältnis den Gewichtsfaktoren entsprechend von Speicherplatz zu Speicherplatz variiert. Der Takt wird kapazitiv über MOS-Transistoren zugeführt und die in die beiden Teilelektroden fließende Ladung differentiell gemessen. Das Teilverhältnis der Elektroden legt das relative Gewicht der betreffenden Anzapfung fest, wobei positive und negative Gewichte realisiert werden können.

### 3. Charakteristische Eigenschaften der Ladungsverschiebeelemente

#### 3.1 Übertragungswirkungsgrad

Das wesentliche Entwurfsziel für Ladungsverschiebelemente ist die integrale Erhaltung der Ladungspakete während des Schiebevorgangs. Bei realen Schaltelementen ist die Verschiebung der Ladung von einer Wanne zur nächsten niemals komplett. Da die daran beteiligten Ladungstransportprozesse Zeit benötigen, ist zumindest bei höheren Taktfrequenzen damit zu rechnen, dass ein Teil der zum Transfer bestimmten Ladung sich am Ende der Taktpause noch unter der die Ladung abgebenden Elektrode befindet. Dieser Effekt ist kumulativ, und die Ladungspakete werden nach dem Durchlauf durch längere Ketten von Potentialwannen verschmiert.

Diese Verzerrung des Signals kann rechnerisch erfasst werden, wenn man annimmt, dass beim Transfer jeweils ein fixer Bruchteil der zu übertragenden Ladung zurückbleibt. Man bezeichnet das betreffende Verhältnis als Verlustfaktor  $\varepsilon$  (transfer inefficiency)

$$\varepsilon = \frac{\text{zurückbleibende Ladung}}{\text{verschobene Ladung}} \quad (4)$$

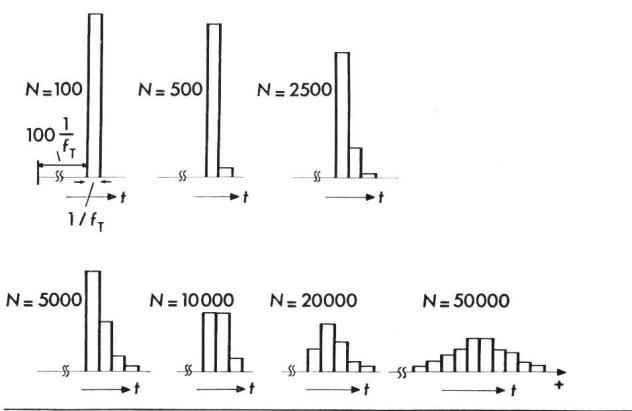

Man findet gemäß [7] als Antwort auf einen in die erste Zelle eingebrachten Einheitsimpuls nach  $n$  Schiebeträgen die folgende Ladungsverteilung über die Zellen

$$Q(i, n) = \frac{n!}{(n-i)! i!} (1-\varepsilon)^i \varepsilon^{n-i} \quad (5)$$

wobei  $i$  die betrachtete Zellenummer bezeichnet. Daraus lässt sich die «Stossantwort» einer  $N$ -stufigen Kette bestimmen. Sie

Fig. 8 a) Anzapfschaltung (Tap) an einer BBD-Verzögerungsleitung und b) Split-Elektroden Version der Floating-Gate-Technik für die Anzapfung von CCD-Zellen (dreiphasige CCD-Speicherzellen) Die auf den geteilten Elektroden in b) influenzierte Ladung wird differentiell gemessen und addiert bei gleichzeitiger Speisung aus  $\phi_3$  [6]

ist in Fig. 9 für einige Kombinationen  $\varepsilon \cdot N$  dargestellt. Fig. 9 bestätigt, dass, wie in [7] angegeben,  $\varepsilon \cdot N$  in erster Näherung die Signalverfälschung bestimmt, und dass für eine gute Übertragung

$$\varepsilon N \ll 1 \quad (6)$$

eingehalten werden muss.

Die Diskussion der Frequenzabhängigkeit von  $\varepsilon$  setzt detaillierte Kenntnisse über die Ladungstransportprozesse voraus [5; 8]. Bei ladungsgekoppelten Elementen mit vergrabenem Kanal kann eine grösere Horizontalkomponente des treibenden Feldes und damit eine höhere Grenzfrequenz erreicht werden als bei den Oberflächenkanal-Elementen.

Der Verlustfaktor  $\varepsilon$  fällt auch bei niedrigen Taktfrequenzen nicht unter einen gewissen Minimalwert. Verschiedene Gründe konstruktiver und materialtechnologischer Natur sind für diesen verbleibenden Rest zurückbehaltener Ladung verantwortlich [9]. Einer dieser Gründe ist das sog. «trapping» der Ladungsträger, das vor allem an Halbleiteroberflächen ausgeprägt ist. Dabei bleiben ursprünglich «freie» Ladungsträger beim Verschieben in sog. Haftstellen (traps) gefangen und

Fig. 9 Impulsantwort einer  $N$ -stufigen Verzögerungskette

$\varepsilon = 10^{-4}$  Verlustfaktor

$f_T$  Taktfrequenz

werden erst nach einer Verweilzeit wieder zur Leitung freigegeben. Sie tragen damit zu nachfolgenden Ladungspaketen bei. Dieser Effekt kann wesentlich reduziert werden, wenn man immer eine gewisse Restladung durch die Speicherkette schiebt (sog. «fat zero» Betrieb). Es ist nämlich so, dass der Frontimpuls eines Impulspaketes, das durch Wannen läuft, die längere Zeit leer waren, durch diese Haftstellen grössere Ladungsverluste erleidet als die nachfolgenden Impulse. Diese dem Frontimpuls entzogene Ladung ist offenbar nötig, um die leeren Haftstellen wieder aufzufüllen. Die Situation gleicht der Haftschicht einer Flüssigkeit auf einer Oberfläche, die bei längerem Nichtgebrauch austrocknet und dann wieder befeuchtet werden muss. Elemente mit vergrabenem Kanal zeigen dieses Haftstellenproblem im allgemeinen weniger. Der Betrieb mit Restladung verkleinert den nutzbaren Dynamikbereich.

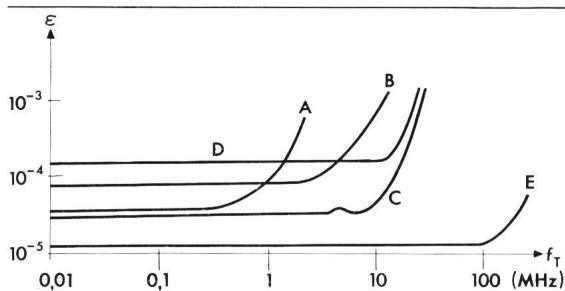

Kleine Verlustfaktoren  $\varepsilon$  sind vor allem dann schwer zu erreichen, wenn nach dem Transfer des Paketes  $\Delta Q$  eine schwellenbedingte Restladung im Topf, von dem der Transfer ausgeht, zurückbleibt, eine Situation, wie sie beim Eimerketten-speicher immer auftritt (Fig. 4). Es ist schwierig, die Höhe dieser Schwelle vom Füllzustand des nachfolgenden Topfes völlig unabhängig zu machen, wie das im vereinfachten Modell der Fig. 4 angenommen wird. Praktische BBD-Ketten verwenden deshalb immer die sog. Tetrodenstruktur mit fix polarisierten Puffertransistoren zwischen den Ladungsspeichern [10]. Fig. 10 zeigt einige Frequenzgangkurven des Verlustfaktors verschiedener Schaltungskonzepte. Man entnimmt daraus etwa gleiche Verlustfaktoren für Eimerketten- und ladungsgekoppelte Oberflächenspeicher bei tiefen Frequenzen, jedoch bedeutend bessere Frequenzgänge bei den CCD's. Die besten Ergebnisse bezüglich Verlustfaktor und Frequenzgang werden mit vergrabenen Kanälen erreicht.

### 3.2 Maximalwert der verschiebbaren Ladungspakete

Die Grösse der verschiebbaren Ladungspakete wird gemäss Modell Fig. 1c durch das Oberflächenpotential  $\phi_0 = 0$  begrenzt. Zusammen mit den charakteristischen Daten der Speicheranordnung ( $U_G$ ,  $C_0$ ,  $C_s$ ,  $U_T$ ) lässt sich dann der Maximalwert der verschiebbaren Ladungspakete errechnen. Er ist bei BBD-Registern am grössten, gefolgt von SCCC und BCCCD's. Die die untere Grenze des Dynamikbereichs bestimmende Rauschspannung ist bei den 3 Typen allerdings auch verschieden.

### 3.3 Untere Betriebsfrequenz

Die bekannte Tatsache, dass die Verschiebefrequenz der Ladungspakete nicht unter ein bestimmtes Minimum absinken darf, ist auf Grund der oben diskutierten Wirkungsweise der Ladungspakete leicht verständlich. Die im Abschnitt 2.1 beschriebenen Oberflächenkondensatoren haben alle die Tendenz, sich von selbst mit Ladung aufzufüllen; die Quellen dieser Aufladeströme sind beim Typ A der Sperrstrom der betreffenden p-n-Diode, beim Typ B die thermische Trägerpaarerzeugung in der unter der Oberflächenspeicherladung entstehenden Sperrsicht. Im Bild der mit Flüssigkeit gefüllten Potentialwannen könnte diese dauernde Trägerzufluss etwa mit einem Regen verglichen werden, der in die offenen Töpfe fällt und sie allmählich auffüllt. Auf Grund dieser anschaulichen Vorstellung ist auch die Auswirkung dieses «Regens» auf das Betriebsverhalten leicht abzuschätzen. Er bewirkt beim Verzögerungselement eine mit fortschreitender

Fig. 10 Verlustfaktor  $\varepsilon$  verschiedener Ladungspakete als Funktion der Taktfrequenz (Beispiele)

- A, B Eimerkettenspeicher [10]

- C 3 Phasen Oberflächen CCD [5]

- D 2 Phasen Oberflächen CCD [5]

- E CCD mit vergrabener Schicht (geschätzte Daten)

Verschiebung zunehmende Grundladung in den Töpfen, die eine Einschränkung der nutzbaren Signaldynamik bewirkt. Einige Abhilfe bieten ein möglichst schnelles Verschieben der Ladung oder eine Verminderung der Trägererzeugung, d.h. eine grosse Taktfrequenz oder eine tiefe Betriebstemperatur.

### 4. Photosensitive Ladungspakete

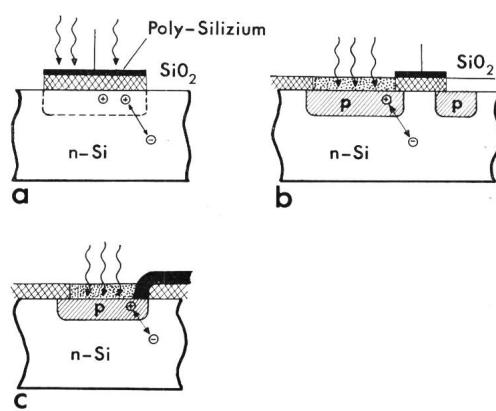

Die beiden im Abschnitt 2.1 beschriebenen Oberflächenkondensatoren können auch als photoempfindliche Zellen eingesetzt werden [11]. Die durch Lichtquanten im Silizium erzeugten Elektron-Lochpaare werden durch die Sperrsichtfelder der Kondensatoren  $C_s$  getrennt und laden die Oberflächenkondensatoren auf. Der Photostrom kann als ein durch das Licht intensitätsgesteuerter Regen in die Potentialwannen aufgefasst werden. Beim als Photodetektor eingesetzten MOS-Kondensator (Typ B) in Fig. 11a muss die leitende Deckelektrode lichtdurchlässig gebaut werden (z.B. aus Polysilizium). Beim p-n-Kondensator wird meistens auf die Deckelektrode verzichtet; dieser kann über einen MOS-Transistor-Schalter entladen werden (Fig. 11b), aber es ist auch möglich, die obere Schicht des p-n-Übergangs metallisch zu kontaktieren (Fig. 11c). Bei allen besprochenen Strukturen besteht auch die Möglichkeit, das Licht von hinten einzustrahlen, allerdings müsste dann das betreffende Substratplättchen sehr dünn sein. Die in Fig. 11 gezeichneten Zellen werden normalerweise integrierend betrieben, d.h. die entstehenden Ladungsträger werden während einer bestimmten Zeit gesammelt und hinterher die auf der Kapazität integrierte Ladung ausgelesen.

Fig. 11 Photosensitive Si-Zellen

- a MOS Kondensator

- b p-n-Diode mit MOS Ausleseschalter

- c p-n-Diode metallisch kontaktiert

Mit lichtempfindlichen CCD-Ketten lassen sich grundsätzlich einfache, zeilenartige Photosensoren bauen. Das einfallende Licht setzt in den einzelnen Potentialwannen Ladungsträger frei, die während der Integrationszeit eingesammelt werden. Anschliessend werden die Taktspannungen angelegt und die Ladungen entlang der Kette zum Ausgang transportiert. Dies muss relativ schnell vor sich gehen, da das Licht auch während des Ausschiebeprozesses weiterhin Träger erzeugt, was zu einer Verschmierung des Bildes führt. Eine alternative Lösung verwendet zum Integrieren und Ausschieben getrennte Ketten: Aus der lichtempfindlichen Kette werden die integrierten Ladungen in ein parallel angeordnetes CCD-Register transferiert und dann in diesem ausgeschoben, während die Sensorkette wieder Ladungen integriert. Diese Technik erlaubt auch die Realisierung zweidimensionaler Sensoren; solche Sensoren sind bis  $512 \times 320$  Bildpunkte gebaut worden.

## 5. Einige Anwendungen von Ladungsverschiebeelementen

Die naheliegendste Anwendung der Ladungsverschiebeelemente ist die Temporärspeicherung und Verzögerung «analoger» Signale. Die ursprünglich zeitkontinuierlichen Signale werden dabei «abgetastet», was die Einhaltung des Sampling Theorems (Abtastfrequenz  $f_T > 2 \times$  höchste Informationsfrequenz  $B$ ) erfordert, wenn man störende Spektralanteile am Ausgang vermeiden will. Man kann zeigen, dass bei idealer Ladungsübertragung ( $\varepsilon = 0$ ) durch die Stufenzahl  $N$  der Kette eine obere Grenze für das Produkt aus Signalbandbreite  $B \times$  Verzögerung  $\tau$

$$B\tau < \frac{1}{2r} N \quad (7)$$

festgelegt ist, wobei  $r$  die Anzahl der pro Abtastwert benötigten Elementarspeicher bezeichnet (für BBD,  $r = 2$ ). Bei endlichem Verlustfaktor  $\varepsilon$  wird das erreichbare  $B\tau$ -Produkt bei grossen  $N$  als Folge der beschriebenen Signalverschmierung durch zurückbleibende Ladung verkleinert. Dieser Effekt wird wesentlich, wenn die akkumulierten Verluste  $N\varepsilon$  über die Kette die Größenordnung 1 erreichen. Bei den heute realisierbaren  $\varepsilon$ -Werten ( $\varepsilon \approx 10^{-4}$ ) wird demnach die Störung bei Kettenlängen  $N \approx 1000$  spürbar. Analoge Verzögerungsketten mit CTD-Elementen lassen sich unter anderem in der Akustik der Ultraschall- und Radartechnik anwenden (z. B. Festzielunterdrückung in Radaranlagen).

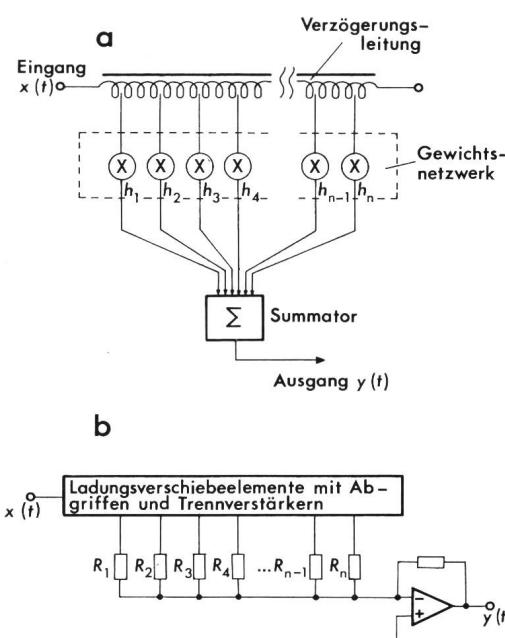

Ladungsverschiebungsketten mit Abgriffen ermöglichen eine einfache Realisierung von *Filtern für abgetastete Signale*. Dieses Gebiet war bisher vor allem der Digitaltechnik vorbehalten. Das dabei verwendete Schema – Abtastung–A/D Wandlung–digitale Verarbeitung–D/A Wandlung – ist als sogenanntes «Digitalfilter» wohl bekannt und theoretisch eingehend untersucht worden. Ladungsverschiebeelemente mit Abgriffen längs der Kette ermöglichen eine direktere Realisierung von Abtastfiltern für amplitudenkontinuierliche Signale, wobei digitale Rechenkreise, A/D- und D/A-Wandler entfallen. Diese Anwendung von CCD's und BBD's hat bisher vor allem für die Klasse der Transversalfilter (*finite impulse response filter, FIR*) Bedeutung erlangt, weil hier die Toleranzanforderungen an die Komponenten geringer sind als bei den rekursiven (rückgekoppelten) Filtern. Ein Transversalfilter wird gemäss Fig. 12a aus einer Verzögerungsleitung, einem Gewichtsnetzwerk und einem Summierer aufgebaut. Dabei kann das Gewichtsnetzwerk fix

oder programmierbar sein. Bekanntlich lässt sich das Ausgangssignal eines Filters für zeit- und amplitudenkontinuierliche Signale im Zeitbereich durch das sogenannte Faltungintegral

$$y(t) = \int_{-\infty}^{+\infty} h(\tau) x(t - \tau) d\tau \quad (8)$$

beschreiben, wobei  $x(t)$  das Eingangssignal und  $h(t)$  die sogenannte Impulsantwort des Filters bezeichnen. Die von der Anordnung Fig. 12a durchgeführte Operation entspricht nun gerade einer diskreten Faltungssumme im Sinne der Gl. (8) (Ersatz des Integrals durch Summe), wenn die Gewichtskoeffizienten  $h_i$  den Abtastwerten der Impulsantwort entsprechen. Selbstverständlich darf die Länge des Signals  $x(t)$  nicht grösser als  $nT$  sein (Länge des Transversalfilters).

Analoge Verzögerungsleitungen mit Abgriffen und nachgeschalteten Trennverstärkern (z. B. BBD) ermöglichen eine besonders einfache Filterrealisation. Zusammen mit Gewichtswiderständen und einem Summierverstärker kann das Transversalfilterschema mit relativ wenigen Komponenten verwirklicht werden (Fig. 12b).

Die Schaltung mit gewichteten Abgriffen aus einer CTD-Kette und nachfolgender Summation kann auch voll integriert auf dem Schieberegisterchip realisiert werden. Dazu eignet sich vor allem die in Fig. 8b gezeigte Split-Elektrodentechnik von CCD-Ketten [12].

Als letzte Anwendungsklasse seien noch die *Digitalspeicher* erwähnt. In Anlehnung an das Konzept der dynamischen digitalen Schieberegister ist es naheliegend, Ladungsverschiebeelemente als serielle digitale Speicher einzusetzen. Dabei sind wegen der kleineren physikalischen Abmessungen für diese Anwendung vor allem die CCD-Register interessant. Die Anforderungen an die Übertragungseigenschaften solcher Register sind natürlich geringer als im Falle der «analogen» Verzögerungsketten, weil am Ausgang nur zwei Zustände sicher unterschieden werden müssen und eine Signalregeneration möglich

Fig. 12 a) Prinzipieller Aufbau eines Transversalfilters

b) Realisierung des Transversalfilters aus einem Ladungsverschiebeelement, Gewichtswiderständen und einem Summationsverstärker

ist. Man kann diese Erleichterung zugunsten der Kettenlänge, der Betriebsfrequenz oder zur Vereinfachung der Herstellungstechnologie ausnützen; zu lange Ketten sind ohnehin aus Gründen der Zugriffszeit nicht brauchbar. Die Zugriffszeit kann durch Multiplexbetrieb (Parallelschaltung) und spezielle Serie/Parallel-Anordnung verkleinert werden, so dass nicht das Durchtakten aller Bits abgewartet werden muss, um im ungünstigsten Fall die gespeicherte Information zu erreichen [18]. Man hofft, mit CCD-Digitalspeichern die Lücke zwischen billigen Plattenspeichern (Floppy Disks), Trommelspeichern und den Random-Access-Speichern auf wirtschaftliche Weise überbrücken zu können. Es sind zurzeit CCD-Speicherchips bis 16 kbit Kapazität pro Chip mit einer Zugriffszeit  $< 100 \mu\text{s}$  erhältlich. Chips mit 64 kbit Speicherkapazität sind angekündigt.

Die Realisierung der Ladungsverschiebeelemente hat technologisch mehr Mühe bereitet als auf Grund optimistischer Prognosen anfangs der 70er Jahre angenommen wurde. Dies gilt insbesondere für die ladungsgekoppelten Elemente, die gegenüber der üblichen MOS-Technologie höhere Ansprüche stellen. Aber auch Eimerkettenschaltungen, die mit der klassischen MOS-Technik eine grössere Verwandtschaft haben als die CCD's, konnten erst in letzter Zeit, dank der Weiterentwicklung der MOS-Technologie mit technisch befriedigenden Spezifikationen realisiert werden.

Unabhängig von der Frage, ob CCD's und BBD's in der zukünftigen Schaltungstechnik eine bedeutende Rolle spielen werden oder nicht, hat die Erweiterung der Theorie der MOS-Strukturen, die zur Beschreibung der Wirkungsweise von

Ladungsverschiebeelementen notwendig war, viele neue Einsichten gebracht, die andere Bauelemente, wie Ladungs-Injektions-Photosensoren, Ladungspumpen und nicht zuletzt die Entwicklung der 1-Transistor Random-Access-Memory-Zellen, ganz wesentlich gefördert haben.

#### Literatur

- [1] K. Schlesinger: Electron tube circuits. US Patent No. 2403955, 1943/1946.

- [2] F. L. J. Sangster: Integrated MOS and bipolar analog delay lines using bucket-brigade capacitor storage. IEEE International Solid-State Circuits Conference 1970, Digest of Technical Papers, (1970), p. 74...75.

- [3] W. S. Boyle and G. E. Smith: Charge coupled semiconductor devices. Bell Syst. Techn. J. 49(1970)4, p. 587...593.

- [4] D. F. Barbe: Charge integration and storage in MOS-Photosensors. Presented at the NATO Advanced Study Institute on Solid Imaging, Louvain, September 1975.

- [5] C. H. Sequin and M. F. Tompsett: Charge transfer devices. New York, Academic Press, 1975.

- [6] W. F. Kosonocky and J. E. Carnes: Basic concepts of charge-coupled devices. RCA Review 36(1975)3, p. 566...593.

- [7] W. B. Joyce and W. J. Bertram: Linearized dispersion relation and Green's function for discrete-charge-transfer devices with incomplete transfer. Bell Syst. Techn. J. 50(1971)6, p. 1741...1754.

- [8] J. E. Carnes, W. F. Kosonocky and E. G. Ramberg: Free charge transfer in charge-coupled devices. Trans. IEEE ED 19(1972)6, p. 798...808.

- [9] C. N. Berglund and K. K. Thornber: Incomplete transfer in charge-transfer devices. IEEE Journal of Solid-State Circuits 8(1973)2, p. 108...116.

- [10] R. R. Buss and G. P. Weckler: Bucket brigade devices. Technical Note No. 107, Reticon Corporation, Sunnyvale/California, 1976.

- [11] D. F. Barbe: Imaging devices using the charge-coupled concept. Proc. IEEE 63(1975)1, p. 38...67.

- [12] O. Müller a. o.: Practical application of CCD-transversal filters in communication systems. Proc. of the 29th Annual Symposium on Frequency Control, Atlantic City, May 1975, p. 88...97.

- [13] G. Panigrahi: Charge-coupled memories for computer systems. Computer (IEEE) 9(1976)4, p. 33...42.

#### Adresse des Autors

Prof. Dr. Walter Guggenbühl, Institut für Elektronik,

Eidg. Technische Hochschule, 8092 Zürich.

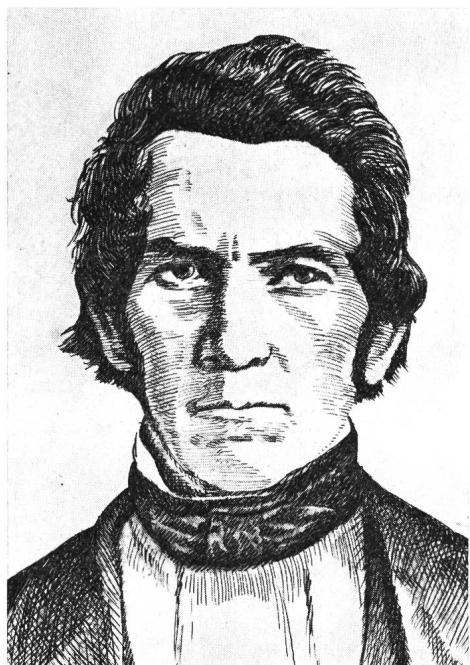

## Thomas Davenport 1802–1851

Library of Congress, Washington DC

Thomas Davenport war das achte von elf Kindern. Da sein Vater früh starb, durfte er nur wenige Jahre eine Schule besuchen, weil er mitverdienen musste. Bei einem Schmied machte er eine Lehre, eröffnete bald eine eigene Schmiede und war recht erfolgreich, konnte er sich doch schon 1827 anlässlich seiner Heirat ein geräumiges Backsteinhaus bauen.

Um 1831 sprach man in der Heimat Davenports, in Vermont, von grossen Magneten – Joseph Henry in Albany baute solche. Im Eisenwerk von Crown Point war auch ein solcher Magnet im Gebrauch. Als Davenport dort Eisen einkaufen wollte, bekam er ihn zu sehen und war so beeindruckt, dass er statt des Eisens einen noch vorhandenen andern Magneten erwarb. Statt weiter zu schmieden, fing er an, selber einen Magneten zu bauen. Das seidene Hochzeitskleid seiner Frau lieferte die Drahtisolation.

Aus unbekannten Gründen kam Davenport auf die Idee, Magnete als Kraftquelle zu verwenden. Mit einem Freund baute er 1834 eine kleine Maschine mit 4 Magneten, von denen zwei auf einer um eine horizontale Achse drehbaren «Speiche», die beiden andern fest montiert waren. Die vier Elektromagnete wurden über einen primitiven Kommutator miteinander verbunden. Schloss man das Ganze an eine Batterie an, so drehte sich die «Speiche» mit grosser Geschwindigkeit. Davenport hatte einen Motor gebaut.

Auf den Rat eines College-Professors und von Freunden finanziell unterstützt, machte er sich mit seiner Maschine auf nach Washington, um die Erfindung patentieren zu lassen. Unterwegs führte er den Motor überall vor, und sein Geld war aufgebraucht, bevor er am Ziel ankam. Unverrichteter Dinge musste er heimkehren. Darauf baute er weitere Motoren und schickte ein Modell ins Patentamt nach Washington. Aber er hatte Pech, denn Ende 1836 brannte das Gebäude des Patentamtes nieder, und alles wurde zerstört. Auf Grund eines weiteren Modelles erhielt er dann 1837 ein Patent.

Wenig später baute Davenport eine kleine Lokomotive und gründete in New York eine Werkstatt; aber er fand keine Abnehmer für seine Motoren. Nur die Druckmaschine, auf der eine von ihm ins Leben gerufene technische Zeitschrift gedruckt wurde, wurde von einem seiner Motoren angetrieben.

Von den vielen Enttäuschungen gebrochen, zog er sich auf eine kleine Farm zurück. Dort experimentierte er noch weiter und brachte unter anderem ein elektrisches Klavier zuwege. Aber zu jener Zeit gab es noch keine leistungsfähige und wohlfeile Elektrizitätsquelle, weshalb alle seine Bemühungen zu Misserfolgen führten.

H. Wüger