|                     |                                                                                                                                                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Bulletin des Schweizerischen Elektrotechnischen Vereins, des Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises électriques suisses |

| <b>Herausgeber:</b> | Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätsunternehmen                                                                                                                              |

| <b>Band:</b>        | 68 (1977)                                                                                                                                                                                                                 |

| <b>Heft:</b>        | 2                                                                                                                                                                                                                         |

| <b>Artikel:</b>     | Magnetische Domänenspeicher                                                                                                                                                                                               |

| <b>Autor:</b>       | Böhnlein, A.                                                                                                                                                                                                              |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-914981">https://doi.org/10.5169/seals-914981</a>                                                                                                                                   |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 12.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Magnetische DomänenSpeicher<sup>1)</sup>

Von A. Böhnlein

621.377.623.223

Magnetische Zylinderdomänen («magnetic bubbles») treten als kleine Bereiche in dünnen Schichten bestimmter magnetischer Werkstoffe auf. Durch geeignete Mikrostrukturen auf der Schicht lassen sich Schieberegister zur Speicherung digitaler Information herstellen. Die zurzeit erreichte Chipkapazität beträgt  $10^5$  bit, noch grössere Kapazitäten werden in den nächsten Jahren erwartet. Damit lassen sich serielle Speicher mit geringer Zugriffszeit, geringem Volumen und kleinem Leistungsverbrauch aufbauen, die in Konkurrenz zu den Magnetschichtspeichern treten werden. Neben der Beschreibung des Prinzips und der Aufbautechnik des Speichers wird auf die Entwicklungsprobleme, den erreichten Stand und auf die Anwendungsmöglichkeiten eingegangen.

Des bulles magnétiques se présentent sous forme de petites régions dans de minces couches de certaines matières magnétiques. Grâce à des microstructures appropriées sur la couche, on peut obtenir des registres pour la mémorisation d'informations numériques. Actuellement, la capacité d'une puce est de  $10^5$  bit, mais des capacités encore plus grandes seront bientôt possibles. Cela permet de réaliser des mémoires sérielles d'un temps d'accès très bref, d'un volume réduit et d'une faible consommation, capables de concurrencer les mémoires à couches magnétiques. Outre la description du principe et de l'établissement de la mémoire, l'auteur traite des problèmes de développement, de l'état atteint et des possibilités d'emploi.

## 1. Einleitung

Die erste Beobachtung von Zylinderdomänen wurde bereits im Jahre 1959 durch R. C. Sherwood durchgeführt [1]<sup>2)</sup>. Doch erst im Jahre 1967 erwachte das weltweite Interesse für diese Entdeckung, als A. H. Bobeck vorschlug, Zylinderdomänen zur Speicherung von digitaler Information zu verwenden [2]. Nach Erstellung der ersten Speicherstrukturen mit Schichten aus Orthoferrit ging die Entwicklung zu den magnetischen Granaten, die zur Erzielung der gewünschten hohen Speicherdichte von  $10^5 \dots 10^7$  bit/cm<sup>2</sup> geeignet sind. Die führenden Entwickler verfügen seit einigen Jahren über Speicherchips mit einer Kapazität von 10...20 kbit [3; 4]. Chips mit einer Kapazität bis zu 100 kbit [5] werden in den Entwicklungslaboren untersucht. Damit lassen sich Speicher mit einer Kapazität bis  $10^8$  bit erstellen. Die Informationsspeicherung erfolgt in Schieberegistern mit einer mittleren Zugriffszeit von 1 ms. Damit können DomänenSpeicher vor allem als Externspeicher anstelle von Festkopfplatten und Trommeln in kommerziellen Datenverarbeitungsanlagen eingesetzt werden.

## 2. Speicherprinzip

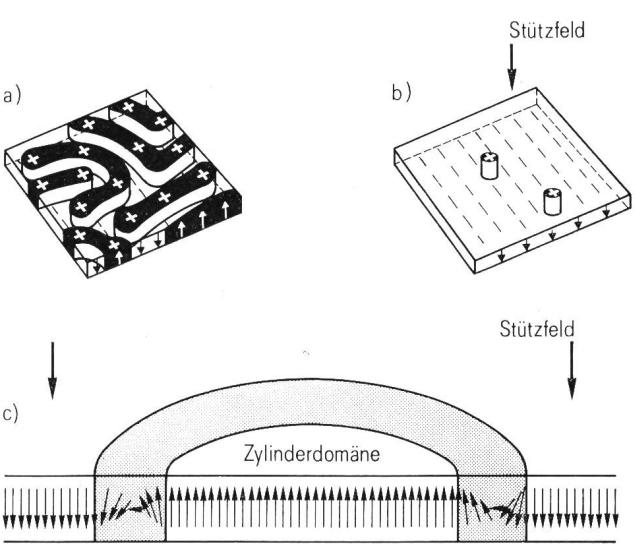

Auf einer geeigneten Trägerschicht aus nicht magnetischem Granat wird epitaktisch eine dünne Specherschicht von ca. 10 µm Dicke aus magnetischem Granat aufgebracht. Die Specherschicht besitzt eine hohe uniaxiale magnetische Anisotropie in Richtung der Schichtnormalen. Im entmagnetisierten Zustand bilden sich mäanderförmige Bereiche aus, die sich mit Hilfe des Faraday-Effektes sichtbar machen lassen (Fig. 1a). Die Magnetisierung der hellen Bereiche verläuft parallel zur Schichtnormalen nach unten, die Magnetisierung der dunklen Bereiche ist antiparallel gerichtet. Wird ein Magnetfeld mit einer Feldstärke von ca. 100 A/cm senkrecht zur Schichtnormalen und antiparallel zur Magnetisierung in den dunklen Bereichen angelegt, so ziehen sich diese entweder an den Schichtrand zurück und verschwinden, oder sie ziehen sich zu zylinderförmigen Bereichen zusammen, den sogenannten «magnetic bubbles», die in der deutschen Literatur als Zylinderdomänen oder Magnetblasen bezeichnet werden (Fig. 1b). Fig. 1c zeigt den Verlauf der Magnetisierung in der Domänenwand. Mit einer weiteren Erhöhung der Feldstärke werden die Domänen kleiner und verschwinden schliesslich schlagartig bei einem kritischen Wert, der Kollapsfeldstärke [6]. Bei einer mittleren Feldstärke des Magnetfeldes, das im folgenden

Stützfeld genannt wird, sind die Zylinderdomänen stabile Bereiche und lassen sich sehr leicht durch Gradienten des Stützfeldes in der Schichtebene fortbewegen.

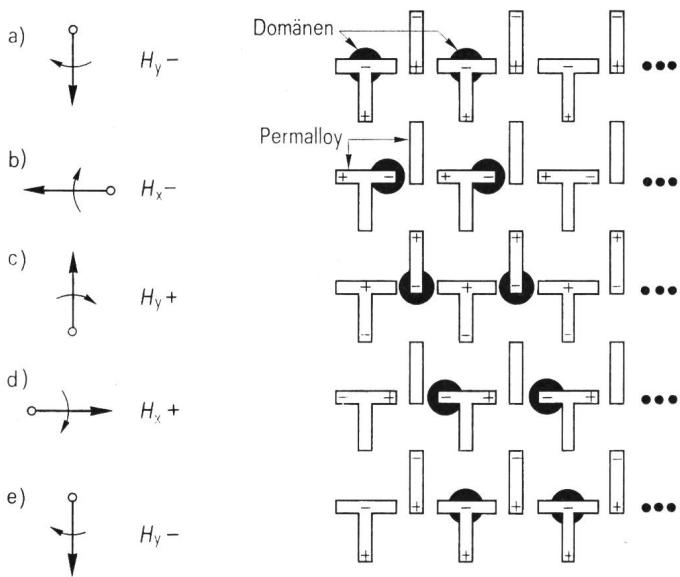

Zur Speicherung von Information werden Domänen in Schieberegistern aufbewahrt. Dabei stellt eine Domäne eine logische «1» dar, eine nicht vorhandene Domäne eine logische «0». Eine Folge aus Domänen und Nichtdomänen bildet ein Wort oder einen Block. Die Schieberegister entstehen durch Anordnung von Permalloymustern («bars») auf der Granatschicht (Fig. 2).

Durch ein in der Schichtebene rotierendes Magnetfeld mit einer Feldstärke von ca. 20 A/cm und einer Frequenz von ca. 100 kHz ändert sich die Verteilung der Magnetpole an den Permalloystrukturen ständig. Dabei laufen die Domänen mit den wandernden Minuspolen der Permalloystruktur vorwärts und legen bei jeder vollen Umdrehung des Rotationsfeldes eine Periode des Schiebekanals zurück. Für Domänen mit 5 µm Ø beträgt diese Periode etwa 20 µm. Eine Periode stellt eine Speicherzelle dar und kann eine Domäne bzw. 1 bit Information aufnehmen. Neben der T-I-Bar Anordnung wurden eine Reihe unterschiedlicher Permalloystrukturen entwickelt, von denen sich besonders die X-Bar-Anordnung [7] für den Betrieb mit hoher Rotationsfrequenz eignet.

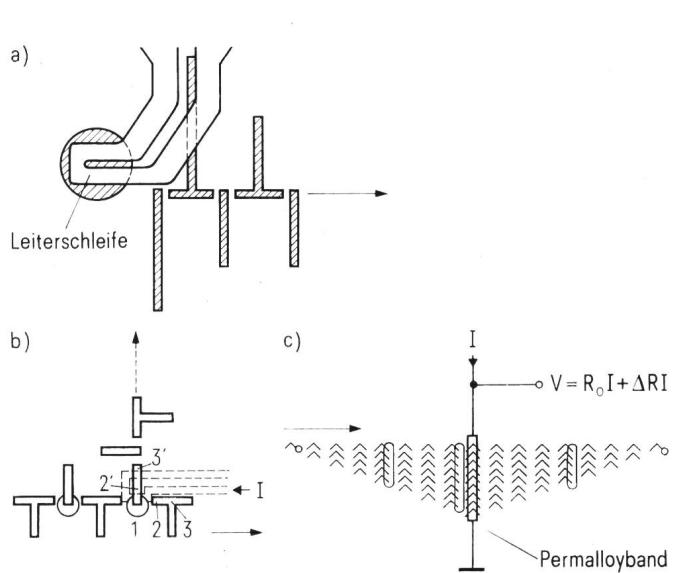

Neben der Speicherung von Information muss noch die Möglichkeit gegeben sein, Information einzuschreiben, auszulesen und zu löschen. Ein Domänengenerator besteht aus einer Leiterschleife, von der ein Schiebekanal wegführt (Fig. 3a).

Fig. 1 Streifen- (a) und Zylinderdomänen (b) mit Wandstruktur (c)

<sup>1)</sup> Vortrag, gehalten an der SEV-Informationstagung «Moderne Technologien in der Elektronik» am 11. November 1976 in Biel.

<sup>2)</sup> Siehe Literatur am Schluss des Aufsatzes.

Fig. 2 Domänentransport durch T-I-Muster aus Permalloy

Ein kurzer Stromimpuls durch die Leiterschleife (ca. 300 mA) erzeugt lokal ein hohes, dem Stützfeld entgegengesetztes Magnetfeld, in dem sich eine Domäne bildet, die unter Einwirkung des Rotationsfeldes in den Schiebekanal wandert («field nucleation» [8]). Zur Vernichtung von Domänen werden diese über eine Weiche zum Chiprand geleitet, wo sie verschwinden (Fig. 3b). Die Weiche wird durch einen Stromimpuls von ca. 100 mA betätigt. Im stromlosen Fall wandern die Domänen unbeeinflusst an der Weiche vorbei.

Der Nachweis der Domänen geschieht mit einem magnetoresistiven Detektor (Fig. 3c) [9]. Dieser besteht aus einem einfachen Permalloystreifen, der beim Vorbeilaufen, der vorher aufgeblähten Domänen seinen elektrischen Widerstand von ca.  $500 \Omega$  um etwa 2 % ändert. Zum Nachweis der Widerstandsänderung wird ein elektrischer Strom von ca. 1 mA durch den Detektor geleitet, der am Detektorwiderstand einen Spannungsabfall von 500 mV erzeugt. Unter Einwirkung einer Domäne sinkt dieser Spannungsabfall um 2 % und erzeugt ein Lesesignal von ca. 10 mV.

### 3. Organisation des Speicherchips

Mit den beschriebenen Strukturelementen lässt sich ein Speicherchip erstellen. Als einfachste Struktur bietet sich ein einziges in sich geschlossenes Schieberegister am Chip an. Mit einer Chipkapazität von  $10^5$  bit und einer Frequenz des Rotationsfeldes von 100 kHz beträgt die Umlaufzeit einer Domäne 1 s, so dass sich eine mittlere Zugriffszeit von 0,5 s ergibt.

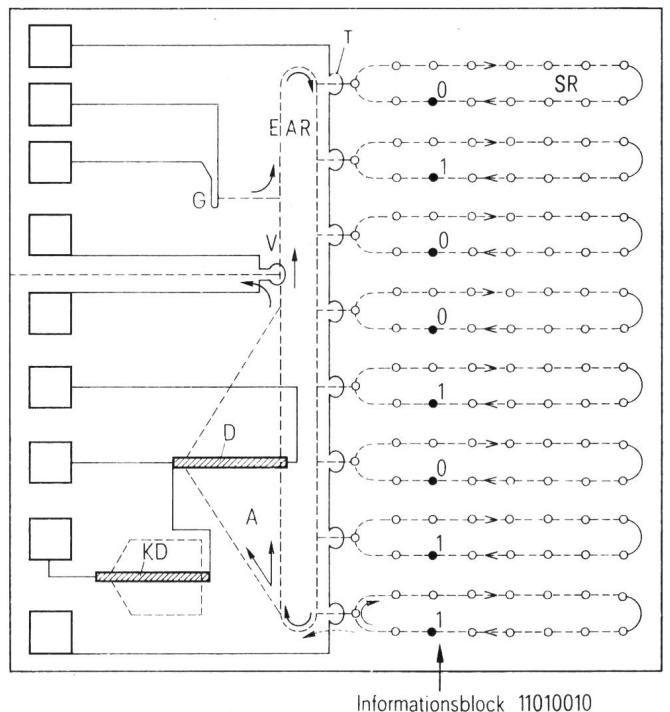

Mit Hilfe der «major-minor»-Anordnung [10] lässt sich eine wesentlich geringere Zugriffszeit erreichen, wie sie für schnelle Externspeicher gefordert wird (Fig. 4). Auf der zur Verfügung stehenden Speicherfläche sind eine grosse Zahl von kleinen Schieberegistern (SR) angeordnet, die über elektrisch ansteuerbare Tore (T) mit einem gemeinsamen Ein-/Ausgaberegister (EAR) in Verbindung stehen. Unter Einwirkung des Rotationsfeldes laufen die Domänenketten in den Schieberegistern synchron um. Alle Domänen, die zur selben Zeit identische Plätze in den Schieberegistern einnehmen, bilden einen Informationsblock. Zum Auslesen eines Blockes werden zu dem Zeitpunkt, zu dem sich seine Domänen an den Toren befinden,

Fig. 3 Generator (a), Weiche (b) und Detektor (c)

die Tore angesteuert. Dabei treten die Domänen des ausgewählten Blockes in das Ein-/Ausgaberegister über und laufen unter Einwirkung des rotierenden Feldes über die Aufblähstruktur (A) zum Detektor (D). Die Domänen werden der Reihe nach gelesen, schrumpfen anschliessend wieder auf ihre ursprüngliche Form zusammen und laufen dann solange im Ein-/Ausgaberegister weiter, bis sie wieder vor den Toren stehen. Die Domänen der nicht ausgewählten Blöcke haben inzwischen einen vollen Umlauf in den Schieberegistern ausgeführt. Eine zweite Ansteuerung der Tore transportiert die gelesenen Do-

Fig. 4 Anordnung der Strukturen am Chip

|     |                       |   |                  |

|-----|-----------------------|---|------------------|

| SR  | Schieberegister       | A | Aufblähstruktur  |

| EAR | Ein-/Ausgaberegister  | T | Tor              |

| D   | Detektor              | G | Generator        |

| KD  | Kompensationsdetektor | V | Vernichterweiche |

mänen wieder in die Schieberegister zurück, wo sie ihre alten Plätze einnehmen (nicht zerstörendes Lesen).

Zum Löschen eines Informationsblockes wird dieser ebenfalls in das Ein-/Ausgaberegister übernommen. Das Vernichtertor (V) leitet die Domänen über einen Schiebkanal zum Chiprand, wo sie verschwinden. Der freigewordene Platz in den Schieberegistern kann nun einen neuen Block aufnehmen. Dieser wird durch eine Ansteuerung des Generators (G) mit dem gewünschten Informationsmuster erzeugt, wandert vor die Tore und wird in die Schieberegister übernommen.

Die Chipkapazität ergibt sich als Produkt aus Anzahl der Schieberegister  $n$  und deren Speicherkapazität  $N_{SR}$ . Die Anzahl  $n$  ist wiederum durch die Länge des Ein-/Ausgaberegisters  $N_{EAR}$  bestimmt. Damit die nach einem Lesevorgang in die Schieberegister zurückkehrenden Domänen wieder ihre ursprünglichen Plätze einnehmen können, muss das Ein-/Ausgaberegister genausol lang sein wie die Schieberegister, oder ein ganzzahliges Vielfaches davon, so dass  $N_{EAR} = i \cdot N_{SR}$ . Will man lange, schmale Chips vermeiden, so bleiben als sinnvolle Werte nur  $i = 1$  oder  $2$ , wobei im folgenden nur der Fall  $i = 2$  betrachtet wird. Eine ins Ein-/Ausgaberegister übernommene Domäne durchläuft dieses in insgesamt  $N_{EAR}$  Takten. In der gleichen Zeit läuft ihr ursprünglicher Speicherplatz zweimal durch das Schieberegister und steht nach  $2 N_{SR}$  Takten wieder am Tor zur Aufnahme der rückkehrenden Domäne bereit. Die mit Schieberegistern belegte Seite des Ein-/Ausgaberegisters hat eine Länge von  $N_{EAR}/2$  bit. Bedingt durch die geometrische Form der Bars beträgt der Minimalabstand zwischen zwei Toren 2 bit, so dass die maximal mögliche Zahl der Schieberegister  $n = N_{EAR}/4$  beträgt. Mit  $N_{EAR} = 2 N_{SR}$  ergibt sich der Zusammenhang zwischen Speicherkapazität  $K$  und der Schieberegisterlänge zu

$$K = \frac{1}{2} N_{SR}^2. \quad (1)$$

Die Zugriffszeit ist durch die Länge der Schieberegister und durch die Rotationsfrequenz bestimmt. Sind auf einem 128-kbit-Chip 256 Schieberegister mit einer Speicherkapazität von  $N_{SR} = 512$  bit angeordnet, so werden bei einem willkürlichen Aufruf eines bestimmten Informationsblockes im Mittel  $512/2$  Takte des Rotationsfeldes benötigt, bis der Block an die Tore gelangt und ins Ein-/Ausgaberegister übertritt. Die bis zum Eintreffen der ersten Domäne am Detektor erforderliche zusätzliche Taktzahl soll vernachlässigt werden. Damit beträgt die mittlere Zugriffszeit  $\bar{t}_{zu} = 256$  Takte oder 2,6 ms für  $f = 100$  kHz. Allgemein gilt:

$$\bar{t}_{zu} = \frac{1}{2} N_{SR}/f \quad (2)$$

Da die mittlere Zugriffszeit nur linear mit  $N_{SR}$ , die Chipkapazität dagegen mit  $N_{SR}^2$  steigt, werden auch für sehr grosse Chipkapazitäten, zusammen mit einer Erhöhung der Frequenz auf 1 MHz, Zugriffszeiten um 1 ms erwartet.

Die Bearbeitungszeit für einen Zugriff setzt sich aus der mittleren Zugriffszeit und der Umlaufzeit der Domänen durch das Ein-/Ausgaberegister  $N_{EAR}/f = 2 N_{SR}/f$  zusammen. Damit berechnet sich die mittlere Zykluszeit

$$\bar{t}_{zu} = \frac{5}{2} N_{SR}/f, \quad (3)$$

die bei willkürlicher Adressierung die maximale Aufruffolge bestimmt.

#### 4. Herstellung des Speicherchips

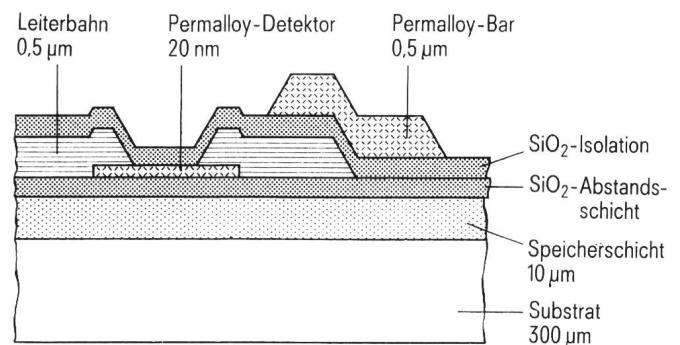

Zur Herstellung des Chips werden im allgemeinen Prozesse verwendet, wie sie aus der Halbleitertechnologie bekannt sind. Als Trägerschicht dient eine 0,3 mm dicke Scheibe aus nichtmagnetischem GdGa-Granat, deren Oberfläche zur Erzielung weitgehend fehlerfreier Speicherschichten äußerst sorgfältig poliert wird [11]. Auf die Trägerschicht wächst in einer Schmelze die Speicherschicht aus magnetischem Granat mit der allgemeinen chemischen Formel  $Y_{3-x} (SE)_x (Ga,Al)_y Fe_{5-y} O_{12}$  epitaktisch auf («liquid-phase»-Epitaxie-Verfahren) [12]. Neben Yttrium und Eisen enthalten die vielen bis heute entwickelten Schichten eine oder mehrere seltene Erden (SE) und Gallium oder Aluminium, so dass neben Sauerstoff 4...6 weitere Komponenten auftreten. Diese müssen in exakter stöchiometrischer Zusammensetzung vorliegen, damit die Speicherschicht die gewünschten magnetischen Eigenschaften aufweist. Zur Vermeidung unerwünschter «hard bubbles» wird die Schicht mit Ionen implantiert [13]. Neben der Granatschicht sind folgende Schichten erforderlich: zwei Siliziumdioxid-Zwischenschichten, eine dünne Permalloyschicht für den Detektor, eine dicke Permalloyschicht für die Bars und eine Leiterbahnschicht (Fig. 5). Zur Herstellung der Strukturen am Chip dienen die bekannten Verfahren der Photolithographie. Die charakteristischen Chipdaten entsprechend dem heutigen Stand der Technik sind in Tabelle I dargestellt, zusammen mit den in einigen Jahren zu erwartenden Chips hoher Speicherkapazität, auf die noch eingegangen wird. Fig. 6 zeigt die Photographie eines Speicherchips.

Fig. 5 Schichtfolge am Chip

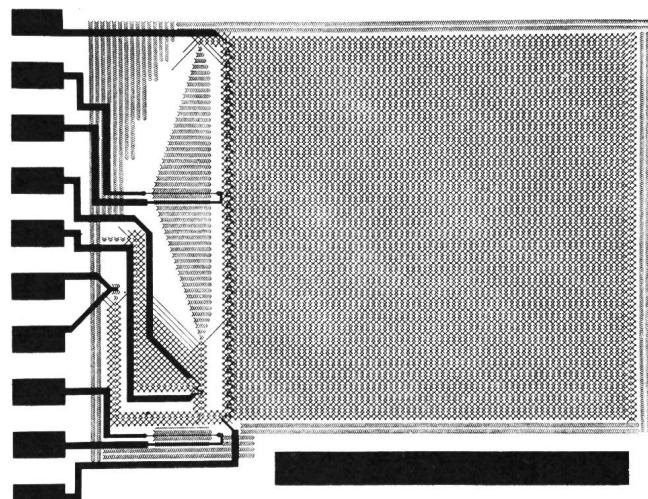

Fig. 6 Photographie eines 4-kbit-Chip

Abmessungen ca. 2 x 1,5 mm

Neben Speicherschichten aus Granat werden auch gelegentlich amorphe Speicherschichten aus GdCoMo verwendet [4], die sich besonders zur Herstellung kleinstter Domänen um  $0,1 \mu\text{m}$  Ø eignen. Bei den Chipentwicklungen der kommenden Jahre dürften aber wie bisher in überwiegendem Masse die wesentlich besser erforschten Granatschichten eingesetzt werden.

## 5. Speicherblock und Modulaufbau

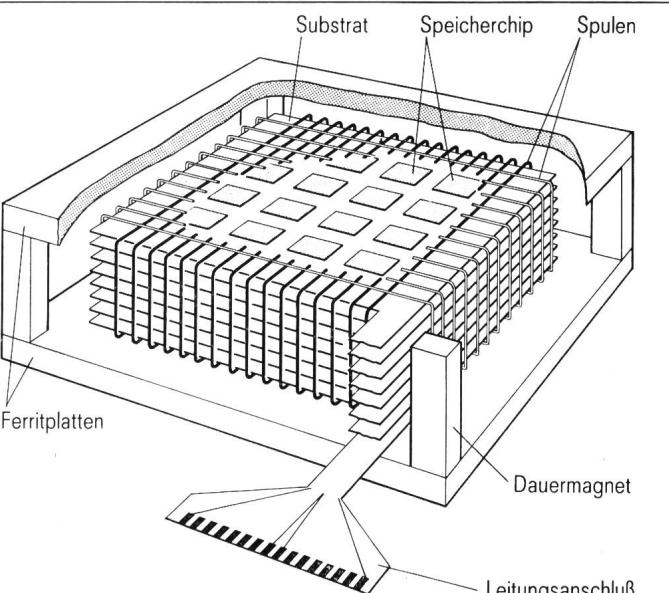

Zum Aufbau eines Speichers sind eine grosse Zahl von Chips erforderlich, für die das Stützfeld und das Rotationsfeld zur Verfügung gestellt werden müssen. Das Rotationsfeld wird mit zwei gekreuzten Flachspulen erzeugt.

Zur optimalen Ausnutzung der aufzubringenden elektrischen Energie soll ein gegebenes Spulenvolumen eine grosse Zahl von Speicherchips aufnehmen. Bei dem in Fig. 7 dargestellten Speichermodell werden 16 Chips auf einem 0,5 mm dicken Keramiksubstrat angeordnet, das mit einem Flügel zum Anschluss der elektrischen Ansteuerleitungen versehen ist. Ein Stapel aus acht Substraten wird mit den beiden gekreuzten Spulen umwickelt und in einem von Dauermagneten erzeugten Stützfeld untergebracht. Bestückt mit 128-kbit-Chips weist der Block von 120 mm Kantenlänge und 20 mm Höhe eine Speicherkapazität von 2 Mbyte auf (Tab. II). Eine Elektronikbaugruppe von  $230 \times 260 \text{ mm}$  nimmt einen Speicherblock zusam-

Fig. 7 Aufbau des Speicherblocks

men mit den elektronischen Bauteilen zur Erzeugung des rotierenden Feldes auf. Sechzehn Baugruppen ergeben mit zwei gemeinsamen Steuerbaugruppen einen Speichermodul von 32 Mbyte, der in einem Baugruppenrahmen von 400 mm Breite untergebracht wird.

Die Organisation der Daten ist durch den Aufbau der Speicherchips festgelegt. Die Daten sind im Speicherchip in Informationsblöcken untergebracht, z.B. in 256 Blöcken zu 512 bit. Werden pro Zugriff grössere Datenmengen gewünscht, so können mehrere Chips eines Speicherblockes gleichzeitig gelesen werden. Arbeiten 64 Chips parallel, so ergibt sich eine Speicherblockgrösse von 4 kbyte und eine Datenrate von 0,8 Mbyte/s. Da jedoch mit steigender Zahl parallel arbeitender Chips auch die Elektronikkosten ansteigen, werden jeweils nur so viele Chips parallel betrieben, wie zur Erzielung der erforderlichen Datenrate nötig sind. Übersteigt die bei einem Zugriff gewünschte Datenmenge die Blockgrösse, so können mehrere Blöcke in sequentieller Folge adressiert werden.

Charakteristische Chipdaten

Tabelle I

|                                 |                   | Jetziger Stand | Zukünftiger Stand |

|---------------------------------|-------------------|----------------|-------------------|

| Domänendurchmesser              | $\mu\text{m}$     | 5              | 0,5–2             |

| Permalloybarbreite              | $\mu\text{m}$     | 3              | 0,5–1             |

| Speicherdicthe im Zellenbereich | $\text{bit/cm}^2$ | $2 \cdot 10^5$ | $10^7$            |

| Chipkapazität                   | bit               | $10^5$         | $10^6$            |

| Chipfläche                      | $\text{cm}^2$     | 0,5            | 0,25–0,5          |

| Rotationsfrequenz               | Hz                | $10^5$         | $10^6$            |

| Mittlere Zugriffszeit           | ms                | 2              | 1                 |

Modell eines DomänenSpeichers

(Epitaktische Granatschicht, Standard-Photolithographie) Tabelle II

|          |                                                                                                                                                                                                                                                                              |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip     | 128 kbit<br>256 SR mit 512 bit<br>$2 \mu\text{m}$ Bahnbreite, $50 \text{ mm}^2$ Gesamtfläche                                                                                                                                                                                 |

| Substrat | 2 Mbit; 16 Chips,<br>$100 \times 100 \text{ mm}$ , 1 mm Höhe                                                                                                                                                                                                                 |

| Block    | 2 Mbyte; 8 Substrate<br>160 var pro Spule bei $100 \text{ kHz}$ , $20 \text{ A/cm}$<br>10 W Leistungsverbrauch für beide Spulen<br>bei einer Schwingkreisgüte $Q = 32$<br>$12 \times 12 \times 2 \text{ cm}$ mit Spulen und Stützfeld<br>100 $\text{cm}^3$ Volumen für H-rot |

| SP-Modul | 32 Mbyte<br>2,5 ms mittlere Zugriffszeit<br>0,2 Mbyte/s Datenrate (16 bit parallel)<br>30 W (nur jeweils 1 Block in Betrieb)<br>16 Speicherbaugruppen mit je 1 Block<br>2 Elektronikbaugruppen<br>401 Volumen                                                                |

## 6. Speicherelektronik

Die Elektronik kann in die folgenden drei Teile aufgegliedert werden: Ablaufsteuerung, Erzeugung des Rotationsfeldes und Verarbeitung des Lesesignales.

Die *Ablaufsteuerung* dekodiert die Befehle (z. B. Lesen oder Schreiben) und steuert die Treiber und das Drehfeld an. Der Aufbau erfolgt auf Elektronikbaugruppen mit integrierten Schaltkreisen. Die Anforderungen an die Treiberströme betragen maximal einige 100 mA.

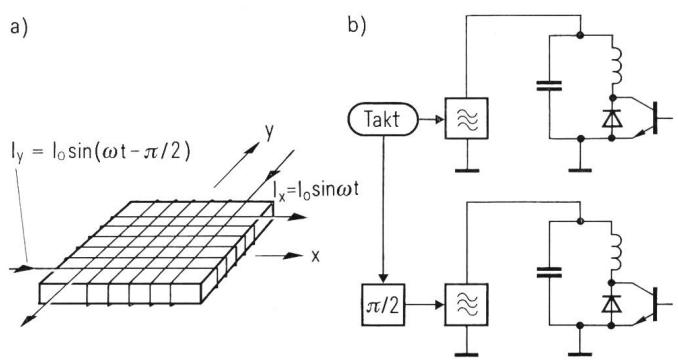

Zur *Erzeugung des Drehfeldes* dienen gekreuzte Spulen, die mit phasenverschobenen Strömen angesteuert werden (Fig. 8a). Die Ansteuerung kann mit diskreten Stromimpulsen [14] oder mit sinusförmigem Wechselstrom erfolgen [15, 16]. Werden die Spulen über eine einfache Impulsansteuerung ohne energiespeichernde Massnahmen betrieben, so wird die magnetische Feldenergie bei jedem Aufbau des Feldes in eine Spule geschickt und beim Abbau des Feldes wieder vernichtet. Dadurch tritt ein hoher Leistungsbedarf auf. Die magnetische Energie  $I_s^2 L/2$  in einer Spule der Induktivität  $L$  wird pro Zyklus infolge

der beiden Strommaxima mit dem Wert  $I_s$  zweimal benötigt. Außerdem arbeitet eine einfache Schaltungsanordnung zur Erzeugung des Spulenstromes nur mit einem Wirkungsgrad von etwa 0,5, so dass sich folgende Wirkleistung für beide Spulen ergibt:

$$2 P = 2 \cdot I_s^2 L / 2 \cdot 2 f / 0,5 \quad (4)$$

Unter der Annahme eines homogenen Magnetfeldes  $H$ , das sich auf das Spuleninnere mit dem Volumen  $V$  beschränkt, folgt aus Gl. (4) mit Hilfe der Beziehung für die magnetische Energie  $I_s^2 L / 2 = \mu_0 H^2 V / 2$  die Wirkleistung/Volumen für beide Spulen zu

$$2 P/V = 4 \mu_0 H^2 f. \quad (5)$$

Für typische Werte von  $H = 20 \text{ A/cm}$ ,  $V = 100 \text{ cm}^3$  und  $f = 100 \text{ kHz}$  ergibt sich ein unerwünscht hoher Leistungsbedarf von 200 W.

Um den Leistungsbedarf bei grösseren Speicherblöcken und hoher Rotationsfrequenz gering zu halten, werden die Spulen in Resonanzkreisen betrieben (Fig. 8b). Die Blindleistung  $P_q$  einer Spule beträgt für einen Scheitelwert des Stromes  $I_s$

$$P_q = \frac{1}{2} I_s^2 2\pi f L. \quad (6)$$

Mit  $I_s^2 L / 2 = \mu_0 H^2 V / 2$  folgt die Blindleistung/Volumen für beide Spulen zu

$$2 P_q/V = 2\pi\mu_0 H^2 f. \quad (7)$$

Für die bereits oben benützten typischen Werte folgt  $2 P_q = 320 \text{ var}$ , so dass sich bei einer Schwingkreisgüte von  $Q = 32$  eine Wirkleistung  $P$  von 10 W ergibt.

Die Erzeugung des Rotationsfeldes in Schwingkreisen erfordert besondere Massnahmen beim Ein- und Ausschalten des Feldes, um die Information in den Speicherbausteinen zu erhalten. Der Domänentransport im Speicherchip erfordert einen bestimmten Mindestwert für das Rotationsfeld. Beim Einschalten des Feldes müssen deshalb die Spulenströme bereits im ersten Rotationszyklus ihre volle Amplitude erreichen, beim Abschalten dürfen die Ströme nach Ausführung des letzten Zyklus den Mindestwert für Domänentransport nicht mehr überschreiten. Dieses spontane Ein- und Ausschalten des rotierenden Feldes ist Voraussetzung für den geforderten «non-volatile» Speicherbetrieb. Dazu wurden bereits verschiedene Schaltungsanordnungen vorgeschlagen [15; 16].

Die Verarbeitung des geringen Lesesignales stellt hohe Anforderungen an die Leseverstärker. Das am Detektor auftre-

Fig. 8 Erzeugung des Rotationsfeldes mit gekreuzten Flachspulen (a), die in Schwingkreisen betrieben werden (b)

tende Signal ist von Störungen überlagert, die durch Zusammenschalten mehrerer Detektoren zu einer Brücke weitgehend kompensiert werden können [17]. Das verbleibende Brückensignal, das für 5-μm-Domänen einige mV beträgt, wird einem Leseverstärker mit Bewertungsschwelle zugeführt und auf TTL-Pegel<sup>3)</sup> umgesetzt.

## 7. Stand und Probleme der Entwicklung

Nach allgemeiner Ansicht ist die Forschungsphase der epitaktischen Granatschichten bei den führenden Entwicklern abgeschlossen. Eine Reihe von Firmen haben 16-kbit-Bausteine bis zur Produktionsreife entwickelt und zum Aufbau von Prototypspeichern mit einer Kapazität bis  $10^6$  bit eingesetzt [z. B. 18]. Die im Labor erreichte Chipkapazität beträgt ca.  $10^5$  bit auf einer Chipfläche von  $0,5 \text{ cm}^2$ . Damit lassen sich Speicher einer Kapazität von einigen 10 Mbyte aufbauen. Aus Kostengründen werden Speicherchips mit etwa  $2 \cdot 10^5 \dots 10^6$  bit angestrebt. Die Eigenschaften der Speicherschichten werden durch eine Reihe physikalischer Größen beschrieben, die auf einen optimalen Wert eingestellt werden müssen [19]. Um dies zu erreichen, werden eine Reihe von Komponenten in exakten stöchiometrischen Verhältnissen zusammengemischt, so dass sich recht komplizierte Schichtzusammensetzungen ergeben. Neben den erforderlichen magnetischen Eigenschaften müssen die Schichten weitgehend homogen und fehlerfrei sein und eine gute Temperaturkonstanz besitzen. Die gewünschte Vergrösserung der Chipkapazität über  $10^5$  bit hinaus wird nur zu einem geringen Teil über eine grössere Chipfläche möglich sein. Eine wesentliche Steigerung wird hauptsächlich durch eine Erhöhung der Bitdichte erwartet, die wiederum eine Verringerung der Linienbreite der Permalloystrukturen erfordert, die heute  $2 \dots 3 \mu\text{m}$  erreicht hat. Da die Leistungsgrenze der Standard-Photolithographie bei einer minimalen Linienbreite von etwa  $2 \mu\text{m}$  liegt, ist zur Erzielung weiterer Fortschritte der Einsatz der Röntgen- oder Elektronenstrahlbelichtung erforderlich. Damit wurde bereits ein 8-kbit-Chip mit  $1 \mu\text{m}$  Linienbreite der Permalloystrukturen hergestellt [4]. In einigen Jahren wird mit der Herstellung von Bausteinen mit  $10^6$  bit gerechnet (Tabelle I).

Weitere Möglichkeiten zur Steigerung der Chipkapazität geben die «contiguous disc»-Permalloystruktur und die «bubble lattic file»-Anordnung [20]. Diese Methoden befinden sich jedoch noch im Entwicklungsstadium.

Neben der Chipkapazität wird an einer Erhöhung der Rotationsfrequenz gearbeitet. Die bisher bekannt gewordenen Speicher arbeiten mit einer Frequenz von 100 kHz, während der angestrebte Wert einige MHz beträgt. Obwohl eine Reihe von Granatmaterialien für diese Frequenzen geeignet sein sollten, treten im allgemeinen bereits bei einer Frequenz über 500 kHz Störungen beim Domänentransport auf. Domänen geraten aus ihrer Bahn, so dass Informationsverfälschungen auftreten. Mit weiteren Untersuchungen des Domänentransportes und Materialverbesserungen dürfte jedoch die angestrebte hohe Frequenz zu erreichen sein.

<sup>3)</sup> TTL = Transistor-Transistor-Logik. Eine Zusammenstellung der verwendeten Abkürzungen der Elektronik befindet sich auf Seite 70.

## **8. Anwendungsmöglichkeiten und Vergleich mit anderen Speichermedien**

Der Zylinderdomänen-Speicher ist ein peripherer Speicher mit wahlfreiem Zugriff. Die in naher Zukunft auf dem Markt erscheinenden Speicher werden, bedingt durch ihre Kapazität und Kosten, zu den Festkopfplatten in Konkurrenz treten. Diese werden als Seitenspeicher in grossen Rechnern eingesetzt und finden in Prozess- und Kleinrechnern und in intelligenten Terminals eine Reihe von Anwendungen. Gegenüber der Festkopfplatte wird der Domänen-Speicher folgende Vorteile aufweisen: Er ist vollelektronisch, benötigt damit keine Wartung und besitzt eine hohe Zuverlässigkeit. Der Leistungsverbrauch, das Volumen, das Gewicht und die Zugriffszeit sind geringer. Ein Kostenvorteil wird jedoch erst in einigen Jahren mit Speicherbausteinen höherer Kapazität erwartet. Dabei rechnen einige Entwickler sogar mit einem Ersatz der grossen Festkopfplatten, sobald Zylinderdomänen-Speicherbausteine mit mindestens  $10^6$  bit zur Verfügung stehen. Die Technologie dieser Massenspeicher ist jedoch noch entwicklungsfähig und wird auch in den kommenden Jahren Laufwerke immer höherer Speicherkapazität verbunden mit stetig sinkendem Bitpreis bringen. Auch ein Einsatz des Domänen-Speichers anstelle von Magnetbandgeräten oder -kassetten dürfte sich auf Anwendungen beschränken, bei denen nicht die Kosten, sondern die Zuverlässigkeit [21] oder andere Gesichtspunkte im Vordergrund stehen.

Eine interessante Anwendung des Domänen-Speichers wird im sogenannten «access gap» erwartet, dem Bereich der Zugriffszeit von 10 µs (langsamer Arbeitsspeicher) bis 10 ms (schneller Plattenspeicher). Der Domänen-Speicher eignet sich infolge seiner charakteristischen Daten zum Aufbau eines erweiterten Speichersystems aus Pufferspeicher, kleinem Arbeitsspeicher und Domänen-Speicher anstelle der herkömmlichen Anordnung aus Pufferspeicher und grossem Arbeitsspeicher. Dieses dreistufige System lässt neben einer Erhöhung der Leistungsfähigkeit eine Verringerung der Gesamtkosten erwarten [22]. Für diese Anwendung wird der Domänen-Speicher mit Halbleiter-Speichern, insbesondere dem CCD-Speicher<sup>4)</sup> in Konkurrenz stehen. Gegenüber der Halbleiter-Techno-

logie werden bei der Herstellung von Domänen-Chips weniger Masken, fast keine Durchkontaktierungen und keine Diffusionen verwendet und die Speicherzellen benötigen keine elektrischen Leitungen. Ein Vergleich der Herstellungsprozesse berechtigt zu der Annahme, dass Domänen-Chips mit einer 2...4fachen Speicherkapazität hergestellt werden können.

## **Literatur**

- [1] R. C. Sherwood, J. P. Remeika and H. J. Williams: Domain behaviour in some transparent magnetic oxides. *J. Applied Physics* 30(1959)2, p. 217...225.

- [2] A. H. Bobeck: Properties and device applications of magnetic domains in orthoferrites. *Bell Syst. Techn. J.* 46(1967)8, p. 1901...1925.

- [3] P. I. Bonyhard a. o.: Magnetic bubble memory chip design. *Trans. IEEE Mag.* 9(1973)3, p. 433...436.

- [4] K. Y. Ahn a. o.: Electron-beam fabrication of high density amorphous bubble-film devices. *Trans. IEEE Mag.* 11(1975)5, p. 1142...1144.

- [5] Texas Instruments moves bubbles to pilot production for its products. *Electronics* 49(1976)5, p. 32...33.

- [6] A. H. Bobeck a. o.: Application of orthoferrites to domain-wall devices. *Trans. IEEE Mag.* 5(1969)3, p. 544...553.

- [7] W. Metzdorf: Properties of X-bar overlay structures for magnetic bubble memories. *International Conference on Magnetic Bubbles*, Eindhoven, 13...15 September 1976.

- [8] T. J. Nelson, Y.-S. Chen and J. E. Geusic: Field nucleation of magnetic bubbles. *Trans. IEEE Mag.* 9(1973)3, p. 289...293.

- [9] G. S. Almasi: Magnetic bubble-domain detection: Review and-outlook. *Trans. IEEE Mag.* 9(1973)4, p. 663...669.

- [10] P. I. Bonyhard a. o.: Applications of bubble devices. *Trans. IEEE Mag.* 6(1970)3, p. 447...451.

- [11] J. W. Nielsen, S. J. Licht and C. D. Brandle: The preparation of large area films for bubble domain devices. *Trans. IEEE Mag.* 10(1974)3, p. 474...476.

- [12] L. J. Varnerin: Approaches for making bubble-domain materials. *Trans. IEEE Mag.* 7(1971)3, p. 404...409.

- [13] R. Wolfe and J. C. North: Suppression of hard bubbles in magnetic garnet films by ion implantation. *Bell Syst. Techn. J.* 51(1972)6, p. 1436...1440.

- [14] K. Yamagishi a. o.: A new proposal on field-access bubble drives. *Trans. IEEE Mag.* 11(1975)1, p. 16...20.

- [15] G. P. Vella-Coleiro and W. E. Hess: The generation of rotating magnetic fields for bubble devices. *Trans. IEEE Mag.* 10(1974)3, p. 750...752.

- [16] F. Navratil: Generation and fast switching of high frequency rotating fields for bubble memories. *Trans. IEEE Mag.* 11(1975)5, p. 1154...1156.

- [17] A. Böhnlein: Signal-to-noise ratio of magnetoresistive bubble domain sensors. *Siemens Forsch.- u. Entwickl.-Ber.* 3(1974)4, p. 225...233.

- [18] P. C. Michaelis and W. J. Richards: Magnetic bubble mass memory. *Trans. IEEE Mag.* 11(1975)1, p. 21...25.

- [19] A. H. Bobeck, R. F. Fischer and J. L. Smith: On overview of magnetic bubble domains. *AIP Conf. Proc.* 5(1971) Part 1, p. 45...55.

- [20] M. S. Cohen and H. Chang: The frontiers of magnetic bubble technology. *Proc. IEEE* 63(1975)8, p. 1196...1206.

- [21] T. T. Chen a. o.: A magnetic bubble domain flight recorder. *Trans. IEEE Mag.* 10(1974)3, p. 739...745.

- [22] W. Anacker: Possible uses of charge-transfer devices and magnetic-domain devices in memory hierarchies. *Trans. IEEE Mag.* 7(1971)3, p. 410...415.

## **Adresse des Autors**

Dr. Anton Böhnlein, Zentrallaboratorium für Nachrichtentechnik, Siemens AG, Hofmannstrasse, D-8 München.

<sup>4)</sup> CCD = Charge Coupled Device.