**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

**Herausgeber:** Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 68 (1977)

Heft: 2

Artikel: La Technologie SOS

Autor: Schwob, P.

**DOI:** https://doi.org/10.5169/seals-914979

## Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

## **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

## Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 01.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# La Technologie SOS 1)

Par P. Schwob

621.3.049.774

Le progrès récent de la technologie SOS permet aujourd'hui de réaliser des circuits intégrés du type MOS qui sont très rapides, dissipent extrêmement peu d'énergie et fonctionnent même en présence d'irradiation ionisante. Le principe du SOS, ses autres avantages et ses problèmes sont discutés ainsi que les applications principales et la question de l'économie d'une telle technologie.

Der heutige Stand der SOS-Technologie erlaubt es, integrierte MOS-Schaltkreise mit folgenden Eigenschaften herzustellen: sehr kurze Schaltzeiten, extrem kleiner Stromverbrauch und Funktionstüchtigkeit unter radioaktiver Bestrahlung. Das Prinzip dieser Technologie sowie deren weitere Vorteile und Besonderheiten werden erklärt, gefolgt von einer Diskussion der wichtigsten Anwendungen und der Wirtschaftlichkeit der Herstellung derartiger integrierter Schaltungen.

#### 1. Introduction

## 1.1 Généralités

«Silicon on Sapphire» (SOS)  $^2$ ) est une technologie récente de la micro-électronique, développée dans le but de supprimer les désavantages de l'isolation à jonctions. Dans la fabrication des circuits intégrés en SOS on part d'une plaquette de saphir pur (corindon Al $_2$ O $_3$ ) sur laquelle est déposée une couche très mince ( $\approx 0.5~\mu m$ ) de silicium. Le circuit intégré est fabriqué dans cette couche de silicium et toutes les parties de la couche qui ne servent pas à la formation d'un élément électrique sont enlevées. Le produit final est donc un circuit intégré à éléments discrets.

Etant donné que cette couche de silicium est une couche épitaxiale (monocristalline), il est possible d'obtenir en technologie SOS des transistors MOS<sup>3</sup>) avec pratiquement les mêmes propriétés que ceux réalisés en silicium massif. Cependant, comme le nombre de défauts cristallins dans la couche est beaucoup plus élevé que dans le silicium massif qui sert à la fabrication des CI<sup>4</sup>), la durée de vie des porteurs minoritaires dans la couche est inférieure à 1 ns. Sans astuces spéciales il est donc impossible de réaliser des transistors bipolaires en SOS.

A l'heure actuelle c'est essentiellement avec la technologie à MOST complémentaires (CMOS)<sup>5</sup>) que le SOS possède les propriétés les plus importantes. Il s'agit donc surtout de circuits digitaux qui sont réalisés en technologie SOS.

## 1.2 La technologie à MOST complémentaires (CMOS)

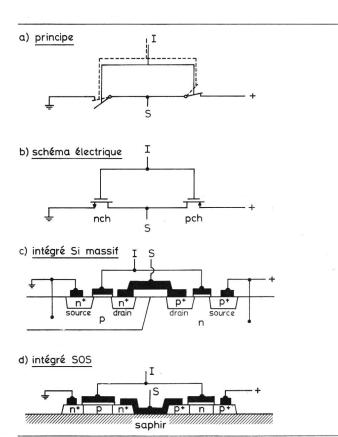

L'élément de base de la technologie CMOS est une paire de deux interrupteurs complémentaires en série, formant un inverseur électrique (fig. 1a). Les deux interrupteurs sont le transistor MOS à canal n (n-ch) et celui à canal p (p-ch), indiqués dans le schéma de la fig. 1b. La version intégrée de cet inverseur est représentée dans la fig. 1c pour le cas du silicium massif et dans la fig. 1d pour le cas du SOS. Les transistors MOS ont les caractéristiques électriques d'une pentode et ils sont commandés par une tension et non pas par un courant. La grille de commande est isolée du reste du transistor par l'oxide de grille. Le MOST à canal n est mis en état de conduction par une tension de grille positive, celui à canal p par une tension de grille négative. La conduction est due à une couche d'inversion (canal) sous l'oxide de grille constituée par des électrons (n-ch) ou des trous (p-ch).

Les propriétés les plus intéressantes de la technologie CMOS sont les suivantes:

- une impédance d'entrée extrêmement élevée ( $R \geq 10^{15}~\Omega,$   $C_{\mathrm{typ}} = 0.1~\mathrm{pF})$

- pas de dissipation de courant statique à part les courants de fuites des diodes qui sont très faibles (inférieurs à 1 nA par élément)

- faible dissipation de courant dynamique à des fréquences moyennes

- Fan-out illimité en régime basse fréquence

- une seule tension d'alimentation

- compatibilité de la tension de sortie avec la tension d'entrée

- grande insensibilité au bruit

La technologie CMOS est donc idéale pour des circuits à très faible puissance et elle est compétitive dans beaucoup d'applications (micro-processeur).

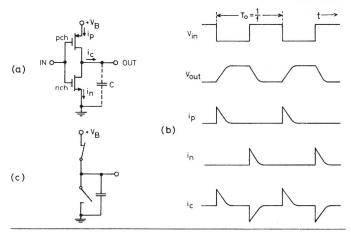

Dans le domaine des fréquences élevées il faut tenir compte des capacités qui sont présentes dans un circuit intégré. La fig. 2 montre le fonctionnement dynamique de l'inverseur CMOS à une fréquence de commutation f. La capacité C du nœud est chargée et déchargée une fois par période. Le courant dynamique est donc

$$I_{\rm dyn} = f \cdot C \cdot V$$

et la puissance dissipée dans le circuit

$$P_{\mathrm{dyn}} = f \cdot C \cdot V^2$$

La fréquence limite de commutation de l'inverseur  $f_{\text{max}}$  est approximativement donnée par

$$f_{\max} = \frac{1}{4} \cdot \beta \cdot V/C$$

où  $\beta$  est und paramètre électrique et géométrique du MOST. Un circuit CMOS sera donc d'autant plus rapide que sa tension d'alimentation est élevée, mais la dissipation d'énergie augmente avec le carré de la tension. D'autre part, par une réduction technologique de la capacité C, le circuit devient plus rapide et la dissipation d'énergie à une fréquence donnée diminue. C'est par la technologie SOS que l'on arrive à réduire au strict minimum les capacités dans un circuit intégré.

## 2. Les avantages de la technologie SOS

## 2.1 Insensibilité à l'irradiation ionisante

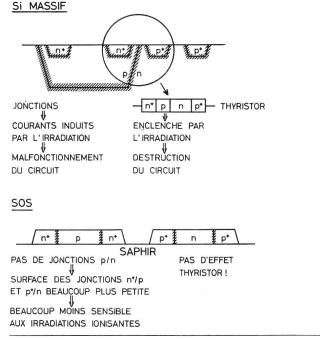

La technologie SOS fut avancée en premier lieu pour diminuer la sensibilité des circuits intégrés à l'intensité de l'irradiation ionisante. Pour atteindre ce but, il fallait trouver une technologie qui puisse se passer de la majorité des jonctions normalement présentes dans un circuit intégré (fig. 3). C'est,

- 1) Conférence tenue lors de la journée d'information de l'ASE intitulée «Technologies modernes dans l'électronique», le 11 novembre 1976 à Bienne.

- 2) Un tableau des abréviations utilisées est donné à la page 70.

- 3) MOS = Metal Oxide Semiconductor

- 4) CI = Circuit intégré

- 5) MOST = MOS Transistor CMOS = Complementary MOS

Fig. 1 Inverseur CMOS

I entrée p<sup>+</sup>, n<sup>+</sup> régions fortement dopées

S sortie p, n régions faiblement dopées

n ch canal n

p ch canal p

en effet, dans la zone de charge d'espace des jonctions que les paires électrons-trous créées par l'irradiation ionisante sont séparées, donnant ainsi lieu à des courants parasites qui peuvent amener un mauvais fonctionnement et même la destruction du circuit (effet thyristor).

En SOS, la jonction entre les zones faiblement dopées p et n n'existe pas du tout, un effet thyristor ne peut donc pas avoir lieu. En plus, la surface des jonctions de la source et du drain n'est que de quelques pour cents de ce qu'elle représente en technologie standard, donc les courants créés par l'irradiation sont réduits très fortement. Finalement, comme il n'y a pas de silicium hors de transistors, les porteurs créés hors des jonctions (dont, en plus, la durée de vie est faible), ne pourront pas diffuser vers ceux-ci.

Il ne s'agit là que des effets immédiats créés par une forte intensité d'irradiation. Quant à l'accumulation d'une dose élevée par une exposition prolongée, on observe la formation de défauts métallurgiques avec pratiquement les mêmes conséquences pour les circuits en SOS ou en silicium massif.

## 2.2 Réduction des capacités du circuit

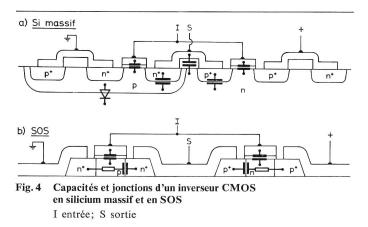

Les capacités qui apparaissent dans un circuit intégré CMOS et qui sont soumises à un signal alternatif sont les suivantes (fig. 4a):

- la capacité entre la grille de commande et le canal du MOST

- 2. les capacités entre les interconnexions et le silicium massif

- 3. les capacités de la jonction du drain des MOST

Fig. 2 Courant dynamique de l'inverseur CMOS

En passant à la technologie SOS (fig. 4b) on supprime totalement les capacités du type 2. Il en est de même pour les capacités du type 3, puisque la très petite capacité de jonction qui est encore présente en SOS n'est liée qu'à travers la résistance très élevée de la couche de silicium aux potentiels fixes. La constante RC est donc beaucoup plus grande que la période du signal; ainsi la capacité de drain ne se manifeste pas en SOS. Finalement, il s'avère que les MOST peuvent être fabriqués plus petits en SOS qu'en silicium massif parce qu'il n'y a plus de danger d'un court-circuit au substrat par un contact trop grand. La surface de la grille et ainsi la capacité du type 1 sont donc réduites, sans pour autant changer la fréquence limite du circuit, parce que la constante  $\beta$  du MOST est changée en même temps. Il est difficile de chiffrer tous ces gains parce qu'ils dépendent fortement des règles de layout du circuit. Typiquement on attend un gain total d'un facteur 2 en

Fig. 3 Influence de l'irradiation ionisante: effets immédiats

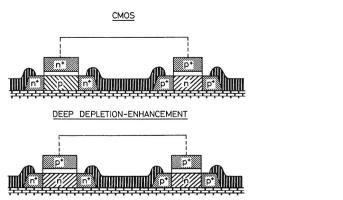

Fig. 5 Technologie SOS: comparaison entre CMOS et Deep Depletion-Enhancement

vitesse et d'un facteur 4 en consommation, donc un gain final d'un facteur 8 apporté par la technologie SOS. Dans un circuit complexe le gain peut être encore plus grand dû à une cumulation des effets considérés.

### 2.3 Augmentation de la densité d'intégration

Dans la conception d'un layout pour un circuit en silicium massif il faut tenir compte de l'extension des diffusions latérales. Ainsi la séparation minimum entre deux transistors MOS complémentaires est de l'ordre de 30 µm. Ce genre de problème n'existe pas en SOS puisqu'il n'y a pas de diffusion hors des îlots de silicium. Il en résulte une plus grande densité d'intégration, donc une surface réduite du circuit. Par conséquent, le prix du circuit sera doublement réduit: d'une part parce qu'il y a un plus grand nombre de circuits par plaquette et d'autre part parce que le rendement de fabrication est plus élevé pour des circuits à petite surface. C'est une des raisons pour lesquelles les circuits SOS ne sont pas beaucoup plus chers que les circuits standard malgré le prix élevé du saphir.

## 2.4 Absence de la jonction entre caisson p et substrat n

La jonction entre les zones faiblement dopées p et n s'étend pratiquement sur la moitié de la surface d'un circuit intégré CMOS en silicium massif. Susceptible de défauts cristallins qui créent des courants de fuites excessifs, cette jonction est souvent à l'origine des défaillances du circuit. Grâce à son absence en technologie SOS on s'attend à un rendement de fabrication plus élevé. Cependant, c'est seulement sur la base d'une production à grand volume que cette hypothèse pourra être vérifiée. En plus, l'apparition d'un thyristor – formé par une succession de quatre couches diffusées – est aussi possible en silicium massif sans l'influence de l'irradiation ionisante. La con-

ception d'un circuit SOS est donc plus sûre, parce qu'il y a moins d'éléments cachés qui peuvent échapper à celui qui conçoit le circuit.

## 2.5 Absence des transistors MOS parasites

Le fabricant d'un circuit MOS en silicium massif doit veiller à ce que les interconnexions métalliques n'agissent pas comme grille de commande d'un transistor MOST parasite dont l'oxide de grille est l'oxide épais qui sert à isoler la métallisation du substrat. Il faut donc que la tension de seuil de ce MOST parasite soit sensiblement plus élevé que la tension d'alimentation du circuit. On atteint ce but par un dopage sélectif ou par une couche d'isolation suffisamment épaisse. En technologie SOS il n'y a pas de transistors MOS parasites parce qu'on enlève le silicium en dehors des éléments actifs. Grâce à ce fait le même circuit SOS peut être utilisé à différentes tensions d'alimentation, p.ex. entre 5 et 10 V. Ceci augmente fortement la flexibilité d'application.

#### 2.6 Le MOST à appauvrissement profond

La fig. 5 montre deux versions d'un inverseur CMOS SOS: la version normale, appelée CMOS et une version nouvelle appelée «deep depletion-enhancement» appauvrissement profond. Cette dernière emploie un nouveau type de MOST à canal n avec un dopage faible du type n au lieu de p. Le blocage du MOST à une tension de grille zéro n'est plus assuré par une jonction en inverse mais par la différence entre les potentiels de contact de la grille et de la couche épitaxiale faiblement dopée. Cette différence de potentiel a pour effet un appauvrissement en porteurs mobiles (électrons) à travers toute la couche jusqu'au saphir. Le choix du matériau de la grille est donc important; dans ce cas-ci on choisit du silicium polycristallin dopé fortement au bore. Sous l'influence d'une tension de grille positive le MOST est mis en état de conduction par l'intermédiaire d'une couche d'accumulation d'électrons qui se forme sous l'oxyde de grille.

Les caractéristiques électriques du MOST à appauvrissement profond sont presque identiques à celles du MOST normal. Du point de vue de la fabrication il apporte le grand avantage de supprimer un pas photolithographique puisqu'il ne faut plus créer les zones faiblement dopées p. Cependant, le procédé de fabrication devient plus critique en ce qui concerne les tolérances des paramètres physiques. Il est aussi possible de fabriquer un MOST à appauvrissement profond dans une technologie SOS à grilles métalliques; c'est le MOST à canal p qui est de ce type.

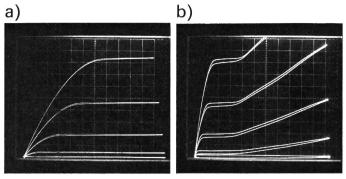

Fig. 6 Effet Kink: Courant de drain en fonction de la tension de drain

Courant de drain 10 μA/div. (vertical)

Tension de drain a) 0,5 V/div.; b) 2 V/div. (horizontal)

Paramètre: tension de grille en pas de 1 V

## 2.7 Facilité de la conception du circuit

Le fait que chaque élément électrique est parfaitement isolé des autres amène un nouveau degré de liberté en ce qui concerne la conception du circuit. Ainsi il est plus facile d'introduire des contre-réactions.

#### 3. Particularités et désavantages de la technologie SOS

#### 3.1 L'effet Kink

Comme l'intérieur du transistor MOS en SOS n'est plus contacté électriquement depuis le dessous de la plaquette, son potentiel varie selon le courant de fuite de la jonction de drain du MOST. Il s'ensuit que la caractéristique de pentode du MOST en SOS (fig. 6a) devient celle d'une triode si la tension d'alimentation est augmentée (fig. 6b). Cet effet a été nommé «Kink» (courbure, coude). Il est tout à fait possible de tenir compte de ces caractéristiques dans la conception du circuit. Souvent, cet effet ne se manifeste qu'à des tensions plus élevées que la tension d'alimentation normale du circuit, comme c'est p.ex. le cas des circuits horlogers.

#### 3.2 Les courants de fuites

La faible durée de vie des porteurs minoritaires dans la couche de silicium sur saphir est la cause des courants de fuites élevés des diodes et des transistors MOS en SOS. La dissipation d'énergie d'un circuit SOS en statique n'atteint donc pas la valeur extrêmement faible d'un circuit CMOS réalisé en silicium massif. En plus, on observe parfois des courants parasites le long des bords des îlots de silicium ou le long de l'interface silicium/saphir. Ce n'est qu'après un effort technologique énorme que les maisons engagées dans le SOS ont finalement pu éliminer les courants parasites et réduire les courants de fuites en dessous du nA par élément. Aussi faut-il se rendre compte que l'augmentation du courant statique pour le SOS est négligeable dans la plupart des applications vis à vis de la diminution du courant dynamique apportée par le SOS.

#### 3.3 L'autodopage par le saphir et l'interface silicium/saphir

Le succès de la technologie CMOS en silicium massif se base essentiellement sur le contrôle réussi des propriétés de l'interface entre le silicium et l'oxyde de grille. En SOS il y a une interface de plus, celle entre le silicium et le saphir. Il fallait appendre à contrôler ses propriétés aussi, ce qui est d'autant plus difficile que le saphir peut, à des températures très élevées, se présenter comme source de dopage d'aluminium.

## 3.4 Sensibilité aux transitoires

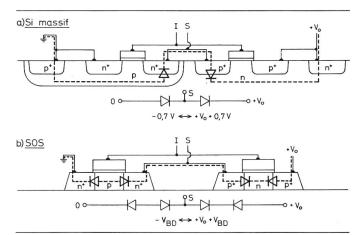

Il est bien connu que l'entrée d'un circuit CMOS doit être protégée contre les surtensions afin d'éviter un claquage des oxydes de grilles. D'autre part, la sortie d'un circuit CMOS en silicium massif est protégée automatiquement contre des tensions élevées par l'intermédiaire des diodes de drain et des

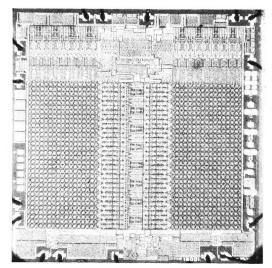

Circuits mémoire RCA en SOS CMOS à 1 kbit

|  | aŀ |  |  |

|--|----|--|--|

|  |    |  |  |

| Tension<br>d'alimentation<br>(V) | Temps<br>d'accès<br>(ns) | Puissance diss           |                         |                        |

|----------------------------------|--------------------------|--------------------------|-------------------------|------------------------|

|                                  |                          | en opération<br>(μW/bit) | en statique<br>(μW/bit) |                        |

| 10<br>5<br>5                     | 90<br>150<br>80          | 20<br>4<br>6             | 3 0.1                   | en vente<br>à paraître |

Fig. 7 Problème de la protection des sorties

I entrée  $V_0$  tension d'alimentation S sortie  $V_{\rm BD}$  tension de claquage des diodes

contacts au substrat n et au caisson p (fig. 7a). Par contre, cette protection des sorties n'existe pas en SOS faute de contacts aux zones faiblement dopées p et n. Les deux diodes têtebêche dans les MOST en SOS protègent la sortie seulement contre des tensions plus élevées que la tension de claquage de diode, qui peut être aussi grande que la tension de claquage de l'oxyde de grille (fig. 7b). Il faut donc incorporer en SOS une protection pour chaque sortie du circuit.

#### 4. Application de la technologie SOS

## 4.1 Généralités

A présent, la plupart des maisons engagées dans le SOS fabriquent des circuits pour leurs propres besoins et n'en vendent pas, ou alors seulement des circuits spéciaux à la demande selon les spécifications du client. C'est le cas des maisons américaines Hewlett Packard, Rockwell International, Hughes et Westinghouse, de la maison japonaise Toshiba et des maisons européennes EFCIS (France) et Siemens (Allemagne). Ce n'est que la maison américaine RCA qui offre des circuits intégrés en technologie SOS sur le marché des semiconducteurs; il s'agit de mémoires du type RAM, de compteurs rapides et d'un circuit horloger. En Suisse, l'industrie horlogère maintient un effort dans la technologie SOS au sein du Centre Electronique Horloger (CEH) afin de réaliser des circuits pour des montres à quartz avancées 6).

## 4.2 Mémoires du type RAM (Random Access Memory)

Les caractéristiques typiques des circuits mémoire RCA en SOS CMOS à  $1024\times1$  bit sont données dans le tableau I. Il s'agit de mémoires statiques qui n'ont pas besoin d'un signal d'horloge. La fig. 8 montre que, sur une surface d'à peu près 3,5 mm de côté, une telle mémoire contient approximativement 7000 transistors. Une cellule de mémoire occupe une surface de  $60~\mu\times60~\mu,$  et elle consiste en six transistors.

Une comparaison avec des circuits mémoires réalisés avec d'autres technologies fournit à peu près les énoncés suivants:

- Le circuit CMOS classique dissipe à peu près 10 fois plus d'énergie en opération et il est 2 fois plus lent. Cependant sa

- 6) Les maisons citées sont celles qui ont participé activement à l'«IEEE Workshop on SOS Technology» en août 1976. Il est clair que d'autres laboratoires de recherche ont également des activités SOS en cours.

consommation de courant en statique est 10 fois plus faible que celle du circuit SOS. Toutefois, dans les deux cas, le courant statique est petit comparé au courant dynamique.

– Les *circuits NMOS* (sur silicium massif) et les *circuits bipolaires p. ex. TTL* <sup>7</sup>) sont au moins aussi rapides que le SOS pour une tension d'alimentation donnée. Mais leur dissipation d'énergie est jusqu'à 100 fois plus élevée que celle du SOS.

Cette comparaison se base sur des produits du marché et elle ne tient pas compte des développements futurs qui ne sont certainement pas les mêmes pour toutes les technologies.

#### 4.3 Miniordinateurs

A part les mémoires ce sont surtout les microprocesseurs pour lesquels le SOS apporte de grands avantages. Ainsi, Hewlett Packard est en train de fabriquer un miniordinateur 16 bit, équivalent au modèle 3000, qui sera équipé en circuits SOS.

## 4.4 Applications horlogères

La plupart des montres à quartz actuellement sur le marché sont équipées d'un quartz oscillant en flexion à une fréquence de 32768 Hz et d'un circuit intégré en technologie CMOS ou I<sup>2</sup>L. Les éléments essentiels de ce circuit intégré sont un circuit oscillateur, une chaîne de division et des transistors de décodage et de sortie. A cette fréquence relativement basse le courant dynamique est comparable au courant statique.

Or, il s'avère que des quartz oscillant à une fréquence de l'ordre de 4 MHz présentent plusieurs avantages, tels que encombrement plus petit, sensibilité réduite au choc et à la température, coût de fabrication réduit, etc. A une telle fréquence, c'est le courant dynamique dans le circuit qui est prépondérant, et il est dissipé essentiellement dans le circuit oscillateur et dans les premiers étages de division. C'est avec la technologie SOS qu'on aura la plus grande chance de réaliser des calibres quartz à fréquence élevée avec une consommation de courant raisonnable. RCA a réalisé une version préliminaire d'un circuit SOS horloger dont les performances seront probablement encore susceptibles d'être améliorées. Les efforts entrepris au CEH ont montré qu'il est possible de réaliser en technologie SOS des diviseurs de fréquence CMOS dynamiques à ultra basse puissance. Une des difficultés additionnelles des circuits hor-

7) NMOS = n-channel MOS

TTL = Transistor-Transistor Logic

Fig. 8 Mémoire RAM 1024 bit en SOS (RCA)

logers est la faible tension d'alimentation (1,5 ou 1,4 V) qui nécessite un contrôle plus sévère des paramètres électriques que pour des circuits à 5 ou 10 V.

## 4.5 Synthétiseurs de fréquences

Dernièrement, un nouvel élément est apparu dans le domaine des émetteurs et récepteurs radio: la génération digitale des fréquences (digital tuning). A partir d'une seule fréquence maximum les fréquences plus basses sont obtenues par un diviseur digital de fréquence à rapport de division variable. Ce développement permettra de construire des récepteurs miniatures même dans le domaine des ondes ultracourtes. Il est évident que la technologie SOS est prédestinée pour ce genre de circuits et plusieurs maisons sont en train de l'exploiter dans ce but.

# 4.6 Circuits devant fonctionner en présence d'irradiations ionisantes

Comme un circuit SOS continue à fonctionner correctement en étant soumis à une douche d'irradiations ionisantes, le SOS présente un intérêt pour les applications militaires et la recherche spatiale. C'est grâce à cette propriété que les premiers efforts extrêmement coûteux ont été entrepris dans la technologie SOS. Aujourd'hui, pas seulement des circuits digitaux, mais aussi des circuits SOS CMOS linéaires ont été développés et – par une technologie modifiée – même des transistors bipolaires ont été fabriqués en SOS. Dans ces cas d'application, le SOS est parfois remplacé par une technologie appelée isolation diélectrique, qui consiste en la formation des îlots de silicium isolés à partir d'une plaquette de silicium massif.

## 4.7 Applications diverses

Entre autres le SOS a permis de réaliser des vannes à microondes et grâce à la transparence du saphir il sert aussi à des applications électro-optiques, p.ex. comme substrat pour téléviseurs miniatures à cristaux liquides contenant directement les transistors de commande.

## 5. La question de l'économie du SOS

#### 5.1 Système à haute performance

Le prix d'un système électronique à haute performance n'est en général pas déterminé par le prix des composants, mais il y a beaucoup d'autres facteurs qui interviennent, p. ex. le prix de l'engineering, l'avance du produit par rapport à la compétition, etc. Malgré un prix de revient élevé le SOS sera toujours utilisé dans ces cas, parce que c'est souvent le SOS seul qui rend un système envisagé possible.

## 5.2 Systèmes complexes

Dans un système complexe contenant plusieurs centaines de circuits intégrés, il est possible que la technologie SOS diminue le prix du système total parce que le producteur du système peut se passer d'un grand nombre d'organes périphériques tels que le refroidissement, des alimentations puissantes et des blindages électriques.

## 5.3 Circuits digitaux intégrés en général

Pour des raisons économiques un fabricant de circuits intégrés aimerait avoir à sa disposition une technologie unique qui permette de satisfaire à toutes les demandes du marché des circuits digitaux à un prix de revient favorable. A présent il semble que les technologies les plus proches de ce but soient le

I<sup>2</sup>L, le NMOS et le SOS CMOS. A vitesses plus ou moins égales le SOS est certainement la technologie avec la dissipation d'énergie la plus faible, mais à présent il est encore plus cher que le I<sup>2</sup>L et le NMOS à cause du prix du saphir. Cependant le progrès obtenu dans la méthode de croissance du saphir en forme de rubans ayant directement l'épaisseur désirée pour le SOS pourrait changer cette situation. La suppression du sciage et éventuellement du polissage des substrats en saphir ferait du SOS la technologie avec le meilleur rapport performance/prix, selon l'avis de certains producteurs.

#### **Bibliographie**

- [1] R. S. Ronen and F. B. Micheletti: Recent SOS technology advances and applications. Solid State Technology 18(1975)8, p. 39...46.

[2] H. Schlötterer: Epitaxiale Siliziumfilme auf Saphir für schnelle integrierte MOS-Schaltungen. NZZ-Beilage Forschung und Technik -(1975)227 vom 1. Oktober, S. 49...50.

- [3] S. S. Eaton: Sapphire brings out the best in C-MOS. Electronics 48(1975)12, p. 115...120.

- [4] P. Schwob et P. Saintot: Application de la technologie SOS aux circuits horlogers. Bulletin annuel de la Société Suisse de Chronométrie 7(1976)2, p. 229...234.

#### Adresse de l'auteur

P. Schwob, Dr ès sc. nat., Centre Electronique Horloger S.A., 2000 Neuchâtel.

## Literatur – Bibliographie

DK 621.314.26

SEV-Nr. A 621

Static power frequency changers. Theory, performance and application. By L. Gyugyi and B. R. Pelly. New York a.o., John Wiley, 1976, 8°, XIX/442 p., fig., tab. Price: cloth £ 20.−.

Die Theorie der verschiedenen, direkten, statischen Frequenzumformer (also ohne Gleichstromzwischenkreis) wird in einheitlicher Form dargestellt. Ausgehend von einer Übersicht über die Anforderungen und Lösungsmöglichkeiten werden die allgemein gültigen, theoretischen Grundlagen hergeleitet. Diese werden dann dazu benützt, die verschiedenen Umformertypen zu analysieren und deren Charakteristiken zu bestimmen. Die ganze Darstellung zeichnet sich durch einen logischen Aufbau und eine klare, gründliche Behandlung der Materie aus. Das Niveau entspricht etwa einer Nachdiplom-Vorlesung und verlangt, dass der Leser gewillt ist, sich eingehend mit den theoretischen Aspekten auseinanderzusetzen.

Das Buch bewegt sich aber ausschliesslich auf einer theoretischen Ebene, auch bei der Besprechung der Anwendungen von Umformern. Es enthält keinerlei praktische Hinweise wie Dimensionierungsunterlagen, Auswahl von Komponenten, Betriebserfahrungen oder irgendwelche Details über die tatsächliche Realisierung der verschiedenen, prinzipiellen Schaltungen. Wer einen statischen Umformer bauen will, wird deshalb mit diesem Buch allein nicht ans Ziel kommen. E. W. Aslaksen

DK 621.373.5: 621.382

SEV-Nr. A 496

Frequency Synthesizers. Theory and design. By Vadim Manassewitsch. New York a.o., John Wiley, 1976; 8°, XII/524 p., fig., tab. Price: cloth \$ 33 .- .

An die in der modernen Übertragungs-, Radar- und Messtechnik verwendeten Normalfrequenzgeneratoren werden hohe Anforderungen gestellt in bezug auf Frequenzbereich, Frequenzstabilität, Umschaltgeschwindigkeit und minimales systembedingtes Rauschen. Dementsprechend gross ist das Bedürfnis nach einem umfassenden einschlägigen, dem Stand der Technik entsprechenden Werk über Theorie und Praxis des Frequenzgeneratorbaus.

Der Autor geht dieses Thema vom Standpunkt des Entwicklungsingenieurs aus an, für den allgemeine theoretische Zusammenhänge weniger wichtig sind als die Lösung konkreter beim Entwurf von Frequenzgeneratoren auftretender Probleme. Im ersten Kapitel seines Buches (Frequency Synthesis) werden die heute üblichen Methoden der Frequenzsynthese kurz vorgestellt. Das zweite und dritte Kapitel (System Analysis, Shielding) befassen sich eingehend mit den Ursachen unerwünschter Frequenzkomponenten, die im System selber erzeugt oder von aussen induziert werden, sowie den Methoden ihrer Reduktion. Phaselocked loops (PLL) sind Gegenstand des vierten und fünften Kapitels (Analog, Digital Phase-Locked Loops), während den übrigen Bauelementen von Frequenzgeneratoren wie Mischer, Frequenzmultiplikations- und -divisionsschaltungen, VCOs usw. das sechste Kapitel (Basis Circuits) gewidmet ist. Im siebten Kapitel (Frequency Synthesizers) werden moderne Normalfrequenz-

generatoren verschiedener US-Firmen vorgestellt. Einen Überblick über Frequenznormale (Quarz-, Cäsium-, Rubidiumnormale) gibt das achte Kapitel (Frequency Reference Sources). Ein ausführlicher Index erleichtert die Verwendung des Buches als Nachschlagewerk.

Obwohl der Autor in der Einleitung sein Buch auch als Basistext für einen Nachdiplomkurs über Frequenzsynthese anbietet, ist es von Konzeption und Inhalt her ganz auf den praktisch tätigen Ingenieur ausgerichtet. Das ganze Buch hindurch achtet der Autor sorgsam auf jene Detailprobleme, die obwohl für den Theoretiker von sekundärer Natur, schlussendlich die Qualität des gebauten Gerätes wesentlich mitbestimmen. Leider bewirkt dies in Zusammenhang mit einem oft eher schwerfälligen Stil, dass Übersichtlichkeit und Klarheit der Linie etwas verloren gehen. Trotzdem wird dieses Buch, nicht zuletzt dank der vielen Blockschaltbilder, Skizzen und Tabellen, dem mit der Entwicklung von Normalfrequenzgeneratoren betrauten Ingenieur sowohl für das Studium praktischer Probeme wie auch als Nach-P. Kleiner schlagewerk nützlich sein.

DK 621.391.822

SEV-Nr. A 495

Noise reduction techniques in electronic systems. By Henry W. Ott. New York a. o., John Wiley, 1976; 8°, XX/294 p. fig., tab. Price: cloth \$ 24.55.

Methoden zur Störsignal-Reduktion in elektronischen Systemen ist eine sinngemässe Übersetzung dessen, was der Autor in diesem Buch behandelt. Damit ist bereits gesagt, dass nicht vorwiegend auf das Rauschen (noise) der aktiven und passiven Bauelemente, sondern hauptsächlich auf die durch Fremdstörquellen in die Schaltung gebrachten Geräuschsignale und deren Verringerung eingegangen wird.

Übersichtlich gegliedert werden die verschiedenen Einstreuprobleme (induktive, kapazitive und magnetische Einkopplung usw. von Fremdsignalen in die untersuchte Schaltung) analysiert und die daraus folgenden schaltungs- und gerätetechnischen Massnahmen hergeleitet. Es sind dies Probleme, die jedem, der elektronische Geräte entwickelt, von der Praxis her bekannt sind (z. B. Abschirmung von Signalleitungen, spezielle Leitungsführungen der Masseleitungen usw.), die aber in keiner entsprechenden Veröffentlichung derart umfassend aufgezeigt und behandelt werden.

Der Autor, Mitglied des technischen Stabes der Bell Telephone Laboratories, unterrichtet den in diesem Buch zusammengefassten Stoff seit 1970 in betriebsinternen Ausbildungskursen für Ingenieure und Techniker, was eine didaktisch ausgefeilte Präsentation bei Verwendung eines Minimums an mathematischen Hilfsmitteln gewährleistet.

Jedem einzelnen Kapitel ist ein umfangreiches Literaturverzeichnis angegliedert, wodurch ein vertieftes Eindringen in die behandelten Probleme wesentlich erleichtert wird. Im ganzen stellt dieses Buch für jeden, der nicht nur theoretisch mit elektronischen Schaltungen zu tun hat, ein wertvolles Hilfsmittel bei der Konzeption und Realisierung von Systemen und Geräten dar.

F. Grogg