**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins, des

Verbandes Schweizerischer Elektrizitätsunternehmen = Bulletin de l'Association suisse des électriciens, de l'Association des entreprises

électriques suisses

Herausgeber: Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätsunternehmen

**Band:** 68 (1977)

Heft: 2

**Artikel:** Integrated Injection Logic

Autor: Lohstroh, J.

**DOI:** https://doi.org/10.5169/seals-914978

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

## Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 09.08.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# BULLETIN

des Schweizerischen Elektrotechnischen Vereins de l'Association Suisse des Electriciens

des Verbandes Schweizerischer Elektrizitätswerke de l'Union des Centrales Suisses d'Electricité

# Elektrotechnik – Electrotechnique

# Moderne Technologien in der Elektronik

Über dieses Thema führte der SEV am 11. November 1976 in Biel eine gut besuchte Informationstagung durch. Wir veröffentlichen nachfolgend die fünf Vorträge in leicht gekürzter Form. Auf Seite 70 befindet sich zudem eine Tabelle mit der Bedeutung der verwendeten Abkürzungen.

# **Integrated Injection Logic**

By J. Lohstroh

621.3.049.721.14

$I^2L$  fulfils the most stringent boundary conditions for LSI: high packing density and low power consumption. Analog, TTL and  $I^2L$  circuitry can be combined on the same chip using existing bipolar technologies. For speeds up to 50 ns the existing technologies can be used; for higher speeds up to 3...5 ns new generation technologies have to be introduced. In this article both an introduction and a survey of the state of the art of  $I^2L$  is given.

I<sup>2</sup>L erfüllt die härtesten an LSI gestellten Randbedingungen: hohe Packungsdichte und niedriger Leistungsbedarf. TTL und I<sup>2</sup>L-Schaltungen können zudem auf demselben Plättchen mittels bekannter bipolarer Technologie kombiniert werden. Für Geschwindigkeiten bis 50 ns sind bekannte Technologien verwendbar; für höhere Geschwindigkeiten bis 3...5 ns sind neue Technologien notwendig. Der Aufsatz gibt eine Einführung und einen Überblick über den Stand der Technik von I<sup>2</sup>L.

I<sup>2</sup>L remplit les conditions les plus strictes posées à la LSI: densité élevée et consommation de puissance faible. De plus, les circuits TTL et I<sup>2</sup>L peuvent être combinés sur une seule puce au moyen des technologies bipolaires existantes. Pour une vitesse de 50 ns, les technologies existantes sont utilisables, pour des vitesses supérieures jusqu'à 3...5 ns de nouvelles technologies doivent être introduites. L'article présente une introduction et une vue d'ensemble sur l'état de la technique de la technologie I<sup>2</sup>L.

#### 1. Introduction

Since 1972, Integrated Injection Logic, I<sup>2</sup>L, the new approach to bipolar LSI<sup>1</sup>) design, is catching the imagination of logic designers throughout the world. The new logic was simultaneously presented by two research laboratories at the International Solid State Circuits Conference in Philadelphia, USA [1; 2]<sup>2</sup>). After four years of intensive research and preproduct development, the semiconductor industry is beginning to understand I<sup>2</sup>L, and the first products are now available [3].

The succes-story of I<sup>2</sup>L is easily explained. Namely the most stringent boundary conditions for LSI, good packing density and low power dissipation are fulfilled by this logic. Moreover I<sup>2</sup>L can be made in existing bipolar processes, which means that every bipolar semiconductor house is able to produce it. Because of the existing process, I<sup>2</sup>L can be easily combined with other types of logic and even analog circuits on the same chip.

Undoubtedly, for a four years old LSI approach, I<sup>2</sup>L has made a dramatic impact. But the lingering question is whether

1) Large Scale Integration.

2) References are shown at the end of the paper.

I<sup>2</sup>L will make it as a mainline digital technology in important areas such as microprocessors and memories where the main competitor, the metal oxide semiconductor (MOS)-LSI is already dominating. A mixture of costs, process availability, technical specifications, and second sourcing will influence the final outcome.

#### 2. Origin of the I<sup>2</sup>L gate

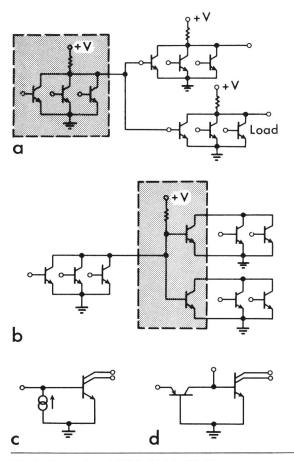

Injection logic derives its layout from the old direct-coupled transistor logic (DCTL) structure shown in Fig. 1a [4; 5]. The circuit within the dashed lines consists of a number of transistors in parallel. Clearly, when one or more of them are ON they act as a short circuit, and no current is supplied to the load gates. Conversely, when they are all in the OFF state, current flows to the bases of the transistors in the load gates.

If the two transistors that have their bases connected are placed in a common region, the result is the circuit between the dashed lines in Fig. 1b. Next, the resistor in Fig. 1b is replaced by an active current source (to be described later), and transistors with connected bases are replaced by a multi-

collector transistor, an easy thing to do because all the DCTL transistors have a common emitter that is connected to ground. This basic I<sup>2</sup>L configuration is presented in Fig. 1c.

The simple pnp-transistor shown in Fig. 1d can serve as the current source, by injecting minority carriers into the emitter region of the npn-transistor.

In any case, it is readily seen that the base of the npn transistor is common to the collector of the current source, while the base of the pnp-transistor is common to the emitter of the npn-transistor. The emitter of the pnp, common for all gates, is called the injector. On silicon, the entire gate takes up the space of a single multi-emitter transistor. Fig. 1d shows the the symbol of the I<sup>2</sup>L gate and the symbol of the very well known nand gate (DCTL, TTL<sup>3</sup>), etc.). The I<sup>2</sup>L gate has only one input and multiple outputs; the logic has to be made now in the wired logic technique.

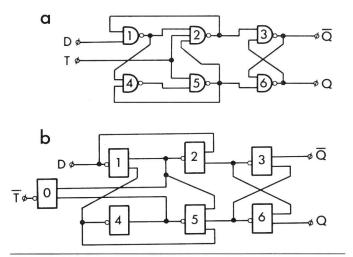

To translate an original scheme with nand symbols to I<sup>2</sup>L symbols is very simple. Every nand-gate has to be replaced by an I<sup>2</sup>L gate with n collectors if a fan-out of n is used with the original nand-gate. The input of the I<sup>2</sup>L gate is to be connected with the outputs of the gates which contributes to the fan-in of the corresponding nand. Further, different inputs of I<sup>2</sup>L gates are not allowed to be interconnected. Fig. 2a shows a standard D-flip-flop built up with I<sup>2</sup>L gates. As it is not allowed to interconnect the inputs of the I<sup>2</sup>L gates 2 and 5 for the T node, an extra gate must be introduced with T at the input (Fig. 2b).

- 3) TTL = Transistor-Transistor Logic.

- 4) ECL = Emitter-Coupled Logic.

Fig. 1 Conversion of DCTL (a) into I<sup>2</sup>L (d)

by placing the transistors with connected bases into a common region (b) and further replacing them by a multi-collector npn-transistor (c)

#### 3. Building I<sup>2</sup>L gates with a standard bipolar technology

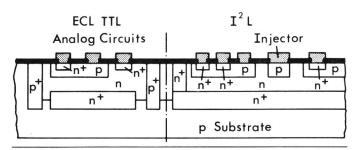

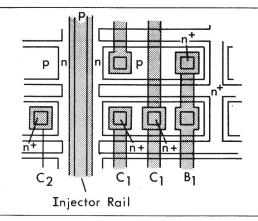

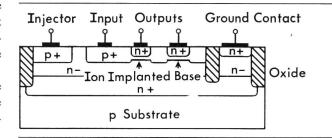

Fig. 3 shows the cross-section of a typical circuit that combines I<sup>2</sup>L gates with conventionally isolated transistors. Fabrication of the circuit starts with a p-type substrate containing discrete n<sup>+</sup>-buried layers. The buried layer in the I<sup>2</sup>L part of the circuit acts as a common emitter for the npn transistors and as a base for the pnp injector, while in conventional TTL or ECL<sup>4</sup>) logic it acts as collector for the isolated structures.

After the n-type epitaxial layer has been grown, a deep p<sup>+</sup>-diffusion is performed to isolate the conventional components, while in the I<sup>2</sup>L part the gates are isolated from each other by a deep n<sup>+</sup>-diffusion. A p-type diffusion is then carried out to form all base regions and emitters of the lateral pnp transistors (the injectors of the I<sup>2</sup>L gate). Next, a shallow n<sup>+</sup>-diffusion forms both the collectors in the I<sup>2</sup>L part of the circuit and the emitter and the collector contact regions for the conventional transistor structures. Two additional mask steps are needed for the contact holes and metallization. In all, only seven masks are required to manufacture both conventional isolated and I<sup>2</sup>L transistors on the same chip. From this fabrication scheme it appears that I<sup>2</sup>L can be combined on the same chip with any electronic circuit, analog or digital, which is made in the bipolar process.

#### 4. Lay out and characteristics of the I2L gate

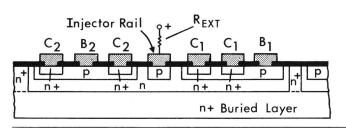

Fig. 4 shows a cross section of an I<sup>2</sup>L structure with two gates with the injector in the center. Each gate has two collectors and one contact to the base. The places of collectors and base contact can be interchanged in order to make simple lay-

Fig. 2 (a) Standard D-flip-flop built up with nands (a) and (b) with I<sup>2</sup>L gates (wired logic system)

Fig. 3 Possibility of combining the bipolar I<sup>2</sup>L technique with conventionally isolated transistors on one chip

Fig. 4 Cross-section of an  $I^2L$  structure with two gates with the injector in the center

The injector forms the emitter of the lateral pnp-transistor; holes are injected to both base areas of the multicollector npn-transistors. Heavily doped deep n<sup>+</sup> isolation regions increase the current gain of the inverse operated npn-transistors and kill the parasitic effects of parasitic pnp-transistors between adjacent gates

outs possible (Fig. 5). For regular circuits, e.g., shift registers, a packing density of 400 gates/mm<sup>2</sup> can be reached in a technology with  $5 \mu m$  details; the packing density drops to about  $250 \text{ gates/mm}^2$  for irregular structures [4].

The most characteristic fact in  $I^2L$  is that the npn transistor is used in an inverse way. The low doped n-epilayer is the emitter and the high doped  $n^+$ -diffusion at the top is the collector. This inverse mode of operation influences both the current amplification  $\beta_{\rm up}$  and the cut-off frequency  $f_{\rm Tup}$  of the transistor. In general  $\beta_{\rm up}$  is much lower than  $\beta_{\rm down}$  and also  $f_{\rm Tup}$  is much lower than  $f_{\rm Tdown}$ . Moreover  $\beta_{\rm up}$  is affected by the presence of the merged pnp-transistor to which a back injection from npn base to pnp emitter takes place. If no recombination is assumed in the base of the pnp transistor it can be calculated [6] that

$$\beta_{\rm up \ eff} = \frac{1}{\frac{I_{\rm p0}}{I_{\rm n0}} + \frac{1}{\beta_{\rm up}}} \tag{1}$$

in which  $I_{\rm p0}$  and  $I_{\rm n0}$  are the saturation currents of the pnp and npn transistors respectively and  $\beta_{\rm up}$  the  $\beta$  of the inverse operated npn-transistor. In fact the  $\beta_{\rm up}$  eff is not allowed to be smaller than 2 or 3, in order to obtain a sufficient noise margin. With  $\beta_{\rm up}=5$  and  $I_{\rm p0}/I_{\rm n0}=0.1, \beta_{\rm up}$  eff  $\approx 3$ .

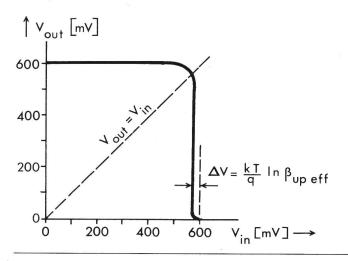

Fig. 6 shows the  $V_{\rm in}-V_{\rm out}$  characteristic of an I<sup>2</sup>L inverter. It can be calculated [6] that the voltage noise margin equals

$$\Delta V = \frac{kT}{q} \ln \beta_{\text{up eff}} \tag{2}$$

With  $\beta_{\rm up\ eff}=3$ ,  $\Delta V$  will be about 27 mV. If  $\beta_{\rm up\ eff}$  becomes lower than one, the noise margin becomes negative, which means that the gate is useless. Therefore  $\beta_{\rm up\ eff}$  must be >1.

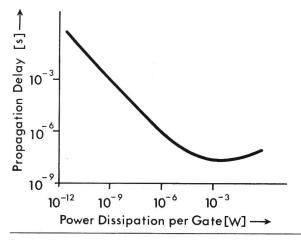

Fig. 7 shows a curve representing measured propagation delay times versus power dissipation. This result was obtained from a five-stage closed-loop inverter chain with one collector for each inverter. The measured speed-power product was 1 pJ/gate for dissipation levels between 1 nW and 7  $\mu W$  per gate. In the curve three dissipation levels are to be distinguished.

At low dissipation levels, i.e., between 1 nW and 1  $\mu$ W, the propagation delay time is determined by junction and parasitic capacitances. The propagation delay time  $\tau$  will be proportional to the time needed to charge and discharge these capa-

Fig. 5 Lay-out example

As the places of collectors and base contact can be interchanged, very simple lay-outs can be made

citances. As Q = CV and t = Q/I,  $\tau$  will be proportional to CV/I. The dissipation D will be D = VI, where V is the logic voltage swing. This logic voltage swing is almost equal to the voltage measured across the forward-biased junction of the injector. From this it follows that the speed-power product  $\tau D$  is proportional to  $CV^2$ , which is constant.

At medium dissipation levels, i.e., between 1  $\mu$ W and 1 mW, the main influence on the propagation delay time comes from

Fig. 6 Typical  $V_{\rm in}-V_{\rm out}$  characteristic of an I<sup>2</sup>L inverter It can be calculated that the voltage noise margin equals  $\varDelta V$

Fig. 7 Typical propagation delay of an I<sup>2</sup>L inverter versus power supplied to this inverter

the active charges in the transistors, of which the active charge in the common epiregion (hole storage) is by far the most important. These active charges are proportional to the current, and therefore the propagation delay is independent of the dissipation.

At high dissipation levels, above 1 mW, the series resistance of the base prevents fast charging and discharging of the active charges, and therefore the propagation delay time increases at increasing dissipation levels.

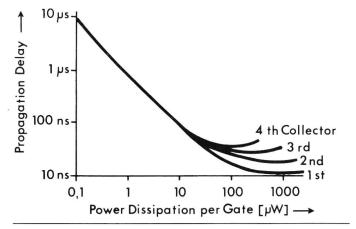

In multiple collector gates, the influence of the base series resistance increases for collectors which are further remote from injector and/or base contact than other collectors. Very often they don't reach the low horizontal part of the  $\tau D$ -curve and exhibit longer delay times. Fig. 8 shows the delay times versus power for the four collectors of a 4-collector-I²L-gate. For low power levels the delay-times are the same, for medium and high power levels a dispersion appears; the 4th collector which is the most remote collector from the injector becomes the slowest one. For worst case delay calculations in logic designs, the worst case delay time of the 4th collector must be taken.

At low dissipation levels, where the  $\tau D$ -product is proportional to  $CV^2$ , the speed and the  $\tau D$ -product can only be improved by decreasing the capacitance C. As C is proportional to the area of a gate, it is important to design the smallest gates possible. Power-delay products of 0.1 pJ have been demonstrated using 5  $\mu$ m lay-out rules [4]; with still smaller lay-out rules even smaller  $\tau D$ -products can be reached.

The minimum delay time depends on  $f_{\rm T\,up\,npn}$ ,  $\beta_{\rm up\,eff}$ ,  $I_{\rm p0}/I_{\rm n0}$ ,  $f_{\rm T\,pnp}$  and  $\alpha_{\rm pnp}$ . The ratio  $I_{\rm p0}/I_{\rm n0}$  not only determines  $\beta_{\rm up\,eff}$  but also indicates (as a back-injection factor) that for a part the low  $f_{\rm T\,pnp}$  must be taken into account in the switching speed calculations. This means that even in the case that  $f_{\rm T\,up\,npn}$  is extremely high, the switching speed is fully governed by  $f_{\rm T\,pnp}$  due to the back injection. The higher the  $I_{\rm p0}/I_{\rm n0}$  ratio, the more important the influence of the low  $f_{\rm T\,pnp}$  will be. Therefore, for a really high speed I<sup>2</sup>L technology, both the  $f_{\rm T}$ 's of the inverse operated npn and the lateral pnp must be increased.

The base series resistance can already influence the switching speed of the first collector. The switching speed of the 2nd, 3th and 4th collector is in any case affected by this series resistance at high power levels.

One remark must be made about the  $\alpha$  of the pnp-transistor. At low power levels the  $\alpha$  of the pnp transistor can be very near to 1 (which means that there is a good emitter efficiency and also a very low recombination in the pnp-base). At high

Fig. 8 Delay time versus power for a four-collector I<sup>2</sup>L gate

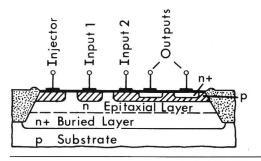

g. 9 Cross-section of a typical fast-I<sup>2</sup>L structure [8] The epilayer is very thin (< 2 μm) and the isolation is a passive one (oxide)</p>

power levels the  $\alpha$  of the pnp decreases where the high injection effect is one of the occurring effects. This means that a reasonable part of the power supply current goes via the base of the pnp-transistor directly as a loss current to earth; sometimes this effect deviates the  $\tau D$ -curve earlier from the straight constant- $\tau D$ -product-line than one should expect.

All the here described effects imply that the high power level behaviour of I<sup>2</sup>L is very complex and that very dedicated experiments must be done in order to discover all the different contributions of the various effects.

#### 5. Fast I<sup>2</sup>L

As explained in the previous chapter, the minimum speed of  $I^2L$  depends strongly on the cut-off frequencies of the inverse operated npn and pnp-transistors. In processes with a relatively thick epilayer (7...10  $\mu$ m) the inverse operated npn-transistor is rather slow due to a considerable storage of holes which are injected from the base into the epilayer. This means that for these processes the maximum speed is in the range of 25...50 ns. In order to reach faster  $I^2L$ , thinner epilayers have to be used; the thinner the epilayer, the faster the npn-transistor.

Together with a thin epilayer, oxide isolation can be used (Fig. 9) in order to eliminate side-wall capacitances. If at the same time, the lateral dimensions are decreased, a very dense  $I^2L$  can be made with a low  $\tau D$ -product for the low power levels and with a short delay time at high power levels. Delay times of 3...5 ns have been reported [7...9], with  $\tau D$ -products in the range of 0.5 pJ. In one of the published high speed  $I^2L$  processes, an extra loss diode is included [7], which fixes  $\beta_{\rm up\ eff}$  at a value of about 3 (too high a  $\beta_{\rm up\ eff}$  causes too much saturation and consequently a longer delay time). Preferably two base diffusions are made [7; 8]; a low doped diffusion (or ion implantation) for the intrinsic base and a high doped diffusion (or ion implantation) for the extrinsic base in order to keep the base series resistance as low as possible.

A switching speed of 3 ns seems to be the physical limit of  $I^2L$  which is made with lateral pnp-transistors. The low  $f_{\rm T\,pnp}$  and a  $\alpha$ -decrease at high power levels cause this limit.

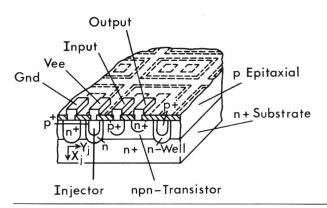

#### 6. Other types and technologies of I<sup>2</sup>L

Another way to manufacture I<sup>2</sup>L is to use a p-epilayer on a n<sup>+</sup>-substrate. The p-epi forms the base of the npn-transistor and the pnp-transistor is made by two diffusions through one hole (Fig. 10). Power-delay products between 0.06 and 0.1 pJ, and a minimum delay time of 10 ns have been reported [10]. The analog circuits and other types of logic can be made on the same chip in this technology using the Collector Diffused Isolation (CDI) concept [11].

Fig. 10 Cross-section of an I<sup>2</sup>L technique by which the pnp-transistor is made with two diffusions through the same hole [10]

In this structure the pnp-base is made with the epilayer and is injected on four sides by the pnp-transistor

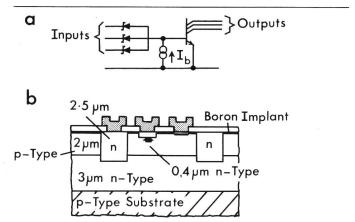

Quite different is the method of substrate fed I<sup>2</sup>L (SFL = Substrate Fed Logic) [12]. Here, two epitaxial layers are used on a heavily doped p-type substrate. The p-type epitaxial layer, which forms the base of the npn-transistor, is lightly doped, allowing the fabrication of Schottky contacts. This gives rise to an extremely powerful multi-input, multi-output logic element on a single base land. Fig. 11 shows the SFL scheme, and the SFL structure. The pnp transistor is a vertical one; the substrate is the emitter, the n-epilayer the base, and the p-epilayer the collector. Due to the compact structure and the low capacitances very low power delay products (0.05 pJ) have been measured [12]. However the low conductivity epilayers introduce large series resistances which implies that the minimum delay at high power levels is quite poor (> 10 ns).

VIL (Vertical Injection Logic) [13] is a I<sup>2</sup>L type just between normal I<sup>2</sup>L and SFL. With an extra p-buried layer a vertical pnp is created which injects holes from this buried layer upwards to the base of the npn-transistor. A power delay product

Power delay product  $(\tau D)$  and minimum delay times  $(\tau)$  of the described  $I^2L$  types

| ٦ | al | hl | P | T |

|---|----|----|---|---|

|                                                  |        | τD-product low power region [p] | τ <sub>min</sub> high power region [ns] |

|--------------------------------------------------|--------|---------------------------------|-----------------------------------------|

| I <sup>2</sup> L; 10 μm clearances<br>710 μm epi | [1]    | 12                              | 50                                      |

| I <sup>2</sup> L; 5 μm clearances<br>5 μm epi    | [1; 4] | 0.10.4                          | 25                                      |

| I <sup>2</sup> L double diffused injector        | [10]   | 0.060.1                         | 10                                      |

| SFL                                              | [12]   | 0.05                            | 10                                      |

| VIL                                              | [13]   | 0.07                            | 9                                       |

| Schottky I <sup>2</sup> L<br>10 µm epi           | [16]   | 0.51                            | 2550                                    |

| CHIL<br>1.5 μm epi                               | [9]    | > 1                             | 15                                      |

| Fast I <sup>2</sup> L<br>12 µm epi               | [79]   | ≈ 0.3                           | 35                                      |

Fig. 11 Logic diagram (a) and Cross-section (b) of the SFL structure [12]

of 0.07 pJ and a minimum delay of about 9 ns have been reported.

Schottky I<sup>2</sup>L uses a Schottky diode in series with each collector in order to reduce the logic swing of the base of the I<sup>2</sup>L transistor [14...16]. As the  $\tau D$ -product is proportional to  $CV^2$  a reduction of this product by a factor of 4 can be expected if the logic swing is reduced from about 700 mV to 300 mV. Improvements in this range have been measured. Fig. 12 gives

Fig. 12

Diagram of Schottky I<sup>2</sup>L

Input

Outputs

the logical scheme of Schottky I<sup>2</sup>L. With a Schottky diode with a forward voltage of about 400 mV the reduced voltage swing is 300 mV indeed. The  $\tau D$ -product improvement exists in the low power range only. The minimum delay time is governed by active charge and series resistances; both will not be reduced by the Schottky diode in series with the collector.

CHIL (Current Hogging Injection Logic) is a combination of I<sup>2</sup>L and Current Hogging Logic (CHL) [9; 17]. The addition of current hogging gates produces an I<sup>2</sup>L gate with more than one input gate, which makes the logic more powerful. Fig. 13 gives the cross-section. The higher  $\tau D$ -product (>1 pJ) and slower speed of CHL makes, that the combination of CHL and I<sup>2</sup>L does not lead to a fast logic with a very low power delay product. The manufacturing and the lay-out however are very simple, and in a thin epilayer process with oxide isolation, minimum delay times of 15 ns have been reached [9].

In Table I all power delay products (for the low power region) and all minimum delay times (for the high power region) of the described injection logic types are summarized.

Fig. 13 Cross-section of a reported CHIL structure [9; 17]

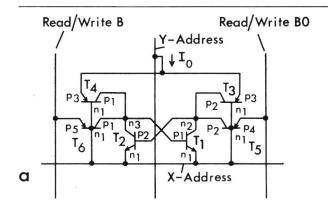

Fig. 14 Equivalent circuit diagram and cross-section of the structure of an injection-coupled RAM-cell [18]

#### 7. Memories

I<sup>2</sup>L can be used successfully for both static and dynamic memories.

Fig. 14 shows the circuit diagram and a cross-section of a very small static memory cell [18]. This memory cell consists of two cross coupled I<sup>2</sup>L gates with a common injector for the power supply. Two extra pnp transistors form a connection to the read- and write-circuits. For reading, the outer pnp transistors are biased as collectors which partially collect the minority carriers that are injected by the ON-transistor into the adjacent n-region. Thus by sensing the differential currents in the bit lines it can be detected which of the npn transistors is ON. For writing, the cell power supply is momentarily turned off, and a current is supplied to the proper bit-line pnp. This causes a minority injection into the n-region which is partially collected by the p-base of the adjacent npn transistor, so that this transistor is turned on.

The cell is very small, viz.  $2000 \, \mu m^2$ , which is equal to a packing density of  $500 \, \text{cells/mm}^2$ . This cell size can be reduced to  $700 \, \mu m^2$  by applying passive (oxide) isolation. For a 4096-bit-chip an access time of about 50 ns has been predicted from measurements simulating a  $64 \times 64$  array. The standby power is smaller than  $0.1 \, \mu \text{W/bit}$  [18].

A similar static memory cell has been reported which requires no row-isolation diffusion, and for which the substrate is common for all the memory cells in the whole array [19]. In this design a double layer metallization is used. With a technology based on 7  $\mu$ m line widths a packing density of 256 bit/mm² is achieved, and a standby current of 0.7  $\mu$ W/bit has been measured. Complete selection, read- and write-circuitry are also given.

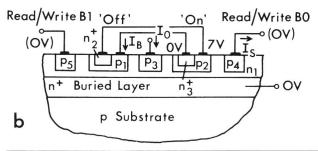

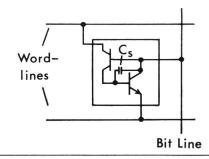

In contrast to the six-transistor static cell, a dynamic  $I^2L$  can be made with only two transistors [20; 21]. The circuit diagram of the cell is shown in Fig. 15. A memory capacitance  $C_8$  is assumed to lie between the base and the collector of the

npn-transistor (also between collector and base of the pnptransistor, due to the merged structure). The capacitance  $C_{\rm s}$ is charged during reading with a negative pulse at the W<sub>n</sub>-line; a charge of  $\beta$  times the charge of the memory capacitance can be measured at the bit-line. Discharging  $C_8$  can be done selectively by applying the appropriate pulses on both the W<sub>p</sub>-line and the bit-line in order to forward biase the merged pnptransistor. The read-process is destructive; therefore, after reading, the right information has to be written back. In the standby state leakage currents affect the logic «1» state, which means that the cell must be refreshed (every 2 ms). Typically, the storage capacitance is about 0.1 pF, and the  $\beta$  of the npntransistor is about 70, making the effective coupling capacitance about 7 pF, which is enough to assure an easily detectible logic swing of about 200 mV. The area of one cell can be very small ( $< 700 \, \mu m^2$ ).

Fully functional parts have been manufactured with 140 ns access time, 200 ns cycle time, 400 mW active power dissipation and 80 mW standby power. How this memory will compete with MOS dynamic memories is still an open question.

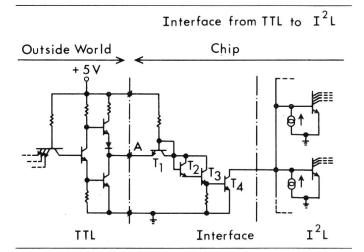

#### 8. Interface circuits, TTL compatibility

The noise immunity of  $I^2L$  is in general too low to interconnect  $I^2L$  chips without noise-buffering interface circuits. As TTL circuits can be made on the same chip, it is advantageous to do so. This means that the  $I^2L$  logic also can be combined with any other TTL circuit.

Generally a TTL load current is 1.9 mA per fan out for a low logic state and 20 µA or less for its high condition. Since an I<sup>2</sup>L gate operates at a current level between 1 and 20 μA per gate (in the low power range), two types of interface circuits are necessary: one at the gate inputs as an interface from TTL to I<sup>2</sup>L, and one at the gate output as an interface from I<sup>2</sup>L to TTL. The circuit diagram of the TTL/I<sup>2</sup>L interface is shown in Fig. 16. For the situation where the TTL gate is at its low logic level, the realization of the proper interface condition follows automatically, because a normal TTL input current will flow if appropriate resistor values are chosen. For the high logic TTL condition, however, care must be taken that the inverse current gain of I<sup>2</sup>L transistor T<sub>1</sub> does not affect the input current of the TTL transistor. Normally this inverse current gain has to be reasonably high for proper gate operation. The way around this dilemma is to short-circuit the collector-base junction of transistor T<sub>1</sub> in the interface circuit and add an extra diode T2 to make the input threshold voltage again equal to the required TTL threshold voltage [5].

The interface from I<sup>2</sup>L to TTL can be made with current amplification stages. The lay-out of the current amplifier depends on the current level of I<sup>2</sup>L and on the number of TTL fan-outs required [5].

Fig. 15 Equivalent circuit diagram of a static I<sup>2</sup>L RAM-cell [20; 21]

Fig. 16 Example of an I<sup>2</sup>L to TTL interface circuit The current level of I2L is amplified to switch the high current level TTL circuitry. Transistors T1 and T2 serve as current amplifiers

#### 9. Applications and conclusion

Applications for I<sup>2</sup>L are numerous. Watches, shutter circuits for camera's, digital-to-analog converters, digital voltmeter circuits, high frequency counters, digital tuners, read-only memories, shift registers, converters of all kinds, control logic for complex calculators, frequency deviders for electronic organs, remote control for TV-sets, microprocessors, telephone tone-dialing systems, alpha-numeric display circuits, motordrive control, random access memories, timing controls, citizens' band radio circuits, phase-locked-loop circuits, automotive electronics, are only a small number of random choosen examples of I<sup>2</sup>L applications. Especially the combination with linear circuits makes I2L very suitable for small low cost systems.

I<sup>2</sup>L reduces a logic gate to a single complementary transistor pair. A vertical npn-transistor with multiple collectors as inverters and a lateral pnp-transistor serve both as current source and load, and no ohmic resistors are required for either source or load function. Packing densities up to 250 gates/mm<sup>2</sup> have been demonstrated. For speeds up to 50 ns existing bipolar technologies can be used; for higher speeds up to 3...5 ns new generation technologies have to be introduced.

#### Literature

- K. Hart and A. Slob: Integrated injection logic: A new approach to LSI. IEEE Journal Solid-State Circuits 7(1972)5, p. 346...351.

- H. H. Berger and S. K. Wiedmann: Merged transistor logic (MTL) A low-cost bipolar logic concept. IEEE Journal Solid-State Circuits 7(1972)5, p. 340...346.

- L. Armstrong and L. Altman: I2L getting a second look. Electronics 49(1976)6, p. 80...82

- N. C. de Troye: Integrated injection logic Present and future. IEEE Journal Solid-State Circuits 9(1974)5, p. 206...211.

C. M. Hart, A. Slob and H. E. J. Wulms: Bipolar LSI takes a new direction with integrated injection logic. Electronics 47(1974)20, p. 111...118.

- F. M. Klaassen: Device physics of integrated injection logic. Trans. IEEE ED 22(1975)3, p. 145...152.

C. Mulder and H. E. J. Wulms: High speed integrated infection logic

- C. Mulder and H. E. J. Wulms: High speed integrated interpretation (I<sup>2</sup>L). IEEE Journal Solid-State Circuits 11(1976)3, p. 379...385.

- [8] R. E. Crippen a. o.: Microprogram sequenzer utilizing I<sup>3</sup>L technology. IEEE International Solid-State Circuits Conference, February 1976, Digest of Technical Papers, p. 98...99.

- [9] R. Müller and J. Graul: CHIL and I<sup>2</sup>L with passive isolation. Proc. first European Solid State Circuits Conference, September 1975, Digest of Technical Papers, p. 28...29.

- Y. Tokumaru a, o.: IFL with self-aligned double-diffusion injector. IEEE International Solid-State Circuits Conference, February 1976, Digest of Technical Papers, p. 100...101.

- [11] B. T. Murphy and V. J. Glinski: Transistor-transistor logic with high packing density and optimum performance at high inverse gain. IEEE Journal Solid-State Circuits 3(1968)3, p. 261...267.

[12] V. Blatt, P. S. Walsh and L. W. Kennedy: Substrate fed logic. IEEE Journal Solid-State Circuits 10(1975)5, p. 336...342.

[13] T. Nelsone, and Vertical injection logic. IEEE International Electron.

- [13] T. Nakano a. o.: Vertical injection logic. IEEE International Electron Devices Meeting, Washington, December 1975, Digest of Technical Devices Meeting, V Papers, p. 555...558.

- H. H. Berger and S. K. Wiedmann: Schottky transistor logic. IEEE International Solid-State Circuits Conference, February 1975, Digest of Technical Papers, p. 172...173.

H. H. Berger and S. K. Wiedmann: Advanced merged transistor logic

- by using Schottky junctions. Micro-Electronics 7(1976)3.

- [16] F. W. Hewlett: Schottky I<sup>2</sup>L. IEEE Journal Solid-State Circuits 10(1975)5, p. 343...348.

- R. Müller: Current hogging injection logic A new logic with high functional density. IEEE Journal Solid-State Circuits 10(1975)5, p. 348...352.

- Wiedmann: Injection-coupled memory: a high-density bipolar memory. IEEE Journal p. 332...337. Solid-State Circuits 8(1973)5,

- [19] F. Camerik and A. Slob: Design of a bipolar static RAM with low dissipation based on integrated injection logic. Colloque Interna-tional sur les Mémoires, Paris, Octobre 1973, Digest of Technical Papers, p. 136...145.

- W. B. Sander and J. M. Early: A 4096x1 (I<sup>3</sup>L) bipolar dynamic RAM. IEEE International Solid-State Circuits Conference, February 1976, Digest of Technical Papers, p. 182...183.

- W. B. Sander, W. H. Shepherd and R. D. Schinelle: Dynamic I<sup>2</sup>L random-access memory competes with MOS designs. Electronics 49(1976)17, p. 99...102.

#### Author's address

J. Lohstroh, Ir., Philips Research Laboratories, Eindhoven NL.