Zeitschrift: Bulletin des Schweizerischen Elektrotechnischen Vereins

Herausgeber: Schweizerischer Elektrotechnischer Verein; Verband Schweizerischer

Elektrizitätswerke

**Band:** 64 (1973)

**Heft:** 20

**Artikel:** Volldecodierter MNOS-Speicher in Ein-Kanal-Technik mit neuartigen

Speichertransistoren

Autor: Horninger, K.H.

**DOI:** https://doi.org/10.5169/seals-915608

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

## **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

# Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 30.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Volldecodierter MNOS-Speicher in Ein-Kanal-Technik mit neuartigen Speichertransistoren 1)

Von K. H. Horninger

621.377.622.25 : 621.382.323

Bei einem MNOS-Speichertransistor werden die Haftstellen an der Grenzschicht zwischen Siliziumdioxid und Siliziumnitrid durch Anlegen hoher Gatespannung umgeladen, dadurch die Einsatzspannung der Transistoren verschoben und die Information eingeschrieben. Zum Einschreiben muss an die Gateelektrode eine bezüglich des Substrates hohe positive oder negative Spannung angelegt werden. Spannungen mit beiden Polaritäten lassen sich jedoch in Schaltungen in Ein-Kanal-MOS-Technik nicht erzeugen.

Diese Schwierigkeit wird bei den vorgeschlagenen, neuartigen MNOS-Transistoren kurzer Kanallänge umgangen, bei denen das Einschreiben durch Anlegen einer Spannung der gleichen Polarität zwischen Gate und Source/Drain, und nicht durch Anlegen einer Spannung entgegengesetzter Polarität zwischen Gate und Substrat, erfolgen kann. Der dabei angewandte Effekt wird durch ein zweidimensionales Transistormodell beschrieben, das vor allem den Einfluss des elektrischen Feldes in der Verarmungszone zwischen Source und Drain beim Umladungsvorgang berücksichtigt.

Die grosse technische Bedeutung dieses Effektes besteht darin, dass die Information in den beschriebenen Speichertransistoren mit Spannungsimpulsen gleicher Polarität sowohl eingeschrieben als auch gelöscht werden kann. Damit kann ein Decodierer in einer Ein-Kanal-MOS-Technik auf demselben Chip wie die Speichermatrix integriert werden. Als Beispiel werden die Schaltung, der Entwurf und die Messergebnisse einer volldecodierten Speichermatrix mit 256 Elementen angeführt.

Dans un transistor MNOS à mémoire, les endroits d'adhérence à l'interface entre dioxyde et nitrure de silicium subissent une inversion de charge lors de l'application d'une tension de gâchette élevée, ce qui décale la tension de fonctionnement des transistors et enregistre l'information. Pour l'enregistrement, il faut appliquer à l'électrode de gâchette une tension positive ou négative élevée par rapport au substrat. Des tensions des deux polarités ne peuvent toutefois pas être produites dans des montages en technique MOS monocanal.

Cette difficulté est surmontée, dans le cas des transistors MNOS du nouveau genre proposé, à courte longueur de canal, l'enregistrement étant produit par application d'une tension de même polarité entre gâchette et source/drain, au lieu d'une tension de polarité contraire entre gâchette et substrat. L'effet utilisé est décrit par un modèle bidimensionnel de transistor, qui tient notamment compte de l'influence du champ électrique dans la zone morte entre source et drain, lors du processus d'inversion de la charge.

La grande importance technique de cet effet est que, dans ces transistors à mémoire, l'information peut être aussi bien enregistrée, qu'effacée, avec des impulsions de tension de la même polarité. Un décodeur peut ainsi être intégré, en technique MOS monocanal, sur la même puce que la matrice de mémoire. Le montage, le projet et les résultats de mesure d'une matrice entièrement décodée, de 256 éléments, sont décrits à titre d'exemple.

#### 1. Einleitung

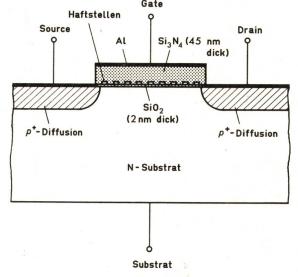

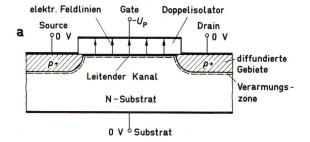

MNOS-VT-Transistoren (Metal-Nitride-Oxide-Semiconductor-Variable-Threshold, oft nur als MNOS-Transistoren bezeichnet) sind Isolierschicht-Feldeffekt-Transistoren, deren Gateisolator aus einer Siliziumdioxidschicht (SiO<sub>2</sub>) mit einer Dicke von etwa 2 nm und aus einer Siliziumnitridschicht (Si<sub>3</sub>N<sub>4</sub>) von ca. 50 nm Dicke besteht (Fig. 1). An der Oxid-Nitrid-Grenzschicht befindet sich eine grosse Anzahl von Haftstellen («Traps»), die durch grosse positive oder negative Gatespannungen umgeladen werden können. Dadurch weist der Transistor entweder eine hohe oder eine niedrige Einsatzspannung auf. Diese beiden Zustände können zur Speicherung der Information «0» und «1» verwendet werden.

Die Vorteile eines mit MNOS-Transistoren aufgebauten Speichers liegen in der Möglichkeit, ohne Energiezufuhr Informationen zu speichern (Non-Volatility) [1]<sup>2</sup>), in der Möglichkeit, in den Elementen die Information zu ändern, und in dem geringen Flächenbedarf (ein Transistor pro Speicherelement). Ein MNOS-Speicher ist damit in erster Linie für einen Festspeicher geeignet, dessen Information nur gelegentlich geändert wird.

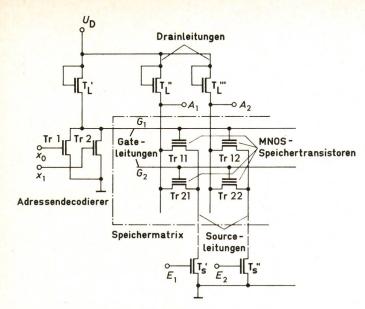

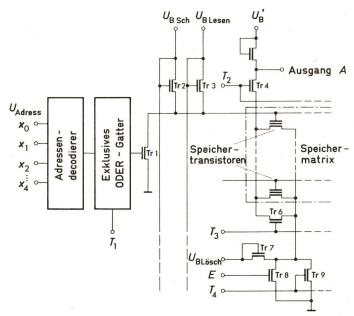

Zur Reduzierung der Anzahl der Anschlussflecken bei MNOS-Speichern grosser Kapazität ist ein Adressendecodierer für die Gateleitungen vorzusehen (Fig. 2). Ein derartiger Adressendecodierer besteht meist aus NAND- bzw. NOR-Gat-

tern, deren Ausgang u. a. am diffundierten Gebiet der Schalttransistoren Tr1 und Tr2 liegt. Werden die MNOS-Speichermatrix und der Decodierer auf demselben Substrat in Ein-Kanal-MOS-Technik realisiert, so kann man an das diffundierte Gebiet Spannungen nur einer Polarität anlegen, beispielsweise bei P-Kanal-Technik Spannungen nur negativer Polarität. Bei positiven Spannungen wäre das diffundierte Gebiet zum Substrat hin in Durchlassrichtung gepolt. Da man

Fig. 1

Querschnitt durch einen MNOS-Speichertransistor

<sup>1)</sup> Vortrag, gehalten am 5. Internationalen Kongress Mikroelektronika in München.

<sup>2)</sup> Siehe Literatur am Schluss des Aufsatzes.

Fig. 2 Schaltung einer MNOS-Speichermatrix mit Adressendecodierer

$A_1$ ,  $A_2$  Informationsausgänge  $E_1$ ,  $E_2$  Informationseingänge  $X_0$ ,  $X_1$  Adresseneingänge  $Tr_1$ ,  $Tr_2$  Schalttransistoren des Decodierers  $T_L'$ ,  $T_L'''$  Lasttransistoren  $T_S'$ ,  $T_S''$  Oversorgungsspannung

zum Schreiben und Löschen von MNOS-Transistoren jedoch positive und negative Gatespannungen in Bezug auf das Substrat benötigt, ist ein derartiger Decodierer für eine Speichermatrix mit MNOS-Transistoren üblicher Abmessungen nicht geeignet.

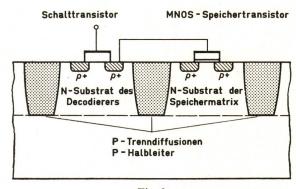

Eine Möglichkeit, diese Schwierigkeit zu lösen, ist, das Substrat des Decodierers vom Substrat der Matrix elektrisch zu trennen [2]. In Fig. 3 ist die Ausführungsform einer derartigen Anordnung schematisch dargestellt. Man kann das Substrat der Speichermatrix auf das Potential  $U_{\rm M}$  und das des Decodierers auf 0 V legen. Dann muss man zum Schreiben eine Spannung  $U_{\rm M}-U_{\rm P}$  an das Gate der Speichertransistoren legen. Wählt man  $U_{\rm M} \leq U_{\rm P}$ , so benötigt man Spannungen nur einer Polarität. Allerdings muss man für die Substrattrennung einen höheren technologischen Aufwand in Form einer Epitaxie-Schicht und von Trenndiffusionen treiben und kann bei dieser Ausführung die Speicherinformation nicht zeilen- oder bitweise, sondern nur als Ganzes löschen.

Eine neue Möglichkeit, die Schwierigkeit mit dem Decodierer zu lösen, bieten die im folgenden beschriebenen MNOS-Transistoren kurzer Kanallänge. Es wird gezeigt, dass mit derartigen Transistoren eine Speichermatrix durch einen in Fig. 2 dargestellten Decodierer angesteuert werden kann. Der Vorteil solcher Transistoren liegt erstens darin, dass man die Speichermatrix samt Decodierer ohne zusätzlichen grossen technologischen Aufwand für die Isolation zwischen Matrix und Decodierer auf ein Substrat integrieren kann und zweitens, dass man die Information je nach Wunsch zeilenweise oder bitweise löschen kann.

Die Funktionsweise und das elektrische Verhalten der MNOS-Transistoren kurzer Kanallänge werden im folgenden Abschnitt erläutert. Im letzten Abschnitt werden die Schaltung, der Entwurf und die Messergebnisse einer volldecodierten 256-bit-Speichermatrix, die mit diesen Transistoren aufgebaut ist, gebracht.

# 2. Speichertransistoren kurzer Kanallänge

#### 2.1 Funktionsweise

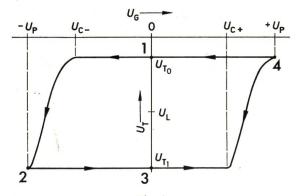

Das Verhalten von MNOS-Speichertransistoren kann anhand ihrer Hysteresekurve erläutert werden (Fig. 4). Der Transistor vom P-Typ habe zu Anfang eine Einsatzspannung von  $U_{\rm T0}$  (Punkt 1 auf der Hysteresekurve). Zum Einschreiben einer «1» (Punkt 2 in Fig. 4) legt man an die Gateelektrode eine negative Spannung  $-U_{\rm P}$ ; dabei bildet sich unter dem Gateisolator ein leitender Kanal, der Source- und Drain-Gebiete elektrisch miteinander verbindet (Fig. 5a) und der die Gegenelektrode zum Gate darstellt. Damit baut sich zwischen diesem Kanal und dem Gate ein elektrisches Feld auf, durch das die Haftstellen in der Isolatordoppelschicht positiv aufgeladen werden (Elektronen tunneln von den Haftstellen ins Substrat). Dadurch wird die Einsatzspannung nach  $U_{\rm T1}$  verschoben (Punkt 3 in Fig. 4).

Die übliche Methode, in einen MNOS-Transistor eine «0» einzuschreiben, wird in Fig. 5b dargestellt. Durch das Anlegen einer Spannung  $+U_{\rm P}$  (Punkt 4 in Fig. 4) an den Gateanschluss bildet sich eine Anreicherungsschicht unter dem Gateisolator. Die Richtung des elektrischen Feldes ist zu der in Fig. 5a umgekehrt und die Haftstellen in der Isolatordoppelschicht werden neutralisiert (Elektronen tunneln vom N-Substrat zu den Haftstellen).

Eine andere neue Methode, in einen MNOS-Transistor eine «0» einzuschreiben, ist in Fig. 5c dargestellt. Bei einem Transistor mit kurzer Kanallänge ( $L=1...5~\mu m$ ) wird die Gateelektrode an 0 V, die Source- und Drainelektrode an die Spannung — $U_{\rm P}$  gelegt. Die Verarmungszone wächst von den Drainund Source-Diffusionen unter dem Gateisolatorgebiet zusammen. Aus Fig. 5c ist ersichtlich, dass das Feldbild dem in Fig. 5b ähnelt. In diesem Fall bildet sich das elektrische Feld zwischen der Verarmungszone und der Gateelektrode aus. Dafür ist eine Spannung nur der gleichen Polarität wie beim Einschreiben einer «1» (Fig. 5a) notwendig.

Mit Hilfe der Formel für den abrupten PN-Übergang [3] kann man die Ausdehnung der Raumladungszonen um die diffundierten Gebiete abschätzen:

$$d = \sqrt{\frac{2 \varepsilon (U_{\rm D} - U)}{\varrho_{\rm n}}} \tag{1}$$

In Gl. (1) ist U die angelegte Spannung,  $U_D$  die Diffusionsspannung des PN-Überganges,  $\varepsilon$  die Dielektrizitätskonstante von Silizium und  $\varrho_n$  die Ladung des schwächer dotierten Halbleiters (in diesem Fall des Substrates). Für eine angelegte

Fig. 3

Querschnitt durch eine Speichermatrix mit Decodierer

bei elektrisch getrennten Substraten für Matrix und Decodierer

Fig. 4

Hysteresekurve eines MNOS-Transistors

$U_{

m T}$  Einsatzspannung  $U_{

m G}$  Gatespannung

Weitere Bezeichnungen siehe im Text

Spannung von -30 V und einer gegebenen Substratdotierung von  $5 \cdot 10^{14}$  cm<sup>-3</sup> (10- $\Omega$ cm-N-Substrat) errechnet sich die Ausdehnung d der Verarmungszone zu 8,5  $\mu$ m. Bei einer Kanallänge von 1...5  $\mu$ m und Spannungen um 30 V ist danach gewährleistet, dass der Spannungsabfall in der Verarmungszone gering und das elektrische Feld zum Löschen gross genug ist.

Zum Auslesen des eingeschriebenen Zustandes wird an das Gate des MNOS-Transistors eine zwischen den Einsatzspannungen  $U_{\rm T0}$  und  $U_{\rm T1}$  liegende Gatespannung  $U_{\rm L}$  angelegt (Fig. 4). Je nachdem, ob eine «0» oder eine «1» gespeichert ist, leitet oder sperrt der Transistor. Da die angelegten Spannungen beim Lesen verhältnismässig niedrig sind, beeinträchtigen kurze Kanallängen den Auslesevorgang nicht.

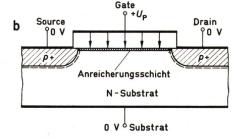

### 2.2 Messergebnisse

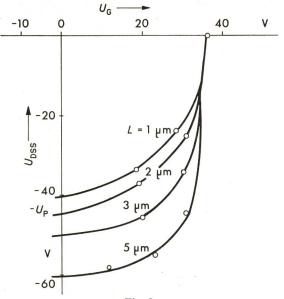

Im folgenden Abschnitt sei auf das Verhalten von MNOS-Transistoren kurzer Kanallänge eingegangen. Die Änderung der Einsatzspannung  $\Delta U_{\rm T}$  in Abhängigkeit von der zwischen Gate und Drain/Source angelegten Spannung  $U_{\rm G-D/S}$  ist in Fig. 6 für die Kanallängen  $L=2~\mu{\rm m}$  und 3  $\mu{\rm m}$  dargestellt. Die Dauer der Spannungsimpulse beträgt in beiden Fällen 5 ms. Zum Vergleich ist die Kurve eingetragen, die man nach der üblichen Methode (Fig. 5b) bei Impulsen mit einer Dauer von 50  $\mu{\rm m}$ s erhält.

Die zum Umschreiben benötigten negativen Source/Drain-Spannungsimpulse sind höher und länger, wenn man damit die gleiche Einsatzspannung erzielen will, wie mit einem positiven Gateimpuls einer Amplitude von 40 V und einer Dauer von 50  $\mu$ s. Wie aus Fig. 6 zu ersehen ist, muss man bei einem Transistor mit 2  $\mu$ m Kanallänge einen Spannungsimpuls mit einer Amplitude von etwa 53 V und einer Dauer von 5 ms an die Source- und Drainelektrode legen, um die vorgegebene Einsatzspannungsänderung  $\Delta U_{\rm T}$  zu erzielen. Der wichtigste Grund hierfür ist, dass eine geringere Spannung am Gateisolator anliegt (Fig. 5c).

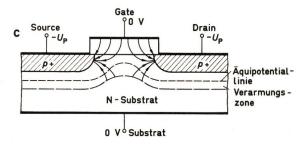

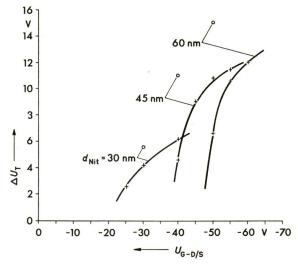

Um MNOS-Transistoren kurzer Kanallänge mit niederen Spannungen umschreiben zu können, kann man die Nitriddicke beim Doppelisolator des Transistors verringern. Hierdurch wird die Feldstärke an der Oxid-Nitrid-Grenzfläche, wo die Haftstellen sitzen, grösser, so dass man schon mit geringeren Spannungen eine Umladung erzielen kann. In Fig. 7 ist die zum Umschreiben erforderliche Spannung für drei verschiedene Nitriddicken dargestellt. Die unterschiedlichen  $\Delta U_{\rm T}$ -Werte für die verschiedenen Nitriddicken folgen aus der Be-

ziehung, dass die Einsatzspannungsverschiebung der Nitriddicke proportional ist [4]. Die angegebenen Punkte stellen zum Vergleich die Werte für die Einsatzspannungsverschiebung  $\Delta U_{\rm T}$  bei der entsprechenden Gatespannung bei  $U_{\rm G-D/S}=0$  V dar.

#### 3. Matrix mit Speichertransistoren kurzer Kanallänge

## 3.1 Speicherkennlinien

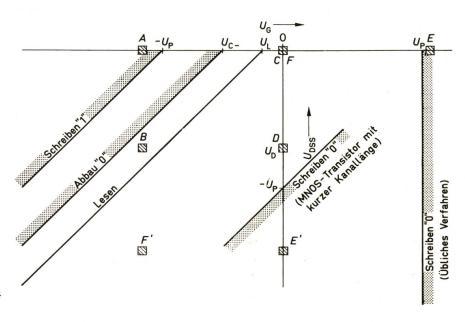

Die Arbeitsbereiche eines MNOS-Speichertransistors in einer Matrixanordnung kann man anhand von sog. Speicherkennlinien (Fig. 8) erläutern. Legt man den Betrachtungen die in Fig. 4 eingezeichneten Spannungen  $+U_{\rm P}$  und  $-U_{\rm P}$  der Hysteresekurve zugrunde, so ergibt sich theoretisch folgendes Bild: Zum Einschreiben einer «1» in einen Transistor muss zwischen Gate und Kanal mindestens die Spannung  $-U_{\rm P}$  anliegen. Legt man zusätzlich zwischen Drain und Source einerseits und Substrat andererseits eine Spannung an, so muss die Gatespannung entsprechend erhöht werden. Damit ergibt sich die eingezeichnete Gerade mit der Steigung 1. Um das Einschreiben einer «1» zu verhindern, darf man die Spannung  $U_{\rm C-}$  (Fig. 4) nicht überschreiten. Da auch in diesem Fall ein vorgegebenes Feld zwischen Gateelektrode und Inversionsrandschicht nicht überschritten werden darf, verläuft die Abbau-«0»-Gerade parallel zur Schreiben-«1»-Geraden. Zum Auslesen der Information ist der Arbeitspunkt auf die «Lesen»-Gerade zu legen, um das Ausgangssignal, auch bei Streuung der Werte, sicher zu erhalten.

Fig. 5

Schematische Darstellung der Zustände eines MNOS-Speichertransistors

- a während des Schreibens einer «1»

- b während des Schreibens einer «0» bei MNOS-Transistoren üblicher Abmessungen

- c bei MNOS-Transistoren kurzer Kanallänge

${

m Fig.}\,\, 6$  Abhängigkeit der Einsatzspannung  $U_{

m T}$  von der an Source und Drain liegenden Spannung

Kanallänge L als Parameter; Impulsdauer  $t_{\rm p}=5~{

m ms};$  Nitriddicke  $d_{

m Nit}=45~{

m nm}$

Die ausgezogene Kurve zeigt die Einsatzspannungsverschiebung  $\Delta U_{\rm T}$  in Abhängigkeit von der angelegten Gatespannung bei einem üblichen MNOS-Transistor (Fig. 5b)

Substratdotierung: 10 Ωcm

$U_{

m D}$  Drainspannung

$U_{

m S}$  Sourcespannung

$U_{G}$  Gatespannung

Anhand einer Speichermatrix mit  $(2 \times 2)$  Transistoren (Fig. 2) werden die Arbeitspunkte der Transistoren beim Schreiben, Löschen und Lesen beschrieben. In alle vier Transistoren Tr11, Tr12, Tr21 und Tr22 sei eine «0» eingeschrieben. In der ersten Zeile soll in Tr11 die Information «0» beibehalten und in Tr12 eine «1» eingeschrieben werden. Dazu wird an die Gateleitung  $G_1$  ein hoher negativer Spannungsimpuls angelegt ( $U_G < -U_P$ ). Der Transistor  $T_s''$  (Fig. 2) wird in den leitenden Zustand geschaltet, so dass Source und Drain mit der Inversionsschicht beim Speichertransistor Tr12 auf etwa 0 V liegen. Dadurch liegt während des Einschreibens eine hohe Spannung zwischen Gate und Kanal, so dass der Transistor Tr12 in den «1»-Zustand geschaltet wird. Der Arbeitspunkt A des Transistors Tr12 liegt in Fig. 8 über der Schreiben-«1»-Geraden.

Der Arbeitspunkt B des Transistors Tr11, in dem die «0» beibehalten werden soll, kommt so zustande: Man sperrt den Transistor  $T_s$  in der Sourceleitung des Transistors Tr11, wo-

Fig. 7 Einfluss der Nitriddicke auf die erzielbare Verschiebung der Einsatzspannung

Impulsdauer  $t_p = 5$  ms, Kanallänge  $L = 2 \mu m$

Die durch Kreise angedeuteten Messpunkte zeigen Einsatzspannungsverschiebungen  $\triangle U_{\mathrm{T}}$ , die man mit Gateimpulsen von 30, 40 und 50 V erzielen kann

Substratdotierung: 10  $\Omega$ cm Weitere Bezeichnungen siehe im Text

durch die Spannung an Drain auf etwa  $U_{\rm D}$  ansteigt. Da eine Inversionsschicht vorhanden ist, liegt zwischen Gate und Kanal eine auf den Wert ( $U_{\rm P}-U_{\rm D}$ ) reduzierte Spannung, die nicht mehr ausreicht, um den Transistor Tr11 in den «1»-Zustand zu schalten. Dieser Arbeitspunkt B des Transistors Tr11 muss unter der Abbau-«0»-Geraden liegen.

Am Transistor Tr22 liegen keine Spannungen; sein Arbeitspunkt ist der Punkt C. Bei Transistor Tr21 liegt an Source und Drain die Spannung  $U_D$ , sein Arbeitspunkt ist der Punkt D. Damit ändern diese beiden Transistoren ihre Information nicht.

Zum Schreiben einer «0» wird bei einer Matrix mit üblichen MNOS-Transistoren mindestens die positive Spannung  $U_P$  an die ausgewählte Gateleitung gelegt (Punkt E). Da das Feld

Fig. 8

Speicherkennlinienfeld für einen MNOS-Transistor

und Arbeitspunkte der Transistoren in einer

Speichermatrix

$U_{

m DSS}$  Spannung an Drain und Source Weitere Bezeichnungen siehe im Text und in Fig. 4

Fig. 9

Gemessene Speicherkennlinien für MNOS-Transistoren

mit kurzen Kanallängen

Kanallänge L als Parameter; Impulsdauer  $t_{\rm p}=5$  ms; Nitriddicke  $d_{\rm Nit}=45$  nm  $U_{\rm DSS}$  Spannung an Drain und Source Weitere Bezeichnungen siehe im Text

zwischen Gate und Anreicherungszone (Substrat) unabhängig von  $U_{\rm DSS}$  ist (Fig. 5b), verläuft die Kennlinie für das Einschreiben einer «0» parallel zur  $U_{\rm DSS}$ -Achse. In diesem Fall wird in alle Transistoren, die an die ausgewählte Gateleitung angeschlossen sind, eine «0» eingeschrieben (zeilenweises Löschen). Bei den Transistoren an den nicht ausgewählten Gateleitungen liegen keine Spannungen (Punkt F).

Verwendet man anstelle der üblichen MNOS-Transistoren solche mit kurzer Kanallänge, so können die in Fig. 5c gezeigten Verhältnisse eingestellt werden. Vernachlässigt man in Fig. 5c den im Halbleiter (N-Substrat) eingezeichneten Spannungsabfall, so muss im statischen Fall bei  $U_{\rm G}=0$  V,  $U_{\rm DSS}=$  $-U_{\rm P}$  angelegt werden. Legt man zusätzlich noch eine positive oder negative Gatespannung an, so stellt sich wieder eine Gerade mit der Steigung 1 ein. Diese Überlegung gilt für den statischen Fall. Um in einen MNOS-Transistor kurzer Kanallänge bei der Gatespannung 0 V eine «0» einzuschreiben, muss man die entsprechende Schreiben-«0»-Kennlinie auf der UDSS-Achse unterschreiten (Punkt E'). Soll in die anderen Transistoren der gleichen Spalte keine «0» eingeschrieben werden, so muss man an die entsprechenden Gateleitungen eine negative Spannung legen, die mindestens so gross ist, dass der Arbeitspunkt F' über der Schreiben-«0»-Kennlinie liegt. Dadurch wird die Feldstärke im Gateisolator so klein, dass die Haftstellen nicht umgeladen werden können (zeilenweise löschen).

Aus den Speicherkennlinien in Fig. 8 ersieht man, dass man zum Einschreiben der Informationen «1» und «0» in eine Matrix mit MNOS-Transistoren kurzer Kanallänge Spannungen nur einer Polarität benötigt; alle Arbeitspunkte A, B, F' und E' befinden sich in einem Quadranten des Kennlinienfeldes.

Die experimentell ermittelten Speicherkennlinien zeigen bei Schreiben-«1», Abbau-«0» und Lesen eine sehr gute Übereinstimmung mit den in Fig. 8 dargestellten theoretischen Kennlinien. Auch die Kennlinie für Schreiben-«0-» wird bei dem üblichen Verfahren beobachtet. Grössere Abweichungen treten

jedoch beim Experiment mit Transistoren sehr kurzer Kanallänge (2...3  $\mu$ m) gegenüber den Betrachtungen für den vereinfachten statischen Fall auf, wie aus den in Fig. 9 dargestellten Kurven zu sehen ist.

#### 3.2 256-bit-Matrix mit Decodierer

Für eine Speichermatrix, die mit MNOS-Transistoren kurzer Kanallängen aufgebaut ist und bei der man die Information zeilenweise einschreiben, löschen und auslesen kann, muss der Adressendecodierer nach den vorhergehenden Ausführungen folgende beiden Bedingungen erfüllen: Beim Schreiben soll nur an die ausgewählte Zeile der Spannungsimpuls gelangen. Beim Umschreiben soll die ausgewählte Zeile auf 0 V liegen, an den nicht ausgewählten Zeilen jedoch die Schreibspannungen.

Fig. 10 zeigt die Schaltung der realisierten Speichermatrix samt Decodierer. Der Adressendecodierer ist aus NAND-Gattern aufgebaut. Der Ausgang des ausgewählten Gatters liegt auf Betriebsspannung, alle anderen Ausgänge liegen auf 0 V. Der Ausgang des Decodierers führt auf ein Exklusiv-ODER-Gatter, das den Transistor Tr1 steuert. Bei einem Signal an Anschluss  $T_1$  wird der Ausgang des Decodierers invertiert. Ist der Adressendecodierer ausgewählt und liegt der Anschluss T<sub>1</sub> auf 0 V, so bleibt der Transistor Tr1 gesperrt. Über den Transistor Tr2 kann der Schreibimpuls an die ausgewählte Gateleitung der Speichermatrix gelegt werden. An allen nicht ausgewählten Zeilen leiten die zu Tr1 entsprechenden Transistoren, über die die Schreibspannung gegen Masse kurzgeschlossen wird. Je nachdem, ob eine «1» eingeschrieben oder das Einschreiben einer «1» verhindert werden soll, wird der Transistor Tr8 geöffnet oder gesperrt und dadurch Source der Speichertransistoren an Masse gelegt oder nicht. Gleichzeitig bleiben die Transistoren Tr6, Tr7 und Tr9 gesperrt, während Transistor Tr4 leitet.

Fig. 10

Schaltung einer mit MNOS-Transistoren kurzer Kanallänge aufgebauten

Speichermatrix samt Ansteuerung

| E                                   | Informationseingang                    |

|-------------------------------------|----------------------------------------|

| $T_1T_4$                            | Eingänge für Taktimpulse               |

| $U_{ m B}$                          | Versorgungsspannung der Speichermatrix |

| $U_{ m B~Sch}$                      | Schreibspannung                        |

| $U_{ m B\ Lesen}$                   | Lesespannung                           |

| $U_{ m B~L\ddot{o}sch}$             | Löschspannung                          |

| $U_{ m Adress}$                     | Adressenspannung                       |

| $X_0X_4$                            | Adresseneingänge                       |

| TVI 's Description of the law Trees |                                        |

Weitere Bezeichnungen siehe im Text

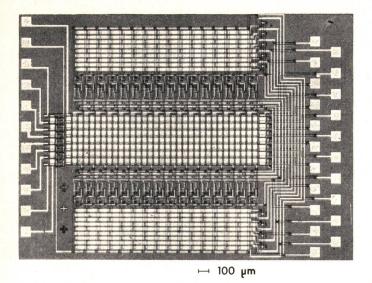

Fig. 11 Realisierte 256-bit-Speichermatrix

Oben und unten sind die Adressendecodierer angeordnet, in der Mitte befindet sich die Speichermatrix mit 8 × 32 Transistoren

Beim Löschen wird nun sowohl über den Transistor Tr2 ein Schreibimpuls, als auch über den Transistor Tr7 ein Löschimpuls an die Speichermatrix gelegt. Gleichzeitig kommt an den Anschluss  $T_1$  eine Spannung -U, so dass der Transistor Tr1 bei ausgewählter Zeile leitet, während er bei nicht ausgewählter Zeile gesperrt bleibt. Die Transistoren Tr4, Tr8 und Tr9 werden gesperrt, während Transistor Tr6 leitet, um die Source- und Drainanschlüsse einer Spalte zu verbinden. Somit liegen sämtliche Source- und Drain-Anschlüsse der Speichertransistoren auf der Spannung  $U_{\rm BL\ddot{o}seh}$ , der Gateanschluss der ausgewählten Zeile liegt auf 0 V, während alle anderen Gateanschlüsse der Speichertransistoren auf der Spannung  $U_{

m BSeh}$ liegen.

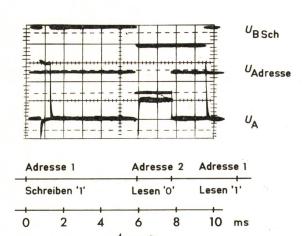

Zum Lesen wird der Anschluss  $T_1$  auf 0 V gelegt, so dass man über den Transistor Tr3 die Lesespannung an die ausgewählte Gateleitung legen kann. Bei allen nicht ausgewählten Zeilen leitet der Transistor Tr1 und somit liegen diese Gate-

Fig. 12 Verlauf der Spannungen  $U_{

m B~Sch}$ ,  $U_{

m Adresse}$  und  $U_{

m A}$ für Schreiben «1» sowie Lesen «1» und Lesen «0»

Aus messtechnischen Gründen wurde eine relativ grosse Ablenkzeit gewählt

V/Teilstrich  $U_{

m B~Sch}$ Schreibspannung 20  $U_{

m Adresse}$ Adressenspannung 10 V/Teilstrich  $U_{\rm A}$ 0,2 V/Teilstrich Ausgangsspannung

leitungen auf 0 V. Die Transistoren Tr6, Tr7 und Tr8 bleiben gesperrt, während die Transistoren Tr4 und Tr9 leiten. Ist im Speichertransistor eine «0» gespeichert, so leitet er, und der Ausgang A der Spalte liegt auf 0 V. Bei einer gespeicherten «1» leitet der Speichertransistor nicht, so dass der Ausgang A auf dem Potential  $U_{\rm D}$ - $U_{\rm T}$  bleibt.

Fig. 11 zeigt einen realisierten 256-bit-Speicher. Der Speicher ist zu 32 Worten mit 8 bit organisiert. Oben und unten sind die Adressendecodierer und die Exklusiv-ODER-Gatter angeordnet, in der Mitte ist die Speichermatrix. Die effektive Kanallänge der Speichertransistoren beträgt etwa 2 µm.

## 3.3 Experimentelle Ergebnisse

Die Messergebnisse des realisierten 256-bit-Speichers sind in Fig. 12 dargestellt. Diese Figur zeigt den zeitlichen Verlauf der Spannungen  $U_{\rm BSch}$ ,  $U_{\rm Adresse}$  und  $U_{\rm A}$  während des Einschreibens einer «1» und dem anschliessenden Auslesen der Information. Der gesamte Speicher wurde zu Beginn gelöscht, d. h. in alle Transistoren wurde eine «0» eingeschrieben. Beim Einschreiben einer «1» wird ein Spannungsimpuls von etwa -40 V an  $U_{\text{BSch}}$  angelegt. Für das Lesen der gespeicherten Information wird ein Spannungsimpuls von etwa -10 V an die ausgewählte Gateleitung gelegt. An dem Speicherplatz, wo keine «1» eingeschrieben wurde, liest man eine «0» aus. Der Ausgangspegel  $U_A$  steigt um etwa 0,2 V. Wo eine «1» eingeschrieben wurde, bleibt der Ausgangspegel auf dem Potential der Versorgungsspannung  $U_{\rm B}$ .

Die Schreibdauer für ein Wort beträgt 100 us, die Löschdauer etwa 5 ms. Zum Auslesen benötigt man eine Zeit von ca. 1 µs.

#### 4. Schlussbemerkungen

MNOS-Transistoren bieten den grossen Vorteil, dass man eine Speichermatrix hoher Packungsdichte für nichtflüchtige Informationen realisieren kann, da man nur einen Transistor für ein Speicherelement benötigt. Der Grund, wieso solche Speichermatrizen bis heute nicht in grossem Umfang angeboten werden, liegt unter anderem am Problem des Decodierers. Mit Speichertransistoren kurzer Kanallänge hat man die Möglichkeit, in einer einfachen Technologie einen Speicher zu realisieren, bei dem man sowohl die Matrix als auch den Decodierer auf einem gemeinsamen Chip integrieren kann. Die diesem Bericht zugrunde liegenden Arbeiten wurden mit Mitteln des Bundesministers für Bildung und Wissenschaft im Rahmen des Technologieprogrammes gefördert. Die Verantwortung für den Inhalt liegt jedoch allein beim Autor.

Dr. R. Hezel vom Siemens Forschungslaboratorium dankt der Autor für die Herstellung der untersuchten Muster.

#### Literatur

- E. C. Ross and J. T. Wallmark: Theory of the switching behaviour of MIS memory transistors. RCA Review 30(1969)2, p. 366...383.

- [2] R. E. Oakley: MNOS: a new non-volatile store. Component Technology 4(1970)5, p. 17...21.

- 4(1970)5, p. 17...21.

[3] A. S. Grove: Physics and technology of semiconductor devices. New York, John Wiley, 1967.

[4] G. Dorda und D. Donninger: MIS-Transistoren mit veränderbarer Einsatzspannung für Speicher. In: Mikroelektronik 4. Manuskriptdruck der Vorträge zum 4. Mikroelektronik-Kongress des «Internationalen Elektronen-Arbeitskreises eV (INEA)» in München vom 9. bis 11. November 1970. München/Wien, Oldenbourg-Verlag, 1971. S. 74...84.

[5] G. Dorda and M. Pulver: Turnel mechanism in MNOS structures. Physica Status Solidi, A: Applied Research 1(1970)1, p. 71...79.

#### Adresse des Autors:

K. Horninger, Zentrale Ferschung und Entwicklung der Siemens AG, Abt. FL TEC 13, Postfach 80 17 09, D-8000 München 80.