Zeitschrift: Bulletin des Schweizerischen Elektrotechnischen Vereins

Herausgeber: Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer

Elektrizitätswerke

**Band:** 63 (1972)

Heft: 26

Artikel: Codierungsmöglichkeit im APOSS-System

Autor: Steiner, H.

**DOI:** https://doi.org/10.5169/seals-915783

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

# **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

# Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 18.10.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Codierungsmöglichkeit im APOSS-System

Von H. Steiner

681.327.12

Für die Auszeichnung von Verkaufsgegenständen mit einem Codezeichen wird an den Code die Bedingung gestellt, dass nie mehr als 3 gleiche aufeinander folgende Bits zulässig sind. Es wird eine Codierungsmöglichkeit beschrieben, die diese Bedingung erfüllt und eine maximale Dichte an Information aufweist. Anhand eines Schaltungsbeispiels wird das Prinzip einer möglichen Lösung der Decodierung erklärt.

Pour le marquage d'objets de vente, selon un code, celui-ci ne doit jamais comprendre plus de 3 bits identiques successifs. L'auteur décrit une possibilité de codage qui satisfait à cette condition, tout en fournissant une densité maximale d'information. A l'aide d'un exemple de montage, le principe d'une solution de décodage est expliqué.

Die Funktionsweise des APOSS-Systems (Automatic Point of Sale System) wurde bereits in mehreren Fachzeitschriften behandelt, so dass in diesem Aufsatz nur noch grob der Ablauf erwähnt und nachher das Problem der Codierung näher erläutert wird.

### 1. Das APOSS-Prinzip

Jeder Verkaufsgegenstand in einem Geschäft wird auf seiner Standfläche mit einem Codezeichen versehen. Das Codezeichen besteht aus halbkreisförmigen Ringen (Fig. 1) und wird vorzugsweise gleichzeitig mit der Verpackungsbedruckung aufgebracht. Das Codezeichen enthält in codierter Form entweder nur die Artikelnummer (Price Look-up-System) oder den Preis und eine Zusatznummer (Price line-System) oder aber den Preis und eine Spartennummer (Price only-System).

Am Kassentisch legt der Kunde die Artikel, mit dem Codezeichen nach unten auf ein Förderband, das sie zur Registrierstelle befördert. Die Kassiererin führt die Ware über einen Ableseschlitz, wo der Dateninhalt des Aposs-Zeichens, mit einem Scanner, automatisch erfasst wird. Da der Code aus Halbkreisen besteht, ist ein Ausrichten der Artikel nicht notwendig, d. h. die Ablesung erfolgt lageunabhängig. Die so erfassten Daten werden einem Kleincomputer im Laden übermittelt, der die Preise bestimmt und an den Kassentisch zurücksendet. Gleichzeitig werden Preisreduktionen bei Sonderangeboten, Mehrfachpackungen etc. berücksichtigt und dem Kassentisch beim Abschluss der Verrechnung der Ware eines Kunden mitgeteilt. Der eingesparte Betrag wird gesondert auf dem Kassenbon ausgedruckt und automatisch subtrahiert.

Die erfassten Verkaufsdaten werden zusätzlich im Kleincomputer abgespeichert und können in gewünschten Zeitabständen über eine Modemleitung an das EDV-Zentrum der Verteilerorganisation übermittelt werden.

Die automatische Datenerfassung an der Kassenfront bringt folgende Vorteile:

- a) Warennachschub und Produktion werden optimal gesteuert.

- b) Die Lagerbestände werden reduziert und der Lagerumschlag beschleunigt.

- c) Die rechtzeitig zur Verfügung stehenden Verkaufsdaten erlauben eine flexible Einkaufs- und Verkaufspolitik.

- d) Fehlregistrierungen sind nicht mehr möglich.

- e) Die Bedienung des Kunden wird beschleunigt. f) Aktionen werden automatisch berücksichtigt.

# 2. Aufbau des Codes

Das Codezeichen besteht aus konzentrischen Kreisringen. Die Breite eines Ringes entspricht dabei einem Bit oder aber einem ganzzahligen Vielfachen davon. Um eine grosse Informationsdichte und somit ein möglichst kleines Codezeichen zu

erhalten, wäre eine rein binäre Codierung vorteilhaft. Je nach der darzustellenden Information kommt es aber zwangsläufig vor, dass der gleiche Wert «H» oder «L» aufeinanderfolgend mehrmals vorkommt.

Ist die Standfläche des Artikels, auf der das CZ angebracht wird, schief oder gekrümmt, so können nicht beliebig viele gleiche aufeinanderfolgende Bits aufgelöst werden, da, bedingt durch die Schräglage, eine scheinbare Verkürzung der Ringbreite und damit eine Reduktion der Anzahl Bits eintritt. Weitere Schwierigkeiten der Auflösung kommen dazu, z. B. die Nichtlinearität des optischen Systemes bezogen auf die Breite

Fig. 1

Das APOSS-Codezeichen

des Leseschlitzes, die Umwandlung des reflektierten Lichtes in ein elektrisches Signal, Frequenzschwankungen des Taktgebers für die Einlesung der Daten, und nicht zuletzt auch die Drucktoleranzen des Codezeichens, abhängig vom Druckverfahren, Papier usw.

Das Problem der Auflösung einer beliebigen Anzahl gleicher, sich folgender Bits wird also gegeben durch die Schwierigkeit der Synchronisation zwischen dem einlesenden Taktgeber und der optoelektronischen gewandelten Information.

Um eine eindeutige Zuordnung und damit eine fehlerfreie Einlesung in das Register zu gewährleisten, wurde für die Codierung die Anzahl sich unmittelbar folgender gleicher Bits auf 3 beschränkt. Der Taktgeber kann somit nach spätestens 3 gleichen Bits mit dem zwangsläufig folgenden Flankenwechsel neu synchronisiert werden.

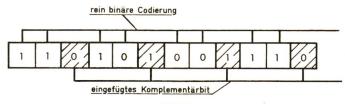

Ein Code mit dieser max. 3-bit-Bedingung kann auf verschiedene Arten verschlüsselt werden. Eine Möglichkeit besteht z. B. darin, eine rein binäre Codierung anzuwenden und nach jedem zweiten Bit ein zum vorangehenden inverses Bit einzufügen (Fig. 1). Mit dieser Art der Codierung wird die max. 3-bit-Bedingung zwar erfüllt, jedoch werden gegenüber der normalen, rein binären Codierung, bei gleichbleibenden Informationsinhalt,  $^{1}/_{3}$  mehr Bitstellen benötigt, das Codezeichen wird grösser, was sich für die Auszeichnung von Verkaufsgegenständen als Nachteil erweist.

Eine optimale Dichte des Codes wird dann erreicht, wenn der Code rein binär aufgebaut wird, jedoch nur diejenigen Bi-

Tabelle I

| Binärcodierung |        | Entsprechende Zuordnung in der<br>Codierung mit der max. 3-bit-Bedingung |  |

|----------------|--------|--------------------------------------------------------------------------|--|

| 0              | 000000 | ungültig                                                                 |  |

| 1              | 000001 | ungültig                                                                 |  |

| 2              | 000010 | ungültig                                                                 |  |

| 3              | 000011 | ungültig                                                                 |  |

| 4              | 000100 | 1                                                                        |  |

| 5              | 000101 | 2                                                                        |  |

| 6              | 000110 | 3                                                                        |  |

| 7              | 000111 | 4                                                                        |  |

| 8              | 001000 | 5                                                                        |  |

| 9              | 001001 | 6                                                                        |  |

| 10             | 001010 | 7                                                                        |  |

| 11             | 001011 | 8                                                                        |  |

| 12             | 001100 | 9                                                                        |  |

| 13             | 001101 | 10                                                                       |  |

| 14             | 001110 | 11                                                                       |  |

| 15             | 001111 | ungültig                                                                 |  |

| 16             | 010000 | ungültig                                                                 |  |

| 17             | 010001 | 12                                                                       |  |

| 18             | 010010 | 13                                                                       |  |

| 19             | 010011 | 14                                                                       |  |

| 20             | 010100 | 15                                                                       |  |

närzahlen zugelassen werden, die die maximal 3-bit-Bedingung erfüllen. In Tabelle I sind zur Illustration in der ersten Kolonne die Zahlen 1 bis 20 in binärer Form und in der zweiten Kolonne die entsprechenden Zahlen in der neuen Codierung mit der maximal 3-bit-Bedingung aufgezeichnet. Einfachheitshalber wird der Code auf sechs Bits beschränkt.

Die Anzahl notwendigen Bits y zur Codierung von x Möglichkeiten [unter Berücksichtigung der 3-bit-Bedingung kann aus folgender Formel errechnet werden:

$$y = 3,77 \log x - 0,32$$

Für z. B. 100 000 Möglichkeiten errechnet sich die Anzahl notwendiger Bits:

$$y = 3,77 \log 100000 - 0,32 = 18,53 \triangleq 19 \text{ bit}$$

Bei einer binären Codierung ohne Einschränkungen benötigt man für die gleiche Anzahl Kombinationen 17 bit. Mit einem Mehrbedarf von nur 2 bit kann man die geforderte max. 3-bit-Bedingung erfüllen.

# 3. Die Decodierung

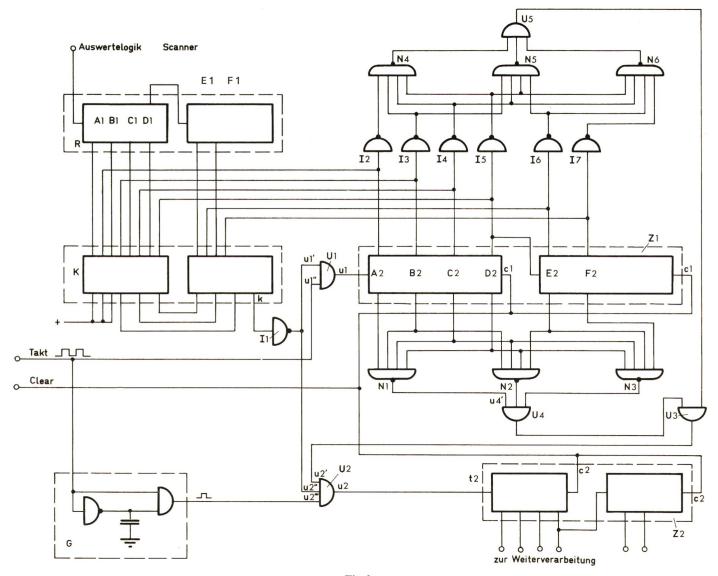

Um diesen Code praktisch auszunützen, muss eine wirtschaftliche Lösung für die Codierung und Decodierung in einen normalen Code gefunden werden. Fig. 2 zeigt eine Decodierungsmöglichkeit des maximal 3-bit-Codes in einen normalen Binärcode. Das Schema wird auf einen Code von 6 bit beschränkt.

Der von der Leseeinheit des Kassentisches abgelesene und zu wandelnde Code liegt am Register R an (Fig 3). Die Bits A1 bis F1 werden dem zweistufigen Komparator K zugeführt. Dieser vergleicht die Bits A1 bis F1 mit den Ausgängen A2 bis F2 des Binärzählers Z1. Wenn die Bedingung A1 bis F1 = A2 bis F2 erfüllt ist, wird der Ausgang k des Komparators K aktiv, das heisst, er zeigt den logischen Zustand «H».

Zu Beginn des Wandelvorganges werden die beiden Zähler Z1 und Z2 mit einem Clear-Impuls an den Eingängen c1 und c2 zurückgestellt. Ist der am Komparator K anliegende Code A1 bis F1 nicht gleich A2 bis F2, so zeigt der Ausgang k den

logischen Zustand «L». Dieses Signal wird über einen Inverter I1 gebracht, so dass das UND-Tor U1 über den Eingang u1' aktiviert wird und der Takt über den Eingang u1' am Ausgang u1 erscheinen kann. Mit jeder fallenden Flanke des Taktes wird der Zählerstand in Z1 um 1 erhöht.

Der Takt wird gleichzeitig dem Differenzierglied G zugeführt, an dessen Ausgang bei jeder steigenden Flanke des Taktes ein steigender Impuls entsteht, der an den Eingang u 2''' des UND-Tores U2 gebracht wird.

Der Eingang u 2" ist aktiviert, da der Ausgang des Inverters I1 den logischen Zustand «H» zeigt. Das Erscheinen des Impulses am Ausgang u2 des Und-Tores U2 und damit auch der Zählvorgang im Zähler Z2 ist somit nur noch vom Zustand des Einganges u2' des Und-Tores U2 abhängig. Die Logik, bestehend aus den Nand-Toren N1, N2, N3 und dem Und-Tor U4 untersucht die Konfiguration der Bits A2 bis F2 darauf, ob mehr als drei aufeinanderfolgende Bits den Zustand «H» zeigen. Die Bits A2 bis D2 werden den Eingängen des Nand-Tores N1 zugeführt. Zeigen nun die vier aufeinanderfolgenden Bits A2 bis D2 an den Eingängen des Nand-Tores N1 alle den logischen Zustand «H», so wird der Ausgang von N1 «L». Dieser wird an den Eingang u4' des Und-Tores U4 gebracht. Der Ausgang von U4 und damit auch der Ausgang des Und-Tores U3 nehmen den Zustand «L» an. Das hat zur Folge, dass über den Eingang u2' des Und-Tores U2 der an G entstandene Impuls nicht an den Zählereingang t2 des Zählers Z2 gelangen kann.

Fig. 2

Rein binäre Codierung mit eingefügten Komplementärbit

Zeigen dagegen eines oder mehrere der aufeinanderfolgenden Bits A2 bis D2 den Zustand «L», so wird der Ausgang des Nand-Tores N1 und damit auch der Eingang des Und-Tores U4 «H».

Auf gleiche Weise werden mit den Nand-Toren N2 und N3 die vier aufeinanderfolgenden Bits B2 bis E2 resp. C2 bis F2 untersucht. Zeigen die vier Bits B2 bis E2 oder C2 bis F2 alle den Zustand «H», so wird der Ausgang der entsprechenden Nand-Tore N2 oder N3 «L», und damit auch die Ausgänge von U4 und U3. Der Zählvorgang des Zählers Z2 wird, wie bereits beschrieben, unterdrückt.

Zeigen eines oder mehrere der vier aufeinanderfolgenden Bits B2 bis E2 und C2 bis F2 den Zustand «L», so wird der Ausgang der Nand-Tore N2 resp. N3 «H» und somit auch die entsprechenden Eingänge des Und-Tores U4.

Der Ausgang des Und-Tores U4 wird also nur dann «H», wenn die Bits A2 bis F2 die Bedingung erfüllen, dass nie mehr als 3 aufeinanderfolgende Bits den Zustand «H» aufweisen.

Die Logik, bestehend aus den Invertern I2 bis I7 und den Nand-Toren N4 bis N6, untersucht die Konfiguration der Bits A2 bis F2 darauf, ob mehr als 3 aufeinanderfolgende Bits den Zustand «L» zeigen.

Mit den Invertern I2 bis I7 wird der zu untersuchende «L»-Zustand der Bits A2 bis F2 umgewandelt und nachher, mit der

$Fig.\ 3$  Prinzipschaltbild für die Decodierung eines 6-bit-Codes

| R          | Register                | I1I7           | Inverter                  |

|------------|-------------------------|----------------|---------------------------|

| K          | Komparator              | U1, U5         | UND-Tor                   |

| k          | Ausgang des Komparators | uI', uI''      | Eingänge des UND-Tores U1 |

| G          | Differenzierglied       | u1             | Ausgang des UND-Tores U1  |

| Z1, Z2     | Binärzähler             | u2', u2", u2"" | Eingänge des UND-Tores U2 |

| <i>t</i> 2 | Eingang des Zählers Z2  | u2             | Ausgang des UND-Tores U2  |

| c1, c2     | Eingänge der Zähler     | N1, N2, N3     | Nand-Tor                  |

| A1F1. A2F2 | Bit                     |                |                           |

gleichen, schon beschriebenen Schaltung, auf mehr als 3 aufeinanderfolgende «H»-Zustände untersucht. Am Ausgang des Und-Tores U5 erscheint also der Zustand «L», wenn mehr als 3 aufeinanderfolgende Bits den Zustand «L» zeigen und der Pegel «H», wenn eine gültige Bit-Konfiguration bezüglich «L»-Zustand im Zähler Z1 anliegt.

Nur wenn von U5 und U4 her die Bestätigung eintrifft, dass bezüglich des «L» resp. «H»-Zustandes, im Zähler Z1 eine gültige Konfiguration anliegt, kann der Ausgang des Und-Tores U3 aktiv werden.

Liegt also im Zähler Z1 eine gültige Konfiguration an, so wird der Ausgang des Und-Tores U3 «H» und damit auch der Eingang u2' des Und-Tores U2.

Die nächste, mit dem Differenzierglied G differenzierte steigende Flanke des Taktes kann über U2 den Zählerstand von Z2 um 1 erhöhen. Der Binärzähler Z1 zählt von A2 bis F2 = 0 bis A2 bis F2 = A1 bis F1 und wird dann mit dem Ausgang

k des Komparators K gestoppt. Der Binär- oder aber Dekadenzähler Z2 zählt von 0 aus nur die in Z1 anliegenden gültigen Konfigurationen, wobei auch Z2 gestoppt wird, wenn die Bedingung A1 bis F1=A2 bis F2 erfüllt ist. Den zu decodierenden Code vom Register R kann man zur Weiterverarbeitung in rein binärer Form resp. im BCD-Code am Zähler Z2 abgreifen.

Diese dynamische Decodierung weist den Nachteil auf, dass bei grossem Informationsinhalt die Decodierzeit eine Rolle spielen kann, da die Frequenz des Taktgebers nach oben begrenzt ist. In solchen Fällen kann die Information in mehr Gruppen aufgeteilt und gleichzeitig mit mehreren Decodierschaltungen bearbeitet werden.

### Adresse des Autors:

Hans Steiner, Zellweger AG, Apparate- und Maschinenfabriken Uster, Werk Hombrechtikon, 8634 Hombrechtikon.

AUF 2000 METER IST DER SOMMER KURZ.

- ABER LANG GEHTS MANCHMAL, BIS EIN NEUER SKILIFT IM DETAIL GEPLANT IST.

"EIN KUNSTSTOFFKABEL IST LEICHTER ALS EIN PAPIERBLEIKABEL, DAS HABEN WIR SCHNELLER OBEN", RIETEN DIE MÄNNER AUS BRUGG. ES WAR IM AUGUST. UND ALS IM SEPTEMBER DER ERSTE SCHNEE FIEL, WAREN DIE 800 METER KABEL IM BODEN.

Grosse Projekte dürfen nicht an kleinen Dingen scheitern. Darum hat Brugg fast alle Kabel am Lager. Und bringt sie auch gleich dorthin, wo sie gebraucht werden. Von Kabeln ist nur gut reden, wenn man sie hat, meint Brugg.

Brugg ist schnell.

Kabelwerke Brugg AG, 5200 Brugg

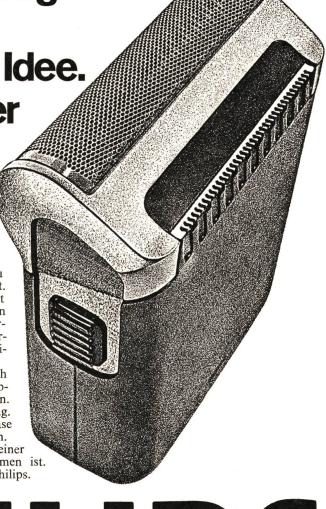

Ein besseres Sieb-Schersystem zu entwickeln, war harte

Arbeit. Es schräg

einzubauen,

war eine gute Idee.

Und das ist der

XTR7 von Philips.

Sieb-Schersysteme sind gut, solange das Sieb gut ist. Aber wenn das Sieb die ersten kleinen Risse bekommt, dann ist es aus mit dem Rasieren.

Jetzt hat Philips ein Sieb aus nahezu unverwüstlichem Chromstahl entwickelt. Die Löcher in diesem Sieb werden nicht einfach galvanisch, sondern mit feinsten Spezialwerkzeugen hergestellt. Dieses Verfahren ergibt ein glattes, hauchdünnes, starkes und doch federndes Sieb — auf das Philips ein ganzes Jahr Garantie geben kann.

Aber ein Sieb-Schersystem allein ist noch nichts. Man muss es auch in einen Rasierapparat mit Motor und Schermessern einbauen.

Das hat Philips getan. Und zwar schräg. Damit man sich endlich auch unter der Nase und am Hals mühelos scharf rasieren kann.

Wir wissen auch nicht, warum noch keiner auf diese geniale einfache Idee gekommen ist. Hauptsache es gibt ihn, den XTR 7 von Philips.

# PHILIPS AREA

Schärfer rasieren - länger rasiert sein.