**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätswerke

**Band:** 63 (1972)

**Heft:** 2

**Artikel:** Empfindlichkeit und Schutz integrierter Schaltkreise gegen Überspannungen

**Autor:** Iseli, J.

**DOI:** <https://doi.org/10.5169/seals-915654>

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

#### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 16.02.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Empfindlichkeit und Schutz integrierter Schaltkreise gegen Überspannungen<sup>1)</sup>

Von J. Iseli, Aarau

621.3.049.75:621.316.91

Bei industrieller Anwendung integrierter Schaltkreise können Elektronik und Starkstromteil oft nicht getrennt werden, was zur Beschädigung von IC's (IC: integrierter Schaltkreis) durch Überspannung führen kann. Analog zur Störung von IC's kann auch die Zerstörung durch eine statische und dynamische Überspannungsempfindlichkeit beschrieben werden. Diese Empfindlichkeit wird ausgemessen und mit den Charakteristiken von Schutzschaltungen verglichen.

Dans les applications industrielles des circuits intégrés, l'électronique et la partie haute tension ne peuvent souvent pas être séparés, ce qui peut endommager les IC (IC = circuit intégré) par les surtensions. D'une manière analogue aux perturbations des IC, on peut également décrire une destruction par suite d'une sensibilité statique et dynamique aux surtensions. Cette sensibilité est mesurée et comparée aux caractéristiques des circuits de protection.

## 1. Veranlassung

Relativ viele IC's werden im Betrieb (vor allem bei Test, Ausprüfung, Montage usw.) durch Überspannungen beschädigt. In der Praxis werden daher verschiedene Schutzschaltungen vorgeschlagen. Um diese Schutzschaltungen in bezug auf ihre Wirksamkeit im Zeit- bzw. Frequenzbereich beurteilen zu können, muss die Spannungsfestigkeit der IC's bekannt sein. Nach gewissen Herstellerangaben halten IC's Überspannungen nicht einmal während Pikosekunden aus. Diese Angaben stehen im Gegensatz zu den praktischen Erfahrungen, dass jedes Element eine gewisse Energie, bzw. Leistung zu seiner Zerstörung braucht. Aus diesem Grunde wird primär die statische und dynamische Überspannungsempfindlichkeit von IC's bestimmt. Zu diesem Zweck wurden gesamthaft ca. 200 integrierte Schaltungen des Typs SN 7400 N bzw. FLH 101 der TTL-Familie (TTL: Transistor — Transistor — Logik) ausgemessen.

## 2. Statische Überspannungsempfindlichkeit

Bei der Messung der statischen Überspannungsempfindlichkeit wird die Speisespannung durch eine nahezu ideale Spannungsquelle angehoben. Die Dauer der Spannungsanhebung ist lang im Vergleich zu den damit verbundenen thermischen Vorgängen im eigentlichen Halbleiter.

### 2.1 Allgemeines

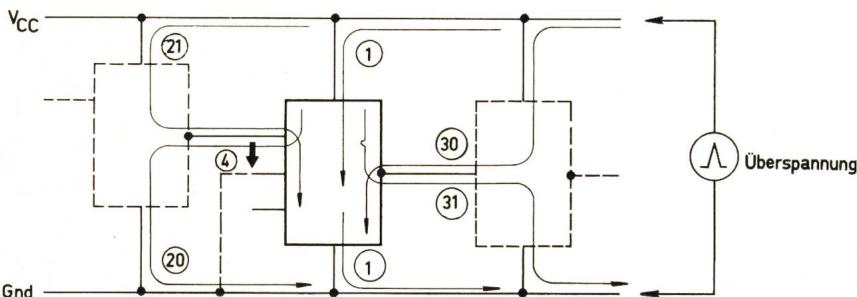

Grundsätzlich kann eine Überspannung nicht nur an der Speisung, sondern auch an den Eingängen bzw. Ausgängen der IC's erscheinen. Fig. 1 zeigt die verschiedenen Zerstörmöglichkeiten und die entsprechenden Ableitströme:

<sup>1)</sup> Vortrag, gehalten an der Eurocon 71, vom 18.—22. Oktober 1971 in Lausanne.

1 – Speisungsanschlüsse

20 – Eingänge im logischen Zustand 0 (0...0,8 V)

21 – Eingänge im logischen Zustand 1 (2,0...5 V)

30 – Ausgänge im logischen Zustand 0 (0...0,4 V)

31 – Ausgänge im logischen Zustand 1 (2,4...5 V)

4 – Differenzspannung zwischen zwei Eingängen mit unterschiedlichen logischen Zuständen.

Es ist nun wichtig zu wissen, in welchem logischen Zustand und durch welchen Pfad ein IC die grösste Überspannungsempfindlichkeit zeigt. Alle folgenden Überspannungsbetrachtungen beziehen sich auf IC's in einem geschlossenen System. Das heisst, die Ein- und Ausgänge der IC's sind wiederum mit IC's verbunden. Die Verbindungen vom und zum System erfolgen über Anpassungsschaltungen, für die zusätzliche, im weiteren nicht betrachtete Schutzmassnahmen notwendig sind.

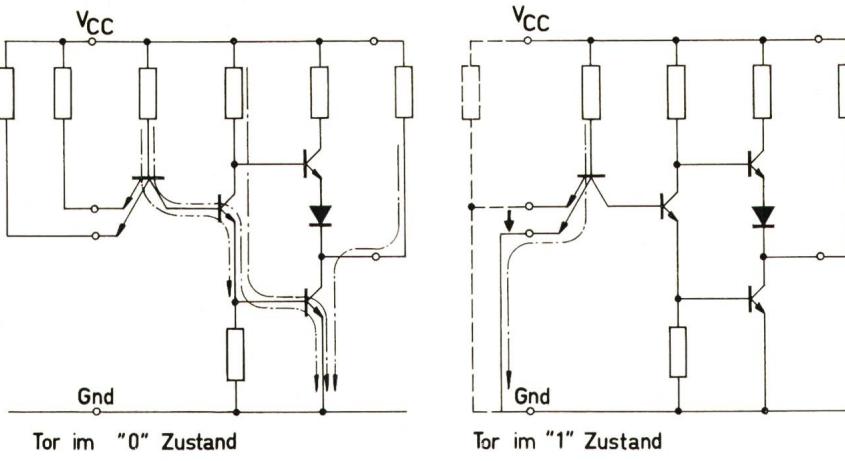

In Fig. 2 sind Tore im logischen Zustand 0 und 1 gezeigt, wobei die Ein- und Ausgänge mit Widerständen entsprechend den Ausgangs- bzw. Eingangscharakteristiken der vorhergehenden bzw. nachfolgenden Tore abgeschlossen sind. Aus der Figur wie auch aus den Handbüchern der Hersteller ([1]<sup>2)</sup>; zeigt sich sofort, dass das Tor im «0»-Zustand niederohmiger und damit gegenüber Überspannungen empfindlicher ist.

Im weiteren ist das Tor im «1»-Zustand kritisch, falls die beiden Eingänge unterschiedliche logische Zustände besitzen. Die Messungen zeigen jedoch, dass diese Anordnung im wesentlichen mit dem «1»-Zustand ohne Differenzspannung zwischen den Eingängen identisch und damit weniger kritisch als der «0»-Zustand ist.

### 2.2 Messung der statischen Überspannungsempfindlichkeit

Es ist zu beachten, dass in einem IC (SN 7400 N / FLH 101) vier Tore vorhanden sind. Die Überspannungsempfindlichkeit wird daher immer für einen IC und damit für eine Gruppe von vier Toren spezifiziert.

Es wurden fünf Arten von Messungen durchgeführt:

Fig. 1

Überspannungseinwirkung auf ein NAND-Tor

$V_{CC}$  Speiseleiter; Gnd Masse

<sup>2)</sup> Siehe Literatur am Schluss des Aufsatzes.

Fig. 2

Innere Stromfluss in TTL-Toren

$V_{CC}$  Speiseleiter; Gnd Masse

zur Zerstörung notwendige Energie  $W$  berechnet werden.

$$W = \int_0^{t_{BD}} V_{ee}(t) \cdot I_{ee}(t) dt \quad (3)$$

Es zeigt sich nun, dass im statischen Bereich diese Energie mit der Zunahme von  $t_{BD}$  immer stärker zu streuen beginnt. Das heisst, eine vernünftige Aussage über die benötigte Zerstörungsenergie kann in diesem

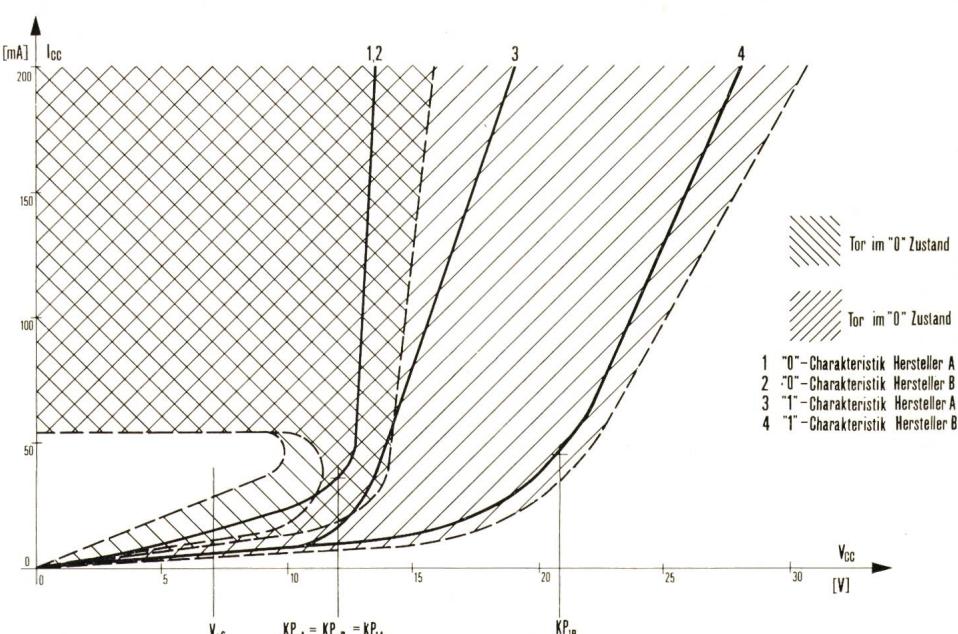

Bereich nicht gemacht werden. Statisch kann daher nur ausgesagt werden, dass ein IC garantiert unter 7 V und typisch unter 12 V nicht zerstört wird. Der Wert  $V_{ee} = 12$  V = typischer Knickpunkt ist dabei als arithmetischer Mittelwert der ausgeführten Messungen zu verstehen.

Aus der Praxis ist es klar, dass die statische Überspannungsempfindlichkeit keine realistische Grösse darstellt. Das heisst, es werden im allgemeinen keine dauernden Überspannungen, sondern nur kurzzeitige Überspannungsspitzen auftreten.

Die statische Überspannungsempfindlichkeit (statische Spannung-Strom-Charakteristik) gibt aber eine, wenn auch beschränkte, Vergleichsmöglichkeit der Produkte verschiedener Hersteller. Die Beschränkung bezieht sich auf die mögliche grosse Streuung zwischen IC's verschiedener Chargen auch beim gleichen Hersteller.

Im weiteren zeigt die statische Überspannungsempfindlichkeit, dass das Tor im «0»-Zustand am empfindlichsten ist. Es seien daher für die dynamische Überspannungsempfindlichkeit nur noch dieser Fall, sowie für Stöße mit relativ hohen Spannungen der «1»-Zustand mit Differenzspannung zwischen den Eingängen betrachtet.

### 3. Dynamische Überspannungsempfindlichkeit

Die Messung der dynamischen Überspannungsempfindlichkeit geschieht durch ein stossweises Anheben der Speisespannung, wobei die Stossdauer im allgemeinen kürzer ist, als zur Erreichung eines thermischen Gleichgewichts innerhalb des

- 2.2.1 Tore im «0»-Zustand (Eingänge hochohmig auf  $V_{ee}$  gelegt. Ausgänge offen.)

- 2.2.2 Tore im «0»-Zustand (Ein- und Ausgänge niederohmig auf  $V_{ee}$  gelegt.)

- 2.2.3 Tore im «1»-Zustand (Eingänge auf Gnd gelegt, Ausgänge offen.)

- 2.2.4 Tore im «1»-Zustand (Eingänge auf Gnd gelegt, Ausgänge niederohmig auf  $V_{ee}$  gelegt.)

- 2.2.5 Tore im «1»-Zustand (Eine Hälfte der Eingänge auf Gnd, die andere Hälfte niederohmig auf  $V_{ee}$  gelegt, Ausgänge niederohmig auf  $V_{ee}$  gelegt.)

Überspannung nur an den Speiseanschlüssen wirksam; Ein- und Ausgänge unbeeinflusst.

Überspannung an den Speiseanschlüssen und an den Ein- und Ausgängen wirksam.

Überspannung nur an den Speiseanschlüssen wirksam; Ein- und Ausgänge unbeeinflusst.

Überspannung an Speisung und Ausgängen wirksam. Keine Differenzspannung zwischen den Eingängen.

Überspannung an Speisung, Ein- und Ausgängen wirksam. Differenzspannung zwischen den Eingängen.

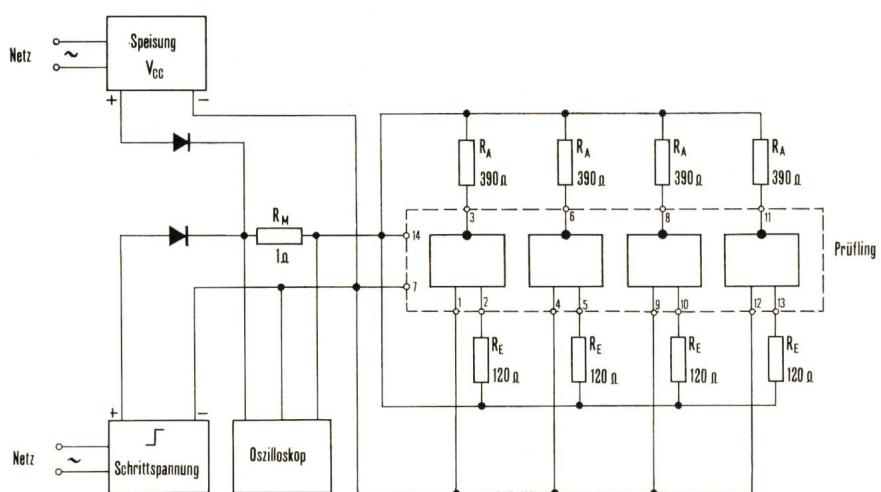

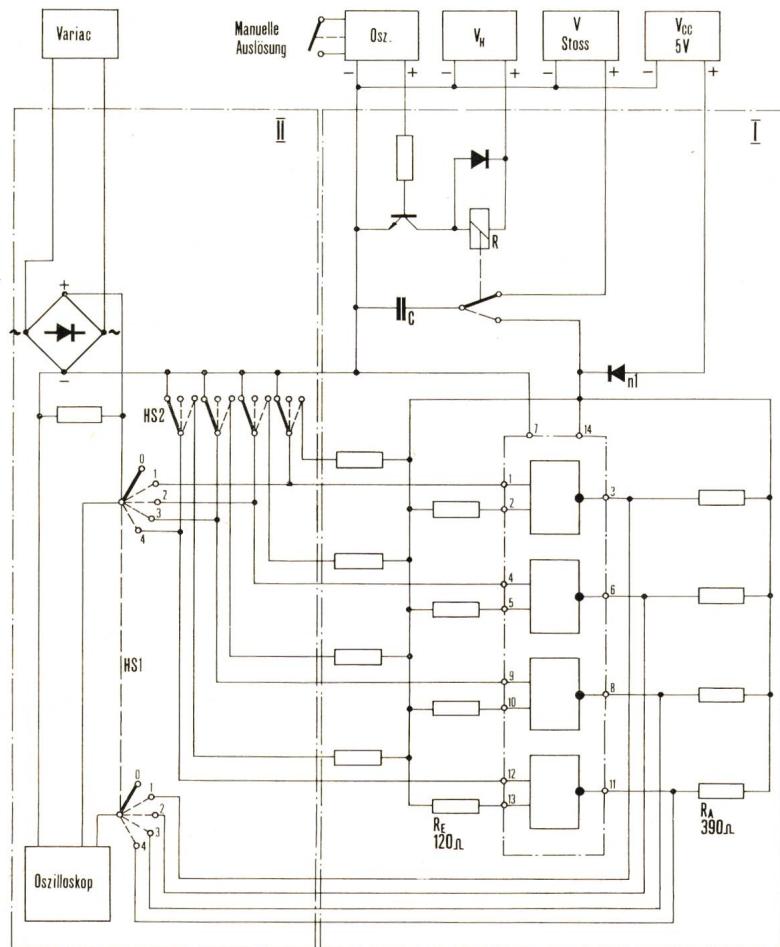

Fig. 3 stellt den Versuchsaufbau für die Messung 2.2.5 dar. Die übrigen Messungen wurden analog ausgeführt, wobei einzig die Beschaltung des Prüflings entsprechend geändert wurde.

Es zeigte sich, dass die Messungen 2.2.1/2.2.2 und 2.2.3/2.2.4 /2.2.5 praktisch zusammenfallen. Man kann daher von einer «0»- bzw. «1»-Charakteristik sprechen, die in Fig. 4 dargestellt ist.

Die wesentlichen typischen Daten sind in Tabelle I zusammengefasst.

Ist  $V_{ee} > KP$  so kann grundsätzlich jederzeit ein Durchbruch erfolgen. Dieser Durchbruch erfolgt jedoch nicht schlagartig. Er zieht sich vielmehr je nach Grösse von  $V_{ee}$  über Millisekunden bis Sekunden hin. Allgemein kann gesagt werden: Je grösser die schlagartig angelegte Störspannung ist, umso rascher erfolgt der Durchbruch.

Ist  $V_{ee}(t), I_{ee}(t)$  und die Zeit  $t_{BD}$  zwischen dem Anlegen der Überspannung und dem endgültigen Durchbruch bekannt, so kann die

Fig. 3

Messungen der statischen Überspannungsempfindlichkeit

$V_{CC}$  Speisung;  $R_M$  Messwiderstand;  $R_A$  Abschlusswiderstand am Ausgang;  $R_E$  Abschlusswiderstand am Eingang

Fig. 4

**Statische Spannung-Strom-Charakteristik SN7400N/FLH101**

$V_{CC}$  Speisespannung

$I_{CC}$  Speistrom

$V_{CG}$  max. vom Hersteller garantierte Speisespannung (7V)

$KP_{0A}$  Knickpunkt 0 (Hersteller A)

$KP_{0B}$  Knickpunkt 0 (Hersteller B)

$KP_{1A}$  Knickpunkt 1 (Hersteller A)

$KP_{1B}$  Knickpunkt 1 (Hersteller B)

eigentlichen Halbleiters notwendig wäre. Diese Anhebung geschieht, indem ein geladener Energiespeicher (Kondensator) auf die Speisung geschaltet wird.

### 3.1 Messung der dynamischen Überspannungsempfindlichkeit

Folgende Messungen wurden durchgeführt:

#### 3.1.1 Tore im «0»-Zustand

Überspannung an Speisung, Ein- und Ausgänge wirksam (analog zu 2.2.2)

#### 3.1.2 Tore im «1»-Zustand

Überspannung an Speisung, Ein- und Ausgänge wirksam, Differenzspannung zwischen den Eingängen (analog zu 2.2.5)

Fig. 5 stellt den Versuchsaufbau dar. Schaltung I dient zur Überlagerung von Energiestößen auf  $V_{cc} = 5$  V. Schaltung II dient zur Kontrolle des Zustandes des Prüflings nach den

Stößen. Für die Versuche wird HS 1 auf 0 geschaltet. Anschliessend an die Versuche kann auf Stellung 1, 2, 3, 4, die Transfercharakteristik der Tore 1, 2, 3, 4 gemessen werden. Im abgefallenen Zustand (Relais R) wird C auf  $V_{Stoss}$  aufgeladen. Durch die manuelle Auslösung zieht R für eine gewisse Zeit an. Dabei wird C entladen, das heisst,  $V_{cc}$  praktisch auf  $V_{Stoss}$  angehoben, wobei n1 sperrt.

### 3.2 Zerstörung durch einmaligen Stoss

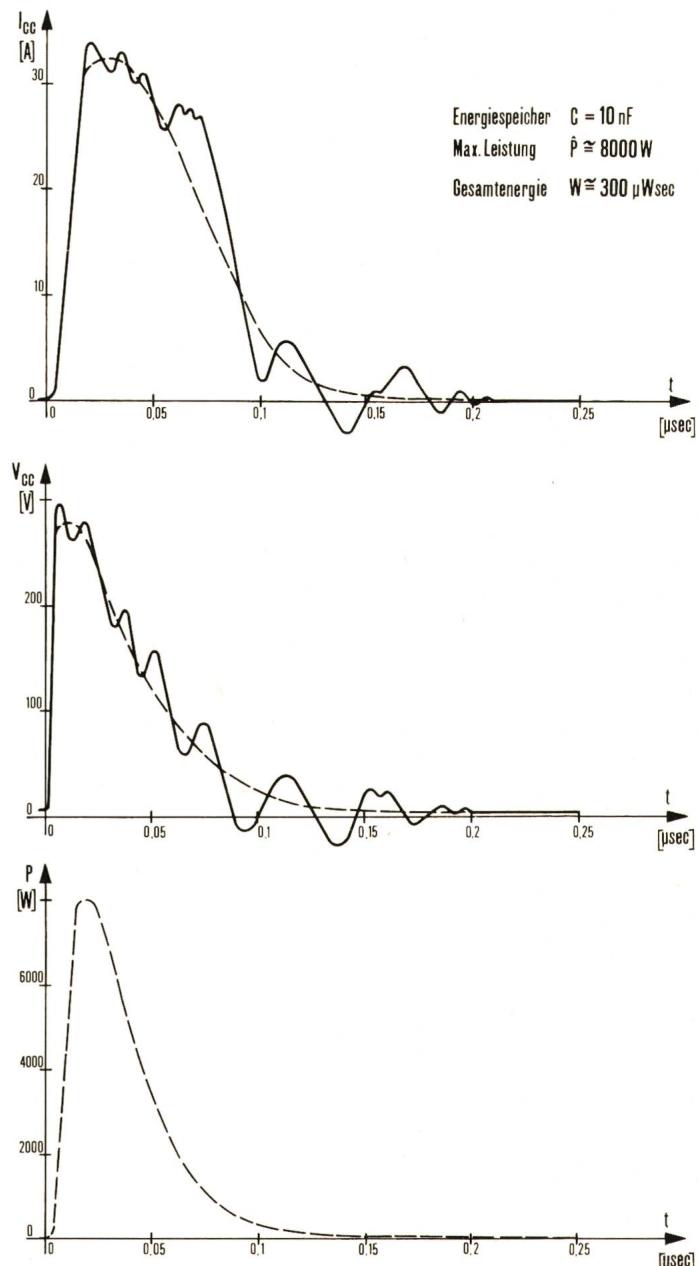

Wie bereits in der Einleitung erwähnt, interessiert von jedem Stoss die dabei maximal auftretende Leistung und die Gesamtenergie. Da die zwischen Energiespeicher und IC auftretenden Verlustfaktoren (Leistungseffekte, Kontaktwiderstand, Kondensatorenrsatzschaltbild usw.) theoretisch nicht vollständig zu erfassen sind, wurden während des Stosses Strom- und Spannung in Funktion der Zeit oszillographiert. Es zeigt sich dabei, dass die übertragene Energie massgebend vom Kondensatortyp beeinflusst wird. Das heisst, dass aus der Kondensatogrösse die maximale Leistung und Energie nur ungenau abgeleitet werden kann. Typische Kurven sind in Fig. 6 gezeigt. Selbst eine kleine Anzahl dieser Stosse ( $n \leq 10$ ) führen zur funktionellen Zerstörung des IC's; das heisst, mindestens eine Funktion erfüllte nicht mehr die Garantiebedingungen des Herstellers.

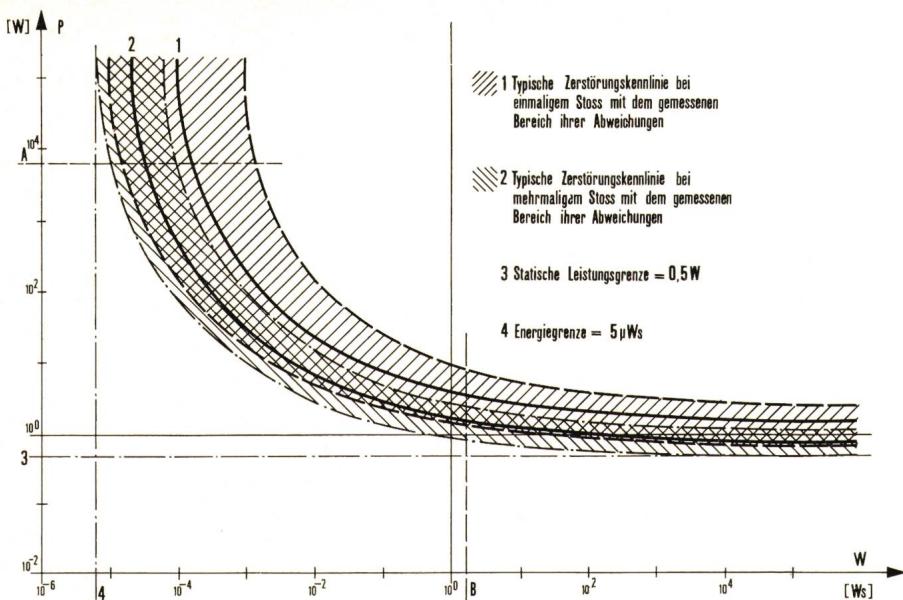

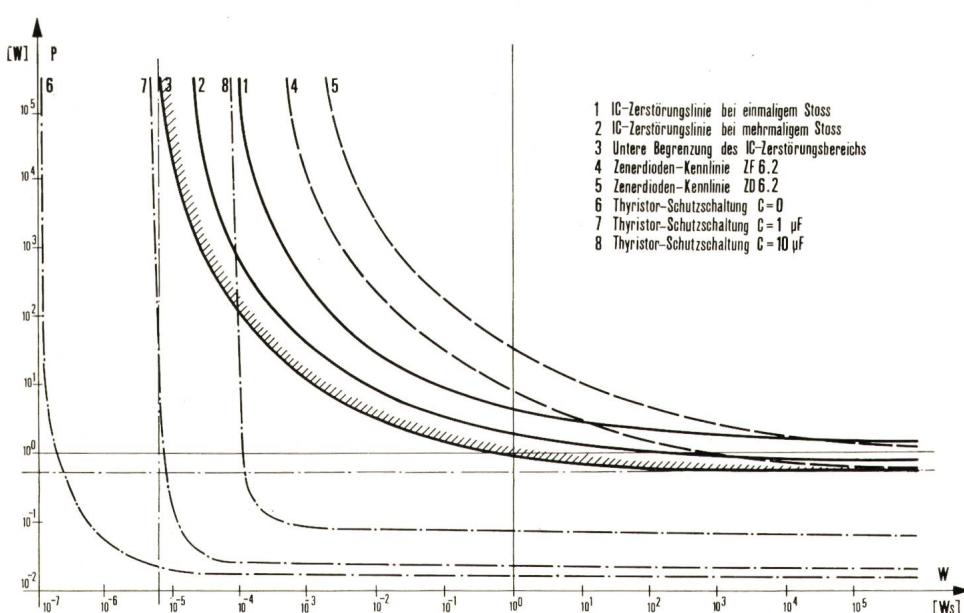

Trägt man die damit erhaltenen Leistungen und Energien in doppeltlogarithmischem Maßstab auf, so erhält man eine hyperbelähnliche Kurve, welche man als Zerstörungskennlinie bei einmaligem Stoss bezeichnen kann (Fig. 7 — Kurve 1). Es ist zu beachten, dass diese typische Kennlinie speziell für den Baustein SN 7400 N bzw. FLH 101 aufgenommen wurde. Es

Fig. 5

**Messung der dynamischen Überspannungsempfindlichkeit**

$V_H$  Hilfsspannung;  $V_{CC}$  Speisespannung; C Energiespeicher; n1 Entkopplungsdiode; R Hilfsrelais;  $R_E$  Abschlusswiderstand am Eingang;  $R_A$  Abschlusswiderstand am Ausgang

|                                  |                                 | Hersteller A |           | Hersteller B |           | Einheit |

|----------------------------------|---------------------------------|--------------|-----------|--------------|-----------|---------|

|                                  |                                 | 0-Zustand    | 1-Zustand | 0-Zustand    | 1-Zustand |         |

| <b>Knickpunkt KP</b>             |                                 | ≈ 12         | ≈ 12      | ≈ 12         | ≈ 21      | V       |

| $V_{eG} < V_{ee} \leq KP$        | $R_{ee}$ abs                    | ≈ 450        | ≈ 700     | ≈ 450        | ≈ 700     | Ω       |

|                                  | $R_{ee}$ diff                   | ≈ 450        | ≈ 700     | ≈ 450        | ≈ 700     | Ω       |

| $V_{ee} > KP$<br>Kein Durchbruch | $R_{ee}$ abs                    | 50...450     | 70...700  | 50...450     | 100...700 | Ω       |

|                                  | $R_{ee}$ diff                   | ≈ 10         | ≈ 40      | ≈ 10         | ≈ 40      | Ω       |

| $V_{ee} > KP$<br>Durchbruch      | $R_{ee}$ abs<br>$R_{ee}$ diff } | < 10         | < 10      | < 10         | < 10      | Ω       |

$R_{ee}$  abs = Absoluter Widerstand über den Speiseanschlüssen.

$R_{ee}$  diff = Differentieller Widerstand über den Speiseanschlüssen.

$V_{eG}$  = Garantierte maximale Speisespannung = 7 V.

ist offensichtlich, dass die spezifische Schaltung und die Chipgrösse eine Rolle spielen. Im weiteren existiert eine grosse Streuung, (ca. ein Faktor 2...10) zwischen den verschiedenen Herstellern sowie zwischen verschiedenen Diffusionschargen beim gleichen Hersteller. Die Kurve wird im übrigen nach rechts durch das thermische Langzeitverhalten und nach oben durch mögliche kalte Durchschläge begrenzt.

### 3.3 Beschädigung bzw. Zerstörung durch mehrmalige Stöße

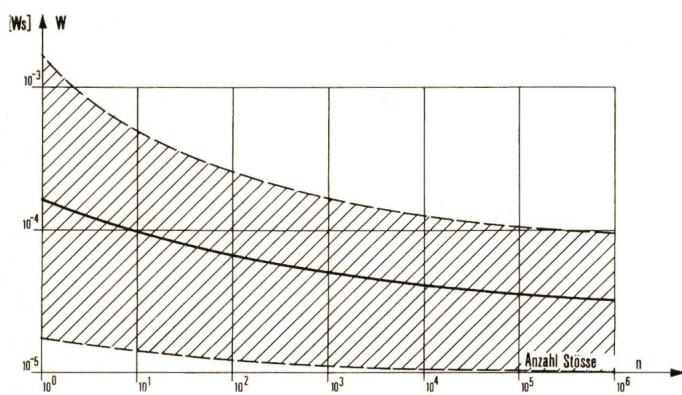

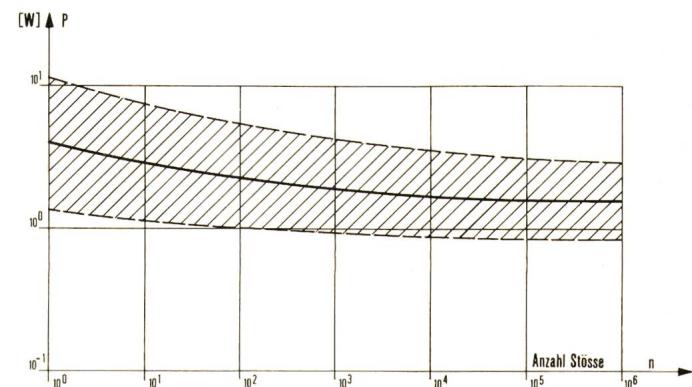

Benötigt man  $n > 100$  Stöße, so spricht man von einer Beschädigung bzw. Zerstörung durch mehrmalige Stöße. Um den Zusammenhang «Energie — Anzahl Stöße» festzuhalten, wählt man einen kleinen Energiespeicher. In diesem Fall befindet man sich im vertikalen Teil der Kurve (Fig. 7 — A). Um den Zusammenhang «Leistung — Anzahl Stöße» zu bestimmen, arbeitet man mit einem grossen Energiespeicher. Das heisst, man befindet sich im flachen Teil der Kurve (Fig. 7 — B). Die beiden Funktionen «Anzahl Stöße bis zur Zerstörung in Funktion der Energie bzw. Leistung» sind in Fig. 8 und 9 gezeigt.

Der Grenzfall, bei dem keine wesentlichen Veränderungen mehr zu beobachten sind, wurde mit  $n \geq 10^6$  Stößen definiert. Die dabei bestimmte Energie bzw. Leistung kann ebenfalls als hyperbelähnliche Kurve aufgezeichnet werden (Fig. 7 — Kurve 2). Diese Kurve hat ebenfalls eine relativ grosse Streuung. Nach den beschränkten Messungen zu urteilen, dürfte die Streuung ebenfalls ein Faktor 2 der typischen Werte betragen (sowohl für Leistung wie für Energie).

Damit wurden die wesentlichen Kriterien für die Beurteilung des dynamischen und statischen Verhaltens einer Schutzschaltung bestimmt.

## 4. Übertragung der gefundenen Kriterien auf die gesamte TTL-Familie

Es stellt sich hier die Frage, welcher Baustein ist gegen Überspannungen am empfindlichsten. Dabei stehen sich zwei Meinungen grundsätzlich gegenüber.

Nach der ersten Ansicht existiert immer ein schwächstes Element, dessen Strom-Spannungscharakteristik für den Ausfall des gesamten IC's massgebend ist. Das heisst, die Chipgrösse ist ohne wesentliche Bedeutung für die Überspannungs-

Fig. 6

Zerstörung eines IC's durch einmaligen Stoß

Fig. 7

Dynamische Überspannungsempfindlichkeit des SN7400/FLH101

P Leistung; W Energie; A Überspannungsempfindlichkeit für kleine Energiespeicher; B Überspannungsempfindlichkeit für grosse Energiespeicher

mpfindlichkeit. Da die einzelnen Teilschaltungen (Eingangs-, Ausgangs- und Verknüpfungsteil) der IC-Logik immer wieder die gleichen Elemente (Transistoren, Widerstände) besitzen, so sind die aufgenommenen Kurven für alle Bausteine gültig.

Nach der zweiten Ansicht besteht der IC aus einer Parallelschaltung vieler ähnlicher Elemente. Beim Fehlen eines Elementes mit ausgeprägter Zenercharakteristik (z. B. Zenerdiode), wie das bei der TTL-Familie der Fall ist, tritt eine Ableitung der Störleistung bzw. -energie über mehrere Pfade auf. Je grösser der Chip ist, das heisst, je mehr Elemente sich auf dem Chip befinden, desto mehr Elemente dürfen sich an der Ableitung der Störung beteiligen, und desto unempfindlicher wird der Chip gegen Überspannungen. Aus diesem Grunde wurde auch ein IC mit kleinem Chip (SN 7400 N) zur Bestimmung der Kurven verwendet.

Gesamthaft gesehen dürfen daher die bestimmten Kurven als «worst case» innerhalb der TTL-Familie anzusprechen sein, wobei allerdings eine messtechnische Verifizierung noch fehlt.

## 5. Schutz integrierter Schaltungen gegen Überspannungen

### 5.1 Allgemeines

Grundsätzlich müssen zwei Arten von Störungen unterschieden werden:

Zusammenhang zwischen Energie W und Anzahl Stößen, die zur Zerstörung eines IC's nötig sind (Fig. 7a)

- 5.1.1 Kurze, sich wiederholende Überspannungsspitzen, die im Normalbetrieb des Systems auftreten (z. B. Spitzen beim Abschalten induktiver Lasten). Die IC's müssen vor diesen Spitzen geschützt werden, ohne dass deswegen das Funktionieren des Systems beeinträchtigt wird.

- 5.1.2 Überspannungen variabler Länge, die sich im allgemeinen nicht wiederholen und die bei gestörtem Betrieb (Fremdspannungen, Kurzschlüsse usw.) auftreten. Die IC's müssen vor diesen Spitzen geschützt werden, wobei das System im Notfall auch abgeschaltet werden kann.

Der wesentliche Unterschied zwischen den beiden Fällen ist der, dass bei 5.1.1 der Störer und somit seine Störleistung und Störennergie wie auch der Ort der Störungseinspeisung bekannt ist. Das heisst, es können Gegenmassnahmen am Störer selbst getroffen werden, oder aber in die Leitungen zwischen dem Störer und dem übrigen System eingebaut werden. Die möglicherweise noch vorhandenen Restüberspannungen kön-

Fig. 9

Zusammenhang zwischen Leistung P und Anzahl Stößen, die zur Zerstörung eines IC's nötig sind (Fig. 7b)

nen dann leicht mit einer Zenerdiode beseitigt werden. Zenerdioden sind, wie Versuche zeigten, auch dynamisch dazu geeignet, sofern ihre Grenzdaten (Leistung und Ableitstrom) eingehalten werden.

Im Fall 5.1.2 ist der Störer wie auch sein Einspeisepunkt unbekannt. Der Störer kann möglicherweise direkt ins System einwirken. Das heisst, Störleistung und -energie sind im allgemeinen für einen einfachen Zenerschutz zu gross. In diesem Fall bleibt nichts anderes übrig, als die Speisung kurzzuschliessen.

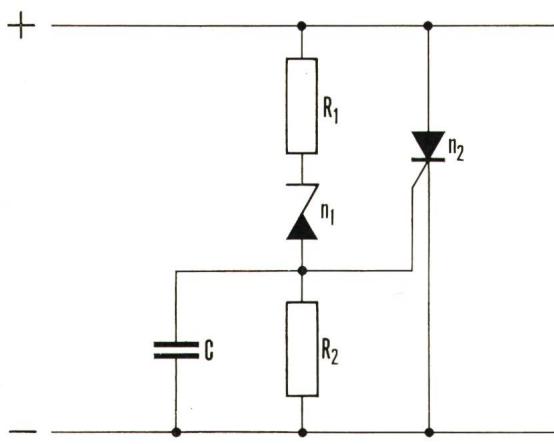

### 5.2 Schutzschaltungen für IC's bei unbekannten Überspannungen

Auch hier ist eine Zenerdiode bei kleinen Störungen anwendbar. Für grössere Störungen besteht eine Schutzschaltung im wesentlichen aus Abtastschaltung, Trigger ev. Impulsstufe und Schutzkreis mit Schalter. Wird durch die Abtastschaltung ein Ansteigen der Speisespannung über ein zulässiges Mass

Fig. 10

Überspannungsschutz mit Thyristor

$R_1$  Begrenzungswiderstand des Zenerstroms;  $R_2$  Gitterwiderstand;  $n_2$  Schutzthyristor;  $C$  Verzögerungskondensator;  $n_1$  Zenerdiode zur Bestimmung der Schaltschwelle

festgestellt, so wird über die Trigger bzw. Impulsstufe der Schutzkreis angesteuert, das heisst, der Schalter wird geschlossen. Das Schliessen bewirkt einen Kurzschluss der Speisung, das heisst, die Speisespannung bricht zusammen. Nach Unterschreiten einer Sicherheitsgrenze kann nun der Schalter wieder manuell oder automatisch geöffnet werden.

Es besteht auch hier grundsätzlich die Möglichkeit des Einsatzes einer Zenerdiode. Bei Überschreiten der Zenerspannung beginnt ein Strom zu fliessen, der bei Überspannungsfällen im allgemeinen rasch zur Zerstörung der Zenerdiode führt. Dabei kommt es in vielen Fällen zum Kurzschluss der Diode, was dem Schliessen des Schalters entspricht. Eine weitere einfache Schaltung besteht aus einem gleichstrommässig angesteuerten Thyristor (Fig. 10).  $C$  erlaubt eine Begrenzung des Frequenzgangs der Schaltung, so dass eine Angleichung an die dynamische Störleistungs-/Störennergie-Kennlinie des IC's möglich ist. Anstelle des einfachen  $RC$ -Netzwerkes mit Zenerdiode lässt sich auch eine echte Triggerschaltung oder Impulsstufe aufbauen.

Im folgenden sollen diese beiden Schaltungen bzw. ihre Kennlinie mit den IC-Kennlinien verglichen werden. Die Ausmessung der Kennlinie erfolgte, indem die Schutzschaltungen

anstelle der IC's in die bereits erwähnten Versuchseinrichtungen eingebaut und analog einem IC getestet wurden.

### 5.3 Kurzschluss-Schutz von IC's durch Zenerdiode

Zenerdioden wurden als Referenz- und Stabilisierungselemente geschaffen. Ihr Einsatz als kurzschliessender Überspannungsschutz wurde primär vom Hersteller nicht betrachtet. Zenerdioden sind aus dieser Betrachtung heraus relativ zählebige Elemente. Statisch betrachtet muss die Zenerspannung unter 7 V liegen. Aus diesem Grunde wurden aus der E 24-Reihe die Zenerspannung 6,2 V (5,8...6,6 V) ausgewählt. Die minimale Leistung der auf dem Markt erhältlichen Zenerdioden liegt allgemein oberhalb 200 mW. Dies ist die gleiche Größenordnung, bei der auch die Leistung der IC's liegt.

Bestimmt man die nötige Energie und Leistung zur Zerstörung der Zenerdiode, so liegt man im allgemeinen oberhalb der IC-Kennlinie für einmalige Stöße. Das heisst, es zeigt sich, dass diese Schutzmassnahmen statisch und für energiereiche Stöße, bei denen es im wesentlichen auf die Leistung ankommt, einen gewissen Schutz darstellen, der aber in keinem Fall garantiert werden kann. Bei energiearmen Stößen mit grösserer Leistung ist die Kurzschlusswirkung ungenügend.

Allgemein ist zu sagen, dass die Zerstörungskennlinie der Zenerdiode ähnlich wie diejenige des IC's verläuft; dies lässt sich mit dem praktisch identischen Zerstörungsmechanismus erklären. Da die Zenerdiode nicht für diese Schutzfunktion speziell entwickelt wurde, liegen ihre Kurven auch nicht wesentlich unterhalb derjenigen der IC's. Ihre Kurzschlusswirkung ist daher zumindest fraglich. Dies ergibt sich aus dem graphischen Vergleich (Fig. 11).

### 5.4 Schutz von IC's durch Thyristoren

Diese Schaltungen wurden speziell für ihre Schutzfunktion entworfen. Die Auslösung ihrer Schutzfunktion kann daher mit bedeutend geringeren Leistungen bzw. Energien erfolgen, als die integrierten Schaltkreise zu ihrer Zerstörung benötigen. Es ist jedoch zu beachten, dass nach erfolgter Triggerung der Thyristor noch eine bestimmte Zeit benötigt (ca. 0,1...10  $\mu$ s) um vollständig leitend zu werden. Während dieser Zeit ist die Schutzwirkung nur unvollständig. Eine zusätzlich parallelgeschaltete Zenerdiode stellt hier die ideale Ergänzung dar.

In Fig. 11 wird die Kennlinie der Thyristorschutzschaltung mit  $C = \text{variabel}$  mit den IC-Kennlinien verglichen. Es zeigt sich, dass die Schutzfunktion, falls  $C \leq 1 \mu\text{F}$  gewählt wurde, gut erfüllt ist. Mit  $C = 0$  besteht die Gefahr eines zufälligen Zündens durch kleine Störspitzen, die den IC überhaupt nicht beschädigen.

Das Rückstellen der beschriebenen Schutzschaltung erfordert

Fig. 11

Vergleich der IC-Überspannungsempfindlichkeit mit den Charakteristiken verschiedener Schutzschaltungen

$P$  Leistung;  $W$  Energie

einen Rückgang des Thyristorstroms unter den Haltestrom sowie eine Spannung unterhalb der Triggerschwelle. Dies kann erreicht werden durch kurzzeitiges Entfernen der Schutzschaltung von der Speisung, oder aber, durch einen zweiten Hilfsschaltkreis mit Thyristor. Die Rückstellung erfolgt im allgemeinen manuell, da vor der Rückstellung der Grund der Überspannung ja untersucht werden muss. Eine automatische Rückstellung wäre nach Ablauf einer gewissen Zeit möglich; sie darf jedoch nur erfolgen, falls die Überspannung tatsächlich verschwunden ist (im Falle transienter Überspannungen).

## 6. Schlussfolgerungen

Die gewonnenen Erkenntnisse der IC-Überspannungsempfindlichkeit erlauben, jeden Überspannungsableiter statisch und dynamisch auf seine Sicherheit zu testen. Im weiteren kann gesagt werden, dass Überspannungsableiter, die eine

Kombination von schneller Begrenzerschaltung mit einer Kurzschlußschaltung aufweisen, den einzigen sicheren Schutz darstellen. Örtlich gesehen, sollte die Begrenzschalterung möglichst nahe beim zu schützenden IC angebracht werden, wogegen der Kurzschlußschutz aus Überwachungsgründen im allgemeinen pro Teilsystem (z. B. Elektronikkassette) zentral eingesetzt werden kann.

## Literatur

- [1] K. Reiss, H. Liedl und W. Spichall: Integrierte Digitalbausteine. Kleines Praktikum. München, Siemens AG, 1970.

- [2] Integrated electronic system. Edited by the Staff of Science and Technology, Aerospace Division, Westinghouse Electric Corporation. Englewood Cliffs, N. J., Prentice-Hall, 1970.

- [3] J. Iseli: Speisungssysteme und Erdungsführung in digitalen Steuerungen Elektr. Ausrüstung 11(1970)3, S. 19...23.

## Adresse des Autors:

J. Iseli, Sprecher & Schuh AG, 5000 Aarau.

## EUROCON 71

Die von der Region 8 des IEEE vom 18. bis 22. Oktober 1971 in Lausanne durchgeführte Tagung genoss die Unterstützung von 34 nationalen europäischen Institutionen, unter ihnen insbesondere derjenigen des Vereins des Gastlandes, nämlich des Schweiz. Elektrotechn. Vereins (SEV). Die Konferenz, die offenbar einem starken Bedürfnis entsprach, erreichte ein unerwartet grosses Echo: Über 1100 Teilnehmer aus vielen Ländern Europas und aus Übersee verfolgten während 4 Tagen etwa 250 Vorträge und Diskussionen zu den Hauptthemen:

- Informationsverarbeitung in grossen Systemen

- Weitverkehrssysteme der Nachrichtentechnik

- Festköperschaltkreise

- Energieverteilung

- Biomedizinische Technik

- Elektronische Zeitmessung

Besonders freuten sich die Veranstalter über die 120 Studenten, welche aus der Schweiz und mehreren europäischen Hochschulen nach Lausanne gekommen waren, um ihren fachlichen und menschlichen Horizont zu erweitern. Für sie war ein eigenes

Programm besonders geeigneter Vorträge zusammengestellt und vorbereitet worden. Neben den vorangehend erwähnten Hauptthemen der EUROCON 71, die auf etwa gleichmässig verteiltes und beträchtliches Interesse gestossen sind, verdienen zwei kleinere Konferenzen besondere Erwähnung: Die Vorträge und Diskussionen zu den Themen «Standardisation» und «Impact of Electronics in Power Distribution» erwiesen sich für die betreffenden Teilnehmer als besonders fruchtbar.

Viele Besucher schätzten die Möglichkeiten zu Kontakten mit Forschern und Entwicklern aus verschiedenen Gebieten der Elektrotechnik, die ihnen durch das breite Spektrum der Themenkreise der EUROCON 71 geboten wurden.

Der «Convention Digest», der in englisch das Konferenzprogramm, zweiseitige Zusammenfassungen der Referate sowie eine Adressliste der Referenten und Organisationskomitees enthält, ist zum Preis von Fr. 25.— erhältlich (Vorausbezahlung durch Check). Von mehr als zwei Dritteln aller Vorträge sind Mikrofilme der vollen Texte erhältlich; Auskünfte über die Gruppierung der Filme und die Preise erteilt das Sekretariat der EUROCON 71: Sekretariat EUROCON 71, 24, Chemin de Bellevue, 1007 Lausanne.