**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätswerke

**Band:** 60 (1969)

**Heft:** 23

**Artikel:** Der Feldeffekttansistor als steuerbares Element

**Autor:** Ow, H.-P. von

**DOI:** <https://doi.org/10.5169/seals-916195>

#### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

#### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 16.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Der Feldeffekttransistor als steuerbares Element

Vortrag, gehalten an der 28. Schweiz. Tagung für elektrische Nachrichtentechnik vom 12. Juni 1969 in Fribourg,

von H.-P. von Ow, Zürich

337 - 352

621.382.323

## 1. Einleitung

Der Feldeffekttransistor (FET) kann auf zwei Arten als steuerbares Element verwendet werden: Entweder als steuerbarer Widerstand im Gebiet um den Nullpunkt oder in regelbaren Selektivverstärkern durch Ausnutzung der von der Vorspannung abhängigen Steilheit im aktiven Gebiet. Hier wird vor allem die erste Möglichkeit behandelt, da darüber nur wenig Literatur zu finden ist. Ausgehend von der mathematischen Formel für die Kennlinien wird der Zusammenhang zwischen Klirrfaktor, Aussteuerbarkeit und Regelbereich bei steuerbaren FET-Widerständen hergeleitet und anschliessend nach Möglichkeiten gesucht, um die Kennlinien zu linearisieren, um die Verzerrungen zu vermindern.

Steuerbare Widerstände werden gebraucht in Regelverstärkern, steuerbaren Dämpfungen, Oszillatoren usw. Neben FET können noch temperatur- und lichtabhängige Widerstände, Dioden und Transistoren verwendet werden. Sie haben entweder eine grosse Regelzeitkonstante oder eine sehr kleine zulässige Amplitude.

Alle folgenden Betrachtungen gelten für N-Kanal-FET. Das P-Kanal-Verhalten erhält man durch Umkehr der Vorzeichen. Obwohl hier speziell der Sperrsicht-FET betrachtet wird, kann alles folgende mit kleinen Abänderungen auch auf den MOS-FET übertragen werden.

## 2. Das FET-Kennlinienfeld

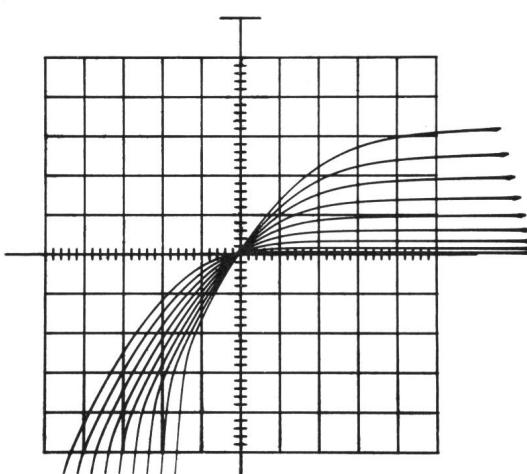

Fig. 1 zeigt das Kennlinienfeld eines Sperrsicht-FET im 1. und 3. Quadranten (Vorwärts- und Rückwärtsgebiet).

Im 1. Quadranten sind die Kennlinien ähnlich wie bei einer Pentode, mit welcher der FET wegen seiner hohen Eingangsimpedanz manchmal verglichen wird. Als ganz wesentlichen Unterschied zur Röhre hat der FET aber ein Rückwärtskenn-

Fig. 1

Kennlinienfeld des Feldeffekttransistors MPF 103 im 1. und 3. Quadranten

Horizontal:  $U_{DS}$  [0,5 V/Skalenteilung (Skt.)]

Vertikal:  $I_D$  [0,5 mA/Skalenteilung (Skt.)]

Parameter:  $U_{GS}$  (0...1,6 V in Stufen von 0,2 V)

linienfeld. Bekanntlich funktioniert er ja dadurch, dass der Widerstand eines Halbleiterplättchens (genauer: der Querschnitt des Kanals) durch ein elektrisches Feld verändert wird, während bei der Röhre der Strom durch Elektronenemission aus der Kathode entsteht. Bei der Pentode ist der Strom nur in einer Richtung möglich, während der FET für positive und negative Drainspannungen leitet.

Die FET-Kennlinien sind nur abhängig von  $U_{GS}$ , nicht aber von  $U_{DS}$ , solange  $U_{DS}$  sehr klein ist. Es ist möglich, den FET

Fig. 2

Gleiches Kennlinienfeld wie Fig. 1

Das Gebiet um den Nullpunkt ist 10fach vergrössert.

Horizontal:  $U_{DS}$  [50 mV/Skt.]

Vertikal:  $I_D$  [50 uA/Skt.]

Parameter:  $U_{GS}$  (0...-2,0 V in Stufen von 0,2 V)

in diesem Gebiet als steuerbaren linearen Widerstand zu verwenden. Für grössere Aussteuerungen wird er nichtlinear, weil der Drainstrom  $I_D$  nun auch von  $U_{DS}$  abhängig ist. Fig. 2 zeigt das gleiche FET-Kennlinienfeld wie Fig. 1 im Gebiet um den Nullpunkt zehnfach vergrössert. Alle Kennlinien gehen exakt durch den Nullpunkt; es gibt also hier keinen Offset wie beim bipolaren Transistor. Der minimale Widerstand bei  $U_{GS} = 0$  beträgt je nach Typ ungefähr 10...1000  $\Omega$ . Der maximale Widerstand bei gesperrtem Kanal, d. h. bei  $U_{GS} < U_p$  (beide Spannungen sind negativ bei N-Kanal-FET), ist laut Datenblatt > 50 M $\Omega$ . Zwischen diesen beiden extremen Werten kann der Widerstand durch die angelegte Gatespannung stetig variiert werden. Die Aussteuerbarkeit ist aber stark abhängig von  $U_{GS}$ . Bei grossen Widerständen sind die Kennlinien viel stärker gekrümmmt.

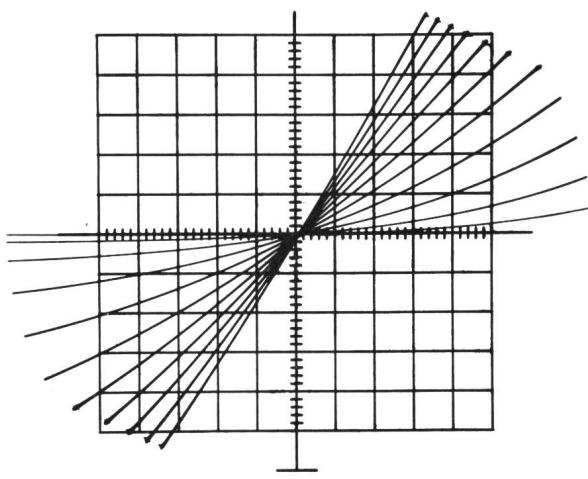

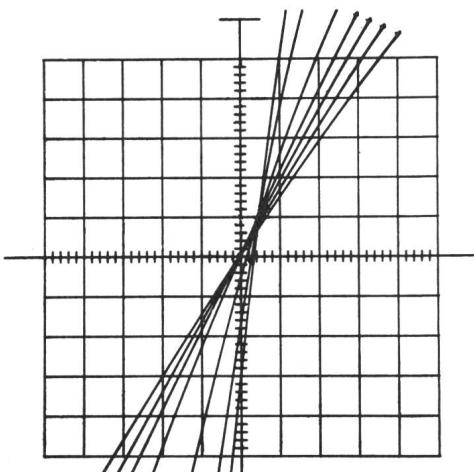

Zum Vergleich zeigt Fig. 3 Kennlinien eines bipolaren Siliziumtransistors (BC 107) im gleichen Maßstab. Ein paar Nachteile gegenüber dem FET lassen sich sofort erkennen:

Die inverse Stromverstärkung ist viel kleiner als jene im Vorwärtsgebiet; die Kennlinien zeigen keine Zentrale Symmetrie. Sie gehen auch nicht durch den Nullpunkt wie beim FET. Dieser benötigt praktisch keine Steuerleistung, während bei

Fig. 3

**Kennlinien eines bipolaren Siliziumtransistors**

Horizontal:  $U_{CE}$  (50 mV/Skt.)

Vertikal:  $I_C$  (50  $\mu$ A/Skt.)

Parameter:  $I_B$  (2  $\mu$ A/Skt.)

Transistoranalogschaltern sehr grosse Basisströme auftreten können wegen der kleinen inversen Stromverstärkung. Dafür kann der minimale Durchlasswiderstand viel kleiner gemacht werden als beim FET.

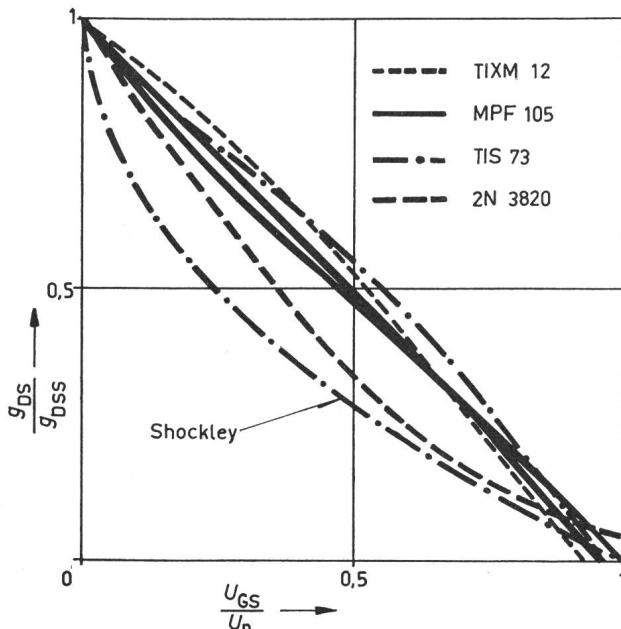

Shockley fand in seinen theoretischen Untersuchungen über Feldeffekttransistoren folgende Abhängigkeit des differentiellen Leitwerts im Nullpunkt von  $U_{GS}$ :

$$g_{DS} = g_{DSS} \left( 1 - \sqrt{\frac{U_{GS}}{U_p}} \right) \quad (1)$$

worin

$g_{DSS}$  differentieller Leitwert bei  $U_{GS} = U_{DS} = 0$  und

$U_p$  Abschnür- oder Pinch-off-Spannung, bei der  $I_D = 0$ ,

$g_{DS} = 0$ .

Den Verlauf von Gl. (1) zeigt Fig. 4. Messungen zeigen aber, dass  $g_{DS}(U_{GS})$  viel besser durch einen linearen Verlauf approximiert wird:

$$g_{DS} = g_{DSS} \left( 1 - \frac{U_{GS}}{U_p} \right) \quad (2)$$

Fig. 4

**Dynamischer Leitwert im Nullpunkt in Funktion von  $U_{GS}/U_p$**

Eingezeichnet sind Gl. (1) und (2) sowie gemessene Kurven für vier verschiedene FET

Infolge der Einfachheit und guten Genauigkeit wird meistens diese Formel verwendet. Bei sehr kleinen Leitwerten, d. h. bei  $U_{GS}$  nahe  $U_p$ , kann der entstehende relative Fehler aber ziemlich gross werden.

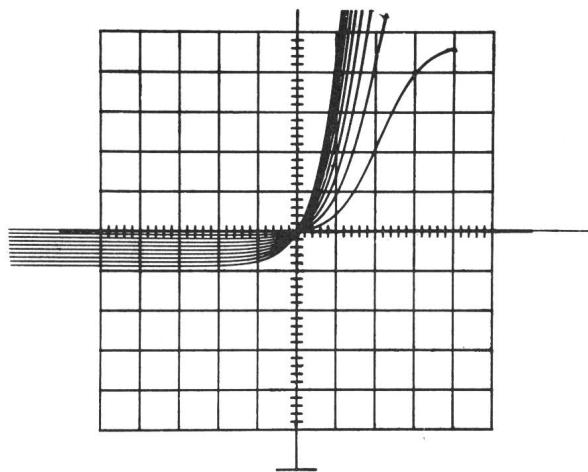

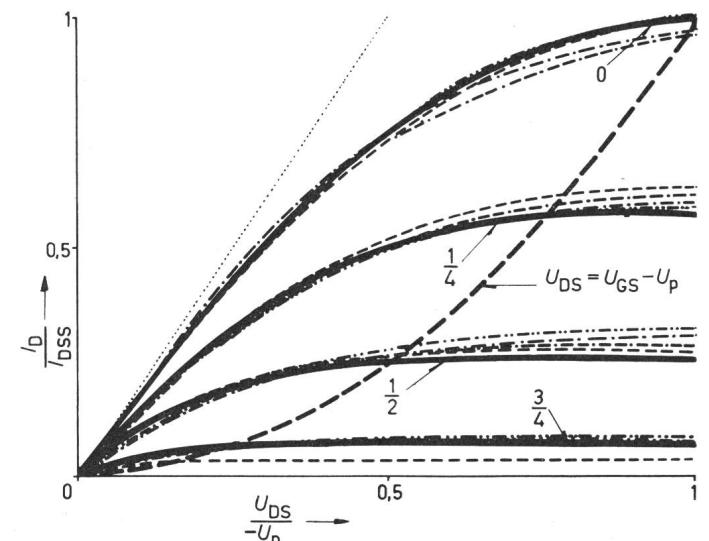

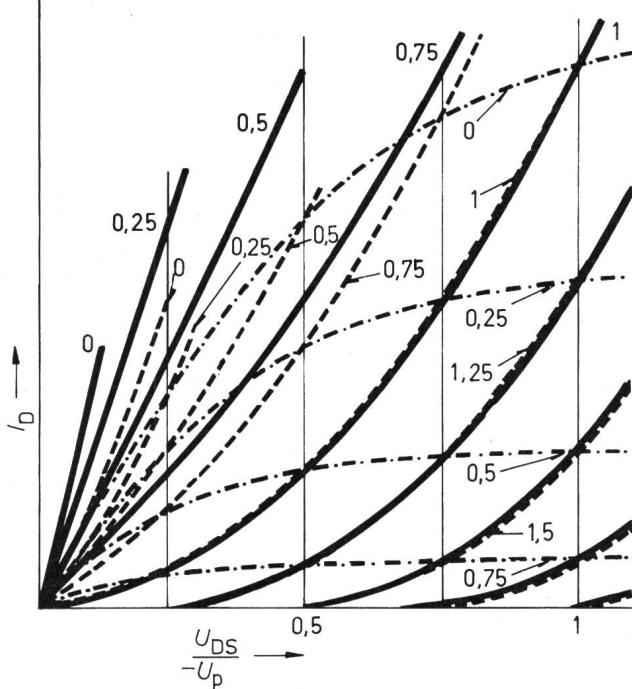

Fig. 5 zeigt die Kennlinien im ersten Quadranten. Mit wachsender Drainspannung  $U_{DS}$  nimmt der Drainstrom  $I_D$  immer weniger zu, bis er schliesslich im Pinch-off-(Abschnür-)Gebiet von  $U_{DS}$  unabhängig wird. Die Region, in der  $I_D$  von  $U_{DS}$  und  $U_{GS}$  abhängt, wird Ohmsches Gebiet genannt. Die Grenze zum Pinch-off-Gebiet ist bei:

$$U_{DS} = U_{GS} - U_p \quad (3)$$

Im Pinch-off-Gebiet ist  $I_D$  nur abhängig von  $U_{GS}$ .

$$I_D = I_{DSS} \left( 1 - \frac{U_{GS}}{U_p} \right)^2 \quad (4)$$

worin

$I_{DSS}$  Drainstrom bei  $U_{GS} = 0$ ,  $U_{DS} > -U_p$

Fig. 5

**Kennlinien im ersten Quadranten normiert auf  $I_{DSS}$  und  $U_p$**

Parameter ist die auf  $U_p$  normierte Gatespannung  $U_{GS}$ . Gestrichelt eingezeichnet sind vier gemessene Kurven für verschiedene FET, ausgezogen der Verlauf der mathematischen Approximation nach Gl. (5)

Die  $I_D(U_{DS}, U_{GS})$ -Approximation im Ohmschen Gebiet kann folgendermassen gefunden werden: Bekannt sind zwei Punkte, der Nullpunkt und der durch die Gl. (3) und (4) gegebene Grenzpunkt zum Pinch-off-Gebiet, wo die Tangente horizontal sein muss. Damit lässt sich eine Funktion 2. Grades bestimmen:

$$I_D(U_{DS}, U_{GS}) = \frac{2 I_{DSS}}{U_p} \left[ U_{DS} \left( 1 - \frac{U_{GS}}{U_p} \right) + \frac{U_{DS}^2}{2 U_p} \right] \quad (5)$$

gültig für  $0 \leq U_{DS} \leq (U_{GS} - U_p)$ ,  $U_p \leq U_{GS} \leq 0$ .

Durch Differenzierung erhält man  $g_{DS}$ :

$$\frac{d I_D}{d U_{DS}} = g_{DS} = - \frac{2 I_{DSS}}{U_p} \left( 1 - \frac{U_{GS}}{U_p} \right) \quad (6)$$

wenn  $U_{DS} = 0$

Durch Vergleich mit Gl. (2):

$$g_{DSS} = - \frac{2 I_{DSS}}{U_p} \quad (7)$$

Bei bekanntem  $I_{DSS}$  und  $U_p$  lässt sich das gesamte Kennlinienfeld in erster Näherung vollständig bestimmen. In Fig. 5 sind 4 gemessene Kennlinienfelder mit dem berechneten verglichen.

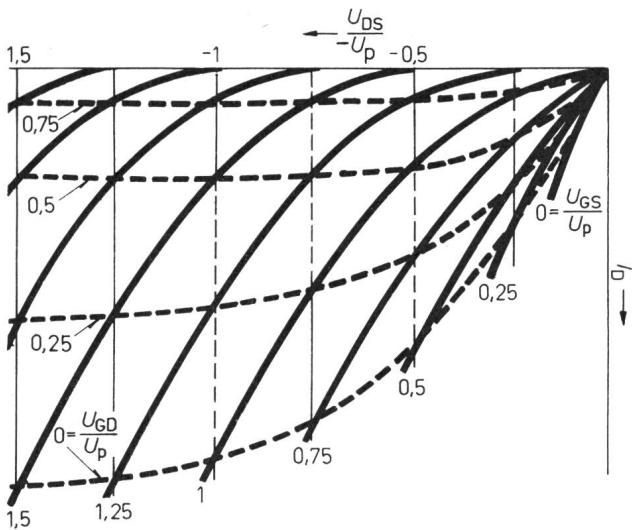

Fig. 6

**Konstruktion des Rückwärtskennlinienfeldes aus dem Vorwärtskennlinienfeld**

Im gestrichelten zum ersten Quadranten zentrale symmetrischen Kennlinienfeld ist  $U_{GD}$  Parameter. Man findet die gesuchten, ausgezogenen Kennlinien mit  $U_{GS}$  als Parameter, indem man die Punkte sucht, die Gl. (8) erfüllen

Gl. (5) setzt sich zusammen aus einem erwünschten linearen und einem unerwünschten quadratischen Term, der für die Verzerrungen verantwortlich ist.

Wenn der lineare Term klein ist ( $U_{GS} \gg U_P$ ), kommt der von  $U_{GS}$  unabhängige quadratische Term in die gleiche Größenordnung wie der lineare.

Die Kennlinien im dritten Quadranten lassen sich aus jenen im ersten Quadranten herleiten. Die meisten FET sind symmetrisch aufgebaut; Drain und Source können vertauscht werden. Die Kennlinienfelder haben die gleiche Form, wenn nach der Vertauschung die Gatespannung auf den Drain- statt auf den Sourceanschluss bezogen wird.  $U_{DS}$  und  $I_D$  haben umgekehrtes Vorzeichen. Dieser Fall entspricht den gestrichelten Kennlinien in Fig. 6. Sie gelten für  $U_{GD} = \text{konstant}$ . Weil aber im Rückwärtsgebiet wie im Vorwärtsgebiet  $U_{GS}$  der Steuerparameter ist, ist  $U_{GD}$  abhängig von  $U_{GS}$  und  $U_{DS}$ :

$$U_{GD} = U_{GS} - U_{DS} \quad (8)$$

Das gesuchte Kennlinienfeld  $I_D(U_{DS}, U_{GS})$  findet man aus den  $I_D(U_{DS}, U_{GD})$ -Kennlinien, indem man die entsprechenden

Fig. 7

**Kennlinienfeld des FET im Gatestromgebiet**

Horizontal:  $U_{DS}$  (50 mV/Skt.)

Vertikal:  $I_D$  (50  $\mu$ A/Skt.)

Parameter:  $U_{GS}$  (positiv), Stufenhöhe = 0,2 V, Innenwiderstand der Gate-Spannungsquelle ist  $300\Omega$

Punkte nach Gl. (8) aufsucht. Gemessene Kennlinien stimmen sehr gut mit den derart konstruierten überein. Es lässt sich zeigen, dass Gl. (5) auch im Rückwärtsgebiet gilt, falls  $U_P \leq U_{GS}$ ,  $U_{GS} \leq U_{DS}$ . Wenn  $U_{DS} < U_{GS}$ , beginnt der Gatestrom zu fliessen. Die Kennlinien sind dann abhängig vom Innenwiderstand der Gatespannungsquelle.

Bei den meisten FET-Typen wird maximal 10 mA Gatestrom zugelassen. Der differentielle Widerstand bei  $I_{Gmax}$  nimmt gegenüber jenem bei  $U_{GS} = 0$  um einen Faktor 10...20 ab. Die Kennlinien gehen aber nicht mehr durch den Nullpunkt, weil der Gatestrom durch einen Teil des Kanals fliesset. Fig. 7 zeigt, dass die Kennlinien schon bei kleinen  $U_{DS}$  stark nichtlinear werden. Daher wird das Gatestromgebiet kaum ausgenutzt.

### 3. Anwendungen des FET im Ohmschen Gebiet

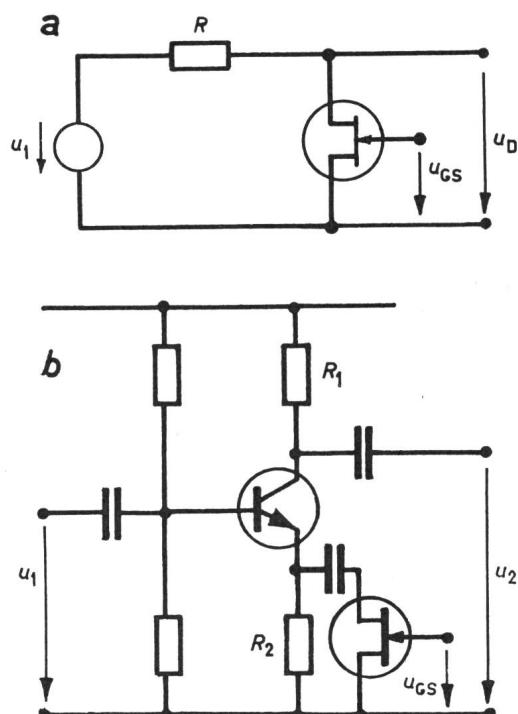

Der FET als steuerbarer Widerstand lässt sich in steuerbaren Dämpfungen, als variabler Gegenkopplungswiderstand,

Fig. 8

Anwendungsbeispiele des gesteuerten FET-Widerstandes

a Variable Dämpfung mit FET

b FET als variabler Gegenkopplungswiderstand

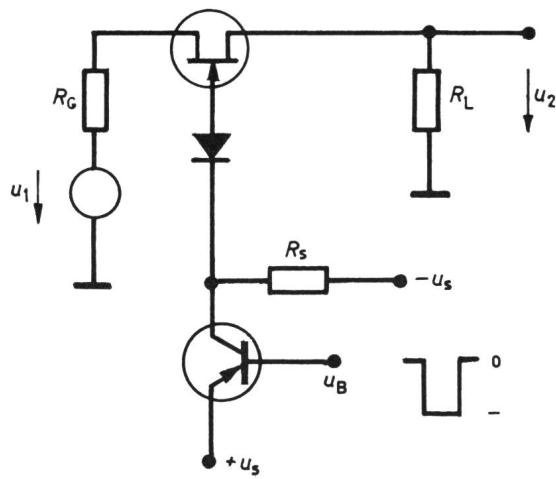

in Multiplikatoren, Modulatoren und steuerbaren aktiven  $RC$ -Filtern einsetzen. Fig. 8 zeigt zwei einfache Beispiele. Bei FET-Schaltern werden nur die beiden extremen Zustände ausgenutzt. Fig. 9 zeigt ein Beispiel eines Chopperschalters.

Bei allen Anwendungen ist zu überlegen, wie gross  $U_{DS}$  sein darf, ohne dass der FET allzu nichtlinear wird. Der entstehende Klirrfaktor ist ein Mass für die Verzerrungen bzw. die Linearität des Elementes.

### 4. Zusammenhang zwischen Klirrfaktor, Aussteuerbarkeit und Regeldynamik

Die folgenden Formeln und Kurven gelten für die Schaltung in Fig. 8a. Nach *Thévenin* lassen sich komplizierte Schaltungen auf diesen grundlegenden Fall zurückführen.

Fig. 9

Beispiel eines Seriechoppers mit FET

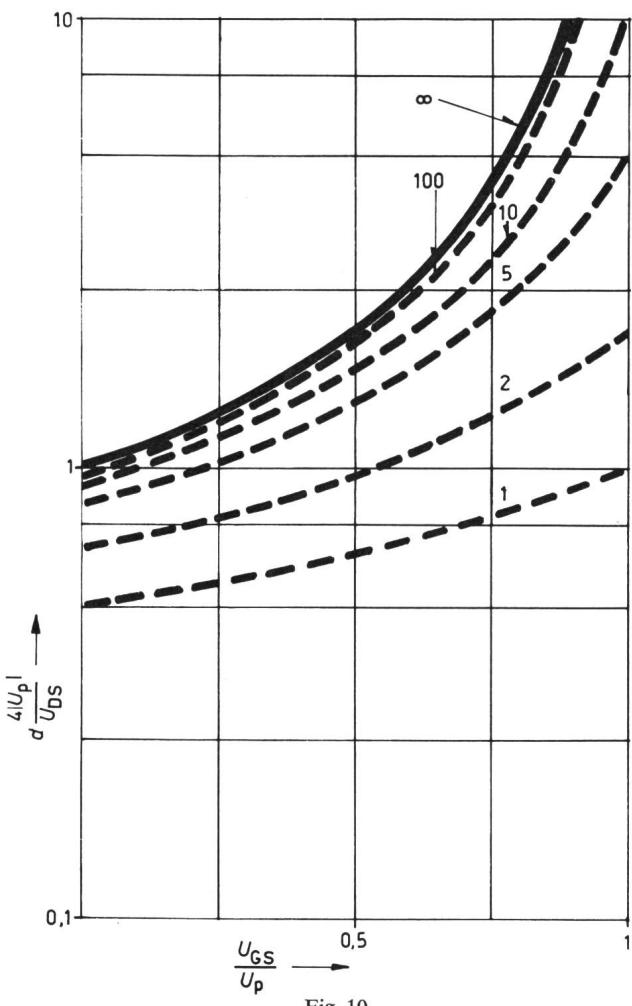

Mit Gl. (5) lässt sich der Klirrfaktor berechnen. Bei Vernachlässigung aller höheren Glieder findet man:

$$d = \frac{U_{\text{DS}}}{4|U_{\text{P}}|} \cdot \frac{1}{1 + \frac{r_{\text{DSS}}}{R} - \frac{U_{\text{GS}}}{U_{\text{P}}}} \quad (9)$$

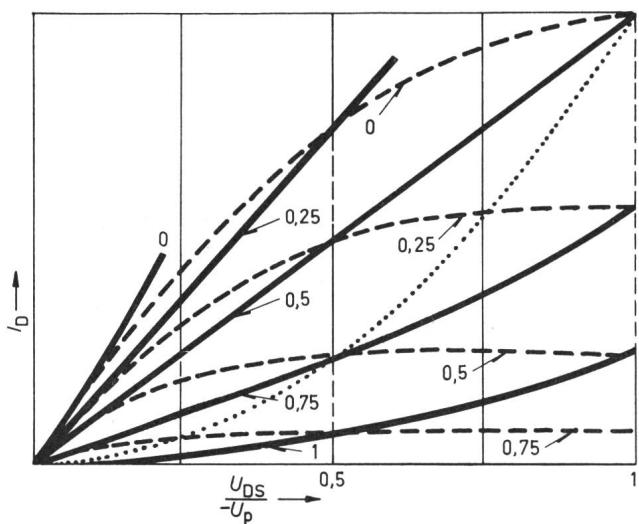

Der Verlauf ist in Fig. 10 aufgezeichnet für verschiedene  $R/r_{DSS}$ . Gl. (9) gilt nur im Ohmschen Gebiet, d. h. nur für  $U_{GS} \geq U_P + U_{DS}$ . Nahe  $U_{GS} = U_P$  hat der Klirrfaktor ein von

**Theoretischer Verlauf des Klirrfaktors [Gl.(9)] der Schaltung in Fig. 8a

in Funktion von  $U_{GS}/U_p$**

$U_{DS}$  abhängiges Maximum und sinkt dann ab auf 0 für  $U_{GS} < U_P$ , wenn  $g_{DS} = 0$ . Für  $U_{GS} = 0$  beginnt in der negativen Halbwelle Gatestrom zu fliessen. Daher ist der gemessene Klirrfaktor bei  $U_{GS} = 0$  etwas höher als der berechnete. Für  $U_{GS} = 0,1 \dots 0,9 U_P$  stimmt der gemessene sehr gut mit dem nach Gl. (9) berechneten Klirrfaktor überein.

Die Aussteuerbarkeit ist proportional zu  $U_P$  oder anders ausgedrückt: Die Verzerrungen nehmen umgekehrt proportional zu  $U_P$  ab.

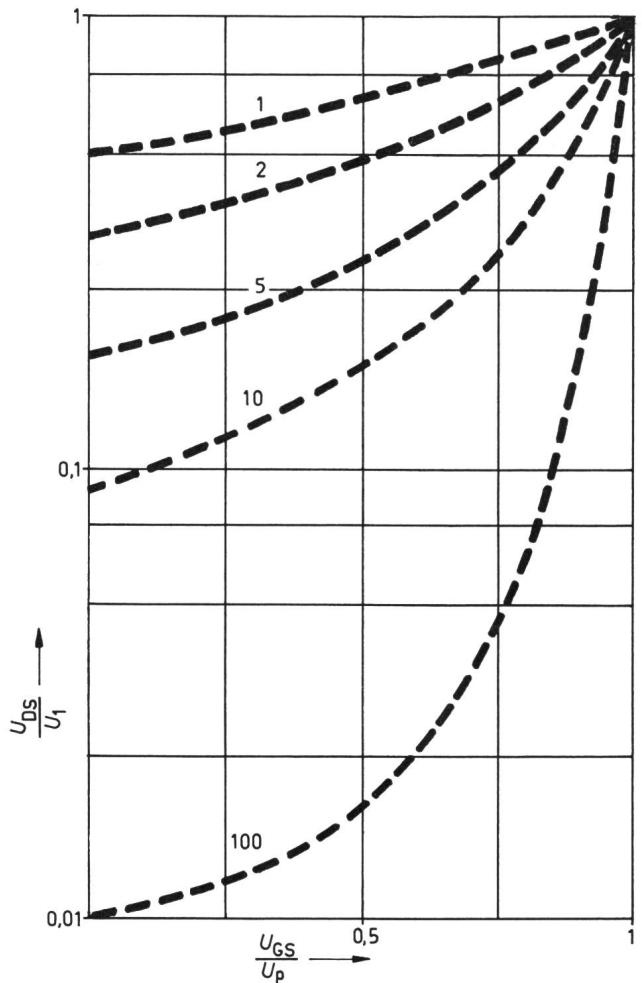

Fig. 11

Abschwächung des Spannungsteilers in Fig. 8a in Funktion von  $U_{GS}/U_p$

Parameter:  $R/r_{DSO}$

nal zu  $U_P$  ab. Für steuerbare Widerstände wären FET mit möglichst grosser Abschnürspannung erwünscht. Da solche FET in allen andern Anwendungen (Schalter, Verstärker) unerwünscht sind, sind sie im Handel nicht erhältlich.

Mit abnehmendem  $R$  nimmt der Klarfaktor ab, leider aber auch der mögliche Regelbereich. Die betrachtete Schaltung hat folgende Abschwächung:

$$a = \frac{U_{\text{DS}}}{U_1} = \frac{1}{1 + \frac{R}{r_{\text{DSS}}} \left( 1 - \frac{U_{\text{GS}}}{U_{\text{P}}} \right)} \quad (10)$$

Fig. 11 zeigt den Verlauf für verschiedene  $R$ . Die Gln. (9) und (10) lassen sich zusammenfassen zu einem Ausdruck:

$$d_{\max} \approx \frac{U_1 a_{\min}^2}{4|U_p| a_{\max}} \approx \frac{U_{\text{DS}} a_{\min}}{4|U_p| a_{\max}} = \frac{U_{\text{DS}} r}{4|U_p|} \quad (11)$$

$a_{\min}$  (bzw.  $a_{\max}$ ) ist die minimale (bzw. maximale) Abschwächung,  $d_{\max}$  ist der maximale Klirrfaktor, der bei  $a_{\min}$

Fig. 12

#### Kennlinien der Antiparallelschaltung von 2 identischen FET

Parameter:  $U_{GS}/U_P$ . Durch Addition der Ströme der beiden FET (gestrichelt) erhält man das gesuchte Kennlinienfeld

auftritt. Bei vorgegebener Regeldynamik  $r$  ist es für den Klirrfaktor gleichgültig, ob man bei kleinem Widerstand  $U_{GS}$  bis fast an  $U_P$  aussteuert oder bei viel grösserem  $R$  nur bis zu einem Bruchteil von  $U_P$ ;  $d_{max}$  ist in beiden Fällen gleich gross.

Sind in Gl. (11) zwei Grössen gegeben, dann ist auch die dritte bestimmt.

Beispiele mit  $|U_P| = 5$  V:

$$\begin{aligned} d_{max} &= 10\% & U_{DS} &= 5 \text{ mV} & r &= 400 \\ r &= 10 & U_{DS} &= 50 \text{ mV} & d_{max} &= 2,5\% \\ d_{max} &= 1\% & r &= 100 & U_{DS} &= 2 \text{ mV} \end{aligned}$$

Dieser Klirrfaktor ist für die meisten praktischen Anwendungen zu gross. Im nächsten Abschnitt wird nach Möglichkeiten gesucht, um ihn zu verkleinern.

#### 5. Möglichkeiten zur Linearisierung der FET-Kennlinien

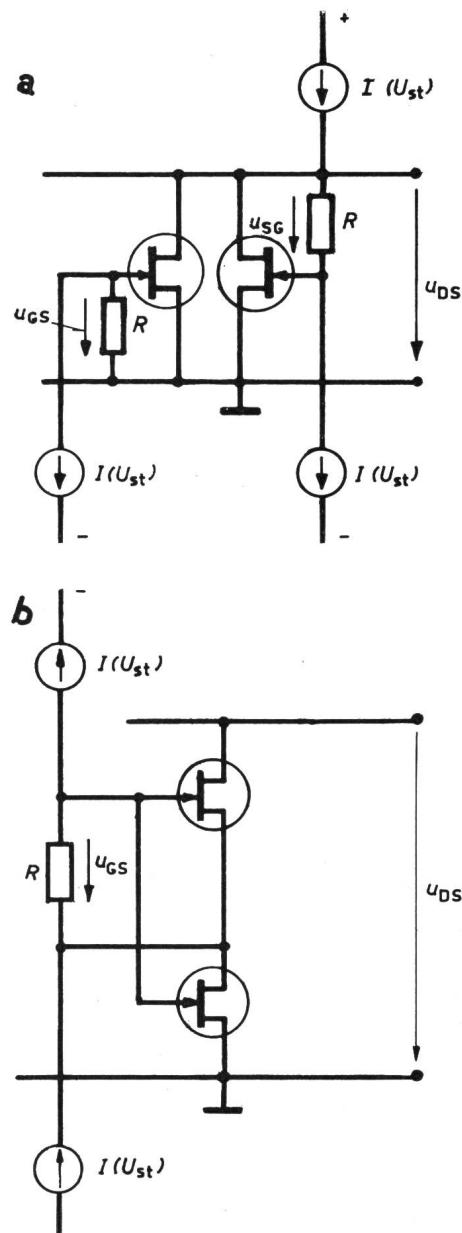

Überlagert man die Kennlinien von zwei identischen FET, wobei der eine normal, der andere rückwärts betrieben wird, so erhält man eine Antiparallel- bzw. Antiserieschaltung. In der einen werden die Ströme, in der andern die Spannungen addiert. In beiden Fällen wird das Kennlinienfeld zentral-symmetrisch.

Fig. 12 zeigt das entstehende Kennlinienfeld bei der Antiparallelschaltung. Bei identischen FET hebt sich der quadratische Term in Gl. (5) auf und übrig bleibt:

$$I_D(U_{DS}, U_{GS}) = \frac{4I_{DSS}}{-U_P} U_{DS} \left(1 - \frac{U_{GS}}{U_P}\right) \quad (12)$$

Diese Gleichung gilt nur im Ohmschen Gebiet. Bei der Antiserieschaltung ist die Linearisierung weniger gut, aber auch dort werden infolge der Zentralsymmetrie die geraden Harmonischen sehr stark reduziert.

In beiden Fällen ist die Ansteuerung kompliziert. Fig. 13 zeigt zwei Möglichkeiten für N-Kanal-FET. Bei einer Kombination N-Kanal und P-Kanal wäre die Ansteuerung einfacher, zwei identische FET zu finden hingegen schwieriger.

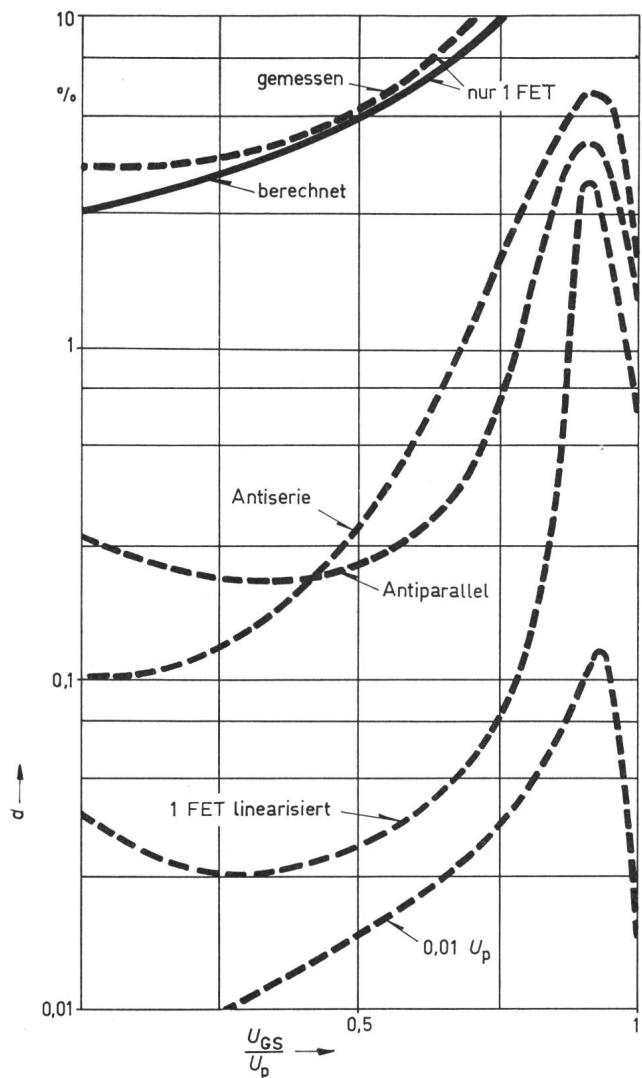

Durch eine Art Gegenkopplung ist es auch bei Verwendung nur eines FET möglich, die Kennlinien zu linearisieren. Überlagert man der Gatespannung die halbe Drainspannung, d. h. ersetzt man in Gl. (5)

$$U_{GS} \rightarrow U_{GS} + \frac{U_{DS}}{2} \quad (13)$$

so erhält man:

$$I_D = \frac{2I_{DSS}}{-U_P} U_{DS} \left(1 - \frac{U_{GS}}{U_P}\right) \quad (14)$$

Der quadratische Term verschwindet wie bei der Parallelschaltung. Im Gegensatz zu dieser muss man ihn aber nicht durch möglichst gutes Aussuchen von identischen FET kompensieren, sondern kann ihn durch optimales Abgleichen der rückgeführten Spannung zum Verschwinden bringen. Fig. 14 zeigt, wie das linearisierte Kennlinienfeld aus dem Gegebenen konstruiert werden kann. Ideale Linearisierung ist nur im

Fig. 13

Möglichkeiten zur Ansteuerung der Gate-Sourcestrecke, die nicht geerdet ist

a bei Antiparallelschaltung

b bei Antiserieschaltung

Nur wenn alle Stromquellen identische Ströme  $I$  in Funktion der Steuerspannung  $U_{st}$  liefern, entsteht am Ausgang kein überlagertes Gleichspannungspotential

Fig. 14

**Konstruktion des durch «Gegenkopplung» linearisierten Kennlinienfeldes**

Man findet es, indem man im ursprünglichen Kennlinienfeld (gestrichelt) den Drainstrom  $I_D$  für die nach Gl. (13) veränderte Gatespannung sucht. Parameter:  $U_{GS}/U_p$

Ohmschen Gebiet möglich. Aber auch bei Aussteuerung ins Pinch-off-Gebiet werden die Verzerrungen stark reduziert. In Fig. 15 werden gemessene Klirrfaktoren für die verschiedenen

Fig. 15

**Vergleich des gemessenen Klirrfaktors verschiedener Linearisierungsschaltungen in Funktion von  $U_{GS}/U_p$  für  $U_{DS} = 0,1|U_p|$ , bzw.  $0,01|U_p|$  (unterste Kurve)**

Linearisierungsmöglichkeiten verglichen. Bei  $U_{DS} = 0,1|U_p|$  (z. B.  $|U_p| = 5$  V,  $U_{DS} = 0,5$  V) erreicht man im Maximum eine Verminderung von  $d$  um einen Faktor 100. Das Maximum des Klirrfaktors wird allerdings etwas weniger reduziert.

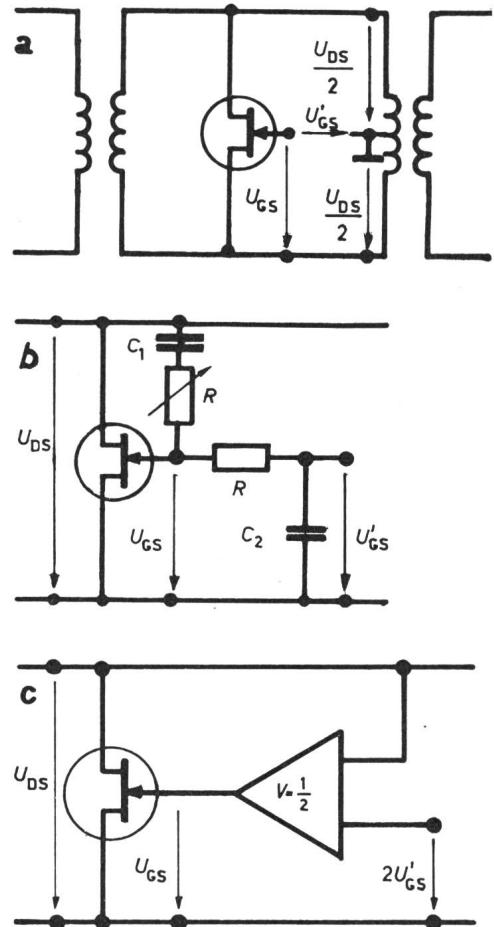

Zur Addition von  $U_{DS}/2$  zu  $U_{GS}$  gibt es, je nach Frequenzbereich, verschiedene Möglichkeiten.  $U_{GS}$  darf nicht auf  $U_{DS}$  zurückwirken. Fig. 16a zeigt eine Lösung mit angezapftem Transformator, Fig. 16b mit Kondensatorkopplung. Beide funktionieren nur mit Wechselspannungen, während die Schaltung in Fig. 16c auch für Gleichspannungen geeignet ist. Die zwei Verstärkereingänge seien hochohmig. Die Ver-

**Mögliche Schaltungen zur Linearisierung des FET Kennlinienfeldes**

a mit symmetrischen Transformatoren; b mit Kondensatorkopplung;

c mit Trennverstärker

a und b nur für Wechselspannungen, c auch für Gleichspannung

stärkung sei einstellbar auf  $0,5 \pm 0,1$  zum Abgleichen, da der optimale «Gegenkopplungsfaktor» etwas von 0,5 abweichen kann.

## 6. Zusammenfassung

Der Feldeffekttransistor (FET) lässt sich ausgezeichnet als steuerbarer Widerstand verwenden, falls sein Kennlinienfeld durch Antiparallelschaltung oder eine Art Gegenkopplung linearisiert wird. Wie Fig. 14 zeigt, liegt der Klirrfaktor bei einer Amplitude der Drainspannung von 50 mV in jedem Fall unter ca. 1 %. Im Vergleich zu andern Elementen, die ähnliche Regelzeitkonstanten haben (Dioden, Transistoren) ist dieses Resultat um Größenordnungen besser.

### Adresse des Autors:

Hanspeter von Ow, wissenschaftlicher Mitarbeiter am Institut für Fernmelde-technik der ETH-Zürich, 8006 Zürich.