**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätswerke

**Band:** 60 (1969)

**Heft:** 22

**Artikel:** Circuits logiques à MOS-FET

**Autor:** Hammer, W.

**DOI:** <https://doi.org/10.5169/seals-916192>

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

#### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 05.12.2025

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Circuits logiques à MOS-FET

Conférence donnée à la 28<sup>e</sup> Journée suisse de la technique des télécommunications, le 12 juin 1969 à Fribourg,

par W. Hammer, Lausanne

329 - 336

681.325.65:621.382.323

*Le transistor à effet de champ du type MOS est un élément qui convient particulièrement bien à la réalisation de circuits logiques intégrés. Ses principaux avantages sont: facilité d'intégration, faibles dimensions, résistance d'entrée élevée, ainsi que sa possibilité d'être utilisé en résistance de grande valeur.*

*Une étude sommaire de ces avantages nous montrera l'influence de la technologie sur le développement des circuits et nous analyserons en guise d'exemple certaines réalisations industrielles.*

*Les MOS-FET ont en particulier révolutionné la conception de registres à décalages. En effet, nous verrons comment la capacité d'entrée de cet élément peut être avantageusement mise à profit pour la réalisation de mémoires et surtout de registres dynamiques.*

*En conclusion, nous analyserons les raisons pour lesquelles les circuits logiques à MOS-FET n'ont actuellement qu'un faible marché, et nous tenterons de prévoir dans quelle mesure leur avenir est prometteur.*

*Der MOS-Feldeffekttransistor (MOS-FET) ist ein Element, welches sich besonders für die Herstellung von integrierten logischen Schaltungen eignet. Seine grundlegenden Vorteile sind: Integrationsfähigkeit, kleine Abmessungen, hoher Eingangswiderstand sowie die Möglichkeit des Einsatzes als hochohmiger Widerstand.*

*In einer kurzen Betrachtung dieser Vorteile wird gezeigt, in welcher Weise die Technologie die Entwicklung der Schaltung beeinflusst. Einige industrielle Anwendungen werden diskutiert.*

*Die MOS-FET haben besonders die Konzeption der Schieberegister revolutioniert. Die Eingangskapazität dieser Bauelemente kann vorteilhaft zur Herstellung von Speichern und von dynamischen Registern verwendet werden.*

*Zum Schluss werden die Gründe untersucht, aus welchen die logischen MOS-FET-Schaltungen heute einen noch kleinen Anwendungsbereich haben und in welcher Weise die zukünftige Entwicklung zu erfolgversprechenden Resultaten führen kann.*

S'il avait fallu dresser une liste d'exigences pour un élément, en vue de son utilisation dans des circuits logiques intégrés, on aurait sans doute énuméré la liste suivante:

- coût minime

- intégration aisée

- faibles dimensions en vue d'une miniaturisation poussée

- universalité de fonctions: utilisation comme élément passif ou actif

- résistance d'entrée élevée

- faible résistance de sortie

- utilisation avec une faible consommation de courant

- simplicité d'utilisation.

Le MOS-FET réunit précisément tous ces avantages:

— Il est bon marché, parce que facilement intégrable et de faibles dimensions; or le prix d'un circuit intégré dépend pour la plus grande part de sa surface.

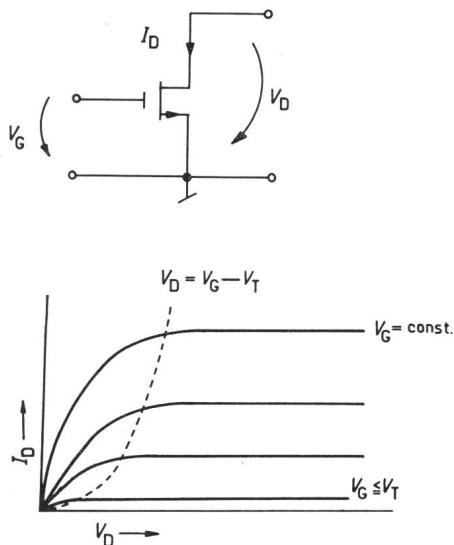

Fig. 1

Caractéristiques d'un MOS-FET

$$I_D = 0$$

$$V_G \leq V_T$$

$$I_D = K \left[ (V_G - V_T) V_D - \frac{V_D^2}{2} \right]$$

$$V_D \leq V_G - V_T$$

$$I_D = \frac{K}{2} (V_G - V_T)^2$$

$$V_D \geq V_G - V_T$$

$$K = \frac{w C_0 u}{L}$$

w largeur du canal;  $C_0$  capacité grille-canal par unité de surface;  $I_D$  courant de drain;  $K$  facteur de pente;  $L$  longueur du canal;  $V_D$  tension de drain;  $V_G$  tension de grille;  $V_T$  tension de seuil du MOS-FET;  $\mu$  mobilité des porteurs

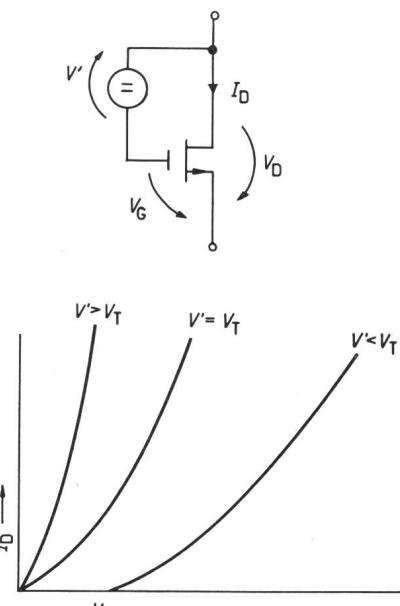

Fig. 2

MOS-FET utilisé en résistance

$$I_D = 0$$

$$V_D \leq V_T - V'$$

$$I_D = K \left[ (V' - V_T) V_D + \frac{V_D^2}{2} \right]$$

$$V' \geq V_T$$

$$I_D = \frac{K}{2} (V' + V_D - V_T)^2$$

$$V' \leq V_T$$

$$K = \frac{w C_0 u}{L}$$

$V'$  tension grille-drain fixe

Autres désignations voir fig. 1

— Il est universel. Il peut être utilisé comme élément actif, étant donné qu'il a approximativement les mêmes caractéristiques qu'une penthode (fig. 1). En tant qu'élément passif, il peut jouer le rôle d'une résistance de grande valeur, ce qui est un avantage considérable par rapport aux circuits intégrés ordinaires, dans lesquels de telles résistances prennent une surface importante. En effet, si l'on applique une tension fixe entre grille et drain (fig. 2) les caractéristiques du dipôle ainsi créé sont approximativement celles d'une résistance. Pour une application digitale, cette approximation est suffisante, et l'on pourra agir sur le facteur  $K$  pour créer des résistances de valeur désirée.  $K$  dépend, en effet, essentiellement des dimensions du MOS-FET. Si l'on désire une résistance de grande valeur, il faudra prendre une faible largeur et une grande longueur du canal.

En pratique on prendra  $V' = 0$ , ce qui revient à relier la grille et le drain.

— La résistance d'entrée du MOS-FET est très élevée. En effet, la grille est totalement isolée du canal; un courant de grille n'apparaît qu'en régime transitoire pour charger ou décharger la capacité d'entrée. Cette capacité d'entrée nous permettra d'ailleurs,

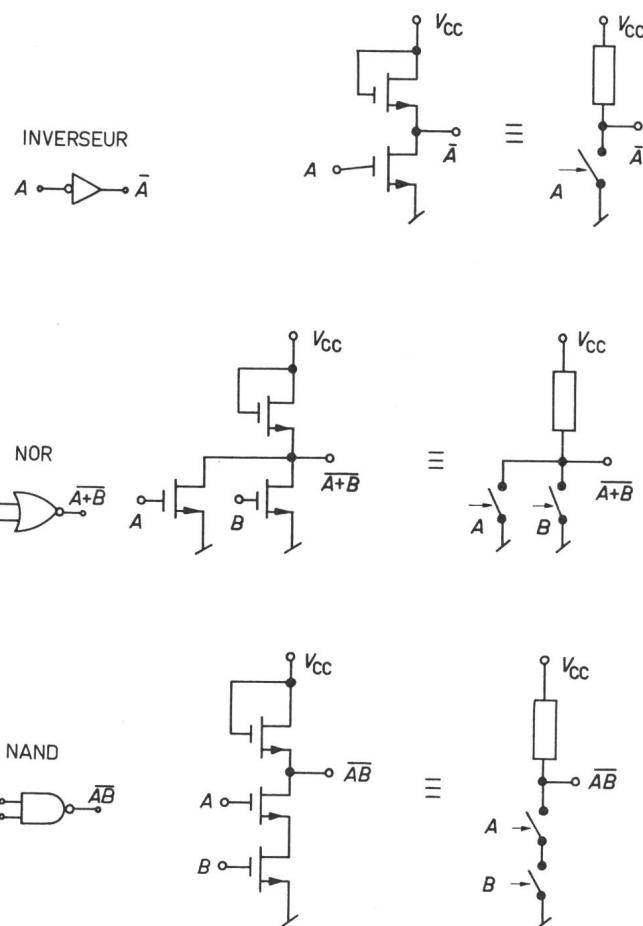

Fig. 3

Circuits logiques à MOS-FET

$A$  variable logique;  $\bar{A}$  inverse logique de  $A$ ;  $B$  variable logique;  $V_{CC}$  tension d'alimentation positive

nous le verrons plus loin, de stocker une information pendant un certain temps et de la mettre ainsi à profit en guise de mémoire dynamique.

— La résistance de sortie du MOS-FET, de l'ordre de  $10 \text{ k}\Omega$ , est relativement faible. Un étage pourra ainsi être chargé par de nombreux autres étages.

— La possibilité du MOS-FET de pouvoir être utilisé en résistance de grande valeur nous permettra de faire des montages à très faible consommation de puissance.

— La tension de seuil  $V_T$  à partir de laquelle le MOS-FET conduit, constitue une immunité naturelle aux parasites, appréciée dans les circuits logiques industriels.

— Enfin, les montages logiques à MOS-FET sont très simples, vu que la tension de sortie d'un étage couvre la plage requise par

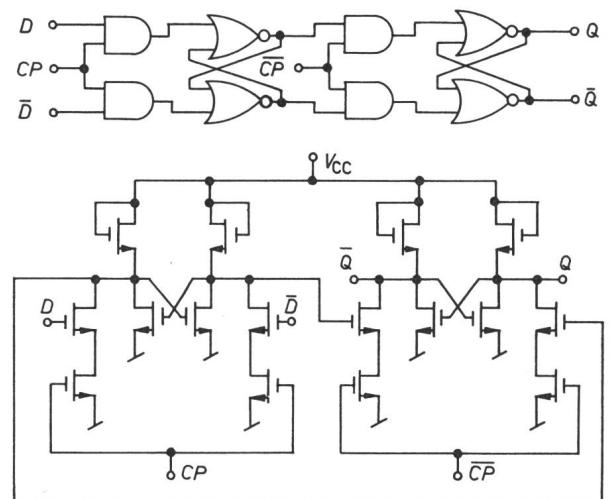

Fig. 4

Flip-flop «master-slave» de type D

$CP$  impulsion d'horloge (Clock Pulse);  $D$  variable logique d'entrée;  $Q$  fonction logique de sortie;  $V_{CC}$  tension d'alimentation positive

la tension d'entrée d'un autre étage. Le couplage direct entre étages s'avère ainsi possible.

La fig. 3 nous montre quelques exemples de circuits logiques à MOS-FET. On remarquera que le seul élément figurant dans ces schémas est le MOS-FET, utilisé comme élément actif (interrupteur) et comme résistance de charge.

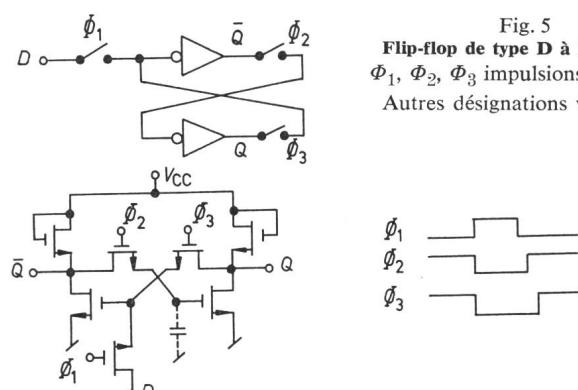

D'ores et déjà on s'aperçoit de l'influence de la technologie sur la conception des circuits. Mais cette influence est encore beaucoup plus marquée pour la conception de circuits séquentiels, en particulier des registres à décalage. Jusqu'ici un registre à décalage était constitué d'une succession de flip-flops «master-slave» du type D (delay). La fig. 4 nous montre une réalisation de ce type de flip-flop classique à l'aide de MOS-FET. Rappelons que la partie «slave» de ce dernier sert à garder l'information présente à la sortie pendant l'inscription d'une nouvelle information dans la partie «master». Or, une réalisation à MOS-FET peut satisfaire à cette exigence de manière beaucoup plus simple. La fig. 5 nous montre cette réalisation comprenant seulement deux inverseurs et trois interrupteurs. Lorsque l'on désire inscrire une nouvelle information dans ce flip-flop, il suffit d'ouvrir les interrupteurs 2 et 3 et de fermer l'interrupteur 1. La valeur de  $D$  va se trouver à l'entrée de l'un des inverseurs et  $\bar{D}$  à la sortie de celui-ci. L'autre inverseur est totalement déconnecté et aura encore en mémoire (dans la capacité de grille du MOS-FET actif) la valeur précédente de  $Q$ . On pourra donc pendant un certain temps utiliser la valeur précédente

Fig. 5

Flip-flop de type D à MOS-FET

$\Phi_1, \Phi_2, \Phi_3$  impulsions d'horloge

Autres désignations voir fig. 4

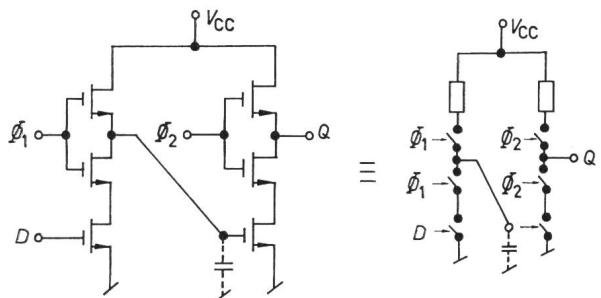

Fig. 6

Flip-flops D dynamiques ou éléments de registres dynamiques

Désignations voir fig. 4 et 5

de  $Q$  qui se trouve à la sortie de cet inverseur découpé. La capacité d'entrée du MOS-FET est ainsi avantageusement mise à profit et remplace dans le cas particulier toute la partie «slave» du montage précédent de la Fig. 4. Pour terminer l'inscription, il suffira de refermer l'interrupteur 2, puis le 3, après avoir ouvert l'interrupteur 1.

Dans certaines applications, il n'est pas indispensable que les registres à décalage fonctionnent à fréquence d'horloge nulle. On peut alors imaginer des «registres dynamiques»

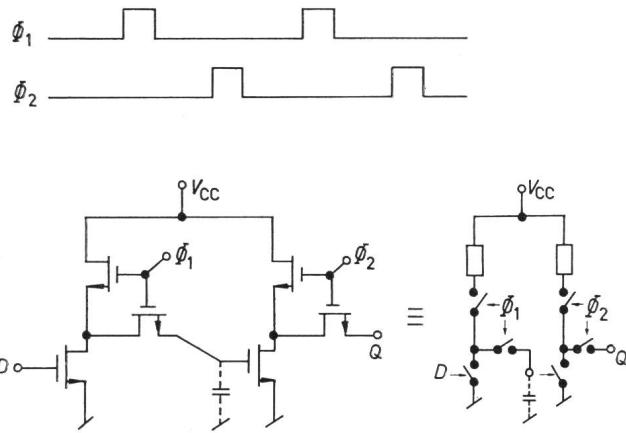

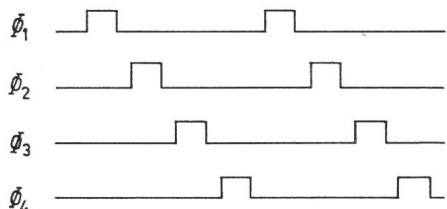

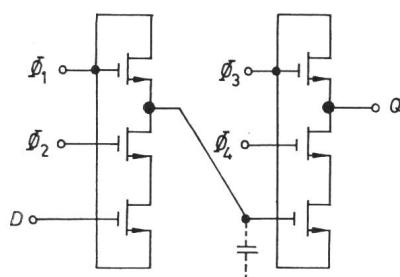

Fig. 7

Flip-flop D dynamique à faible consommation de courant

Désignations voir fig. 4 et 5

qui ont une structure étonnamment simple et entièrement nouvelle si on les réalise à l'aide de MOS-FET.

La fig. 6 nous montre deux de ces structures possibles qui fonctionnent de la même manière:

Lorsque l'impulsion d'horloge  $\Phi_1$  est présente, la première partie du circuit n'est rien d'autre qu'un inverseur dont la sortie est reliée à l'entrée de la deuxième partie. La capacité de grille de cette dernière prendra la valeur  $\bar{D}$ . Après la descente de l'impulsion d'horloge  $\Phi_1$ , cette capacité est entièrement isolée et garde donc la valeur  $\bar{D}$  suffisamment longtemps pour que la même opération puisse se faire dans la deuxième partie. On retrouvera donc la valeur d'entrée  $D$  à la sortie, à la suite des impulsions  $\Phi_1$  et  $\Phi_2$ .

Ce flip-flop de type  $D$  ne pourra pas garder indéfiniment une information, d'où le terme «dynamique» qui le caractérise.

Il est possible d'apporter certaines améliorations à ce flip-flop, en particulier en vue de diminuer sa consommation: lorsqu'une impulsion d'horloge est présente, un courant circule de  $V_{CC}$  à la terre et une faible dérivation de ce courant va charger ou décharger la capacité de grille de l'étage suivant. On a donc cherché à supprimer le courant circulant inutilement et on est arrivé à la structure de la fig. 7.

Dans cette structure, tous les MOS-FET sont utilisés en interrupteur et chaque interrupteur se ferme à tour de rôle comme le montre la séquence des impulsions d'horloge.

Lorsqu'on ferme l'interrupteur 1, la capacité d'entrée de l'étage suivant se charge. Puis on ferme l'interrupteur 2 et cette capacité reste chargée si  $D$  vaut 0, ou se décharge si  $D$  vaut 1. Après ces deux temps, on aura donc la valeur de  $\bar{D}$  mémorisée dans cette capacité. De même, on ferme l'interr-

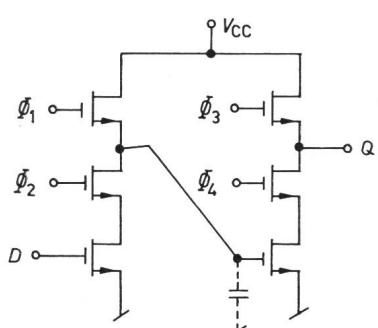

Fig. 8

Flip-flop D dynamique sans source d'alimentation

Désignations voir fig. 4 et 5

rupteur 3, et la capacité d'entrée du flip-flop suivant se charge, puis l'interrupteur 4, et cette capacité reste chargée si  $\bar{D}$  vaut 0, ou se décharge si  $\bar{D}$  vaut 1.

Les 4 impulsions d'horloge ayant agi, on retrouvera la valeur  $D$  mémorisée à l'entrée du flip-flop suivant. On remarquera que pour cette structure, les seuls courants nécessaires sont ces deux courants de charge des capacités, qui sont donc très faibles. On a ainsi réduit avantageusement la consommation du flip-flop  $D$ .

Une dernière simplification peut encore être faite: la tension d'alimentation  $V_{CC}$  n'est utilisée que lorsque  $\Phi_1$  et  $\Phi_3$  sont présents. On peut utiliser directement  $\Phi_1$ , respectivement  $\Phi_3$  comme alimentations des différents étages. De même, la terre n'est nécessaire que lorsque  $\Phi_2$  et  $\Phi_4$  sont présents, c'est-à-dire lorsque  $\Phi_1$  resp.  $\Phi_3$  sont absents. De même on utilisera  $\Phi_1$  et  $\Phi_3$  comme niveaux de référence, ce

qui aboutit finalement à la structure d'une simplicité remarquable: le flip-flop *D* dynamique de la fig. 8.

Une conclusion évidente apparaît:

Le MOS-FET, étant donné sa grande simplicité et ses multiples possibilités d'utilisation, est l'élément le mieux adapté à la réalisation de circuits logiques intégrés.

Mais... car il y a un «mais», la faible consommation de ces circuits a pour corollaire une rapidité limitée. La fréquence maximum d'utilisation des circuits logiques est de

l'ordre de grandeur de 1 MHz. C'est une des raisons pour lesquelles les circuits intégrés à MOS-FET sont actuellement d'un emploi limité. Des travaux sont en cours pour hausser ce plafond; on parle déjà de circuits fonctionnant à 50 MHz.

Nous sommes persuadés que le MOS-FET, dont nous avons tenté d'exposer certains avantages, est destiné à un avenir prometteur. Souhaitons que cet avenir soit proche.

#### Adresse de l'auteur:

*W. Hammer*, assistant à la chaire de systèmes logiques de l'Ecole Polytechnique Fédérale de Lausanne, 1000 Lausanne.

## Comité Européen de Coordination de Normes Electriques (CENEL)

### Sitzung des Comité directeur vom 19. September 1969 in Wien

Das Comité directeur des CENEL tagte am 19. September 1969 in Wien unter dem Vorsitz seines Präsidenten, *S. E. Goodall* (Vereinigtes Königreich). Vertreten waren alle Nationalkomitees der EWG- und der EFTA-Länder (einschl. Finnlands). Das CES hatte *E. Dünner* und *H. Marti* delegiert.

Das Protokoll der Sitzung vom 26. März 1969 in Zürich wurde genehmigt.

Haupttraktandum war das Gesuch des Tripartite Committee on Electronic Components, das CENEL solle die Durchführung des vom Committee entworfenen Verfahrens der Harmonisierung elektronischer Bestandteile übernehmen.

An der Sitzung des Comité directeur des CENEL in Zürich lag erstmals ein solches Gesuch vor. Das Tripartite Committee war vor einigen Jahren von Regierungsstellen Englands, Deutschlands und Frankreichs gebildet worden, um ein System einheitlicher Qualitätsbezeichnungen und entsprechender Kontrollen bei den Herstellern elektronischer Bestandteile aufzustellen. Von Anfang an war das Tripartite Committee der Auffassung, es sei vorzuziehen, wenn ein neutrales Gremium mit breiterer Grundlage die Durchführung des Systems übernehme, damit auch andere als die drei Gründerländer daran teilnehmen könnten und es von den Regierungsstellen unabhängig werde. Auf der Suche nach einem solchen Gremium wandte sich das Tripartite Committee an das Comité directeur des CENEL und lud gleichzeitig weitere interessierte Nationalkomitees zu einer Sitzung der Arbeitsgruppe des Committee ein, die im Mai 1969 in München abgehalten wurde. Dieser Situation gegenüber sah sich das Comité directeur im März 1969 ausserstande, einen grundsätzlichen Entscheid zu fällen, weil sich sowohl das System an sich als auch die Konsequenzen von dessen Durchführung nicht genügend überblicken liessen. Es verschob deshalb seinen Entscheid auf die Wiener Sitzung vom 19. September. Inzwischen fanden Besprechungen und Verhandlungen zwischen Präsident Goodall und Vertretern des Tripartite Committee statt, welche ergeben sollten, was für eine Aufgabe das Comité directeur des CENEL konkret übernehmen müsste. Eine Reihe von Fragen blieb indessen noch ungelöst. Ausser den Nationalkomitees der Gründerländer interessieren sich zur Zeit diejenigen von Belgien, Dänemark, Italien, der Niederlande, Norwegen und Schweden für die Teilnahme am Tripartite-System.

Präsident Goodall unterbreitete dem Comité directeur zwei Anträge, die gutgeheissen wurden. Erstens: Das Comité directeur des CENEL beschliesst grundsätzlich, das vom Tripartite Committee entworfene System für die Harmonisierung elektronischer Bestandteile durchzuführen. Zweitens: Eine ad-hoc-Arbeitsgruppe, genannt President's ad-hoc Working Group, wird gebildet, welche bis April 1970 alle Detail-Fragen klären und

Bericht erstatten muss. Ihr Mandat dauert ein halbes Jahr; sie wird nach dessen Ablauf aufgelöst. Die Aufgabe der Arbeitsgruppe besteht darin, einmal die ungeklärten Fragen zu erforschen und zweitens Vorschläge zuhanden des Comité directeur zu unterbreiten, wie die grundsätzlich beschlossene Übernahme der neuen Aufgabe durchzuführen sei. Vermutlich wird ein vom Comité directeur geleitetes Comité spécial mit einem eigenen Sekretariat gebildet werden müssen, wobei dessen Aufwand von den Nationalkomitees derjenigen Länder gedeckt wird, welche dem Harmonisierungssystem beitreten. Schon jetzt herrscht Einigkeit darüber, was *nicht* zu den Aufgaben des CENEL gehören wird, nämlich: die Anerkennung neuer Kontrollstellen; das Erstellen von Regeln für die Anerkennung neuer Prüfstellen; die Einberufung der Prüfstellen zu Sitzungen; Fragen der Abweichung von den aufgestellten Regeln, welche sich durch die praktische Anwendung ergeben. Das Comité directeur sieht seine erste Aufgabe darin, zu der Harmonisierung der elektronischen Komponenten im europäischen Raum Hand zu bieten. Die Kontrolle der Qualität selbst gehört aber nicht in den Bereich des CENEL und wird vom Comité directeur ausdrücklich abgelehnt. Auf lange Sicht soll der Übergang vom europäischen Raum auf die ganze Welt angestrebt werden, wobei zu gegebener Zeit das CENEL die übernommene Aufgabe beispielsweise der CEI abtreten könnte. In das President's ad-hoc Committee wurden je ein Vertreter der Nationalkomitees von Deutschland, Frankreich, des Vereinigten Königreichs, von Italien, der Niederlande, sowie ein gemeinsamer Vertreter der Nationalkomitees der drei skandinavischen Länder delegiert. Die erste Sitzung findet am 18. Oktober 1969 in London statt.

Eine Mitteilung des Präsidenten über die offiziellen Kontakte zwischen CENEL und CEI löste eine längere Aussprache aus. Daraus ergab sich, dass es für beide Teile besser ist, wenn offizielle Beziehungen zwischen dem Comité directeur und der CEI unterbleiben. Das hindert selbstverständlich die Nationalkomitees, die dem CENEL angehören, nicht, in der CEI wie bisher völlig frei mitzuarbeiten,

Im gleichen Sinne wurde über eine Anregung entschieden, einen Vertreter des Nationalkomitees der USA als Beobachter zu den Sitzungen des Comité directeur des CENEL einzuladen. Das CENEL muss gemäss seiner Zielsetzung eine Organisation der Nationalkomitees derjenigen europäischen Länder bleiben, welche der EWG oder der EFTA angehören. Deshalb wurde auch beschlossen, auf ein Ansuchen tschechischer Stellen, eine Verbindung mit dem CENEL zwecks Vereinheitlichung bestimmter Motordimensionen in den ost- und westeuropäischen Staaten herzustellen, damit zu beantworten, dass nur die CEI zuständig für die Normung sei.